存储器设备和操作存储器设备的方法

文献发布时间:2023-06-19 13:49:36

本申请要求于2020年6月23日在韩国知识产权局提交的韩国专利申请号10-2020-0076692的优先权,其全部公开内容通过引用并入本文。

技术领域

本公开涉及一种存储器设备和一种操作存储器设备的方法,并且更具体地,本公开涉及一种能够执行编程操作的存储器设备和一种操作编程操作的方法。

背景技术

存储器设备可以存储数据或输出所存储的数据。例如,存储器设备可以是易失性存储器设备,其中所存储的数据在电源切断时丢失,或者存储器设备可以是非易失性存储器设备,其中即使电源切断,所存储的数据也被保持。存储器设备可以包括:其中存储有数据的存储器单元阵列;能够执行编程、读取或擦除操作的外围电路;以及能够控制外围电路的逻辑电路。

存储器单元阵列可以包括多个存储器块,并且多个存储器块中的每个可以包括多个存储器单元。存储器单元可以在位线与源极线之间彼此串联连接,并且配置串。被包括在不同串中并且连接到相同字线的存储器单元可以配置页。编程操作和读取操作可以以页为单位执行。编程操作可以包括增加所选择存储器单元的阈值电压的子编程操作、以及确定所选择存储器单元的阈值电压是否增加到目标电压的验证操作。子编程操作和验证操作可以配置一个循环,并且多个循环可以在编程操作中被执行。当执行多个循环时,可以逐步增加编程电压。这种编程方法被称为增量步进脉冲编程(ISPP)方法。

发明内容

根据本公开的一个实施例的存储器设备可以包括:包括多个串的存储器块,该多个串包括连接到局部线的多个存储器单元;被配置为生成操作电压并且将操作电压输出到全局线的电压生成器;响应于块选择电压而将全局线和局部线彼此连接或彼此阻断的通过开关组;被配置为响应于行地址而输出块选择电压的解码器;以及逻辑电路,该逻辑电路被配置为控制解码器和电压生成器,使得局部线在初始化串的沟道之后被浮置,并且全局线的电压低于当初始化串的沟道时全局线的电压,当存储器块的所选择页中包括的所选择存储器单元的编程操作完成时,串的沟道被初始化并且局部线被浮置。

根据本公开的一个实施例的操作存储器设备的方法可以包括:提供通过全局线输出操作电压的电压生成器、将施加到全局线的操作电压传送到局部线的通过开关、以及包括连接到局部线的多个存储器单元的存储器块;将全局线和局部线彼此连接;对与局部线之中的所选择字线连接的所选择存储器单元执行编程操作;当编程操作完成时,初始化包括存储器单元的串的沟道;当沟道被初始化时,浮置沟道;当沟道被浮置时,将全局线和局部线彼此阻断;以及当局部线被浮置时,降低全局线中包括的全局字线的电压。

附图说明

图1是用于描述根据本公开的一个实施例的存储器设备的图。

图2是用于描述图1的存储器单元阵列的图。

图3是用于具体描述根据本公开的一个实施例的第i存储器块的图。

图4是用于具体描述存储器单元的结构的图。

图5是用于具体描述根据本公开的一个实施例的行解码器的图。

图6是用于具体描述图5所示的通过开关组的图。

图7和图8是用于描述根据本公开的第一实施例的操作方法的图。

图9和图10是用于描述根据本公开的第二实施例的操作方法的图。

图11和图12是用于描述根据本公开的第三实施例的操作方法的图。

图13是用于具体描述根据本公开的另一实施例的行解码器的图。

图14是用于具体描述图13所示的通过开关组的图。

图15是用于描述包括本公开的存储器设备的存储器系统的图。

图16是用于描述包括本公开的存储器设备的另一存储器系统的图。

具体实施方式

本公开的一个实施例可以提供一种能够抑制编程操作期间的错误发生的存储器设备及其操作方法。

本技术可以通过抑制编程操作期间的错误发生,来改善经编程的存储器块的读取操作的可靠性。

图1是用于描述根据本公开的一个实施例的存储器设备的图。

参考图1,存储器设备1100可以包括:其中存储有数据的存储器单元阵列110;执行编程、读取和擦除操作的外围电路120至160;以及控制外围电路的逻辑电路170。外围电路120至160可以包括电压生成器120、行解码器130、页缓冲器组140、列解码器150和输入/输出电路160。

存储器单元阵列110可以包括多个存储器块,并且存储器块中的每个可以包括多个存储器单元。存储器块可以通过第一局部线LL1至第i局部线LLi连接到行解码器130,并且可以通过位线BL连接到页缓冲器组140。在一个实施例中,i可以是大于1的整数。

电压生成器120可以响应于操作码Cop而生成编程、读取或擦除操作所需要的操作电压。例如,电压生成器120可以生成包括编程电压、读取电压、擦除电压、通过电压、关断电压等的操作电压,并且可以根据设置时间来调节操作电压的输出时间。电压生成器120可以通过全局线GL将操作电压传送到行解码器130。

行解码器130可以响应于行地址ADDR#而选择存储器块,并且可以将通过全局线GL接收的操作电压传送到与所选择存储器块连接的局部线(LL1至LLi中的任何一个)。第一局部线LL1至第i局部线LLi中的每个可以包括多个字线、漏极选择线和源极选择线。

在编程操作期间,页缓冲器组140可以临时存储从外部接收的数据,并且可以临时存储在验证或读取操作期间从存储器单元感测的数据。页缓冲器组140可以响应于页缓冲器信号PBSIG而临时存储数据或对位线预充电,并且可以感测位线的电压或电流。

列解码器150可以响应于列地址ADDC而在输入/输出电路160与页缓冲器组140之间传输数据。

输入/输出电路160可以通过输入/输出线IO从外部设备(例如,控制器)接收命令CMD和地址ADD,并且输入或输出数据。在编程操作期间,输入/输出电路160可以将通过输入/输出线IO输入的命令CMD和地址ADD传送到逻辑电路170,并且将数据传送到页缓冲器组140。在读取操作期间,输入/输出电路160可以向外部设备输出从页缓冲器组140读取的数据。

逻辑电路170可以由能够响应于命令CMD和地址ADD而控制外围电路的软件和硬件来配置。逻辑电路170可以响应于命令CMD和地址ADD而输出操作码Cop、页缓冲器信号PBSIG、行地址ADDR#和列地址ADDC。

图2是用于描述图1的存储器单元阵列的图。

参考图2,存储器单元阵列110可以包括第一存储器块BLK1至第i存储器块BLKi。在单平面结构中,第一存储器块BLK1至第i存储器块BLKi可以配置存储器单元阵列110。在多平面结构中,第一存储器块BLK1至第i存储器块BLKi可以配置一个平面,并且存储器单元阵列110可以包括多个平面。第一存储器块BLK1至第i存储器块BLKi可以被配置为彼此完全相同,并且在第一存储器块BLK1至第i存储器块BLKi之中,第i存储器块BLKi作为一个实施例被具体描述如下。

图3是用于具体描述根据本公开的一个实施例的第i存储器块的图。

参考图3,第i存储器块BLKi可以包括连接在位线BL1至BLm与源极线SL之间的多个存储器串ST11至ST1m和ST21至ST2m。存储器串ST11至ST1m和ST21至ST2m中的每个可以沿Z方向延伸。这里,Z方向可以是存储器单元MC堆叠的方向,并且可以是垂直于基板的方向。m是等于或大于2的整数。

存储器串ST11至ST1m和ST21至ST2m中的每个可以包括串联连接的源极选择晶体管SST、存储器单元MC和漏极选择晶体管DST。

存储器串之一(ST11至ST1m和ST21至ST2m中的任何一个)中包括的源极选择晶体管SST可以串联连接在存储器单元MC与源极线SL之间。源极选择晶体管SST的栅极电极可以连接到源极选择线SSL。另外,位于相同层上的源极选择晶体管SST可以连接到相同的源极选择线SSL。

存储器串之一(ST11至ST1m和ST21至ST2m中的任何一个)中包括的存储器单元MC可以串联连接在至少一个源极选择晶体管SST与至少一个漏极选择晶体管DST之间。存储器单元MC的栅极电极可以连接到字线WL。驱动所需要的操作电压(编程电压、通过电压、读取电压等)可以被施加到字线WL中的每个字线WL。连接到相同字线WL的一组存储器单元成为页PG。存储器单元MC可以以页PG为单位进行编程或读取。

存储器串之一(ST11至ST1m和ST21至ST2m中的任何一个)中包括的漏极选择晶体管DST可以串联连接在位线BL1至BLm与存储器单元MC之间。漏极选择晶体管DST的栅极电极连接到漏极选择线DSL。布置在相同行(X方向)中的存储器串ST11至ST1m或ST21至ST2m中包括的漏极选择晶体管DST之中、形成在相同层上的漏极选择晶体管DST可以连接到相同的漏极选择线DSL。另外,布置在不同行(X方向)中的漏极选择晶体管DST可以连接到不同的漏极选择线DSL。

与第i存储器块BLKi连接的源极选择线SSL、字线WL和漏极选择线DSL可以被包括在第i局部线LLi中。

第十一串ST11中包括的一些存储器单元31的结构被具体描述如下。

图4是用于具体描述存储器单元的结构的图。

参考图4,存储器块可以以堆叠结构形成,该堆叠结构包括在垂直于基板的方向Z上堆叠的多个字线WL和层间绝缘层IT、以及竖直穿过字线WL和层间绝缘层IT的插塞PLG。字线WL和层间绝缘层IT可以交替地堆叠。字线WL可以由导电材料形成,并且层间绝缘层IT可以由绝缘材料形成。

插塞PLG可以形成在竖直穿过字线WL和层间绝缘层IT的竖直孔VH中。插塞PLG可以包括间隙填充层GF、沟道层CL和存储器层MR。间隙填充层GF可以形成为从竖直孔VH的中央在竖直方向Z上延伸的柱形形状。沟道层CL可以形成为围绕间隙填充层GF的侧壁的柱形形状,并且存储器层MR可以形成为围绕沟道层CL的侧壁的柱形形状。间隙填充层GF可以由绝缘材料形成,并且沟道层CL可以由多晶硅形成。替代地,沟道层CL可以形成为柱形形状,以代替在竖直孔VH的中央的间隙填充层GF。在下面描述的本实施例中,以其中间隙填充层GF形成在竖直孔VH的中央的插塞PLG为例进行描述。

存储器层MR可以包括围绕沟道层CL的侧壁的柱形隧穿绝缘层TO、围绕隧穿绝缘层TO的侧壁的柱形电荷俘获层TR、以及围绕电荷俘获层TR的侧壁的柱形阻止层BK。隧穿绝缘层TO可以由氧化物层形成,该氧化物层是绝缘材料,电荷俘获层TR可以由氮化物层形成,并且阻止层BK可以由氧化物层形成,该氧化物层是绝缘材料。隧穿绝缘层TO是其中电子在沟道层CL与电荷俘获层TR之间隧穿的层,电荷俘获层TR是俘获电子的层,并且阻止层BK是阻止被俘获在电荷俘获层TR中的电子移动到字线WL的层。

存储器单元可以与字线WL相邻地形成在插塞PLG中,并且存储器单元的宽度可以与插塞PLG的宽度相同。例如,由于插塞PLG形成在竖直穿过字线WL和层间绝缘层IT的竖直孔VH内部,所以插塞PLG的宽度根据竖直孔VH的宽度来确定。

当向字线WL施加正电压时,可以在存储器单元中所包括的沟道层CL中形成沟道。例如,当向字线WL施加高于存储器单元的阈值电压的正电压时,可以在存储器单元中包括的沟道层CL中形成沟道,并且从而可以使存储器单元导通。沟道层CL的电压成为沟道电压,并且沟道电压可以根据存储器单元的阈值电压或施加到字线WL的电压而改变。

图5是用于具体描述根据本公开的一个实施例的行解码器的图。

参考图5,行解码器130可以包括与第一存储器块BLK1至第i存储器块BLKi连接的第一通过开关组PSG1至第i通过开关组PSGi、以及选择性地启动第一通过开关组PSG1至第i通过开关组PSGi的第一解码器DEC1至第i解码器DECi。例如,第i解码器DECi和第i通过开关组PSGi可以形成一对,并且根据第i行地址ADDRi来选择或不选择第i存储器块BLKi。第一通过开关组PSG1至第i通过开关组PSGi可以分别连接在全局线GL与第一局部线LL1至第i局部线LLi之间。也就是说,从电压生成器120输出的操作电压可以通过全局线GL被共同传送到第一通过开关组PSG1至第i通过开关组PSGi。第一通过开关组PSG1至第i通过开关组PSGi可以通过块选择线BLKSEL1至BLKSELi连接到第一解码器DEC1至第i解码器DECi。

在编程操作期间,当电压生成器120将用于编程操作的操作电压Vop输出到全局线GL时,操作电压Vop可以被共同地传送到第一通过开关组PSG1至第i通过开关组PSGi。当选择第一存储器块BLK1时,第一解码器DEC1可以响应于第一行地址ADDR1而向第一块选择线BLKSEL1输出正电压的块选择电压。当通过第一块选择线BLKSEL1施加块选择电压时,第一通过开关组PSG1可以将全局线GL和第一局部线LL1彼此连接。此时,由于第二解码器DEC2至第i解码器DECi根据第二地址ADDR2至第i地址ADDRi被停用,因此第二通过开关组PSG2至第i通过开关组PSGi将全局线GL和第二局部线LL2至第i局部线LLi彼此阻断。因此,第二局部线LL2至第i局部线LLi可以被浮置。由于操作电压Vop被施加到第一局部线LL1,所以可以执行对第一存储器块BLK1的编程操作。

当通过第一块选择线BLKSEL1施加关断电压时,第一通过开关组PSG1可以将全局线GL和第一局部线LL1彼此阻断。

图6是用于具体描述图5所示的通过开关组的图。

参考图6,第i通过开关组PSGi可以包括第一通过开关PS1至第n+2通过开关PSn+2。第一通过开关PS1至第n+2通过开关PSn+2可以连接在全局线GL与第i局部线LLi之间,并且第一通过开关PS1至第n+2通过开关PSn+2的栅极可以共同连接到第i块选择线BLKSELi。例如,第一通过开关PS1可以连接在全局源极选择线GSSL与源极选择线SSL之间,第二通过开关PS2至第n+1通过开关PSn+1可以连接在第一全局字线GWL1至第n全局字线GWLn与第一字线WL1至第n字线WLn之间,并且第n+2通过开关PSn+2可以连接在全局漏极选择线GDSL与漏极选择线DSL之间。

当将正电压的块选择电压施加到第i块选择线BLKSELi时,第一通过开关PS1至第n+2通过开关PSn+2可以同时导通。当第一通过开关PS1至第n+2通过开关PSn+2全部都导通时,全局线GL连接到第i局部线LLi。此时,施加到全局源极选择线GSSL、第一全局字线GWL1至第n全局字线GWLn、和全局漏极选择线GDSL的操作电压Vop可以被传送到源极选择线SSL、第一字线WL1至第n字线WLn、和漏极选择线DSL。

当关断电压被施加到第i块选择线BLKSELi时,第一通过开关PS1至第n+2通过开关PSn+2可以同时关断。当第一通过开关PS1至第n+2通过开关PSn+2全部都关断时,第i通过开关组PSG1可以将全局线GL和第i局部线LLi彼此阻断。因此,操作电压Vop被施加到全局源极选择线GSSL、第一全局字线GWL1至第n全局字线GWLn、和全局漏极选择线GDSL,但是源极选择线SSL、第一字线WL1至第n字线WLn、和漏极选择线DSL可以被浮置。在一个实施例中,当通过开关关断时,阻止施加到全局源极选择线GSSL、第一全局字线GWL1至第n全局字线GWLn、和全局漏极选择线GDSL的操作电压Vop被传送到源极选择线SSL、第一字线WL1至第n字线WLn、和漏极选择线DSL。

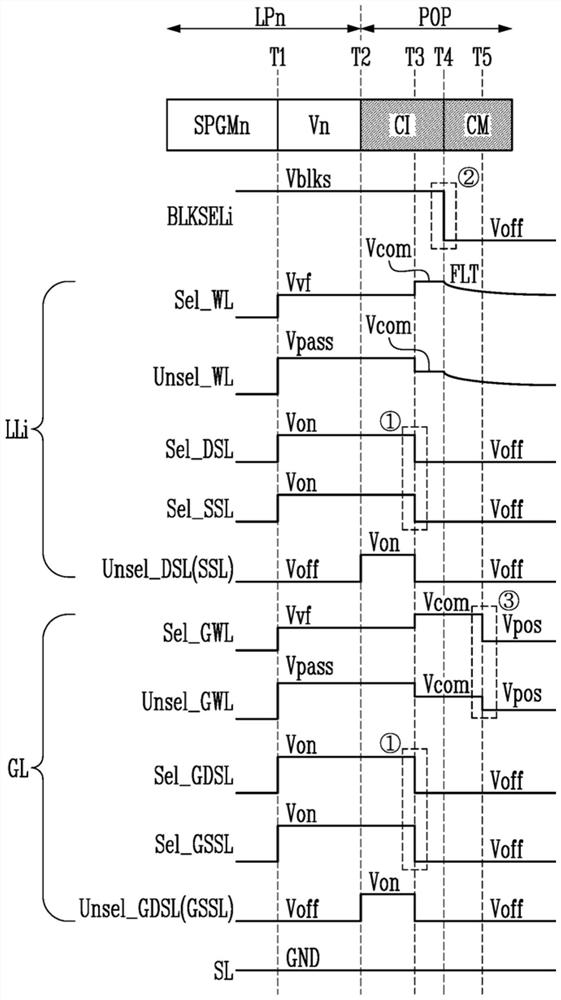

图7和图8是用于描述根据本公开的第一实施例的操作方法的图。

图7是用于简要描述根据第一实施例的第i存储器块的编程操作方法的图,并且图8是用于具体描述根据第一实施例的第i存储器块的编程操作方法的图。

参考图7,可以执行对所选择存储器单元的编程操作,直到所选择存储器单元的阈值电压增加到目标电压。例如,可以通过将编程电压施加到与所选择存储器单元连接的所选择字线,来执行编程操作。可以通过逐步增加向所选择字线施加的编程电压的增量步进脉冲编程(ISPP)方法,来执行编程操作。在ISPP方法的编程操作中,可以执行第一循环LP1至第n循环LPn(n是正整数)。第一循环LP1至第n循环LPn中的每个可以包括使用编程电压增加存储器单元的阈值电压的子编程操作、以及确定存储器单元的阈值电压是否增加到目标电压的验证操作。例如,在第一循环LP1中,可以执行使用第一编程电压的第一子编程操作SPGM1,并且在执行第一子编程操作SPGM1之后,可以执行第一验证操作V1。当所选择存储器单元的阈值电压达到目标电压时,第一验证操作V1通过,并且可以结束对所选择存储器单元的编程操作。当检测到所选择存储器单元中的至少一个所选择存储器单元的阈值电压未达到目标电压时,可以将第一验证操作V1确定为失败,并且可以执行第二循环LP2。在第二循环LP2中,可以执行第二子编程操作SPGM2,第二子编程操作SPGM2使用比在第一子编程操作SPGM1中使用的编程电压高的编程电压,并且可以执行第二验证操作V2,第二验证操作V2用于确定对其执行第二子编程操作SPGM2的存储器单元的阈值电压是否增加到目标电压。在这样的方法中,可以执行第一循环LP1至第n循环LPn,直到所选择存储器单元的阈值电压增加到目标电压。也就是说,第n循环LPn可以包括第n子编程操作SPGMn和第n验证操作Vn,并且当第n验证操作Vn通过时,可以结束对所选择存储器单元的编程操作。

当所选择页中包括的所选择存储器单元的编程操作完成时,可以针对所选择页的下一操作继续执行后操作POP。

例如,在第一实施例的后操作POP中,可以执行沟道初始化操作CI和沟道保持操作CM。可以执行沟道初始化操作CI和沟道保持操作CM以防止如下现象:由于根据当被施加正电压的字线在编程操作中放电时字线的电压降进行耦合,沟道的电压低于参考电平。这里,参考电平可以是0V。根据第一实施例的后操作POP被具体描述如下。

参考图8,在时段T1至T2中,可以执行第n循环LPn的第n验证操作Vn。当第n验证操作Vn通过时,可以从时间点T2开始执行后操作POP。

在执行编程操作的同时,可以将具有正电压的块选择电压Vblks施加到第i块选择线BLKSELi。因此,施加到全局线GL的电压可以被传送到第i局部线LLi。例如,在时间点T1,当验证电压Vvf被施加到全局所选择字线Sel_GWL时,验证电压Vvf可以被传送到所选择字线Sel_WL,并且当通过电压Vpass被施加到全局未选择字线Unsel_GWL时,通过电压Vpass可以被传送到未选择字线Unsel_WL。当导通电压Von被施加到所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL时,导通电压Von可以被传送到所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。

关断电压Voff可以被施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL,并且因此,关断电压Voff还可以被施加到未选择漏极选择线Unsel_DSL和未选择源极选择线Unsel_SSL。接地电压GND可以被施加到源极线SL。

在时间点T2,当第n验证操作Vn通过时,由于所选择页的编程操作完成,因此可以从时间点T2开始执行后操作POP。在图8所示的第一实施例中,后操作POP可以包括沟道初始化操作CI和沟道保持操作CM。沟道初始化操作CI可以在时段T2至T4中执行。沟道初始化操作CI可以包括将导通电压Von施加到全局选择线Sel_GDSL、Sel_GSSL、Unsel_GDSL和Unsel_GSSL(T2至T3),将关断电压Voff施加到选择线Sel_GDSL、Sel_GSSL、Unsel_GDSL和Unsel_GSSL(①),浮置局部线(②),以及使全局字线放电(③)。步骤①、②和③可以顺序地执行。

沟道初始化操作CI被具体描述如下。

在时间点T2,可以将导通电压Von施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL。也就是说,在时段T2至T3中,由于导通电压Von被施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL、以及所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL,所以还可以将导通电压Von传送到未选择漏极选择线Unsel_DSL和未选择源极选择线Unsel_SSL、以及所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。因而,可以初始化第i存储器块BLKi中包括的所有串的沟道。

在时间点T3,可以将关断电压Voff施加到所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL、以及未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Sel_GSSL(①)。另外,在时间点T3,可以将具有正电压电平的补偿电压Vcom施加到全局字线Sel_GWL和Unsel_GWL。补偿电压Vcom可以具有高于验证电压Vvf并且低于通过电压Vpass的电平。由于在时段T3至T4中将块选择电压Vblks施加到第i块选择线BLKSELi,所以可以将关断电压Voff传送到第i局部线LLi中包括的所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。当关断电压Voff被施加到所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL时,包括所选择存储器单元的串的沟道可以被浮置。另外,补偿电压Vcom可以被传送到第i局部线LLi中包括的所选择字线Sel_WL和未选择字线Unsel_WL。

沟道保持操作CM被具体描述如下。在时间点T4,可以将关断电压Voff施加到第i块选择线BLKSELi,以浮置第i局部线LLi(②)。关断电压Voff可以是接地电压GND。当关断电压Voff被施加到第i块选择线BLKSELi时,由于连接在全局线GL与第i局部线LLi之间的图6的所有通过开关PS1至PSn+2关断,所以全局线GL与第i局部线LLi之间的连接可以被阻断。因而,所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL可以在其中施加关断电压Voff的状态中被浮置,并且所选择字线Sel_WL和未选择字线Unsel_WL可以在其中施加补偿电压Vcom的状态中被浮置FLT。

在时间点T5,可以将全局字线Sel_GWL和Unsel_GWL的电压调节为低。例如,在时间点T5,可以将施加到全局字线Sel_GWL和Unsel_GWL的电压降低到具有比当执行沟道初始化操作CI时施加到全局字线Sel_GWL和Unsel_GWL的电压低的电平。例如,在时间点T5,全局字线Sel_GWL和Unsel_GWL的电压可以被降低到接地电压GND,或者被降低到高于接地电压GND并且低于验证电压Vvf的正电压Vpos。此时,由于图6的所有通过开关PS1至PSn+2关断,所以第i局部线LLi中包括的字线Sel_WL和Unsel_WL可以保持在浮置FLT状态。因此,在第i局部线LLi中包括的字线Sel_WL和Unsel_WL所连接到的存储器块中,可以防止串的沟道的电压低于参考电平的现象。也就是说,当串的沟道的电压低于参考电平时,当执行接下来要执行的读取操作时,存储器单元的数据的可靠性可能降低。因此,在一个实施例中,沟道的电压可以不降低到低于参考电平,以改善存储器设备的可靠性。因此,优选的是,在时间点T5将施加到全局字线Sel_GWL和Unsel_GWL的电压降低到高于接地电压GND的正电压Vpos。由于在图6的通过开关PS1至PSn+2中可能发生泄漏,因此为了有效地防止第i局部线LLi中包括的字线Sel_WL和Unsel_WL的电压降低,图1的逻辑电路170可以控制图1的电压生成器120,使得正电压Vpos被施加到全局字线Sel_GWL和Unsel_GWL。

图9和图10是用于描述根据本公开的第二实施例的操作方法的图。

图9是用于简要描述根据第二实施例的操作方法的图,并且图10是用于具体描述根据第二实施例的操作方法的图。

参考图9,对所选择存储器单元的编程操作可以与参考图7描述的方法完全相同地执行,并且在后操作POP中,可以附加地执行第n+1子编程操作SPGMn+1。例如,当在第n循环LPn中执行的第n验证操作Vn通过时,在执行第n+1子编程操作SPGMn+1之后,可以执行沟道初始化操作CI和沟道保持操作CM。可以执行第n+1子编程操作SPGMn+1,以通过在选择页的编程操作完成之后附加地将编程电压施加到所选择字线Sel_WL,来使存储器单元的阈值电压的分布宽度变窄。

参考图10,在时段T1至T2中,可以执行第n循环LPn的第n验证操作Vn。当第n验证操作Vn通过时,可以从时间点T2开始执行后操作POP。

在执行编程操作的同时,可以将具有正电压的块选择电压Vblks施加到第i块选择线BLKSELi。因此,施加到全局线GL的电压可以被传送到第i局部线LLi。例如,在时间点T1,当验证电压Vvf被施加到全局所选择字线Sel_GWL时,验证电压Vvf可以被传送到所选择字线Sel_WL,并且当通过电压Vpass被施加到全局未选择字线Unsel_GWL时,通过电压Vpass可以被传送到未选择字线Unsel_WL。当导通电压Von被施加到所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL时,导通电压Von可以被传送到所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。

关断电压Voff可以被施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL,并且因此,关断电压Voff还可以被施加到未选择漏极选择线Unsel_DSL和未选择源极选择线Unsel_SSL。接地电压GND可以被施加到源极线SL。

在时间点T2,当第n验证操作Vn通过时,由于所选择页的编程操作完成,因此可以从时间点T2开始执行后操作POP。在图10所示的第二实施例中,后操作POP可以包括第n+1子编程操作SPGMn+1和沟道初始化操作CI。

在时间点T2,可以使全局线GL和第i局部线LLi两者放电,并且然后可以将编程电压Vpgm施加到所选择全局字线Sel_GWL。编程电压Vpgm可以具有与在第n子编程操作SPGMn中使用的编程电压相同的电平,或者可以具有比在第n子编程操作SPGMn中使用的编程电压低的电平。当编程电压Vpgm被施加到所选择全局字线Sel_GWL时,通过电压Vpass可以被施加到未选择全局字线Unsel_GWL,并且导通电压Von可以被施加到所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL。此时,关断电压Voff可以被施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL。

由于块选择电压Vblks被施加到第i块选择线BLKSELi,所以施加到全局线GL的电压可以被传送到第i局部线LLi。在预定时间期间将编程电压Vpgm施加到所选择字线Sel_WL之后,可以执行沟道初始化操作CI。

沟道初始化操作CI可以包括将导通电压Von施加到全局选择线Sel_GDSL、Sel_GSSL、Unsel_GDSL和Unsel_GSSL(T2至T3),将关断电压Voff施加到选择线Sel_GDSL、Sel_GSSL、Unsel_GDSL和Unsel_GSSL(①),浮置局部线(②),以及使全局字线放电(③)。步骤①、②和③可以顺序地执行。

沟道初始化操作CI被具体描述如下。

在时间点T3,可以将低于编程电压Vpgm的补偿电压Vcom施加到所选择全局字线Sel_GWL。补偿电压Vcom可以具有低于通过电压Vpass并且高于接地电压GND的电平。因而,具有彼此相同的电平的电压可以被施加到所选择字线Sel_WL和未选择字线Unsel_WL。

在预定时间期间将补偿电压Vcom施加到所选择字线Sel_WL之后,可以将导通电压Von施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL。也就是说,由于导通电压Von被施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL、以及所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL,所以导通电压Von还可以被传送到未选择漏极选择线Unsel_DSL和未选择源极选择线Unsel_SSL、以及所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。因而,可以初始化第i存储器块BLKi中包括的所有串的沟道。

在时间点T4,可以继续将关断电压Voff施加到所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL、以及未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL(①)。另外,在时间点T4,可以将具有正电压电平的补偿电压Vcom施加到全局字线Sel_GWL和Unsel_GWL。补偿电压Vcom可以具有高于验证电压Vvf并且低于通过电压Vpass的电平。由于在时段T4至T5中将块选择电压Vblks施加到第i块选择线BLKSELi,所以可以将关断电压Voff传送到第i局部线LLi中包括的所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。当关断电压Voff被施加到所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL时,包括所选择存储器单元的串的沟道可以被浮置。另外,补偿电压Vcom可以被传送到第i局部线LLi中包括的所选择字线Sel_WL和未选择字线Unsel_WL。

沟道保持操作CM被具体描述如下。

在时间点T5,可以将关断电压Voff施加到第i块选择线BLKSELi,以浮置第i局部线LLi(②)。关断电压Voff可以是接地电压GND。当关断电压Voff被施加到第i块选择线BLKSELi时,由于连接在全局线GL与第i局部线LLi之间的图6的所有通过开关PS1至PSn+2关断,所以全局线GL与第i局部线LLi之间的连接可以被阻断。因而,所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL可以在其中施加关断电压Voff的状态中被浮置,并且所选择字线Sel_WL和未选择字线Unsel_WL可以在其中施加补偿电压Vcom的状态中被浮置FLT。

在时间点T6,可以将全局字线Sel_GWL和Unsel_GWL的电压调节为低。例如,在时间点T6,可以将施加到全局字线Sel_GWL和Unsel_GWL的电压降低到具有比当执行沟道初始化操作CI时施加到全局字线Sel_GWL和Unsel_GWL的电压低的电平。例如,在时间点T6,全局字线Sel_GWL和Unsel_GWL的电压可以被降低到接地电压GND,或者被降低到高于接地电压GND并且低于验证电压Vvf的正电压Vpos。此时,由于图6的所有通过开关PS1至PSn+2关断,所以第i局部线LLi中包括的字线Sel_WL和Unsel_WL可以保持在浮置FLT状态。因此,在第i局部线LLi中包括的字线Sel_WL和Unsel_WL所连接到的存储器块中,可以防止串的沟道的电压低于参考电平的现象。也就是说,当串的沟道的电压低于参考电平时,当执行接下来要执行的读取操作时,存储器单元的数据的可靠性可能降低。因此,在本实施例中,沟道的电压可以不降低到低于参考电平,以改善存储器设备的可靠性。因此,优选的是,在时间点T6将施加到全局字线Sel_GWL和Unsel_GWL的电压降低到高于接地电压GND的正电压Vpos。由于在图6的通过开关PS1至PSn+2中可能发生泄漏,因此为了有效地防止第i局部线LLi中包括的字线Sel_WL和Unsel_WL的电压降低,图1的逻辑电路170可以控制图1的电压生成器120,使得正电压Vpos被施加到全局字线Sel_GWL和Unsel_GWL。

图11和图12是用于描述根据本公开的第三实施例的操作方法的图。

图11是用于简要描述根据第三实施例的操作方法的图,并且图12是用于具体描述根据第三实施例的操作方法的图。

参考图11,对所选择存储器单元的编程操作可以与参考图7描述的方法完全相同地执行,并且在后操作POP中,可以附加地执行第n+1子编程操作SPGMn+1和沟道补偿操作CP。例如,当在第n循环LPn中执行的第n验证操作Vn通过时,第n+1子编程操作SPGMn+1、沟道初始化操作CI和沟道保持操作CM可以顺序执行。可以执行第n+1子编程操作SPGMn+1,以通过在选择页的编程操作完成之后附加地将编程电压施加到所选择字线Sel_WL,来使存储器单元的阈值电压的分布宽度变窄。可以执行沟道初始化操作CI和沟道保持操作CM,以防止如下现象:由于根据当被施加正电压的字线在编程操作中放电时字线的电压降进行耦合,所以沟道的电压低于参考电平。在图11所示的第三实施例中,与图9所示的沟道初始化操作CI不同,可以包括使线放电并且顺序地减小施加到字线的电压的操作。

参考图12,在时段T1至T2中,可以执行第n循环LPn的第n验证操作Vn。当第n验证操作Vn通过时,可以从时间点T2开始执行后操作POP。

在执行编程操作的同时,可以将具有正电压的块选择电压Vblks施加到第i块选择线BLKSELi。因此,施加到全局线GL的电压可以被传送到第i局部线LLi。例如,在时间点T1,当验证电压Vvf被施加到全局所选择字线Sel_GWL时,验证电压Vvf可以被传送到所选择字线Sel_WL,并且当通过电压Vpass被施加到全局未选择字线Unsel_GWL时,通过电压Vpass可以被传送到未选择字线Unsel_WL。当导通电压Von被施加到所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL时,导通电压Von可以被传送到所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。

关断电压Voff可以被施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL,并且因此,关断电压Voff还可以被施加到未选择漏极选择线Unsel_DSL和未选择源极选择线Unsel_SSL。接地电压GND可以被施加到源极线SL。

在时间点T2,当第n验证操作Vn通过时,由于所选择页的编程操作完成,因此可以从时间点T2开始执行后操作POP。在图12所示的第三实施例中,后操作POP可以包括第n+1子编程操作SPGMn+1、沟道初始化操作CI和沟道保持操作CM。

在时间点T2,可以使全局线GL和第i局部线LLi两者放电,并且然后可以将编程电压Vpgm施加到所选择全局字线Sel_GWL。编程电压Vpgm可以具有与在第n子编程操作SPGMn中使用的编程电压相同的电平,或者可以具有比在第n子编程操作SPGMn中使用的编程电压低的电平。当编程电压Vpgm被施加到所选择全局字线Sel_GWL时,通过电压Vpass可以被施加到未选择全局字线Unsel_GWL,并且导通电压Von可以被施加到所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL。此时,关断电压Voff可以被施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL。

由于块选择电压Vblks被施加到第i块选择线BLKSELi,所以施加到全局线GL的电压可以被传送到第i局部线LLi。在预定时间期间将编程电压Vpgm施加到所选择字线Sel_WL之后,可以在时段T3至T5中执行沟道补偿操作CP。

在时间点T3,在全局线GL和第i局部线LLi两者放电之后,在时间点T4,可以将补偿电压Vcom施加到全局字线Sel_GWL和Unsel_GWL、以及全局漏极选择线Sel_GDSL和全局源极选择线Sel_GSSL。补偿电压Vcom可以被设置为低于通过电压Vpass并且高于验证电压Vvf的电压。由于块选择电压Vblks被施加到第i块选择线BLKSELi,所以补偿电压Vcom可以被传送到所选择字线Sel_WL、未选择字线Unsel_WL、以及所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。在时间点T5开始之前,可以将导通电压Von施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL。也就是说,由于导通电压Von被施加到未选择全局漏极选择线Unsel_GDSL和未选择全局源极选择线Unsel_GSSL、以及所选择全局漏极选择线Sel_GDSL和所选择全局源极选择线Sel_GSSL,所以导通电压Von还可以被传送到未选择漏极选择线Unsel_DSL和未选择源极选择线Sel_SSL、以及所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。因而,可以初始化第i存储器块BLKi中包括的所有串的沟道。

在时间点T5,可以将关断电压Voff施加到全局漏极选择线Sel_GDSL和全局源极选择线Sel_GSSL(①)。由于块选择电压Vblks被施加到第i块选择线BLKSELi,所以关断电压Voff可以被传送到第i局部线LLi中包括的所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL。当关断电压Voff被施加到所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL时,包括所选择存储器单元的串的沟道可以被浮置。

在时段T5至T6中,可以逐步降低全局字线Sel_GWL和Unsel_GWL的电压。例如,当将补偿电压Vcom施加到全局字线Sel_GWL和Unsel_GWL直到时间点T5为止时,可以在时段T5至T6中逐步将低于补偿电压Vcom的电压施加到全局字线Sel_GWL和Unsel_GWL。当施加到全局字线Sel_GWL和Unsel_GWL的电压逐步降低时,可以将逐步降低的电压顺序地施加到第i局部线LLi中包括的所选择字线Sel_WL和未选择字线Unsel_WL。在时段T5至T6中,全局字线Sel_GWL和Unsel_GWL的电压可以被降低到第一正电压Vpos1,该第一正电压Vpos1具有高于接地电压GND的电平。

沟道保持操作CM被具体描述如下。

在时间点T6,可以将关断电压Voff施加到第i块选择线BLKSELi,以浮置第i局部线LLi(②)。关断电压Voff可以是接地电压GND。当关断电压Voff被施加到第i块选择线BLKSELi时,由于连接在全局线GL与第i局部线LLi之间的图6的所有通过开关PS1至PSn+2关断,所以全局线GL与第i局部线LLi之间的连接可以被阻断。因而,所选择漏极选择线Sel_DSL和所选择源极选择线Sel_SSL可以在其中施加关断电压Voff的状态中被浮置,并且所选择字线Sel_WL和未选择字线Unsel_WL可以在其中施加第一正电压Vpos1的状态中被浮置FLT。

在时间点T7,可以将全局字线Sel_GWL和Unsel_GWL从第一正电压Vpos1降低到第二正电压Vpos2(③)。第二正电压Vpos2可以被设置为在第一正电压Vpos1与接地电压GND之间的电平。例如,在时间点T7,可以将全局字线Sel_GWL和Unsel_GWL的电压降低到接地电压GND,或者降低到第二正电压Vpos2,该第二正电压Vpos2高于接地电压GND并且低于第一正电压Vpos1。此时,由于图6的所有通过开关PS1至PSn+2关断,所以第i局部线LLi中包括的字线Sel_WL和Unsel_WL可以保持在浮置FLT状态。因此,在第i局部线LLi中包括的字线Sel_WL和Unsel_WL所连接到的存储器块中,可以防止串的沟道的电压低于参考电平的现象。也就是说,当串的沟道的电压低于参考电平时,当执行接下来要执行的读取操作时,存储器单元的数据的可靠性可能降低。因此,在本实施例中,沟道的电压可以不降低到低于参考电平,以改善存储器设备的可靠性。因此,优选的是,在时间点T7将施加到全局字线Sel_GWL和Unsel_GWL的电压降低到高于接地电压GND的第二正电压Vpos2。由于在图6的通过开关PS1至PSn+2中可能发生泄漏,因此为了有效地防止第i局部线LLi中包括的字线Sel_WL和Unsel_WL的电压降低,图1的逻辑电路170可以控制图1的电压生成器120,使得第二正电压Vpos2被施加到全局字线Sel_GWL和Unsel_GWL。因此,在第i局部线LLi中包括的字线Sel_WL和Unsel_WL所连接到的存储器块中,可以防止串的沟道的电压低于参考电平的现象。也就是说,当串的沟道的电压低于参考电平时,当执行接下来要执行的读取操作时,存储器单元的数据的可靠性可能降低。因此,在本实施例中,沟道的电压可以不降低到低于参考电平,以改善存储器设备的可靠性。

图13是用于具体描述根据本公开的另一实施例的行解码器的图。

参考图13,行解码器130a可以包括多个解码器DEC1至DEC(i/2)和多个通过开关组PSG1至PSGi,一个解码器可以被配置为同时导通或关断两个或更多通过开关组。为此,还可以包括多个电压生成器。所包括的电压生成器的数目可以与由一个解码器操作的通过开关组的数目相同。例如,当第一通过开关组PSG1和第二通过开关组PSG2共同连接到第一解码器DEC1时,由于一个解码器控制这两个通过开关组,所以电压生成器可以包括被配置为向相应的第一通过开关组PSG1和第二通过开关组PSG2输出电压的第一电压生成器120a和第二电压生成器120b。也就是说,第一通过开关组PSG1和第二通过开关组PSG2可以共同连接到第一块选择线BLKSEL1,并且第一解码器DEC1可以响应于第一行地址ADDR1而将块选择电压输出到第一块选择线BLKSEL1。如本文中关于发生事件所使用的词语“同时”和“同时地”是指发生事件在重叠的时间间隔上发生。例如,如果第一发生事件在第一时间间隔内发生,并且第二发生事件在第二时间间隔内同时发生,则第一间隔和第二间隔至少部分地彼此重叠,从而存在第一发生事件和第二发生事件两者都在发生的时间。

第一电压生成器120a可以通过第一全局线1GL连接到第一通过开关组PSG1,并且第二电压生成器120b可以通过第二全局线2GL连接到第二通过开关组PSG2。当第一电压生成器120a和第二电压生成器120b之一被启动时,另一个可以被停用。

作为一个示例,描述了其中选择第一存储器块BLK1的情况。

第一电压生成器120a可以通过第一全局线1GL输出操作电压Vop,并且第二电压生成器120b可以通过第二全局线2GL输出接地电压GND。操作电压Vop被施加到与第一全局线1GL连接的奇数编号的通过开关组PSG1、PSG3、……和PSGi-1。当第一解码器DEC1响应于第一行地址ADDR1而将块选择电压输出到第一块选择线BLKSEL1时,第一通过开关组PSG1和第二通过开关组PSG2中包括的通过开关可以被导通。响应于第二行地址ADDR2至第i/2行地址ADDR(i/2),所有其余的偶数编号的通过开关组PSG2、PSG4、……和PSGi被停用,并且偶数编号的通过开关组PSG2、PSG4、……和PSGi中包括的所有通过开关可以被关断。因此,操作电压Vop可以仅被传送到第一局部线LL1,接地电压GND可以被施加到第二局部线LL2,并且其余的第三局部线LL3至第i局部线LLi可以被浮置FLT。

图14是用于具体描述图13所示的通过开关组的图。

参考图14,第一通过开关组PSG1和第二通过开关组PSG2中的每个中包括的通过开关PS1至PSn+2的所有栅极可以共同连接到第一块选择线BLKSEL1。

第一通过开关组PSG1中包括的第一通过开关PS1至第n+2通过开关PSn+2可以连接在第一全局线1GL与第一局部线LL1之间。例如,第一通过开关组PSG1中包括的第一通过开关PS1可以连接在第一全局线1GL中包括的全局源极选择线GSSL与第一局部线LL1中包括的源极选择线SSL之间。在这种方法中,第二通过开关PS2至第n+1通过开关PSn+1可以连接在第一全局字线GWL1至第n全局字线GWLn与第一字线WL1至第n字线WLn之间,并且第n+2通过开关PSn+2可以连接在全局漏极选择线GDSL与漏极选择线DSL之间。第二通过开关组PSG2中包括的第一通过开关PS1可以连接在第二全局线2GL中包括的全局源极选择线GSSL与第二局部线LL2中包括的源极选择线SSL之间。在这种方法中,第二通过开关PS2至第n+1通过开关PSn+1可以连接在第一全局字线GWL1至第n全局字线GWLn与第一字线WL1至第n字线WLn之间,并且第n+2通过开关PSn+2可以连接在全局漏极选择线GDSL与漏极选择线DSL之间。

当正的块选择电压被施加到第一块选择线BLKSEL1时,由于第一通过开关组PSG1和第二通过开关组PSG2中包括的第一通过开关PS1至第n+2通过开关PSn+2同时导通,所以第二局部线LL2可以连接到第二全局线2GL,并且第一局部线LL1可以连接到第一全局线1GL。由于接地电压GND被施加到第二全局线2GL,所以接地电压GND可以被传送到第二局部线LL2。由于操作电压Vop被施加到第一全局线1GL,所以操作电压Vop可以被传送到第一局部线LL1。

在图13和图14所示的设备中,编程操作和后操作可以根据上述图7至图12所示的实施例来执行。

图15是用于描述包括本公开的存储器设备的存储器系统的图。

参考图15,存储器系统1000可以包括存储器设备1100和控制器1200,在存储器设备1100中存储数据,控制器1200在存储器设备1100与主机2000之间进行通信。

存储器系统1000可以包括多个存储器设备1100,并且每个存储器设备1100可以执行根据上述实施例的编程操作。存储器设备1100可以通过至少一个通道连接到控制器1200。例如,多个存储器设备1100可以连接到一个通道,并且即使在多个通道连接到控制器1200的情况下,多个存储器设备1100也可以连接到每个通道。

控制器1200可以在主机2000与存储器设备1100之间进行通信。控制器1200可以根据主机2000的请求来控制存储器设备1100,或者即便没有来自主机2000的请求,控制器1200也可以执行后台操作以改善存储器系统1000的性能。主机2000可以生成针对各种操作的请求,并且将所生成的请求输出给存储器系统1000。例如,请求可以包括:可以控制编程操作的编程请求、可以控制读取操作的读取请求、可以控制擦除操作的擦除请求等。

主机2000可以通过各种接口与存储器系统1000通信,该各种接口诸如为快速外围组件互连(PCIe)、高级技术附件(ATA)、串行ATA(SATA)、并行ATA(PATA)、串行附接SCSI(SAS)、快速非易失性存储器(NVMe)、通用串行总线(USB)、多媒体卡(MMC)、增强型小盘接口(ESDI)或集成驱动电子器件(IDE)。

图16是用于描述包括本公开的存储器设备的另一存储器系统的图。

参考图16,存储器系统70000可以被实现为存储器卡或智能卡。存储器系统70000可以包括存储器设备1100、控制器1200和卡接口7100。

控制器1200可以控制存储器设备1100与卡接口7100之间的数据交换。根据一个实施例,卡接口7100可以是安全数字(SD)卡接口或多媒体卡(MMC)接口,但不限于此。

存储器设备1100可以执行根据上述实施例的编程操作,并且在读取操作期间,被编程在存储器设备1100中的数据可以在控制器1200的控制下通过卡接口7100被输出。

卡接口7100可以根据主机60000的协议对在主机60000与控制器1200之间的数据交换进行接口连接。根据一个实施例,卡接口7100可以支持通用串行总线(USB)协议和芯片间(IC)-USB协议。这里,卡接口7100可以指代能够支持由主机60000使用的协议的硬件、安装在该硬件中的软件、或信号传输方法。

当存储器系统70000连接到主机60000的主机接口6200时,主机接口6200可以在微处理器(μP)6100的控制下通过卡接口7100和控制器1200执行与存储器设备1100的数据通信。主机60000诸如为PC、平板PC、数字相机、数字音频播放器、移动电话、控制台视频游戏硬件或数字机顶盒。