一种用于数字隔离器的隔离电容互连绑定线断线检测电路

文献发布时间:2023-06-19 18:25:54

技术领域

本发明涉及数字隔离器芯片技术领域,具体涉及一种用于数字隔离器的隔离电容互连绑定线断线检测电路。

背景技术

在现有的数字隔离器的芯片中,大部分采用电容隔离。如图1所示,图中采用一个单向通道为例,一个数字隔离器通道通常包含两颗裸芯,裸芯1为发射器,裸芯2为接收器。隔离电容集成在裸芯1和裸芯2上面,电容隔离器芯片内部通过绑定线将两颗隔离电容串联起来(如C1_P与C2_P串联、C1_N与C2_N串联),而为了提供信号的可靠性和抗干扰能力,通常采用差分的方式传输信号(如C1_P与C1_N组成差分发射端,C2_P与C2_N组成差分接收端)。输入信号IN经TX驱动调制后,经C1_P、C1_N传递到C2_P、C2_N,再经RX放大和解调,从OUT输出。

但是在目前的方案中,如果隔离电容的互连绑定线出现单根线断裂的情形,量产测试无法有效筛选出不良品。如图2所示,发射器10,包含输入施密特触发器101、ON/OFF-KEY调制102、高频振荡器103、发射驱动器等模块104,输入信号经施密特触发器101进行整形,在ON/OFF-KEY调制102被调制为OOK信号,被发射驱动器等模块104分别驱动到两个差分的隔离电容上。接收器20,包含放大与解调器105、驱动器106;从隔离电容接收到的微弱信号被放大与解调器105放大和解调,将信号恢复出来,再经驱动器106驱动后输出。L1和L2为两颗隔离器裸芯的隔离电容的互连绑定线,由于在封装的制造过程中,不可避免的存在一定概率的断线可能性,如果L1和L2同时发生断线,则信号无法正常传递,常规的量产终测便可筛选出来;如果L1和L2其中一根绑定线发生断线,意味着输入信号的幅度减半,由于接收侧具有较高的增益,信号仍可能被正常解调。这样,普通的量产终测方法就无法筛选出该类型不良品,导致在客户端存在一定的风险。

发明内容

有鉴于此,本申请实施例提供一种用于数字隔离器的隔离电容互连绑定线断线检测电路,能够在量产测试时在单侧针对隔离电容互连绑定线断线的问题进行专门测试,以筛选出该类问题的不良品,避免产生不确定性后果。

本申请实施例提供以下技术方案:一种用于数字隔离器的隔离电容互连绑定线断线检测电路,包括:隔离器电路、接口与测试电路;

所述隔离器电路包括发射器和接收器,所述发射器输出端的隔离电容与所述接收器输入端的隔离电容分别通过第一绑定线和第二绑定线连接;

所述发射器包括施密特触发器、调制器、发射驱动器A、发射驱动器B,还包括逻辑与门A和逻辑与门B;输入信号与所述施密特触发器的输入相连,所述施密特触发器的输出与所述调制器的输入相连,所述调制器的输出分别连接所述逻辑与门A和所述逻辑与门B的第一输入端,所述逻辑与门A和所述逻辑与门B的输出端分别连接所述发射驱动器A和所述发射驱动器B的输入端,所述发射驱动器A和所述发射驱动器B的输出端分别连接至所述发射器输出端的隔离电容;

所述接收器包括第一开关管、第二开关管、放大与解调器和驱动器,所述第一开关管和所述第二开关管的漏极分别连接所述接收器输入端的隔离电容,源极分别连接所述放大与解调器的两个输入端,所述放大与解调器的输出端连接所述驱动器;

所述接口与测试电路的输入端连接至时钟信号CLK和数据信号DATA,所述接口与测试电路的输出端分别连接至所述逻辑与门A和所述逻辑与门B的第二输入端,以及所述第一开关管和所述第二开关管的栅极;

当电路为正常工作模式,所述接口与测试电路的所有输出均为信号1;

当电路为测试模式,在所述发射器侧进行测试时,所述接收器侧的所述接口与测试电路的两个输出端均默认输出信号1,对所述发射器侧的所述接口与测试电路的两个输出端分别交替两次输出信号1和信号0,分别选通两根差分绑定线对应的单端通道,从TX输入隔离器的非默认值,进行测试,根据所述接收器的输出是否正常,对所述第一绑定线和第二绑定线的断线情况进行判断;在所述接收器侧进行测试时,所述发射器侧的所述接口与测试电路的两个输出端均默认输出信号1,对所述接收器侧的所述接口与测试电路的两个输出端分别交替两次输出信号1和信号0,分别选通两根差分绑定线对应的单端通道,从TX输入隔离器的非默认值,进行测试,根据所述接收器的输出是否正常,对所述第一绑定线和第二绑定线的断线情况进行判断。

根据一种实施例,所述发射器还包括高频振荡器,所述高频振荡器连接至所述调制器的输入端。

根据一种实施例,所述接收器还包括第一电阻和第二电阻,所述第一电阻和所述第二电阻分别连接至所述放大与解调器的两个输入端。

根据一种实施例,所述第一开关管和所述第二开关管为包括NMOS管、PMOS管、传输门中的任一种。

根据一种实施例,当电路为测试模式时,采用包括IIC或SPI的方式进行通信。

与现有技术相比,本发明实施例的检测电路在量产终测中进入测试模式,可以在发射侧和接收侧分别控制每一路绑定线路径的信号传输,进行信号传输测试,判定出断线的不良品。该不良芯片的可靠性差,抗干扰能力也差,可能带来潜在不确定风险。本发明在设计端进行电路的可测性设计,在量产终测时可轻松筛选不良品,极大的提高了测试筛选效率,提高了终端产品的可靠性,降低了产品的风险。

附图说明

为了更清楚地说明本申请实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

图1为单通道电容型数字隔离器结构示意图;

图2为单通道电容型数字隔离器的电路原理图;

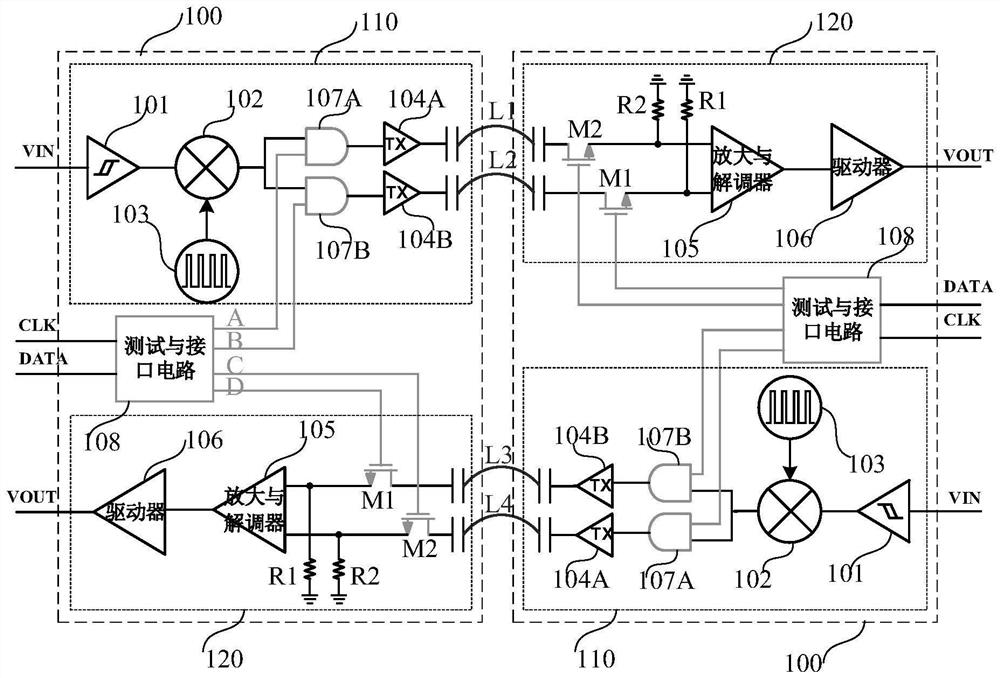

图3为本发明实施例的隔离电容互连绑定线断线检测电路结构示意图;

图4为本发明一种实施例的电容型数字隔离器与其他裸芯合封成隔离接口芯片结构示意图。

具体实施方式

下面结合附图对本申请实施例进行详细描述。

需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本发明,对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明实施例提供了一种用于数字隔离器的隔离电容互连绑定线断线检测电路,包括:隔离器电路、接口与测试电路;

所述隔离器电路包括发射器和接收器,所述发射器输出端的隔离电容与所述接收器输入端的隔离电容分别通过第一绑定线和第二绑定线连接;

所述发射器包括施密特触发器、调制器、高频振荡器、发射驱动器A、发射驱动器B,还包括逻辑与门A和逻辑与门B;输入信号与所述施密特触发器的输入相连,所述施密特触发器的输出与所述高频振荡器均与所述调制器的输入相连,所述调制器的输出分别连接所述逻辑与门A和所述逻辑与门B的第一输入端,所述逻辑与门A和所述逻辑与门B的输出端分别连接所述发射驱动器A和所述发射驱动器B的输入端,所述发射驱动器A和所述发射驱动器B的输出端分别连接至所述发射器输出端的隔离电容;

所述接收器包括第一开关管、第二开关管、放大与解调器和驱动器、第一电阻和第二电阻,所述第一开关管和所述第二开关管的漏极分别连接所述接收器输入端的隔离电容,源极分别连接所述放大与解调器的两个输入端,所述第一电阻和所述第二电阻分别连接至所述放大与解调器的两个输入端,所述放大与解调器的输出端连接所述驱动器;

所述接口与测试电路的输入端连接至时钟信号CLK和数据信号DATA,所述接口与测试电路的输出端分别连接至所述逻辑与门A和所述逻辑与门B的第二输入端,以及所述第一开关管和所述第二开关管的栅极;

当电路为正常工作模式,所述接口与测试电路的所有输出均为信号1;

当电路为测试模式,在所述发射器侧进行测试时,所述接收器侧的所述接口与测试电路的两个输出端均默认输出信号1,对所述发射器侧的所述接口与测试电路的两个输出端分别交替两次输出信号1和信号0,分别选通两根差分绑定线对应的单端通道,从TX输入隔离器的非默认值,进行测试,根据所述接收器的输出是否正常,对所述第一绑定线和第二绑定线的断线情况进行判断;在所述接收器侧进行测试时,所述发射器侧的所述接口与测试电路的两个输出端均默认输出信号1,对所述接收器侧的所述接口与测试电路的两个输出端分别交替两次输出信号1和信号0,分别选通两根差分绑定线对应的单端通道,从TX输入隔离器的非默认值,进行测试,根据所述接收器的输出是否正常,对所述第一绑定线和第二绑定线的断线情况进行判断。如果单侧只有TX或RX,只需单独控制TX或RX,便可在单侧进行隔离电容的互连绑定线断线检测。

本发明提供了能够在量产终测时筛选出该不良芯片的电路,在具体实施时,可适用于多种连接结构,具有更强的通用性。具体一种包含该测试电路的隔离器电路图如图3所示,该图以包含一正一反两个数字隔离器通道为例说明。所述的电容型数字隔离器包含两颗裸芯100,每颗裸芯都包含一个发射器110和一个接收器120,和一个测试电路108。

发射器110,包含施密特触发器101、ON/OFF-KEY调制器102、高频振荡器103、发射驱动器104A和发射驱动器104B、逻辑与门107A和逻辑与门107B,所述输入信号VIN与施密特触发器101的输入相连,施密特触发器101的输出与调制器102的输入相连,高频振荡器103的输出与调制器102的另一个输入相连,调制器102的输出分别连接到逻辑与门107A和逻辑与门107B两个逻辑与门的输入端,逻辑与门107A和逻辑与门107B的另外一个输入与测试与接口电路108的输出相连,逻辑与门107A和逻辑与门107B的输出分别连接到发射驱动器104A和发射驱动器104B两个TX驱动器的输入,发射驱动器104A和发射驱动器104B的输出分别连接到两个隔离电容的输入端。

接收器120,包含第一开关管、第二开关管、第一电阻R1、第一电阻R2、放大与解调器105、驱动器106等电路。本实施例的第一开关管、第二开关管均为NMOS管。所述输入信号来自隔离电容,隔离电容输入差分信号分别与NMOS管M1和NMOS管M2的漏端连接,NMOS管M1和NMOS管M2的源端分别与放大与解调器105的两个输入端连接,NMOS管M1和NMOS管M2的栅极分别连接至测试与接口电路108;第一电阻R1、第一电阻R2分别连接至放大与解调器105的两个输入端。放大与解调器105的输出连接至驱动器106的输入端,驱动器106的输出连接至VOUT。

所述的测试与接口电路108连接至接口管脚DATA和CLK。

所述的两颗裸芯100通过4根封装绑定互连打线L1、L2、L3、L4连接。

如图3所示,所述的输入信号VIN经施密特触发器101进行信号整形,高频振荡器103提供高频载波信号,输入信号与高频载波信号在调制器102被调制为OOK信号,再与测试信号经过逻辑与门107A和逻辑与门107B进行逻辑与,被发射驱动器104A和发射驱动器104B分别驱动到两个差分的隔离电容上。当隔离电容互连绑定线L1和L2均未断时,差分信号传输到RX的输入端,放大与解调器105将输入信号放大解调,输出到驱动器106,驱动外部负载。正常工作情况下,输出端口A=B=1,逻辑与门107A和逻辑与门107B将输入信号直通,测试电路不影响正常工作;当进行测试时,输出端口A和输出端口B可以配置控制TX发射信号;正常工作时,输出端口C=D=1,NMOS管M1和NMOS管M2常通,对信号传输没有影响,当进入测试模式后,输出端口C、D信号会受控测试电路对RX进行控制。

在量产终测时,需要进入测试模式,通常可以用IIC或者SPI等方式进行通信,控制内部电路,可以与EN或者NC等管脚复用,其中CLK为时钟信号、DATA为数据信号。可以对TX发射端进行选通测试,也可以对RX接收端进行选通测试。以左边的裸芯为例,测试控制信号进入测试与接口电路108后,分别测试TX两条路径的连通情况。考虑到如果两根绑定线都断或者都正常,比较容易测试筛选,主要考虑其中一根绑定线断线的情况。当输出端口A=1,B=0,发射驱动器104A输出正常驱动信号,发射驱动器104B无信号输出,如果L1恰好断线了,则RX的两个差分输入均没信号输入,则说明该片为不良品;如果L1正常,L2断线,则RX正常输出。继续轮询,输出端口A=0,B=1,发射驱动器104A无输出,发射驱动器104B正常输出,如果L1断线,RX正常解调;如果L2断线,RX无输出,则能准确筛选出不良品。通过控制输出端口C、D信号可以对接收器120进行断线检测,考虑L3和L4有一根断线的情况,若L3断线,L4正常,当输出端口C=1,D=0时,右侧的TX信号无法正常传递到RX,RX无输出,可以筛选出不良品;若L3正常,L4断线,当C=0,D=1时,右侧的TX信号无法正常传递到RX,RX无输出,同样可以筛选出不良品。

图3对一正一反两个通道进行了举例说明,本发明也可以适用其他通道配置的情形,譬如左边的几个通道全部都是发射器,或者全部都是接收器。也可适用于与其他合封的情况。在另一实施例中,如图4所示,两颗隔离器裸芯与另一颗其他功能裸芯200合封(如RS485或者CAN)组成隔离CAN或者隔离RS485,只需对最左侧的数字隔离器裸芯进行控制测试,即可以对TX和RX的互连断线均进行检测,高效,并且轻松方便的筛选出不良品。

以上所述,仅为本申请的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以权利要求的保护范围为准。

- 电容型隔离器的键合线失效检测电路、方法及电子设备

- 电容型隔离器的键合线失效检测电路及电子设备