可配置多域多相分解式电压调节器

文献发布时间:2023-06-19 18:34:06

技术领域

本公开内容涉及针对可配置多域多相分解式电压调节器的技术、方法和装置。

背景技术

当在半导体材料(例如,硅)的晶圆上制造电子电路时,电子电路通常被称为集成电路(IC)。具有这种IC的晶圆通常被切割成许多单个的管芯。管芯可以封装到IC封装中,该IC封装包含一个或多个管芯以及诸如电阻器、电容器和电感器的其他电子部件。IC封装可以集成到电子系统上,例如消费电子系统。这种IC的部件在特定额定功率、电压和/或电流下工作。在许多IC中,虽然电流消耗是动态的并且取决于负载,但是电压是固定的并且理想地是恒定的,以便部件的正常运行。可以用电压调节器(VR,voltage regulator)来维持固定电压。线性VR是基于晶体管的设备,其通常被封装为IC或与IC一起封装,IC使用差分放大器来相对于参考电压控制输出电压,典型地具有与输出电流相当的输入电流。开关VR以高频率切换串联设备的开/关,从而改变作为输出而传递的电压的占空周期。它们的常见拓扑是降压(输出电压低于输入电压)、升压(输出电压高于输入电压)和降压-升压。在典型计算机的示例中,VR将来自电源单元的12V或5V或3.3V直流(DC)转换为IC的较低工作电压,例如0.8V、1V或1.2V。

附图说明

根据结合附图的以下具体实施方式,将容易理解实施例。为了便于描述,相同的附图标记表示相同的结构元件。在附图的各图中,通过示例而非限制的方式示出了各实施例。

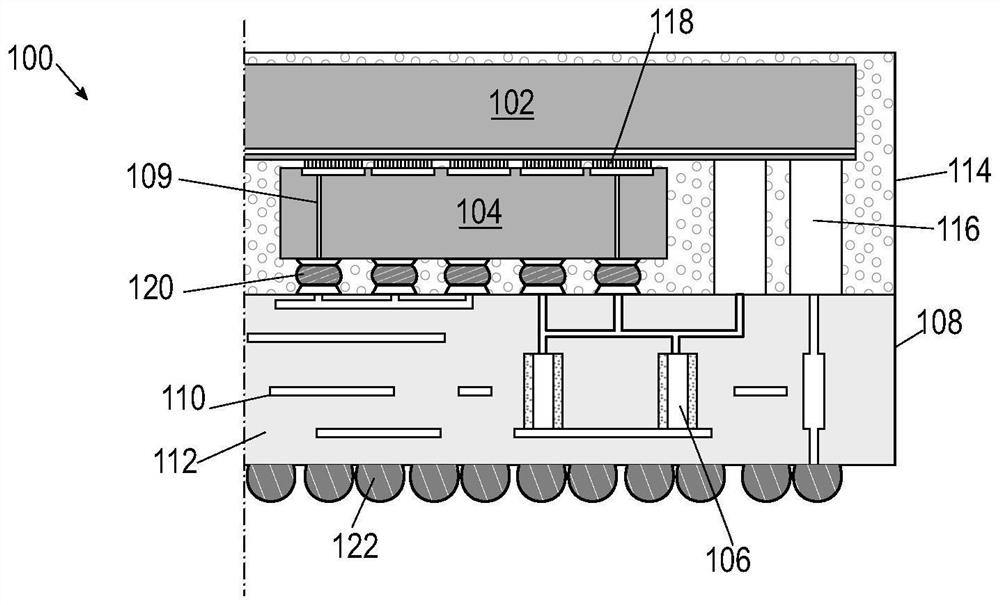

图1是根据本公开内容的一些实施例的示例VR封装架构的简化截面图。

图2是根据本公开内容的一些实施例的示例VR的细节的示意性框图。

图3是根据本公开内容的一些实施例的示例VR的细节的示意性框图。

图4是根据本公开内容的一些实施例的示例VR的细节的示意性框图。

图5是根据本公开内容的一些实施例的示例VR的细节的示意性框图。

图6是根据本公开内容的一些实施例的示例VR的细节的示意性框图。

图7是根据本公开内容的一些实施例的示例VR封装架构的简化截面图。

图8是根据本公开内容的一些实施例的另一示例VR封装架构的简化截面图。

图9是根据本公开内容的一些实施例的又一示例VR封装架构的简化截面图。

图10是根据本公开内容的各种实施例的制造微电子组件的示例方法的流程图。

图11是根据本公开内容的各种实施例的制造微电子组件的示例方法的流程图。

图12是根据本文所公开的任何实施例的可以包括一个或多个IC封装的设备封装的截面图。

图13是根据本文公开的任何实施例的可以包括一个或多个IC封装的设备组件的截面侧视图。

图14是根据本文公开的任何实施例的可以包括一个或多个IC封装的示例计算设备的框图。

具体实施方式

为了说明本文描述的IC封装,理解在IC的组装和封装期间可能起作用的现象是重要的。以下基本信息可以被视为可以适当地解释本公开内容的基础。提供这样的信息仅用于解释的目的,并且因此不应以限制本公开内容及其潜在应用的广泛范围的方式来解释。

在一般意义上,被实施为降压转换器的基本VR电路(本质上是单相VR电路)包括以高电压(例如,12V)向金属氧化物半导体场效应晶体管(MOSFET)开关输送功率的电源(例如,电池)。开关连接到工作在低电压(例如1.2V)的电负载,该电负载具有用作扼流圈的中间电感器。可以注意到,本文使用的术语“电负载”指的是消耗电能的IC的一部分,例如,诸如中央处理单元(CPU)的处理器。当开关闭合时,电感器的更接近电源的输入侧上的电压变为12V,但是电感器的连接到电负载的输出侧处的电压不瞬时改变。相反,电感器抵抗电流的变化,从而建立磁场,这在电感器的输出端处创建电压降。当开关断开时,电感器的输入端处的电压降至0V。在充电期间建立的电感器的磁场开始崩溃,从而在电感器的输出端处生成电流,该电流被馈送到电负载。通过适当地断开和闭合开关(例如,通过使用脉宽调制(PWM)的合适控制器)可以将电感器的连接到电负载的输出端处的电压维持在大约1.2V的平均值。

在一些IC中,使用多相VR。多相VR的工作方式与上述单相VR类似,但是使用多个并联的这种电路,其中每相处理电负载所需的总电流的一部分。如本文所用,术语“相”或“相电路”是指VR电路的级、段或部分,包括开关、电感器、电容器和如上所述的将电力从第一电压转换成第二电压所需的其他元件。每相被稍微偏移,使得在任何给定时间,仅单相对其电感器充电,而剩余的相放电。通过以偏移重叠各相,各相的组合输出将平均为1.2V,但是当一相的电压开始下降时,下一相接管,从而产生具有更严格电压容限的稳定平均输出电压。由于与单相VR相比,馈送到电负载的电流总量或多或少地保持不变,因此总电流分布在多相中,从而对任何单独电路施加较少的应变。此外,增加相数还减轻了电路中由于开关的断开和闭合而产生的总噪声。应当注意,以上描述简要地解释基本VR电路装置(circuitry),而IC中的实际实施方式将包括许多更多部件,例如电容器、二极管、反馈电路、模数转换器(ADC)和数模转换器(DAC)。

根据服务器、云计算、人工智能(AI)和图形的市场趋势,对诸如CPU的需要高功率和功率密度的处理器的需求日益增加,以满足日益增长的计算需求。为了支持这种功耗设备(例如,消耗大于1000W),例如在最后的功率输送级中可以使用与CPU管芯封装在一起的高输入电压(例如,大于2.0V的输入电压)集成VR(IVR)。这样的IVR可以以完全集成的形式(完全集成的电压调节器或FIVR)来实施,其是集成在CPU管芯自身上的降压转换器VR。然而,FIVR策略固有地受到特定技术限制,这阻碍了将CPU计算和功率能力扩大到市场趋势所要求的水平。

最近和未来的硅工艺(例如,制造)技术越来越多地被调整以改进和加速数字性能(例如,通过缩小设备尺寸、减小晶体管电压设备和增加金属层)。然而,对于包括IVR的高效功率输送电路(也称为功率输送知识产权(IP)),这种趋势固有地与期望的最佳工艺特性(例如高电压、低电阻和低成本)相反。因为FIVR位于CPU管芯上,所以它们必须使用与CPU管芯相同的技术工艺节点,该节点通常是不支持高效功率输送IP的先进工艺节点。这对跟上当前和未来CPU的快速功率增加的需求产生了若干基本障碍。

另外,先进数字工艺节点的使用迫使在降低FIVR的输入电压与创建更独特和复杂的FIVR功率系(PTR,powertrain)拓扑(例如多堆叠硅架构)之间进行选择。另外,半导体管芯中的小设备尺寸和高金属层数会增加工艺泄漏和电阻,这增加FIVR损耗并且降低FIVR功率效率。此外,因为最新的工艺节点通常比较老的制造技术昂贵,所以通常以利用管芯的平面布置面积来提高性能为目标(例如,每个管芯具有较大数量的处理核)。将FIVR定位在该相同管芯上使得无法实现性能目标,因为它占用否则会放置处理核的昂贵的平面布置面积(例如,在先进服务器产品上为10%),同时低效地工作。另外,使用先进工艺节点制造FIVR导致更昂贵的FIVR。实际上,近来和未来的CPU工艺节点的高度多样性需要在所有这些不同节点上制造FIVR,尽管其架构完全相同,由此产生设计开销(例如,主要用于模拟和安全数字(SD))和验证/质量风险(例如,分别重新验证每个工艺节点)。

在本公开内容的一个方面中,多域多相VR封装架构的示例包括第一IC管芯和第二IC管芯,第一IC管芯包括电负载电路,并且第二IC管芯包括耦接到第一IC管芯的多个PTR相。PTR相包括调节(例如,控制)去往电负载电路的功率供应的VR的高压驱动级和/或功率级。第一IC管芯还包括调节对应的电负载电路的域控制器(DCU),以及PTR管芯控制器(XCU),XCU在多个PTR相与DCU之间接口连接,例如,将PTR相与DCU进行映射。

本公开内容的结构、组件、封装、方法、设备和系统中的每一个可以具有若干创新方面,其中没有单一方面单独负责本文所公开的所有期望属性。在以下描述和附图中阐述了本说明书中描述的主题的一个或多个实施方式的细节。

在以下具体实施方式中,将使用本领域技术人员通常采用的术语来描述说明性实施方式的各个方面,以向本领域其他技术人员传达其工作的实质。例如,术语“连接”表示在没有任何中间设备的情况下被连接的事物之间的直接连接(其可以是机械、电和/或热连接中的一个或多个),而术语“耦接”表示被连接的事物之间的直接连接,或者通过一个或多个无源或有源中间设备的间接连接。术语“电路”和“电路装置(circuitry)”表示一个或多个无源和/或有源部件,它们被布置为彼此合作以提供期望的功能。如本文所使用的,这些术语还指模拟电路装置、数字电路装置、硬连线电路装置、可编程电路装置、微控制器电路装置和/或任何其他类型的物理硬件电气和/或电子部件。例如,术语“互连”可以用于描述由导电材料形成的任何元件,其用于提供到与IC相关联的一个或多个部件的电连接和/或在各种这样的部件之间的电连接。通常,“互连”可以指导电迹线(有时也称为“线”)和导电过孔两者。通常,在互连的上下文中,术语“导电迹线”可以用于描述由提供在管芯的平面内的绝缘材料(例如,低k电介质材料)隔离的导电元件。这些迹线通常堆叠成金属化堆叠体的若干层级或若干层。另一方面,术语“过孔”可以用于描述将不同层级处的两条或更多条迹线互连的导电元件。为此,可以提供基本上垂直于管芯平面的过孔,并且该过孔可以互连相邻层级中的两条迹线或不相邻的层级中的两条迹线。术语“金属化堆叠体”可以用于指用于提供到管芯的不同电路部件的连接的一个或多个互连的堆叠体。有时,迹线和过孔可以分别称为“导电迹线”和“导电过孔”,以强调这些元件包括诸如金属的导电材料的事实。

如本文所述的互连(特别是如本文所述的IC结构的互连)可以用于提供到与IC相关联的一个或多个部件的电连接和/或在各种这样的部件之间的电连接,其中,在各种实施例中,与IC相关联的部件可以包括例如晶体管、二极管、电源、电阻器、电容器、电感器、传感器、收发器、接收器、天线等。与IC相关联的部件可以包括安装在IC上的部件或连接到IC的部件。IC可以是模拟的或数字的,并且可以用于许多应用中,例如微处理器、光电子器件、逻辑块、音频放大器等,这取决于与IC相关联的部件。IC可以用作芯片组的一部分,以用于执行计算机中的一个或多个相关功能。在另一示例中,术语“封装”和“IC封装”是同义的,术语“管芯”和“IC管芯”也是同义的,除非另有说明,否则术语“绝缘”表示“电绝缘”,术语“传导”表示“导电”。

在又一示例中,如果使用的话,术语“氧化物”、“碳化物”、“氮化物”等分别指包含氧、碳、氮等的化合物,术语“高k电介质”指具有比氧化硅更高的介电常数的材料,而术语“低k电介质”指具有比氧化硅更低的介电常数的材料。

术语“基本上”、“接近”、“近似”、“附近”和“大约”通常是指基于如本文所述或如本领域已知的特定值的上下文在目标值的+/-20%内(例如,在目标值的+/-5%或10%内)。类似地,指示各种元件的取向的术语(例如“共面”、“垂直”、“正交”、“平行”或元件之间的任何其他角度)通常是指基于如本文所述或如本领域中已知的特定值的上下文在目标值的+/-5-20%内。

如本文所用,术语“上方”、“下”、“之间”和“上”是指一个材料层或部件相对于其他层或部件的相对位置。例如,设置在另一层上方或下的一层可以直接与另一层接触或者可以具有一个或多个中间层。此外,设置在两层之间的一层可以直接与两层中的一层或两层接触,或者可以具有一个或多个中间层。相反,被描述为在第二层“上”的第一层是指与该第二层直接接触的层。类似地,除非明确地另外说明,否则设置在两个特征之间的一个特征可以与相邻特征直接接触或可以具有一个或多个中间层。另外,如本文所用的术语“设置”是指位置、定位、放置和/或布置,而不是指任何特定的形成方法。

出于本公开内容的目的,短语“A和/或B”表示(A)、(B)或(A和B)。出于本公开内容的目的,短语“A、B和/或C”表示(A)、(B)、(C)、(A和B)、(A和C)、(B和C)或(A、B和C)。当参考测量范围使用时,术语“之间”包括测量范围的端点。当在本文中所用时,符号“A/B/C”表示(A)、(B)和/或(C)。

本说明书使用短语“在实施例中(in an embodiment或in embodiments),其可以各自指代相同或不同实施例中的一个或多个。此外,如关于本公开内容的实施例所使用的术语“包括”、“包含”、“具有”等是同义的。本公开内容可以使用基于透视的描述,例如“之上”、“下方”、“顶部”、“底部”和“侧面”;这样的描述用于方便讨论,并且并非旨在限制所公开的实施例的应用。附图不一定是按比例绘制的。除非另有说明,否则使用序数形容词“第一”、“第二”和“第三”等来描述共同对象仅指示正在引用类似对象的不同实例,并且并非旨在暗示如此描述的对象必须在时间上、空间上、在排序上或以任何其他方式处于给定序列中。

在以下具体实施方式中,参考形成其一部分的附图,并且在附图中通过说明示出了可以实践的实施例。应当理解,可以利用其他实施例,并且可以在不脱离本公开内容的范围的情况下进行结构或逻辑改变。因此,以下具体实施方式不应被理解为限制性的。

在附图中,相同的附图标记指代所示的相同或类似的元件/材料,使得除非另有说明,在附图之一的上下文中提供的具有给定附图标记的元件/材料的解释可应用于其中可以示出具有相同附图标记的元件/材料的其他附图。此外,在附图中,本文所述的各种设备和组件的示例结构的一些示意图可以用精确的直角和直线示出,但是应当理解,这些示意图可能不反映现实工艺限制,这可能导致当使用例如合适的表征工具的图像(例如扫描电子显微镜(SEM)图像、透射电子显微镜(TEM)图像或非接触式轮廓曲线仪)检查本文所述的任何结构时,特征看起来不是那么“理想”。在真实结构的这种图像中,可能的处理缺陷和/或表面缺陷可能也是可见的,例如表面粗糙度、曲率或轮廓偏差、凹坑或划痕、材料的不完全直的边缘、锥形过孔或其他开口、拐角的无意倒圆角或不同材料层的厚度变化、(一个或多个)结晶区域内的偶然的螺旋、边缘或组合位错、和/或单个原子或原子簇的偶然位错缺陷。可能存在此处未列出的但在设备制造和/或封装领域内常见的其他缺陷。

在附图中,出于说明性目的呈现了结构和部件的特定数量和布置,并且在各种实施例中可以呈现此类结构和部件的任何期望数量或布置。此外,图中所示的结构可以根据材料特性、制造工艺和操作条件而采用任何合适的形式或形状。

可以以最有助于理解所要求保护的主题的方式依次将各种操作描述为多个分立的动作或操作。然而,描述的顺序不应被解释为暗示这些操作必须是顺序相关的。特别地,这些操作可以不以所呈现的顺序执行。所描述的操作可以以与所描述的实施例不同的顺序来执行。在附加实施例中,可以执行各种附加操作,和/或可以省略所描述的操作。

图1是根据本公开内容的一些实施例的微电子组件100的一部分的示意性截面图。示例实施例包括以低电压向负载管芯102中的一个或多个负载域提供功率的VR。VR包括负载管芯102上的一个或多个DCU(域控制器)和XCU(PTR管芯控制器)、PTR管芯(XPT)104上的多个PTR相以及封装衬底108中的电感器106。在一些实施例中,XPT 104可以包括穿衬底过孔(TSV)109;在其他实施例中,XPT 104可以不包括任何TSV。封装衬底108包括绝缘(例如,电介质)材料112中的导电路径110。负载管芯102和XPT 104可以被包封在模制化合物114中,穿过该模制化合物的铜柱116将负载管芯102与封装衬底108电耦接。在一些实施例中,模制化合物114与XPT 104和铜柱106一起可以包括分立部件,例如中介层。管芯到管芯(DTD)互连118将负载管芯102与XPT 104电和机械耦接。管芯到封装衬底(DTPS)互连120将XPT 104与封装衬底108电和机械耦接。互连122提供封装衬底108到系统中的其他组件(例如,印刷电路板)的电和机械耦接。

DCU包括反馈控制,以调节输出电压并且通过负载管芯102中的XCU向XPT 104中的PTR相发送反馈信号(例如,PWM信号或模拟电压)。XCU可以连接到多个DCU,并且基于数字配置任意地将DCU映射到PTR相。映射还应用于从PTR相到DCU的模拟和数字信号(例如,遥测)的通信,例如,用于电流感测、故障检测和其他这样的功能。在一些实施例中,来自多个PTR管芯(例如,XPT 104中的多个管芯)的PTR相可以被配置(例如,成组)以服务于相同的负载域。在这样的实施例中,DCU可以直接连接以共享电流信息并且实现PTR相之间的负载平衡。

XPT 104上的PTR相可以从不同的输入电压源供电(如果它们提供不同的负载域),而调节相同负载域的PTR相可以从相同的输入电压源供电。DCU和XCU可以具有用于负载管芯102中的其他管芯部件(例如,功率管理)的高带宽(BW)和/或高引脚数接口,以用于电压设置点、控制器设置、相启用、遥测信息等的双向通信。在一些实施例中,互连118可以包括低引脚数接口。在各种实施例中,XPT 104的配置和状态读出可以通过专用工业标准通信接口(例如,I2C)由负载管芯102中的XCU主控。在许多实施例中,到XPT 104中的PTR相的输入电压可以高于到负载管芯102的电源电压。

一些实施例中,负载管芯102耦接在XPT 104的一侧上,XPT 104在相对侧上附接到封装衬底108。虽然图1所示的实施例示出了堆叠在负载管芯102下面的XPT 104,但是其他实施例可以包括平面配置,其中XPT 104可以与负载管芯102并排放置,并且穿过封装衬底108与例如桥接管芯或其他互连互连,如在随后的图中所讨论的。信号连接通过合适的互连(例如118、120)、模制化合物114中的铜柱116和XPT 104中的TSV 109。从XPT 104去往电感器106的功率连接可以通过DTPS互连120。从电感器106到负载管芯102的功率连接可以通过专用功率桥,该专用功率桥或者通过XPT 104中的TSV 109或者通过模制化合物114中的铜柱116馈送。

本文所述的各种实施例可以提供许多优点。例如,可以为XPT 104中的PTR相提供高电压,而可以为负载管芯102中的负载域完全提供低输入电压。此外,与负载管芯102中的负载域解耦的XPT 104中的功率系相(power train phase)可以允许将XPT 104的输入电压增加到比负载管芯102所允许电平的更高的电平,由此允许分布在负载管芯102与XPT 104之间的VR在较低电压下向负载管芯102中的负载域提供更高的电流。另一个优点是:可以选择能够实现功率输送、高电压和低电阻的处理技术来制造XPT 104,而可以使用支持更高性能的先进工艺节点来制造负载管芯102。通过将PTR相移动到XPT 104,由此释放待释放的区域(例如,5-10%)以用于更高性能的计算部件(例如,核、AI引擎、图形执行单元等),也可以降低负载管芯102中的平面布置面积方面的成本。

在一些实施例中,负载管芯102和XPT 104可以包括基本上单晶的半导体,例如硅或锗作为衬底,在该衬底上用传统的半导体处理方法制造有源设备。在一些其他实施例中,可以使用替代材料形成负载管芯102和XPT 104的衬底,替代材料可以或可以不与硅结合,替代材料包括但不限于锗、锑化铟、碲化铅、砷化铟、磷化铟、砷化镓、砷化铟镓、锑化镓、或III-V族、II-VI族或IV族材料的其他组合。在又一些其他实施例中,衬底可以包括化合物半导体,例如,具有来自周期表的III族的至少一种元素(例如,Al、Ga、In)的第一子晶格和周期表的V族的至少一种元素(例如,P、As、Sb)的第二子晶格。在又一些其他实施例中,衬底可以包括本征IV或III-V半导体材料或合金,其不是有意掺杂有任何电活性杂质;在替代实施例中,可以存在标称杂质掺杂剂水平。在再一些其他实施例中,衬底可以包括有机材料,例如二氧化硅填充的环氧树脂。在其他实施例中,衬底可以包括高迁移率氧化物半导体材料,例如氧化锡、氧化锑、氧化铟、氧化铟锡、氧化钛、氧化锌、氧化铟锌、氧化铟镓锌(IGZO)、氧化镓、氮氧化钛、氧化钌或氧化钨。通常,衬底可以包括氧化锡、氧化钴、氧化铜、氧化锑、氧化钌、氧化钨、氧化锌、氧化镓、氧化钛、氧化铟、氮氧化钛、氧化铟锡、氧化铟锌、氧化镍、氧化铌、过氧化铜、IGZO、碲化铟、辉钼矿、二硒化钼、二硒化钨、二硫化钨、N或P型非晶或多晶硅、锗、砷化铟镓、硅锗、氮化镓、氮化铝镓、磷化铟和黑磷中的一种或多种,它们中的每一种都可以掺杂有镓、铟、铝、氟、硼、磷、砷、氮、钽、钨和镁等中的一种或多种。

在各种实施例中,负载管芯102可以包括以下中的一个或多个,或者是其一部分:CPU、存储器设备(例如,高带宽存储器设备)、逻辑电路、输入/输出电路装置、收发器(例如,现场可编程门阵列收发器)、门阵列逻辑单元(例如,现场可编程门阵列逻辑单元)、功率输送电路装置、III-V或III-N设备(例如,III-N或III-N放大器(例如,GaN放大器))、外围部件互连高速(PCIe)电路装置、双倍数据速率传输电路装置或本领域已知的其他电子部件。

尽管为了不使附图混乱而没有在所有本图示中具体示出,但是当描述DTD或DTPS互连时,(例如,负载管芯102或XPT 104的)第一表面可以包括第一组导电触点,并且(例如,XPT 104或封装衬底108的)第二表面可以包括第二组导电触点。然后,第一组的一个或多个导电触点可以通过DTD或DTPS互连而电和机械地耦接到第二组中的一些导电触点。在一些实施例中,DTD互连(例如,118)的间距可以与DTPS互连(例如,120)的间距不同,尽管在其他实施例中,这些间距可以基本上相同。在一些实施例中,本文公开的DTPS互连可以具有约80微米至300微米之间的间距,而本文公开的DTD互连可以具有约0.7微米至100微米之间的间距。

本文公开的DTPS互连(例如,120)可以采用任何合适的形式。在一些实施例中,一组DTPS互连可以包括焊料(例如,经受热回流以形成DTPS互连的焊料凸块或球)。包括焊料的DTPS互连可以包括任何适当的焊料材料,例如铅/锡、锡/铋、共晶锡/银、三元锡/银/铜、共晶锡/铜、锡/镍/铜、锡/铋/铜、锡/铟/铜、锡/锌/铟/铋、或其他合金。在一些实施例中,一组DTPS互连可以包括各向异性导电材料,例如各向异性导电膜或各向异性导电膏。各向异性导电材料可以包括分散在非导电材料中的导电材料。在一些实施例中,各向异性导电材料可以包括嵌入在粘结剂或热固性粘合膜(例如,热固性联苯型环氧树脂或丙烯酸基材料)中的微观导电颗粒。在一些实施例中,导电颗粒可以包括聚合物和/或一种或多种金属(例如,镍或金)。例如,导电颗粒可以包括进而涂覆有聚合物的镍涂覆的金或银涂覆的铜。在另一示例中,导电颗粒可以包括镍。当未压缩各向异性导电材料时,从材料的一侧到另一侧可能没有导电路径。然而,当充分压缩各向异性导电材料时(例如,通过各向异性导电材料的任一侧上的导电触点),压缩区域附近的导电材料可以彼此接触,以便在压缩区域中形成从膜的一侧到另一侧的导电路径。

本文公开的DTD互连(例如,118)可以采用任何合适的形式。在一些实施例中,如本文描述的DTD互连中的一些或全部可以包括混合接合互连、金属到金属互连(例如,铜到铜互连或电镀互连)。在其他实施例中,DTD互连可以是焊料凸块(例如,C4凸块)或微凸块(例如,C2凸块)。在DTD互连包括金属-金属接合的实施例中,DTD互连的任一侧上的导电触点可以接合在一起(例如,在升高的压力和/或温度下),而不使用中间焊料或各向异性导电材料。在一些实施例中,可以在金属到金属互连中使用焊料的薄盖以适应平面性,并且该焊料可以在处理期间变成金属间化合物。在利用混合接合的一些金属到金属互连中,电介质材料(例如,氧化硅、氮化硅、碳化硅或有机层)可以存在于接合在一起的金属之间(例如,在提供相关联的导电触点的铜焊盘或柱之间)。在一些实施例中,DTD互连的一侧可以包括金属柱(例如,铜柱),并且DTD互连的另一侧可以包括凹入电介质中的金属触点(例如,铜触点)。在一些实施例中,金属到金属互连(例如,铜到铜互连)可以包括贵金属(例如,金)或其氧化物导电的金属(例如,银)。在一些实施例中,金属到金属互连可以包括可以具有降低的熔点的金属纳米结构(例如,纳米棒)。金属到金属互连能够比其他类型的互连可靠地传导更高的电流;例如,当电流流动时,一些焊料互连可形成脆性金属间化合物,并且可以限制通过这种互连提供的最大电流以减轻机械故障。

在一些实施例中,一组DTD互连的任一侧上的IC可以是未封装的管芯,和/或DTD互连可以包括通过焊料附接到相应导电触点的小导电凸块或柱(例如,铜凸块或柱)。在一些实施例中,DTD互连中的一些或全部可以是焊料互连,该焊料互连包括熔点比包括在DTPS互连中的一些或全部中的焊料更高的焊料。例如,当在形成DTPS互连之前形成DTD互连时,基于焊料的DTD互连可以使用较高温度的焊料(例如,具有高于200摄氏度的熔点),而DTPS互连可以使用较低温度的焊料(例如,具有低于200摄氏度的熔点)。在一些实施例中,较高温度的焊料可以包括锡;锡和金;或锡、银和铜(例如,96.5%锡、3%银和0.5%铜)。在一些实施例中,较低温度的焊料可以包括锡和铋(例如,共晶锡铋)或者锡、银和铋。在一些实施例中,较低温度的焊料可以包括铟、铟和锡、或镓。

在一些实施例中,一组DTD互连可以包括任何适当的焊料材料,例如上面针对DTPS互连讨论的任何材料。在一些实施例中,一组DTD互连可以包括各向异性导电材料,例如上面针对DTPS互连讨论的任何材料。在一些实施例中,DTD互连可以用作数据传输通道,而DTPS互连可以用于电源线和地线等。注意,在图1和随后的附图中,DTD和DTPS互连被示为在相应的接口处对准,这仅仅是为了便于说明;实际上,它们中的一些或全部可能未对准。另外,在组件中可以存在有其他部件(例如接合焊盘、着陆焊盘、金属化等),这些部件在图中未示出以防止混乱。例如,穿过连接部(through-connection)可以在其顶部上具有焊盘,并且可以着陆在顶部管芯上的更大的焊盘上。

在本文描述的封装中,DTD互连中的一些或全部可以具有比DTPS互连更精细的间距。在一些实施例中,DTD互连可能具有过于精细的间距以至于不能直接耦接到封装衬底(例如,过于精细以至于不能用作DTPS互连)。由于在一组DTD互连的任一侧上的不同管芯中的材料的相似性大于在一组DTPS互连的任一侧上的管芯和封装支撑件之间的相似性,所以DTD互连可以具有比DTPS互连更小的间距。特别地,由于在操作期间生成的热量(以及在各种制造操作期间施加的热量),IC和封装支撑件的材料成分的差异可能导致IC和封装支撑件的不同膨胀和收缩。为了减轻由这种有差异的膨胀和收缩引起的损坏(例如,破裂、焊料桥接等),如本文所述的任何封装中的DTPS互连可以形成为比DTD互连更大并且更远地分开,由于DTD互连的任一侧上的管芯对的更大的材料相似性,DTPS互连可以经历更少的热应力。

在各种实施例中,电感器106可以包括嵌入在封装衬底108的绝缘体112内的同轴磁性电感器层(MIL)结构。在一些实施例中,同轴MIL结构可以包括由诸如磁性树脂的高磁导率磁性材料围绕的镀铜衬通孔(copper-lined plated through-hole)(PTH)。磁性树脂还可以包括铁氧体颗粒填充物。在其他实施例中,同轴MIL结构可以包括具有圆柱形外壳的铁氧体芯。在又一些实施例中,电感器106可以包括磁互连(或磁芯、铁氧体芯等),其可以被制造成空心圆柱体外壳(或类似物)的形状,嵌入和/或以其他方式设置在封装衬底108的绝缘体112中,其中磁互连围绕铜填充PTH过孔。在各种实施例中,电感器106的磁性材料可以包括一种或多种铁磁(或亚铁磁)材料,包括(但不限于)钴、铁、氧化铁(例如,氧化铁和/或氧化亚铁),铁、镍、铜、镁、锰、铋、锑、钇、铬、砷、镉、锌、碲化物的氧化物(例如,FeOFe

可以通过铜柱116和其他导电路径在封装衬底108与负载管芯102之间传送电源、接地和/或信号。在其他实施例中,可以通过DTPS互连120、XPT 104和DTD互连118在封装衬底108与负载管芯102之间传送电源、接地和/或信号。此外,封装衬底108中的电源和接地平面可以根据需要促进到XPT 104和/或负载管芯102的电源和接地连接。根据各种实施例,负载管芯102还包括电容器及其他部件,所述其他部件包括诸如多域多相VR的MOSFET开关及二极管的有源部件。在一些实施例中,包括开关和二极管的VR的有源部件可以包括在XPT104中,而控制开关的控制电路(例如,XCU)可以包括在负载管芯102中。如本文进一步讨论的,各种其他配置是可能的。

在各种实施例中,绝缘体112可以包括与形成导电路径110的金属层交替的电介质层。在一些实施例中,绝缘体112可以包括环氧树脂(和/或其他有机聚合物材料)的内建层。在一些实施例中,绝缘体112可以包括双马来酰亚胺-三嗪(BT)树脂、聚酰亚胺材料、玻璃增强环氧树脂基体材料、具有无机填充物的有机电介质或低k和超低k电介质(例如,碳掺杂电介质、氟掺杂电介质、多孔电介质和有机聚合物电介质)。在其他实施例中,绝缘体112可以包括陶瓷(和/或其他绝缘无机材料)。在一些实施例中,封装衬底108可以包括玻璃纤维增强环氧树脂芯,其中在任一侧上导电金属层与绝缘层交替。在一些实施例中,封装衬底108可以包括阻燃等级4(FR-4)玻璃环氧树脂基,其具有层压在任一侧上的薄铜箔。对于某些实施例,多层印刷电路板(PCB)可以与铜箔和预浸材料(prepreg)一起使用,以制造分别包括导电路径110和绝缘体112的附加金属层。特别地,当使用标准PCB工艺形成封装衬底108时,封装衬底108可以包括FR-4,并且导电路径110可以由通过FR-4的内建层分离的图案化铜片形成。导电路径110可以包括铜(或其他导电金属)迹线、线路、焊盘、过孔、过孔焊盘、孔和/或平面。导电路径110可以由衬层材料界定,例如粘合衬层和/或阻挡衬层,视情况而定。

在一些实施例中,可以使用光刻限定的过孔封装工艺来形成封装衬底108。在一些实施例中,使用标准有机封装制造工艺来制造封装衬底108,并且因此封装衬底108可以采用有机封装的形式。可以使用本领域中已知的用于制造封装衬底108的任何方法,并且为了简洁起见,本文将不进一步详细讨论这样的方法。

在一些实施例中,模制化合物114可以包括二氧化硅填充的环氧树脂或其他合适的有机聚合物。在图中所示的实施例中,模制化合物114完全包围负载管芯102和XPT 104。在其他实施例中,模制化合物114可以部分地包围负载管芯102和/或XPT 104。例如,可以使负载管芯102的表面暴露以在顶部上附接热沉和/或另一部件。在其他实施例中,模制化合物114可以由多于一种材料构成,例如,围绕负载管芯102的第一材料和围绕XPT 104的不同的第二材料。在各种实施例中,模制化合物114可以根据任何合适的工艺来设置,所述工艺例如沉积、层压和/或后续固化。在示例工艺中,可以首先围绕XPT 104和铜柱116设置模制化合物114。如果形成模制化合物114以完全覆盖XPT 104和铜柱116,则可以使用任何合适的技术暴露顶表面XPT 104和铜柱116处的导电触点,所述技术包括研磨或蚀刻(例如湿法蚀刻、干法蚀刻(例如等离子体蚀刻))、湿法喷砂或激光烧蚀(例如使用准分子激光)。随后,可以通过互连118附接负载管芯102,然后围绕负载管芯102设置附加的模制材料,并且将其固化。

微电子组件100还可以包括底部填充材料(未示出)。在一些实施例中,底部填充材料可以在XPT 104与封装衬底108之间延伸,包括在相关联的DTPS互连120周围进行延伸。底部填充材料可以是绝缘材料,例如适当的环氧树脂材料。在一些实施例中,底部填充材料可以包括毛细底部填充物、非导电膜(NCF)或模制底部填充物。在一些实施例中,底部填充材料可以包括环氧树脂助焊剂。底部填充材料可以选择为具有可以减轻或最小化XPT 104与封装衬底108之间的应力的热膨胀系数(CTE),该应力由微电子组件100中的不均匀热膨胀引起。在一些实施例中,底部填充材料的CTE可以具有介于封装衬底108的CTE(例如,绝缘体112的CTE)与XPT 104的CTE之间的值。

微电子组件100还可以包括电路板(未示出)。封装衬底108可以通过在封装衬底108的与XPT104相对的表面处的互连122耦接到电路板。互连122可以是任何合适的第二级互连,包括用于球栅阵列布置的焊球、引脚栅阵列布置中的引脚或连接盘栅阵列布置中的连接盘。电路板可以是例如主板,并且可以具有附接到主板的其他部件。电路板可以包括导电路径和其他导电触点,用于穿过电路板传送电源、接地和信号,如本领域已知的。在一些实施例中,互连122可以不将封装衬底108耦接到电路板,而是可以将封装衬底108耦接到另一IC封装、中介层或任何其他合适的部件。

注意,图1旨在示出部件在其组件内的相对布置,并且一般地,这样的组件可以包括未示出的其他部件(例如,各种界面层或与光学功能、电连接或热缓解有关的各种其他部件)。例如,在一些另外的实施例中,如图1所示的组件可以包括更多的管芯以及其他电气部件。另外,尽管组件的一些部件在图1中被示为平面矩形或由矩形实体形成,但这仅仅是为了易于说明,并且这些组件的实施例可以是弯曲的、圆形的或其他不规则形状,这是由于用于制造各种部件的制造工艺决定的,并且有时是不可避免的。

图2是示出管芯组件200中的多域多相VR的示例实施例的简化框图。负载管芯102包括一个或多个负载域202,每个负载域由相应的DCU 204控制。在所示的示例实施例中,负载管芯102是片上系统(SOC)CPU管芯。在其他实施例中,负载管芯102可以包括消耗功率的任何合适IC,例如,专用IC(ASIC)、可编程逻辑阵列(PLA)、网络处理器等。在各种实施例中,负载域202包括消耗功率的(一个或多个)电负载电路。负载域202的示例包括CPU、图形处理器单元(GPU)等。每个负载域202根据其功率消耗而具有功率状态(例如,开、关),并且可以与其他负载域不同地并且独立地消耗功率。根据各种实施例,每个负载域202也可以在独立的电压和频率设置下操作。例如,一个负载域可以在0.8V下操作,而另一个负载域可以在1.2V下操作。在一般意义上,负载域202在比提供给XPT 104的功率(例如,12V)低的电源电压(例如,0.8V、1.2V)下操作。

在各种实施例中,每个DCU 204包括调节对应负载域202的电负载电路的(一个或多个)控制电路。例如,调节包括在1.2V下操作的逻辑电路的负载域的DCU可以将到逻辑电路的电压供应调节到在1.2V左右的适当范围内;调节包括在0.8V下操作的处理器电路的另一负载域的另一DCU可以将到处理器电路的电压供应调节到在0.8V左右的适当范围内,等等。在另一示例中,调节特定负载域的DCU可以检测其中的电负载电路中的灾难性故障,并且相应地作出响应,例如切断对故障负载域的电流供应。如参考随后的附图所讨论的,在实施例的广泛范围内也可以预期各种其他操作。

耦接到DCU 204的XCU 206可以与XPT 104中的一个或多个PTR相208通信。PTR相208包括VR 210的高压驱动级和/或功率级,VR 210调节去往包括负载域202的电负载电路的功率供应。在一些实施例中,PTR相208可以被供应有1.8V到12V范围内的功率。在示例实施例中,PTR相208可以被供应有3V与5V之间的功率。在各种实施例中,XCU 206可以包括在DCU 204与XPT 104之间进行协调的控制电路。例如,XCU 206可以将PTR相208映射到DCU204,并且反之亦然。例如,XCU 206可以向XPT 104中的PTR相208提供PWM驱动信号,接收反馈信号以调节电感器106的输出电压,并且生成去往负载域202的输出电流,以及实现根据需要并参考随后附图所讨论的其他功能。DCU 204、XCU 206和PTR相208连同电感器106一起可以包括跨三个不同封装部件(负载管芯102、XPT 104和封装衬底108)分解和散布(例如,分布)的多域多相VR 210。

在一般意义上,将VR 210分解成多个封装部件不是简单的,因为在组装之前不能全面地对各个部件进行功能测试。因此,本公开内容的实施例与其中VR在负载管芯(例如,完全集成的VR(FIVR))、封装衬底或分立的专用电子模块中、其所有构成元件(例如,控制器、相、电感器等)一起在一个单个电子模块/部件/部分中的其他解决方案不同。如本文所公开的分解的一个优点是:负载管芯102中的控制器(例如,DCU 204和XCU 206)可以利用先进的半导体制造工艺的优点,而PTR相208和电感器106可以使用可以承受高电压的不太先进的处理技术来制造。其他优点参考上述图1讨论。

在各种实施例中,DCU 204生成反馈控制信号以调节通过XCU 206到PTR相208的输出电压和PWM信号。XCU 206可以连接到多个DCU 204,并且基于数字配置任意地将DCU 204映射到PTR相208,使得DCU 204在不可知(agnostic)PTR相208的情况下操作。映射还应用于通过包含一条或多条线(例如,反馈线、电流感测线等)的适当总线将模拟和数字信号从PTR相208传递到DCU 204。例如,取决于负载电流需求,XCU 206可以启动多个PTR相208,使得每相在给定电流范围内以适当有效的电平操作。在另一示例中,XCU 206可以监视总负载电流并且启动所选数量的PTR相208以将每相的平均电流维持在合适的窗口内。供应负载管芯102中的不同负载域202的XPT104中的PTR相208可以从不同的输入电压供应。服务于相同负载域202的PTR相206可以由相同输入电压供应。在各种实施例中,到XPT 104中的PTR相208的输入电压可以高于到负载管芯102上的负载域202的电源电压。

图3是示出在管芯组件300中成组的多域多相VR的示例实施例的简化框图。多个负载域202可以“成组”或组合成单个成组负载域302。在本领域中存在各种方法来执行这种成组;在实施例的范围内,本文可以使用这样的方法中的任一种。例如,成组负载域302中的一个负载域充当主负载域,并且成组负载域302中的所有其他负载域是遵循编程到主负载域的电压的从负载域。在另一示例中,来自成组负载域302中的各种负载域的输出引脚可以耦接在一起。通过使用成组,来自多个管芯104(1)和104(2)的PTR相208可以被配置为服务于同一成组负载域302。每个XPT 104(1)和104(2)可以分别由单独的XCU 206(1)和206(2)控制。在这样的实施例中,可以连接与成组负载域302通信的DCU 204以在它们之间共享成组电流信息304,并且实现PTR相208之间的负载平衡,而与PTR相208所属的特定XPT 104(1)或104(2)无关,并且使得成组负载域302对于启用电压调节的特定XPT 104(1)或104(2)是不可知的。这种VR 210的配置还可以包括由分离的DCU 204控制的单独的负载域202,如图所示。

图4是根据各种实施例的示例DCU 204的简化框图。DCU 204包括PWM 402、补偿器(CPS)模块404、DAC 406、ADC 408、数字前端(FE)410、延迟锁相环(DLL)412和电流传感器处理(CSX)模块414。在各种实施例中,数字FE 410用作用于与负载管芯102中的包括SOC功率管理(PM)实体的负载域202进行任何通信的前端。在各种实施例中,数字FE 410处理和控制工作点(WP)序列,例如VR_SETTLE信号(例如,传递电源电压的状态,例如,电压标识定义(VID)转换)、运行中PTR相、操作模式(例如,无熔丝、无时钟、加速、连续电流模式(CCM)、不连续传导模式(DCM)等)、遥测、警报/事件和功率状态(例如,PWRGOOD)通知。在一些实施例中,数字FE 410处理和控制IN和OUT灾难性故障(例如,过电压或过电流),这需要安全地关闭VR 210。在各种实施例中,数字FE 410从XCU 206接收DCU启用信号(例如,通知映射到DCU204的PTR相208中的至少一个PTR相)和映射的PTR相208的数量。

在各种实施例中,DAC 406将数字VID码转换为模拟电压电平。CPS 404通过在所需电压(例如,DAC输出)与实际负载电压电平(LOAD_SENSE)之间进行比较并且创建“电压误差”信号(V_ERROR)来闭合VR电压回路,所述“电压误差”信号被发送到PWM 402。DLL 412生成PWM时钟相以馈送到PWM 402中。PWM 402生成PWM定相脉冲(例如,用于功率系、N/P驱动器),其被馈送到XCU 206以用于启用XPT 104中的对应PTR相208。在各种实施例中,PWM 402包括生成定相电压三角的模拟三角波生成器(TWG,triangle wave generation),定相电压三角被输入到比较器中,该比较器通过将定相电压三角与来自CPS 404的V_ERROR信号进行比较来生成PWM定相脉冲。CSX 414可以处理通过XCU 206来自PTR相208的电流感测信息。ADC 408可以对诸如电流感测、电压等的模拟数据进行数字化,以用于遥测和调试。

图5是示出根据各种实施例的示例XCU 206的简化框图。XCU 206包括用于XPT 104的接口(例如,总线),通过该接口,XCU 206接收和发送与PTR相208和电感器106相关的信息。用于XPT 104的接口包括两个通道:第一通道,其传递XPT 104中的电路所共有的信息,例如复位、时钟、I2C数据和灾难性故障(如果有的话);以及第二通道,其传递XPT 104中的PTR相208中的每一个所特有的信息,例如电流、启用、操作模式和关闭。XCU 206可以实现负载管芯102中的DCU 204与XPT 104中的PTR相208之间的可配置映射。PTR相208中的每一个可以被映射到任何DCU 204或不被映射到任何DCU(未映射)。来自各个DCU 204的域信息可以被转换成每相输入并且被驱动到XPT 104。来自XPT 104的相信息可以被转换成每域输入并且被驱动到相关的DCU 204。

域到相映射模块(DPMM)502可以从DCU 204接收每域信息,将每域信息转换为每相输入,并且通过第二通道将每相输入发送到XPT 104中的PTR相208中的相关一个。在示例实施例中,来自DCU 204中的特定一个的每域信息包括PWM定相脉冲、是否启用PTR相208、对应负载域202所需的PTR相208的操作模式以及关闭信号。每相输入包括与PTR相208中的特定一个相关的启用、操作模式和关闭信号。

XCU寄存器504可以生成或存储映射信息,映射信息例如包括具有与映射到DCU204中的特定DCU的PTR相208中的特定PTR相、DCU 204的数量和PTR相208的数量有关的标识信息的相到域映射(PDM)配置位。PDM配置位可以由DPMM 502使用,将DCU 204与一个或多个PTR相208映射(反之亦然)。例如,PTR相208中的特定PTR相可以被映射到一个或多个DCU204。同样,DCU 204中的特定DCU可以被映射到一个或多个PTR相208。

使用PDM配置位中的信息,DPMM 504可以将每域信息转换为每相信息。例如,PDM[7]=2可以将相XPT_PHASE_7与域控制器DCU_2映射。在一般意义上,DPMM 502可以根据来自XCU寄存器504的PDM配置位将XPT 104中的PTR相208映射到负载管芯102中的任何DCU204,或者可以解映射PTR相208中已经映射的PTR相。PTR相208可能不知道它们所映射到的特定的负载域202或DCU 204,因为XCU 206中的DPMM 502在它们(PTR相208和负载域202或DCU 204)之间进行协调,从一个聚集信息,将该信息转换为与另一个相关的信息,并且将转换的信息发送到另一个。例如,PTR相208不存储关于它们被映射到的任何DCU 204的标识信息。

使用PDM配置位,DCU数字模块(DCU DIG)506可以聚集每域信息(例如启用的特定DCU、每域启用的相数、XCU 206中接收的灾难性故障信号),并且将每域信息发送到适当的DCU 204。在示例实施例中,DCU DIG 506从PTR相208接收每相信息,使用PDM配置位将每相信息转换为每域输入,并且通过用于DCU 204的接口将每域输入发送到DCU 204中的相关DCU。每相信息可以包括来自PTR相208中的每一个的灾难性故障信号、电流等。到DCU中每一个的每域输入可以包括是否启用该特定域、所连接的PTR相的数量、域电流信息(例如,来自所连接的PTR相的电流总和)、相关联PTR相中的任何灾难性故障等。DCU 204可以没有关于它们正在驱动多少个或哪些特定PTR相208的概念。例如,DCU 204可以不存储关于它们被映射到的任何PTR相208的任何标识信息。

在各种实施例中,可以访问XCU寄存器504以进行写入和读取。XCU 206中也可以存在具有功能接口和测试接口的模块508。功能接口耦接到控制寄存器(CR)总线(例如,32位寄存器总线),并且测试接口耦接到可制造性、可测试性和可调试性设计(DFx)联合测试行动小组/测试访问端口(JTAG/TAP),以使位能够被写入XCU寄存器504并且从XCU寄存器504访问。该信息还可以被转换成工业标准串行管芯到管芯通信协议,例如通过I2C总线的I2C主块510中的I2C,其中I2C从块(slave)驻留在XPT 104中。在各种实施例中,I2C主块510可以用作转换模块,将在CR总线上接收的信息转换为工业标准串行协议,例如I2C。I2C总线可以用于与XPT 104交互,以在XPT 104与XCU 206之间来回传输数据。

XCU 206可以使用适当的电路模块来执行每域的电流感测平均,例如,用于功率系相电流平衡操作。相到域电流求和模块(PDCSM)512可以对来自根据PDM配置位映射到DCU204的所有PTR相208的电流进行求和,并且将电流和信息发送到DCU 204。PDCSM 512可以将每相电流信息映射到每域电流和,该每域电流和可以被馈送到DCU 204。域到相电流平均模块(DPCAM)514可以基于运行中PTR的数量执行每电压冲击(PTR)电流平均计算,并且将平均电流信息发送回XPT 104。在示例实施例中,DPCAM 514针对PTR相208中的每个运行中PTR相执行每冲击电流平均计算,其中,PTR相208中的任何一个可以包括在任何给定时间将电压从高电压降低到低电压的多于一个的电压冲击电路。

模拟电压电源(VCC_ANA)低压差调节器(LDO)516可以启用用于负载管芯102和XPT104中的模拟块的模拟电源轨。在各种实施例中,到负载域202的输入电压(例如,SOC CPU输入电压)可以是灵活的,其中基于可用性来实施高电压或低电压(LDO旁路)。

图6是示出根据各种实施例的示例XPT 104的简化框图。XPT 104包括高电压管芯,该高电压管芯包含VR功率驱动器级,VR功率驱动器级在本文也称为功率系或PTR,其被分组到相同的、独立的PTR相208中,该PTR相将VR输出功率(VR VCC_OUT)驱动到位于封装衬底108中的电感器106中。在各种实施例中,XPT 104包括具有多个PTR相208的高压块、以及具有XPT公共块602的低压块。在各种实施例中,XPT公共块602包括聚集来自XCU 206的数据并且相应地进行响应的电路。在许多实施例中,PTR相208包括VR 210的双极结型晶体管(BJT)或MOSFET开关。XPT 104的大小可以基于PTR相208的数量。因此,功率系管芯大小可以通过适当地添加或去除相而容易地被模块化或配置。在任何给定时间运行的PTR相208的数量可以基于电压冲击/相的数量,电压冲击/相的数量基于聚集电流要求来确定,聚集电流要求包括负载域202或DCU 204的数量和每域的电流要求,该信息从XCU 206接收。

XPT 104包括两个接口:用于XCU 206的一个接口,以及用于封装衬底108的另一个接口。与XCU 206,XPT 104可以传递模拟功率(例如,VCC_ANA)、复位、时钟、I2C(或其他标准串行协议)、灾难性故障信息。对XPT 104的所有PTR相208公共的该信息可以通过XPT公共块602来传递。诸如电流(IN/OUT)、相启用、操作模式、关闭等的每相信息可以通过适当的寄存器总线(例如,32位)直接发送到各个PTR相208。

与封装衬底108,XPT 104中的PTR相208中的每一个可以传递输入电压(VCC_IN),根据负载管芯102中的负载域202的功率消耗,可以通过多个VCC_IN轨从封装支撑件108供应该输入电压。在各种实施例中,调节相同负载域的所有相由相同VCC_IN轨馈送。每个域相组可以由不同的VCC_IN轨来馈送。PTR相208中的每一个可以将输出电压(VR VCC_OUT)形式的每相功率传递到单独的电感器106,电感器106通过负载管芯102中的XCU 206电耦接到负载域202。

在各种实施例中,XPT公共块602可以用于访问XPT 104中的适当寄存器,并且在诸如功率损耗、过热、过电压、过电流等灾难性故障的事件下生成或接收灾难性故障信号。作为I2C从块,XPT公共块602可以将通过I2C总线从XCU 206接收的信息转换到内部并行寄存器总线,该内部并行寄存器总线在XPT公共块602和各个PTR相208中本地访问所有的功率系管芯寄存器。XPT公共块602可以定位JTAG端点,将JTAG数据与I2C通信协议数据多路复用,以使得能够对XPT 104中的寄存器进行双重I2C/JTAG源访问。在各种实施例中,XPT公共块602可以使从XCU 206接收的安全关闭指示过载,并且将该信息驱动到PTR相208以关闭它们(例如,以避免烧坏管芯)。在一些实施例中,例如,可以向XCU 206发信号通知XPT 104中生成的灾难性故障,使得可以关闭对应的DCU 204。XPT公共块602可以实现其他公共功能,例如用于探测/测试的引脚,以及网络最终多路复用。

图7是根据示例实施例的用于多域多相VR的封装架构的简化截面图。负载管芯102和XPT 104可以并排地位于微电子组件700中。半导体桥702可以通过DTD互连118实现负载管芯102与XPT104之间的电耦接。半导体桥702可以嵌入在包括铜柱116的有机中介层704中,该铜柱提供到具有电感器106的封装衬底108的穿过连接(through-connection)。在一些实施例中,半导体桥702可以是无源的。在其他实施例中,半导体桥702可以包括诸如晶体管和二极管的有源部件。DTPS互连120可以提供中介层704与封装衬底108之间的电和机械耦接。中介层704与封装衬底108之间的底部填充物706可以为DTPS互连120提供热机械稳定性和可靠性。分布在负载管芯102、XPT 104和封装衬底108上的VR 210的各个部件之间的信号连接可以通过合适的互连118和120来完成。

图8是根据示例实施例的用于多域多相VR的另一封装架构的简化截面图。负载管芯102和XPT 104可以并排地位于微电子组件800中。负载管芯102和XPT 104可以利用DTPS互连120直接耦接到封装衬底108。管芯与封装衬底108之间的底部填充物706可以为DTPS互连120提供热机械稳定性和可靠性。电感器106可以设置在封装衬底108中。分布在负载管芯102、XPT 104和封装衬底108上的VR 210的各个部件之间的信号连接可以通过互连120来完成。

图9是根据示例实施例的用于多域多相VR的又一封装架构的简化截面图。负载管芯102和XPT 104可以并排地位于微电子组件900中。例如,在面板级扇出型封装架构中,负载管芯102和XPT 104可以附接到再分布面板902。再分布面板902可以包括通过在电介质材料(例如,玻璃纤维增强芯)上层压或旋涂并且通过激光钻孔和电镀创建导电过孔和线而形成在面板载体上的一组再分布层。再分布面板902中的合适过孔和导电迹线可以实现负载管芯102与XPT 104之间的电耦接。管芯组件可以利用DTPS互连120和填充在其间的空间中的合适的底部填充物706而附接到封装衬底108。电感器106可以设置在封装衬底108中。分布在负载管芯102、XPT 104和封装衬底108上的VR 210的各个部件之间的信号连接可以通过再分布面板902和互连120中的适当的过孔和导电迹线来完成。

在各种实施例中,本文中参考图1-9中的任何图讨论的任何特征可以与任何其他特征组合以形成具有如本文所述的一个或多个IC的封装,例如以形成修改的微电子组件100。上面描述了一些这样的组合,但是在各种实施例中,进一步的组合和修改是可能的。

图10是根据本公开内容的各种实施例的制造微电子组件100的示例方法1000的流程图。尽管图10示出了以特定顺序执行的各种操作,但是这仅仅是说明性的,并且可以适当地重新排序和/或重复本文讨论的操作。此外,在不脱离本公开内容的范围的情况下,也可以执行未示出的附加处理。此外,可以根据本公开内容修改本文关于图10讨论的操作中的各种操作,以制造本文公开的其他微电子组件100。

在1002,可以提供具有一个或多个负载域202的负载管芯102。在1004,对应于负载域202的DCU 204可以共同定位在负载管芯102上。在一些实施例中,每个DCU对应于不同的负载域。在其他实施例中,若干负载域可以一起分组为成组负载域302,并且可以提供共享成组电流信息304的单独DCU。在1006,XCU 206可以共同定位在负载管芯102中。在1008,可以提供具有PTR相208的XPT 104。在1010,可以在封装衬底108中提供电感器106。在1012,可以耦接DCU 204、XCU 206、XPT 104和电感器106以生成VR 210。

在一些实施例中,耦接DCU 204、XCU 206、XPT 104和电感器106可以包括:在DCU204处,(例如,通过数字FE 410)将数字VID码转换为表示特定负载域处的期望电压电平的模拟电压,并且当期望电压电平不同于在特定负载域处测量的实际电压电平时,(例如,由CPS 404)生成电压误差信号,(例如,由PWM 402)生成用于调节PTR相驱动器的PWM定相脉冲,(例如,由CSX 414)处理来自PTR相208的电流感测信息;以及(例如,由数字FE 410)对模拟数据进行数字化以用于遥测和调试。

在一些实施例中,耦接DCU 204、XCU 206、XPT 104和电感器106可以包括:利用合适的互连将负载管芯102、XPT 104和电感器106电连接在封装(例如,微电子组件100)中。在一些实施例中,互连包括负载管芯102与XPT 104之间的DTD互连118、XPT 104与封装衬底108之间的DTPS互连120、以及负载管芯102与包括电感器106的封装衬底108之间的中介层(例如,模制化合物114)中的铜柱116。在一些其他实施例中,互连包括在负载管芯102与XPT104之间的DTD互连118、在XPT 104与封装衬底108之间的DTPS互连120、以及在负载管芯102与包括电感器106的封装衬底108之间的XPT 104中的TSV 109。在一些其他实施例中,互连包括电耦接负载管芯102和XPT 104的再分布面板902中的导电过孔和迹线、以及再分布面板902与封装衬底108之间的DTPS互连120。在一些其他实施例中,互连包括在负载管芯102与封装衬底108之间以及在XPT 104与封装衬底108之间的DTPS互连120。

尽管方法1000的操作在图10中以每个操作一次并且以特定顺序示出,但是操作可以以任何合适的顺序执行并且根据需要重复。例如,可以并行地执行一个或多个操作以基本上同时制造多个IC封装。在另一示例中,可以以不同的顺序执行操作以反映特定IC封装的结构,在该IC封装中可以包括如本文所述的一个或多个微电子组件100。许多其他变化也是可能的,以实现微电子组件100的期望结构。

此外,图10中所示的操作可以被组合或者可以包括比所描述的更多的细节。此外,图10所示的方法1000还可以包括与制造本文所述的微电子组件的其他部件或可以包括如本文所述的微电子组件的任何设备相关的其他制造操作。例如,方法1000可以包括各种清洁操作、表面平坦化操作(例如,使用CMP)、用于表面粗糙化的操作、根据需要包括阻挡层和/或粘附层的操作、和/或用于将如本文所述的封装并入IC部件、计算设备或任何期望的结构或设备中或与其结合的操作。

图11是根据本公开内容的各种实施例的操作XCU 206的示例方法1100的流程图。在1102,XCU 206从XPT 104接收关于输入电压(例如,VCC_ANA、VCC_IN)和PTR相208(例如,数量、灾难性故障信号等)的信息。在1104,XCU 206从对应的DCU 204接收关于负载域202的信息(例如,负载域的数量、电流感测等)。在1106,XCU 206可以适当地将DCU 204映射到PTR相208。在各种实施例中,映射包括将PTR PDM配置位的值写入XCU寄存器504中。在1108,XCU206可以将每域信息传递到对应的DCU 204。在1110,XCU 206可以将每相信息传递到XPT104。在一些实施例中,PTR相208中的特定PTR相的每相信息包括与PTR相208中的该特定PTR相相关的启用、操作模式和关闭信号。在1112,XCU 206可以监视来自DCU 204和XPT 104的反馈信息(例如,电流感测、负载变化、相变化、灾难性故障信号等)。在各种实施例中,监视来自XPT 104的反馈信息包括:通过工业标准串行协议(例如,I2C)将数据传递到XPT 104中的低电压XPT公共块602。在一些实施例中,监视反馈信息还包括将复位和时钟值传递到XPT104。

本文所公开的封装(例如图1-9所示的任何实施例或本文所述的任何其他实施例)可以包括在任何合适的电子部件中。图12-14示出了可以与本文所公开的任何IC封装一起使用或包括本文所公开的任何IC封装的封装、组件和设备的各种示例。

图12是根据本文公开的任何实施例的可以包括IC封装的示例IC封装2200的侧视截面图。在一些实施例中,IC封装2200可以是系统级封装(SiP)。

如图12所示,封装支撑件2252可以由绝缘体(例如,陶瓷、内建膜、其中具有填充物颗粒的环氧树脂膜等)形成,并且可以具有在第一面2272与第二面2274之间、或第一面2272上的不同位置之间、和/或第二面2274上的不同位置之间延伸穿过绝缘体的导电路径。这些导电路径可以采取例如以上参考图1讨论的包括线路和/或过孔的任何互连结构个的形式。

封装支撑件2252可以包括穿过封装支撑件2252耦接到导电路径2262的导电触点2263,从而允许管芯2256和/或中介层2257内的电路装置电耦接到导电触点2264中的各个导电触点2264(或耦接到封装支撑件2252中所包括的其他设备,未示出)。

IC封装2200可以包括经由中介层2257的导电触点2261、第一级互连2265和封装支撑件2252的导电触点2263耦接到封装支撑件2252的中介层2257。图12中所示的第一级互连2265是焊料凸块,但是可以使用任何合适的第一级互连2265,例如焊料凸块、焊料柱或接合线。

IC封装2200可以包括经由管芯2256的导电触点2254、第一级互连2258、以及中介层2257的导电触点2260耦接到中介层2257的一个或多个管芯2256。导电触点2260可以穿过中介层2257耦接到导电路径(未示出),从而允许管芯2256内的电路装置电耦接到导电触点2261中的各个导电触点2261(或电耦接到中介层2257中所包括的其他设备,未示出)。图12中所示的第一级互连2258是焊料凸块,但是可以使用任何合适的第一级互连2258,例如焊料凸块、焊料柱、或接合线。如本文所用,“导电触点”可以指导电材料(例如,金属)的用作不同部件之间的界面的部分;导电触点可以凹入部件的表面、与部件的表面齐平或者远离部件的表面延伸,并且可以采取任何合适的形式(例如,导电焊盘或插座)。

在一些实施例中,底部填充材料2266可以围绕第一级互连2265设置在封装支撑件2252与中介层2257之间,并且模制物2268可以围绕管芯2256和中介层2257设置并且与封装支撑件2252接触。在一些实施例中,底部填充材料2266可以与模制物2268相同。可以用于底部填充材料2266和模制物2268的示例材料是环氧树脂(在合适的情况下)。第二级互连2270可以耦接到导电触点2264。图12所示的第二级互连2270是焊球(例如,用于球栅阵列布置),但是可以使用任何合适的第二级互连2270(例如,引脚栅阵列布置中的引脚或连接盘栅阵列布置中的连接盘)。第二级互连2270可以用于将IC封装2200耦接到另一部件,例如电路板(例如,主板)、中介层、或另一IC封装,如本领域中已知的以及如以下参考图13所讨论的。

在各种实施例中,任何管芯2256可以包括本文所述的VR 210的部分。在IC封装2200包括多个管芯2256的实施例中,IC封装2200可以被称为多芯片封装(MCP)。管芯2256可以包括用于执行任何期望功能的电路装置。例如,除了包括如本文所述的VR 210的部件的一个或多个管芯2256之外,一个或多个管芯2256可以是逻辑管芯(例如,硅基管芯),一个或多个管芯2256可以是存储器管芯(例如,高带宽存储器)等。在一些实施方式中,至少一些管芯2256可以不包括本文所述的VR 210的部件。

尽管图12中所示的IC封装2200是倒装芯片封装,但是可以使用其他封装架构。例如,IC封装2200可以是BGA封装,例如嵌入式晶圆级球栅阵列(eWLB)封装。在另一示例中,IC封装2200可以是晶圆级芯片尺寸封装(WLCSP)或面板扇出(FO)封装。尽管在IC封装2200中示出了两个管芯2256,但是IC封装2200可以包括任何期望数量的管芯2256。IC封装2200可以包括附加的无源部件,例如设置在封装支撑件2252的第一面2272或第二面2274上方、或者中介层2257的任一面上的表面安装电阻器、电容器和电感器。更一般地,IC封装2200可以包括本领域已知的任何其他有源或无源部件。

在一些实施例中,IC封装2200中可以不包括中介层2257;相反,管芯2256可以通过第一级互连2265直接耦接到第一面2272处的导电触点2263。

图13是IC设备组件2300的截面侧视图,该IC设备组件可以包括具有根据本文公开的任何实施例的一个或多个微电子组件200的部件。IC设备组件2300包括设置在电路板2302(其可以是例如主板)上方的多个部件。IC设备组件2300包括设置在电路板2302的第一面2340和电路板2302的相对的第二面2342上方的部件;一般地,部件可以设置在面2340和2342中的一个或两个上方。特别地,IC设备组件2300的部件中的任何合适的部件可以包括根据本文公开的任何实施例的一个或多个微电子组件200中的任何微电子组件;例如,下面参考IC设备组件2300讨论的任何IC封装可以采取上面参考图12讨论的IC封装2200的任何实施例的形式。

在一些实施例中,电路板2302可以是包括多个金属层的PCB,多个金属层通过绝缘体层彼此分离并且通过导电过孔互连。任何一个或多个金属层可以以期望的电路图案形成,以在耦接到电路板2302的部件之间传送电信号(可选地与其他金属层结合)。在其他实施例中,电路板2302可以是非PCB封装支撑件。

图13示出了在一些实施例中,IC设备组件2300可以包括通过耦接部件2316耦接到电路板2302的第一面2340的中介层上封装结构(package-on-interposer structure)2336。耦接部件2316可以将中介层上封装结构2336电和机械地耦接到电路板2302,并且可以包括焊球(如图所示)、插座的凸出和凹入部分、粘合剂、底部填充材料和/或任何其他合适的电和/或机械耦接结构。

中介层上封装结构2336可以包括通过耦接部件2318耦接到中介层2304的IC封装2320。耦接部件2318可以取决于期望的功能而采取任何合适的形式,例如上面参考耦接部件2316讨论的形式。在一些实施例中,IC封装2320可以是或包括IC封装2200,例如,如上文参考图12所描述的。在一些实施例中,IC封装2320可以包括至少一个本文所述的VR 210。VR210没有在图13中具体示出,以免使附图混乱。

尽管图13中示出了单个IC封装2320,但是多个IC封装可以耦接到中介层2304;实际上,附加的中介层可以耦接到中介层2304。中介层2304可以提供用于桥接电路板2302和IC封装2320的中间封装支撑件。一般地,中介层2304可以将连接再分布到更宽的间距或者将连接重新布线到不同的连接。例如,中介层2304可以将IC封装2320耦接到耦接部件2316的BGA,以用于耦接到电路板2302。

在图13所示的实施例中,IC封装2320和电路板2302附接到中介层2304的相对侧;在其他实施例中,IC封装2320和电路板2302可以附接到中介层2304的同一侧。在一些实施例中,三个或更多个部件可以通过中介层2304互连。

中介层2304可以由环氧树脂、玻璃纤维增强环氧树脂、陶瓷材料或诸如聚酰亚胺的聚合物材料形成。在一些实施方式中,中介层2304可以由交替的刚性或柔性材料形成,其可以包括与上述用于半导体衬底的材料相同的材料,例如硅、锗和其他III-V族和IV族材料。中介层2304可以包括金属互连2308和包括TSV 2306的过孔2310。中介层2304还可以包括嵌入式设备2314,包括无源设备和有源设备两者。这些设备可以包括但不限于电容器、去耦电容器、电阻器、电感器、熔丝、二极管、变压器、传感器、静电放电(ESD)设备和存储器设备。诸如射频(RF)设备、功率放大器、功率管理设备、天线、阵列、传感器和微机电系统(MEMS)设的更复杂设备也可以形成在中介层2304上。中介层上封装结构2336可以采用本领域已知的任何中介层上封装结构的形式。

在一些实施例中,IC设备组件2300可以包括通过耦接部件2322耦接到电路板2302的第一面2340的IC封装2324。耦接部件2322可以采用上文参考耦接部件2316讨论的任何实施例的形式,并且IC封装2324可以采用上文参考IC封装2320讨论的任何实施例的形式。

在一些实施例中,IC设备组件2300包括通过耦接部件2328耦接到电路板2302的第二面2342的堆叠式封装结构(package-on-package structure)2334。堆叠式封装结构2334可以包括通过耦接部件2330耦接在一起的IC封装2326和IC封装2332,使得IC封装2326设置在电路板2302与IC封装2332之间。耦接部件2328和2330可以采用上述耦接部件2316的任何实施例的形式,并且IC封装2326和/或2332可以采用上述IC封装2320的任何实施例的形式。堆叠式封装结构2334可以根据本领域已知的任何堆叠式封装结构来配置。

图14是根据本文所公开的任何实施例的可以包括具有一个或多个IC封装的一个或多个部件的示例计算设备2400的框图。例如,计算设备2400的部件中的任何合适部件可以包括微电子组件,该微电子组件包括根据本文公开的任何实施例的VR 210的部件。在另一示例中,计算设备2400的部件中的任何一个或多个可以包括IC封装2200的任何实施例(例如,如图12所示)。在又一示例中,计算设备2400的部件中的任何一个或多个可以包括IC设备组件2300(例如,如图13中所示)。

图14中示出了包括在计算设备2400中的多个部件,但是这些部件中的任何一个或多个可以被省略或复制,以适合于应用。在一些实施例中,包括在计算设备2400中的一些或所有部件可以附接到一个或多个主板。在一些实施例中,在单个SoC管芯上制造一些或所有这些部件。

另外,在各种实施例中,计算设备2400可以不包括图14中所示的一个或多个部件,但是计算设备2400可以包括用于耦接到一个或多个部件的接口电路装置。例如,计算设备2400可以不包括显示设备2406,但是可以包括显示设备2406可以耦接到的显示设备接口电路装置(例如,连接器和驱动器电路装置)。在另一组示例中,计算设备2400可以不包括音频输入设备2418或音频输出设备2408,但是可以包括音频输入设备2418或音频输出设备2408可以耦接到的音频输入或输出设备接口电路装置(例如,连接器和支持电路装置)。

计算设备2400可以包括处理设备2402(例如,一个或多个处理设备)。如本文所使用的,术语“处理设备”或“处理器”可以指处理来自寄存器和/或存储器的电子数据以将该电子数据转换成可以存储在寄存器和/或存储器中的其他电子数据的任何设备或设备的一部分。处理设备2402可以包括一个或多个数字信号处理器(DSP)、ASIC、CPU、GPU、密码处理器(在硬件内执行密码算法的专用处理器)、服务器处理器或任何其他合适的处理设备。计算设备2400可以包括存储器2404,其本身可以包括一个或多个存储器设备,例如易失性存储器(例如,动态随机存取存储器(DRAM))、非易失性存储器(例如,只读存储器(ROM))、闪存存储器、固态存储器、和/或硬盘驱动器。在一些实施例中,存储器2404可以包括与处理设备2402共享管芯的存储器。该存储器可以用作高速缓冲存储器并且可以包括嵌入式动态随机存取存储器(eDRAM)或自旋转移矩磁性随机存取存储器(STT-MRAM)。

在一些实施例中,计算设备2400可以包括通信芯片2412(例如,一个或多个通信芯片;注意,术语“芯片”、“管芯”和“IC管芯”在本文中可互换使用)。例如,通信芯片2412可以被配置用于管理用于向和从计算设备2400传输数据的无线通信。术语“无线”及其派生词可以用于描述可以通过使用经调制的电磁辐射经由非固体介质来传递数据的电路、设备、系统、方法、技术、通信信道等。该术语并不意味着相关联的设备不包括任何导线,尽管在一些实施例中它们可能不包括。

通信芯片2412可以实施多种无线标准或协议中的任何一种,包括但不限于电气和电子工程师协会(IEEE)标准,包括Wi-Fi(IEEE 802.11系列)、IEEE 802.16标准(例如,IEEE802.16-2005修订版)、长期演进(LTE)项目以及任何修订版、更新版和/或修正版(例如,高级LTE项目、超移动宽带(UMB)项目(也称为“3GPP2”)等)。兼容IEEE 802.16的宽带无线接入(BWA)网络通常被称为WiMAX网络,WiMAX网络是代表微波接入全球互操作的首字母缩写词,其是通过IEEE802.16标准的一致性和互操作性测试的产品的认证标志。通信芯片2412可以根据全球移动通信系统(GSM)、通用分组无线业务(GPRS)、通用移动电信系统(UMTS)、高速分组接入(HSPA)、演进HSPA(E-HSPA)或LTE网络来操作。通信芯片2412可以根据增强型数据速率GSM演进(EDGE)、GSM EDGE无线接入网(GERAN)、通用陆地无线接入网(UTRAN)或演进型UTRAN(E-UTRAN)来操作。通信芯片2412可以根据码分多址(CDMA)、时分多址(TDMA)、数字增强无绳电信(DECT)、演进数据优化(EV-DO)及其派生物、以及被指定为3G、4G、5G及更高版本的任何其他无线协议来操作。在其他实施例中,通信芯片2412可以根据其他无线协议来操作。计算设备2400可以包括天线2422,以便于无线通信和/或接收其他无线通信(例如AM或FM无线电传输)。

在一些实施例中,通信芯片2412可以管理有线通信,例如电、光或任何其他合适的通信协议(例如,以太网)。如上所述,通信芯片2412可以包括多个通信芯片。例如,第一通信芯片2412可以专用于诸如Wi-Fi或蓝牙的较短距离无线通信,并且第二通信芯片2412可以专用于诸如全球定位系统(GPS)、EDGE、GPRS、CDMA、WiMAX、LTE、EV-DO或其他的较长距离无线通信。在一些实施例中,第一通信芯片2412可以专用于无线通信,并且第二通信芯片2412可以专用于有线通信。

计算设备2400可以包括电池/电源电路装置2414。电池/电源电路装置2414可以包括一个或多个能量存储设备(例如,电池或电容器)和/或用于将计算设备2400的部件耦接到与计算设备2400分离的能量源(例如,AC线路电源)的电路装置。

计算设备2400可以包括显示设备2406(或如上所述的对应的接口电路装置)。显示设备2406可以包括任何视觉指示器,例如,诸如平视显示器、计算机监视器、投影仪、触摸屏显示器、液晶显示器(LCD)、发光二极管显示器或平板显示器。

计算设备2400可以包括音频输出设备2408(或如上所述的对应的接口电路装置)。音频输出设备2408可以包括生成可听指示符的任何设备,例如扬声器、耳机或耳塞。

计算设备2400可以包括音频输入设备2424(或如上所述的对应的接口电路装置)。音频输入设备2424可以包括生成表示声音的信号的任何设备,例如麦克风、麦克风阵列或数字乐器(例如,具有乐器数字接口(MIDI)输出的乐器)。

计算设备2400可以包括GPS设备2416(或如上所述的对应的接口电路装置)。GPS设备2416可以与基于卫星的系统通信,并且可以接收计算设备2400的位置,如本领域已知的。

计算设备2400可以包括其他输出设备2410(或如上所述的对应的接口电路装置)。其他输出设备2410的示例可以包括音频编解码器、视频编解码器、打印机、用于向其他设备提供信息的有线或无线发射机、或附加存储设备。

计算设备2400可以包括其他输入设备2420(或如上所述的对应的接口电路装置)。其他输入设备2420的示例可以包括加速计、陀螺仪、罗盘、图像捕捉设备、键盘、光标控制设备(例如,鼠标、指示笔、触摸板)、条形码读取器、快速响应(QR)码读取器、任何传感器、或射频识别(RFID)读取器。

计算设备2400可以具有任何期望的形状因子,例如手持式或移动计算设备(例如,蜂窝电话、智能电话、移动互联网设备、音乐播放器、平板计算机、膝上型计算机、上网本计算机、超级本计算机、个人数字助理(PDA)、超移动个人计算机等)、台式计算设备、服务器或其他联网计算部件、打印机、扫描仪、监视器、机顶盒、娱乐控制单元、车辆控制单元、数码相机、数字视频记录器或可穿戴计算设备。在一些实施例中,计算设备2400可以是处理数据的任何其他电子设备。

以下段落提供了本文所公开的实施例的各种示例。

示例1提供了一种微电子组件,包括:第一IC管芯(例如,102),具有电负载电路(例如,202)、第一控制电路(例如,204)和第二控制电路(例如,206);第二IC管芯,具有电耦接到第一IC管芯的功率系(PTR)相电路(例如,208);以及封装衬底(例如,108)中的电感器(例如,106),电感器电耦接到封装内的第一IC管芯和第二IC管芯。第一控制电路调节去往对应电负载电路的功率,第二控制电路将第一控制电路与PTR相电路进行映射,PTR相电路控制去往电感器的功率,并且第一控制电路、第二控制电路、PTR相电路和电感器一起操作来用作VR(例如,210),VR被配置为在第一电压下从封装衬底接收功率,并且在第二电压下将功率输送到电负载电路,第一电压高于第二电压。

示例2提供了示例1的微电子组件,其中,电感器包括MIL电感器。

示例3提供了示例1-2中任一项的微电子组件,其中,PTR相电路被配置为在第一电压下操作。

示例4提供了示例3的微电子组件,其中,第二IC管芯还包括被配置为在第二电压下操作的公共块电路(例如,602)。

示例5提供了示例4的微电子组件,其中,公共块电路被配置为使用标准串行协议与第二控制电路接口连接。

示例6提供了示例4-5中任一项的微电子组件,其中,第二IC管芯中的公共块电路被配置为:当在PTR相电路中检测到灾难性故障时生成信号,并且将信号发送到第一IC管芯上的第二控制电路。

示例7提供了示例1-6中任一项的微电子组件,其中,PTR相电路包括半导体开关,半导体开关被配置为接通或关断以控制对电感器的功率供应。

示例8提供了示例1-7中任一项的微电子组件,其中,PTR相电路是相同的并且彼此独立。

示例9提供了示例1-8中任一项的微电子组件,其中,第二控制电路将第一控制电路中的各个第一控制电路映射到PTR相电路中的一个或多个PTR相电路。

示例10提供了示例1-9中任一项的微电子组件,其中,电负载电路利用公共成组电流而成组一起,并且对应的第一控制电路被配置为共享关于公共成组电流的信息。

示例11提供了示例1-10中任一项的微电子组件,其中:第一IC管芯利用DTD互连(例如,118)来耦接到第二IC管芯的第一侧,并且第二IC管芯在与第一侧相对的第二侧上利用DTPS互连(例如,120)来耦接到封装衬底。

示例12提供了示例11的微电子组件,其中,第二IC管芯中的TSV(例如,109)将第一IC管芯电耦接到封装衬底。

示例13提供了示例11-12中任一项的微电子组件,其中,在第一IC管芯与封装衬底之间的有机绝缘体(例如,114)中的铜柱(例如,116)将第一IC管芯电耦接到封装衬底。

示例14提供了示例11-13中任一项的微电子组件,其中,第一IC管芯和第二IC管芯被包封在模制化合物(例如,114)中。

示例15提供了示例1-14中任一项的微电子组件(例如,图9),其中,第一IC管芯与第二IC管芯并排,并且第一IC管芯通过再分布面板(例如,902)的第一侧上的导电过孔和迹线电耦接到第二IC管芯,再分布面板在与第一侧相对的第二侧上利用DTPS互连(例如,120)来电耦接到封装衬底。

示例16提供了示例1-15中任一项的微电子组件(例如,图7),其中:第一IC管芯与第二IC管芯并排,并且第一IC管芯通过中介层(例如,704)中的半导体桥(例如,702)电耦接到第二IC管芯,第一IC管芯和第二IC管芯在半导体桥的第一侧上利用DTD互连(例如,118)来耦接到半导体桥,并且中介层在半导体桥的与第一侧相对的第二侧上利用DTPS互连(例如,120)来耦接到封装衬底。

示例17提供了示例1-16中任一项的微电子组件,其中:第一IC管芯与第二IC管芯并排(例如,图8),并且第一IC管芯通过封装衬底中的导电迹线和过孔电耦接到第二IC管芯,第一IC管芯和第二IC管芯利用DTPS互连来耦接到封装衬底。

示例18提供了示例1-17中任一项的微电子组件,其中,使用第一工艺制造第一IC管芯,并且使用与第一工艺不同的第二工艺制造第二IC管芯。

示例19提供了一种位于IC管芯中的控制电路(例如,206),包括(例如,图5):映射模块(例如,502);寄存器(例如,504);数字控制模块(例如,506);模拟控制模块(例如,516);用于另一IC管芯的第一接口;以及用于IC管芯中的DCU的第二接口。另一IC管芯包括PTR相,DCU调节IC管芯中的对应负载域,映射模块使用存储在寄存器中的映射信息将DCU映射到PTR相,数字控制模块调节DCU的操作,并且模拟控制模块调节去往IC管芯中的模拟电路的功率。

示例20提供了示例19的控制电路,其中,映射信息包括PDM配置位,PDM配置位包括与映射到DCU中的特定DCU的PTR相中的特定PTR相、DCU的数量和PTR相的数量有关的标识信息。

示例21提供了示例19-20中任一项的控制电路,其中,PTR相中的特定一个PTR相映射到DCU中的一个或多个DCU。

示例22提供了示例19-21中任一项的控制电路,其中,PTR相中的至少一个PTR相不映射到DCU中的任何一个DCU。

示例23提供了示例19-22中任一项的控制电路,其中,PTR相不存储关于它们映射到的DCU中的任何一个DCU的标识信息。

示例24提供了示例19-23中任一项的控制电路,其中,DCU中的特定一个DCU映射到PTR相中的一个或多个PTR相。

示例25提供了示例19-24中任一项的控制电路,其中,DCU不存储关于它们映射到的PTR相中的任何一个PTR相的标识信息。

示例26提供了示例19-25中任一项的控制电路,其中,IC管芯与另一IC管芯之间的所有电耦接都通过第一接口。

示例27提供了示例19-26中任一项的控制电路,其中,第一接口包括:第一通道,被配置为传递另一IC管芯中的电路所共用的信息;以及第二通道,被配置为传递另一IC管芯中的PTR相中的每一个PTR相所特有的信息。

示例28提供了示例19-27中任一项的控制电路,其中,映射模块被配置为:从DCU接收每域信息,使用映射信息将每域信息转换为每相输入,以及通过第一接口将每相输入发送到另一管芯中的PTR相中的相关一个PTR相。

示例29提供了示例28的控制电路,其中,DCU中的特定一个DCU的每域信息包括:PWM定相脉冲;要启用的PTR相;对应负载域所需PTR相的操作模式;以及关闭信号。

示例30提供了示例28-29中任一项的控制电路,其中,到PTR相中的特定一个PTR相的每相输入包括:与PTR相中的特定一个PTR相相关的启用、操作模式和关闭信号。

示例31提供了示例19-30中任一项的控制电路,其中,数字控制模块(例如,506)被配置为:从PTR相接收每相信息,使用映射信息将每相信息转换为每域输入,以及通过第二接口将每域输入发送到DCU中的相关一个DCU。

示例32提供了示例31的控制电路,其中,每域输入包括:连接的PTR相的数量;要启用DCU中的相关一个DCU;以及域电流信息。

示例33提供了示例19-32中任一项的控制电路,其中,寄存器对于写入命令和读取命令是可访问的。

示例34提供了示例19-33中任一项的控制电路,还包括具有功能接口和测试接口的模块(例如,508),其中,功能接口被配置为耦接到CR总线,并且测试接口包括JTAG/TAP。

示例35提供了示例34的控制电路,其中,CR总线包括32位寄存器。

示例36提供了示例34-35中任一项的控制电路,还包括转换模块(例如,510),其被配置为将在CR总线上接收的数据转换成工业标准串行协议,其中,使用工业标准串行协议将转换的数据发送到另一管芯。

实施例37提供了实施例36的控制电路,其中,工业标准串行协议是I2C。

示例38提供了示例19-37中任一项的控制电路,还包括电流感测电路(例如,512),其被配置为:对来自根据映射信息映射到DCU的PTR相的电流求和;以及将电流和信息发送到DCU。

示例39提供了示例38的控制电路,还包括电流平均电路(例如,514),其被配置为基于电流和信息对每个运行中PTR相执行每冲击电流平均计算,其中,运行中PTR相中的任何一个可以包括将电压从第一电压降低到第二电压的多于一个电压冲击电路。

示例40提供了示例19-39中任一项的控制电路,其中,模拟控制模块包括LDO。

示例41提供了一种方法(例如,图10的1000),包括:提供具有负载域的第一IC管芯(例如,1002);将域控制器共同定位在第一IC管芯中(例如,1004);将功率系管芯控制器共同定位在第一IC管芯中(例如,1006);提供具有功率系相的第二IC管芯(例如,1008);在封装衬底中提供电感器(例如,1010);以及在封装中将域控制器、功率系管芯控制器、功率系相和电感器进行耦接以生成VR(例如1012)。

示例42提供了示例41的方法,其中,耦接包括在第一IC管芯中的功率系管芯控制器处(例如,图11的1100)进行以下操作:从第二IC管芯接收关于输入电压和功率系相的信息(例如,1102);从域控制器接收关于负载域的信息(例如,1104);将域控制器映射到功率系相中的特定功率系相(例如,1106);将每域信息传递到域控制器(例如,1108);将每相信息传递到第二IC管芯(例如,1110);以及监视来自域控制器和第二IC管芯的反馈信息(例如,1112)。

示例43提供了示例42的方法,其中,映射包括将功率系PDM配置位的值写入功率系管芯控制器中的寄存器中。

示例44提供了示例42-43中任一项的方法,其中,功率系相中的特定一个功率系相的每相信息包括与PTR相中的特定一个PTR相相关的启用、操作模式和关闭信号。

示例45提供了示例42-44中任一项的方法,其中,监视来自第二IC管芯的反馈信息包括:通过工业标准串行协议将数据传递到第二IC管芯中的低电压公共块电路。

示例46提供了示例42-45中任一项的方法,其中,监视反馈信息包括:将复位和时钟值传递到第二IC管芯。

示例47提供了示例42-46中任一项的方法,其中,耦接还包括在第一IC管芯中的域控制器处进行以下操作:将数字VID码转换为表示在特定负载域处的期望电压电平的模拟电压;当期望电压电平不同于在特定负载域处测量的实际电压电平时,生成电压误差信号;生成用于调节功率系相驱动器的PWM定相脉冲;处理来自功率系相的电流感测信息;以及对模拟数据进行数字化以用于遥测和调试。

示例48提供了示例41-47中任一项的方法,还包括将负载域耦接为共享公共成组电流的成组负载域,其中,具有功率系相的多个功率系管芯耦接到第一IC管芯,功率系管芯中的各个功率系管芯由第一IC管芯中的单独功率系管芯控制器控制。

示例49提供了示例41-48中任一项的方法,其中,耦接包括利用合适的互连在封装中将第一IC管芯、第二IC管芯和电感器进行电连接。

示例50提供了示例49的方法,其中,互连包括:第一IC管芯与第二IC管芯之间的DTD互连、第二IC管芯与封装衬底中的电感器之间的DTPS互连、以及第一IC管芯与封装衬底中的电感器之间的中介层中的铜柱。

示例51提供了示例49-50中任一项的方法,其中,互连包括:第一IC管芯与第二IC管芯之间的DTD互连、第二IC管芯与封装衬底中的电感器之间的DTPS互连、以及第一IC管芯与封装衬底中的电感器之间的第二IC管芯中的TSV。

示例52提供了示例49-51中任一项的方法,其中,互连包括:将第一IC管芯与第二IC管芯进行电耦接的再分布面板中的导电过孔和迹线,以及再分布面板与封装衬底之间的DTPS互连。

示例53提供了示例49-52中任一项的方法,其中,互连包括:第一IC管芯与封装衬底之间以及第二IC管芯与封装衬底之间的DTPS互连。

以上对本公开内容的所示实施方式的描述,包括摘要中所描述的,不是旨在是详尽无遗的或将本公开内容限制为所公开的精确形式。虽然本文出于说明性目的描述了本公开内容的具体实施方式和示例,但是如相关领域的技术人员将认识到的,在本公开内容的范围内各种等效修改是可能的。

- 多相电压调节器及用于操作多相电压调节器的方法

- 多相电压调节器及用于操作多相电压调节器的方法