一种基于存储迭代的非规则LDPC码的译码实现方法及系统

文献发布时间:2023-06-19 18:32:25

技术领域

本发明涉及通信技术领域,尤其涉及一种基于存储迭代的非规则LDPC码的译码实现方法及系统。

背景技术

低密度校验码(LowDensityParityCheckCode,LDPC)码是RobertG.Gallager在1962年提出的,直到1999年MacKay和Wilberg重新发现了LDPC码的优秀性能,才引起了编码领域专家和学者们的广泛关注。非规则LDPC码由具有不同列重和不同行重的奇偶校验矩阵所确定的,其泰勒图中变量节点和校验节点具有不同的度,大量实验已经证明,长随机非规则码的性能可以逼近香农极限,而采用迭代的译码算法使得非规则LDPC码可以接近香农极限的性能。由于LDPC译码器易于并行实现,能提供高吞吐率,因此被多个标准使用,目前,LDPC码的技术已应用于CMMB、DTMB、DVB-S2、DVB-T2、ATSC3.0和4G等标准的通信系统中。

非规则LDPC码以其可以逼近香农极限的优势,广泛应用于通信领域,在卫星导航接收机中,使用非规则LDPC译码器进行译码,会极大程度的提高接收机对弱信号的接收能力,但是目前,如何利用非规则LDPC码校验矩阵的特点,实现译码器的快速迭代处理是一个亟需解决的技术问题。

发明内容

本发明的目的是提供一种基于存储迭代的非规则LDPC码的译码实现方法及系统,以解决如何根据非规则LDPC码校验矩阵的特点,对行列校验矩阵及其索引值进行预存储,进而实现非规则LDPC译码器的快速迭代译码处理的技术问题。

本发明是采用以下技术方案实现的:一种基于存储迭代的非规则LDPC码的译码实现方法,包括如下步骤:

S1:初始化存储器值,设置最大迭代译码次数N;

S2:校验节点更新,解交织后的数据经过列矩阵和行索引矩阵处理,写入变量节点存储器中,当写满数据后,开始执行校验节点更新过程,每个校验节点根据接收到与之关联的变量节点信息,计算反馈给对应校验节点的信息;

S3:变量节点更新,变量节点接收到与之关联的校验节点传回的信息后,与初始信息融合,计算每个变量节点需要反馈的信息同时计算校验和进行硬判决。

进一步的,步骤S2具体包括如下子步骤:

S21:将变量节点存储器读出的数据分两路处理,一路复制到存储器1中,另一路进行异或处理和比较判断;

S22:读取存储器1的数据,并实时进行比较判断;

S23:判断是否达到最大迭代次数N,并跳转至变量节点更新。

进一步的,步骤S21具体为:将变量节点存储器读出的数据分两路处理,其中,将一部分读出的数据复制到存储器1中保存;将另一部分读出的数据进行异或和比较判断处理。

进一步的,所述异或和比较判断处理具体包括:求累积校验和,求存储器读出数据的绝对值,求存储器读出数据的极值及其对应的地址。

进一步的,步骤S22具体为:读取存储器1的数据,锁存读出数据的符号和地址,将读出的数据与极值比较,并判断存储器1读出数据的地址和极值对应的地址是否相等,选择极值中的最小值或次小值更新校验节点。

进一步的,步骤S23具体为:判断是否达到最大迭代次数N,计算校验和,并产生校验和标志,跳转到变量节点更新。

进一步的,步骤S3具体包括如下子步骤:

S31:将校验节点更新的值写入存储器2中;

S32:将校验节点存储器读出的数据与初值融合累积;

S33:判决校验和输出译码结果。

进一步的,步骤S31具体为:将校验节点更新的值复制到存储器2当中。

进一步的,步骤S33具体为:判决校验和输出译码结果,如果校验和不为零,将和差运算结果经行矩阵和列索引矩阵处理,写入变量节点存储器中,此时便完成了变量节点的更新过程,同时迭代次数加一。

一种基于存储迭代的非规则LDPC码的译码实现系统,包括初始化模块、校验节点更新模块和变量节点更新模块,其中,所述初始化模块用以初始化存储器值,设置最大迭代译码次数N;所述校验节点更新模块用以对解交织后经列矩阵和行索引矩阵的数据处理,执行校验节点更新过程,每个校验节点根据接收到与之关联的变量节点信息,计算反馈给对应校验节点的信息;所述变量节点更新模块用以将变量节点接收到与之关联的校验节点传回的信息后,与初始信息融合,并计算每个变量节点需要反馈的信息同时计算校验和进行硬判决。

本发明的有益效果在于:本发明根据非规则LDPC码校验矩阵的特点,对行列校验矩阵及其索引值进行预存储,利用可编程阵列逻辑并行处理和存储的优势实现校验节点和变量节点的快速更新完成译码器的迭代,同时该方法可以有效提高接收机对弱信号的接收能力。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图示出的结构获得其他的附图。

图1为本发明流程图。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。通常在此处附图中描述和示出的本发明实施例的组件可以以各种不同的配置来布置和设计。

应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

下面结合附图,对本发明的一些实施方式作详细说明。在不冲突的情况下,下述的实施例及实施例中的特征可以相互组合。

实施例1:

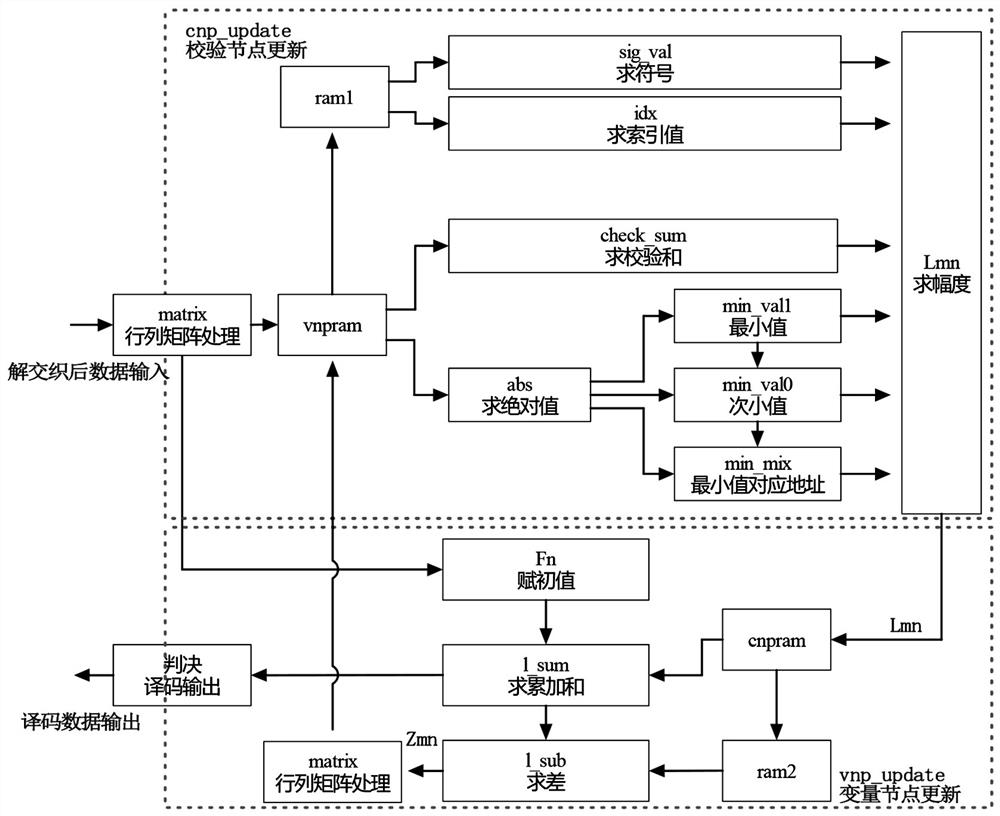

参阅图1,一种基于存储迭代的非规则LDPC码的译码实现方法,包括如下步骤:

初始化存储器vnpram,初始化状态期间根据列校验矩阵存储器ROM的数据作为初始化存储器的读地址,将初始化数据存入存储器vnpram中,完成数据的解交织。

校验节点更新,解交织后的数据经过列矩阵和行索引矩阵处理,写入变量节点存储器中,当写满数据后,开始执行校验节点更新过程,具体包括如下子步骤:

从存储器vnpram读出的数据分两路处理,一部分将读出的数据复制到存储器ram1中保存,ram1相当于缓存;另一部分将读出的数据进行处理,包括求累积校验和,求存储器读出数据的绝对值,求存储器读出数据的极值及其对应的地址。

读取存储器ram1的数据,锁存ram1读出数据的符号和地址,将ram1读出的数据和最小值、次小值比较。如果存储器ram1读出的数据地址和最小值对应的地址相等,那么幅度Lmn取次小值;如果存储器ram1读出的数据地址和最小值对应的地址不等,那么幅度Lmn取最小值,并且将求取的Lmn值写入校验节点存储器cnpram中。

判断是否到最大迭代次数N,判断校验和是否为零,并跳转到变量节点更新。

变量节点更新,将存储器cnpram读出的数据进行求和运算以及比较判决,具体包括如下子步骤:

将Lmn值复制到存储器ram2缓存当中。

将存储器cnpram读出的数据与初值Fn融合累积。

判决校验和输出译码:如果此时校验节点更行中校验和为零或到达最大迭代次数N,则判断求和结果l_sum值,如果l_sum为正值,则译码为1,如果l_sum为负值,则译码为0。

如果校验和不为0,则将累加结果l_sum与存储器ram2读出的数作差,将作差的结果l_sub经过行矩阵和列索引矩阵处理,写入变量节点存储器vnpram中,此时便完成了变量节点的更新过程,同时迭代次数加一。

一种基于存储迭代的非规则LDPC码的译码实现系统,用以实现上述所述的基于存储迭代的非规则LDPC码的译码实现方法,该系统包括初始化模块、校验节点更新模块和变量节点更新模块,其中,所述校验节点更新模块用以对解交织后经列矩阵和行索引矩阵的数据处理,执行校验节点更新过程,每个校验节点根据接收到与之关联的变量节点信息,计算反馈给对应校验节点的信息;所述变量节点更新模块用以将变量节点接收到与之关联的校验节点传回的信息后,与初始信息融合,并计算每个变量节点需要反馈的信息同时计算校验和进行硬判决。

本发明根据非规则LDPC码校验矩阵的特点,对行列校验矩阵及其索引值进行预存储,利用可编程阵列逻辑并行处理和存储的优势实现校验节点和变量节点的快速更新完成译码器的迭代,同时该方法可以有效提高接收机对弱信号的接收能力。

需要说明的是,对于前述的实施例,为了简单描述,故将其都表述为一系列的动作组合,但是本领域技术人员应该知悉,本申请并不受所描述的动作顺序的限制,因为依据本申请,某一些步骤可以采用其他顺序或者同时进行。其次,本领域技术人员也应该知悉,说明书中所描述的实施例属于优选实施例,所涉及的动作并不一定是本申请所必须的。

上述实施例中,描述了本发明的基本原理和主要特征和本发明的优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的只是说明本发明的原理,在不脱离本发明精神和范围的前提下,本领域人员所进行的改动和变化不脱离本发明的精神和范围,则都应在本发明所附权利要求的保护范围内。

- 一种基于存储迭代的QC-LDPC码的译码实现方法及系统

- 基于加权的非规则LDPC码线性规划译码方法