高纯度半绝缘单晶碳化硅晶片与碳化硅晶体

文献发布时间:2023-06-19 13:48:08

技术领域

本申请关于一种半绝缘单晶碳化硅晶体,特别是一种具备硅空缺的高纯度半绝缘单晶碳化硅晶体。

背景技术

半导体材料历经三个发展阶段,第一代是硅(Si)、锗(Ge)等基础功能材料;第二代开始进入由二种以上元素组成的化合物半导体材料,以砷化镓(GaAs)、磷化铟(InP)等为代表;第三代则是氮化镓(GaN)、碳化硅(SiC)等化合物半导体材料。第三代半导体材料属于宽能带隙材料,具有高频、耐高电压、耐高温等优势,且导电性、散热性佳,可降低能量耗损,元件体积相对较小,适合功率半导体应用。但是碳化硅的生产条件的控制难度大,导致碳化硅晶圆量产不易,直接影响了终端晶片与应用的发展。

物理气相传输法(physical vapor transport,PVT)是目前商业量产碳化硅晶体的主流方法。一般而言,利用物理气相传输法生长碳化硅晶体过程为先准备一晶种,将晶种置于坩埚中,所述坩埚包括一成长室、一固持器及一料源容器。固持器位于成长室上方,用于固定晶种,并设置于提供温度梯度的热场装置的相对冷端。料源容器位于成长室下方,用以容纳材料源,将碳化物原料盛装于料源容器内,将原料由固体升华为气体分子,将升华的气体分子传送并沉积晶种晶片上,使晶体生长。

为了制造高电阻率的碳化硅晶圆,现有技术主要是使用高纯度的原料以及深能级掺杂剂如钒掺杂来制作,在长晶过程中提供反应气体与浅能级导电元素结合并辅以外加制程,退火制程或中子轰击等使晶圆具备高阻率特性。但是当生长晶体尺寸增加后,先前技术的方法并不足以提供有效的大尺寸晶体均匀电阻率及良率,且会增加制程成本。此外,受限于长晶设备的因素,尺寸越大(例如大于4英寸)的晶体越难制作,良率也不易提升。

发明内容

鉴于上述现有技术的缺点,本申请提供一种大尺寸、高电阻率、低缺陷的碳化硅晶片,特别是一种具备硅空缺的高纯度半绝缘单晶碳化硅晶片。

根据本申请实施例公开的一种高纯度半绝缘单晶碳化硅晶片,包括单一多形体的单晶,所述高纯度半绝缘单晶碳化硅晶片内具有硅空缺,其中硅空缺浓度至少大于5E11cm^-3。

根据本申请公开的大尺寸的高纯度半绝缘单晶碳化硅晶体或硅晶片,其高电阻率特性由晶体本征缺陷(亦即硅空缺)浓度主导,于晶体生长过程中即可完成,晶圆不须额外进行退火制程或中子轰击制程。而在现有技术中,硅空缺浓度约为2E11cm^-3至3E11cm^-3。本申请公开的碳化硅晶体或碳化硅晶片的硅空缺浓度至少大于5E11cm^-3。

本申请的其他优点将搭配以下的说明和图式进行更详细的解说。

附图说明

此处所说明的附图用来提供对本申请的进一步理解,构成本申请的一部分,本申请的示意性实施例及其说明用于解释本申请,并不构成对本申请的不当限定。在附图中:

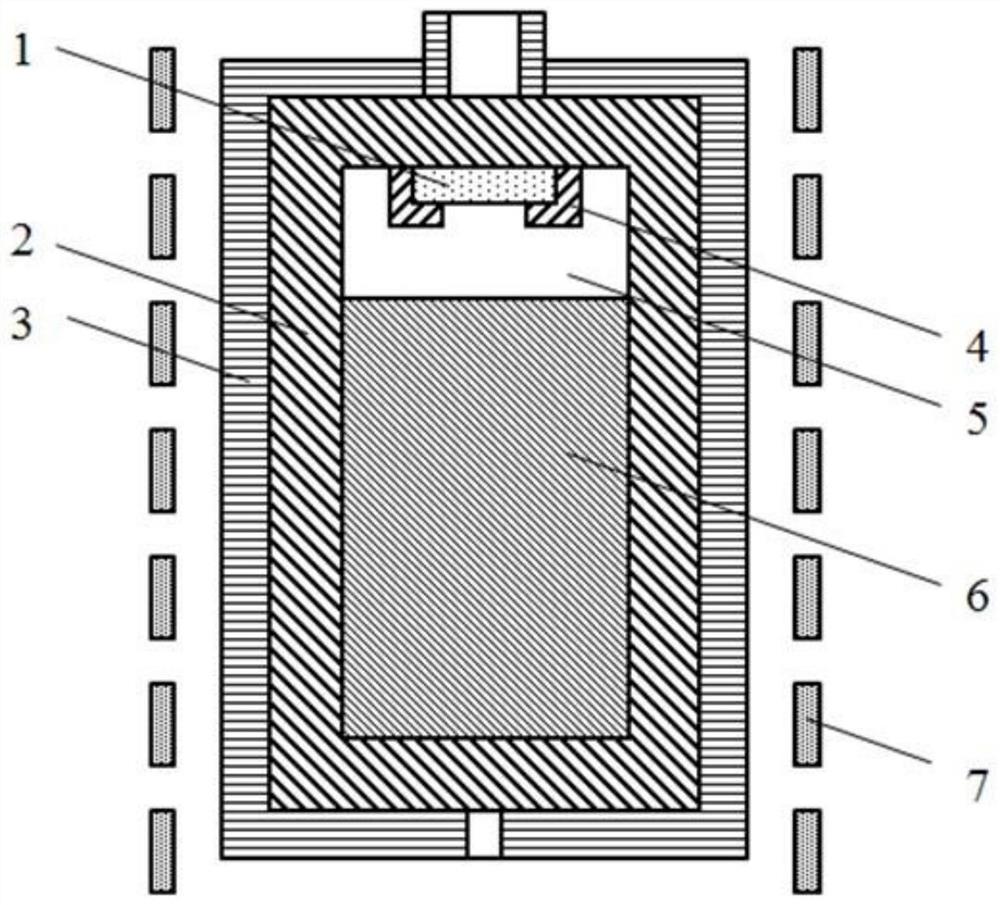

图1是本申请用于成长高纯度半绝缘单晶碳化硅晶体的成长系统的示意图;

图2是本申请的第一实施例中的高纯度半绝缘单晶碳化硅晶体的电阻率量测结果;

图3是本申请的第一实施例中的高纯度半绝缘单晶碳化硅晶体的微管密度;

图4是本申请的第一实施例中的高纯度半绝缘单晶碳化硅晶体的电子顺磁共振光谱;

图5是本申请的第二实施例中的高纯度半绝缘单晶碳化硅晶体的电阻率量测结果;

图6是本申请的第二实施例中的高纯度半绝缘单晶碳化硅晶体的微管密度;

图7是本申请的第二实施例中的高纯度半绝缘单晶碳化硅晶体的硅空缺;

图8是本申请的第二实施例的碳化硅晶片的硅空缺浓度;

图9是本申请的第二实施例的电子顺磁共振光谱;

图10是本申请的第二实施例的碳化硅晶片的光致发光光谱;

图11是本申请的第一实施例的PL/TO比率;

图12是本申请的第三实施例的高纯度半绝缘单晶碳化硅晶片的微管密度;以及

图13是本申请的第三实施例的高纯度半绝缘单晶碳化硅晶片的微管密度。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

必须了解的是,使用于本说明书中的“包含”、“包括”等词,用以表示存在特定的技术特征、数值、方法步骤、作业处理、元件以及/或组件,但并不排除可加上更多的技术特征、数值、方法步骤、作业处理、元件、组件,或以上的任意组合。

本申请公开一种大尺寸、高电阻率、低缺陷的高纯度半绝缘单晶碳化硅晶体,借由物理气相传输法(physical vapor transport,PVT)成长高纯度单晶系统中,利用控制高纯度长晶原料的Si/C比例及粒径分布,在晶体生长过程中控制长晶温度及时间,使系统中成为富碳(C-rich)环境。在浅能级导电元素稀缺的状态下,可以于晶体内生成本征缺陷硅空缺并控制硅空缺浓度。以本征缺陷做为其主导提升电阻率的机制,以达到半绝缘晶圆的电性范围。此外,因使用高纯度原料,于长晶过程中排除了杂质导入晶体的机率,因此本申请的本申请公开一种高纯度半绝缘单晶碳化硅晶体的微管缺陷低于3cm^-2。

此处所称的大尺寸是指直径至少4英寸,或者4英寸至6英寸的高纯度半绝缘碳化硅晶片(晶圆)。而高纯度是指长晶原料的纯度>99.99%。而高电阻率是指电阻率大于1E7ohm-cm或者在室温下至少1E7 ohm-cm。此外,说明书实施例中所指的晶体是指由碳化硅成长系统制作的碳化硅晶体,而对碳化硅晶体切割后的成品一般称作晶片或者晶圆(Wafer)。

本申请的高纯度半绝缘单晶碳化硅晶体或硅晶片的高电阻率特性由晶体或晶片内的本征缺陷(硅空缺)浓度主导,硅空缺在晶体生长过程中即可完成,不须额外进行退火制程或中子轰击制程,因此简化了制程。

参考图1,为本申请用于成长高纯度半绝缘单晶碳化硅晶体的成长系统的示意图。如图所示,成长系统包括有坩埚2、保温材3与加热器7。坩埚2用于使晶种1借由材料源6以长晶。保温材3设置于坩埚2外部,图式中绘示的保温材3是包覆于坩埚2的外部,但实际上也不一定要包覆于坩埚2外部,只要可以达到温度保持的效果即可,因此图示中仅为示意。加热器7用以提供热源,图示中绘示的加热器7是多个,也可以视系统配置,设置为一个,图示中的数量仅为示意说明,并非限制加热器7实际的设置数量。加热器7可以使用高周波加热器或者电阻式加热器,更具体的实施例中,加热器7可使用加热线圈或加热电阻丝(网)。

坩埚2的内部上方配置有固持器4,固持器4用于固定晶种1。坩埚2的内部下方可配置有料源6,晶种1与材料源6的空间可以做为碳化硅晶体的成长区5。放置晶种1的区域可以定义为晶种区,放置材料源6的区域可以定义为料源区。因此一个空的坩埚2内部是具有晶种区、料源区以及成长区。在一非限定的实施例中,坩埚2可为为石墨坩埚,保温材3可为石墨毯、多孔性绝热碳材。

在实施例中,晶种可使用碳化硅,本申请所使用的晶种可以是一厚度350μm以上,直径4英寸到6英寸以上单晶晶圆片,用以成长相对应尺寸以上的单晶晶体。单晶晶圆片可以是碳化硅。而坩锅内容纳材料源的料源区可使用碳化硅,料源形态可以是粉状、粒状、或块状,纯度为>99.99%,其结晶相可以为α相或β相,硅碳比例(Si/C ratio)可以为0.95至1.05。

透过坩埚2的构型、保温材3的构型及加热器7来控制坩埚2内温度分布、气氛流动及料源的升华过程,将升华的气体分子传送并沉积在晶种1(晶片)上而制成碳化硅晶体。在长晶过程的一实施例中,制程条件为控制坩埚内底部到晶种区的温差范围为10℃至300℃,氩气流量范围控制在100至1000sccm,压力范围控制在1至200torr,长晶时晶种温度范控制于2000℃至2270℃之间。其中最重要的是控制料源的纯度及型态、长晶温度区间、及长时间长晶,以先消耗系统内部导电元素后,当晶体内部本征缺陷生成后便可主导晶体电性表现。

根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其透过在晶种的生长表面上沉积含Si和C的蒸气物质生长,包括单一多形体的单晶,所述高纯度半绝缘单晶碳化硅晶体内具有硅空缺,其中硅空缺浓度至少大于5E11cm^-3,小于5E13cm^-3。在先前技术中,通常,碳化硅晶片中固有的硅空位浓度约为2E11cm^-3至3E11cm^-3。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其直径大于等于90毫米。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其直径小于等于200毫米。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其电阻率大于1E7 ohm-cm。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其微管密度少于每平方厘米3个。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其微管密度少于每平方厘米2个。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其微管密度少于每平方厘米1个。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其微管密度少于每平方厘米0.4个。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其微管密度少于每平方厘米0.1个。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体,其所包括的单一多形体的单晶选自碳化硅的3C,4H,6H和15R多形体,其中4H多形体是目前最优选的。晶片可以选自碳化硅的3C,4H,6H和15R多形体,其中4H多形体是目前最优选的。可获得的晶片是沿轴取向的,例如正轴取向,或者多种离轴取向的,比如(但不限于)选自4°和3.5°和2°。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体的厚度至少8mm。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶体的厚度为8mm至30mm。

以下的实施例说明本申请公开的高纯度半绝缘单晶碳化硅晶体的具体制程,借由物理气相传输法(physical vapor transport,PVT),使用高纯度长晶原料及部件、调整制程窗口及时间,除晶体生长过程中可以有效抑制杂质及导电元素进入晶体内,提升晶体品质,并辅以热场优化及制程控制,除使整体的长晶生长面更平坦外,并使晶体本征缺陷浓度提升,达到4到6英寸碳化硅晶体电阻率至1E7 ohm-cm。

第一个实施例说明利用图1的成长系统成长6英寸单晶碳化硅晶体。本实施例使用的起始原料为纯度99.99%以上的高纯度碳化硅粉料,平均粒度为5至20mm,初始硅/碳比为1,长晶后重新测量余料的硅/碳比下降至0.85。

搭配上述碳化硅料源以PVT法制备4H-SiC单晶晶体,生长制程于高温真空感应炉中的石墨坩埚进行,晶种长晶温度约为2100℃,系统使用Ar为载体气体,其系统长晶时压力约为5torr,生长时间为150小时。使用约500μm碳化硅单晶晶圆片作为晶种。

首先进行抽气制程,将4H-SiC晶种以固持器加以固定,然后进行抽气,以移除坩埚系统内的空气及其他杂质。抽完气后,进行加热制程。于加热制程中,加入惰性气体Ar作为辅助气体,并使用加热线圈加热整个系统,加热至约2100℃并持续长晶时间长达150小时。透过第一实施例的制程条件可产出晶体界面形状为凸界面的6英寸单晶碳化硅晶球,其晶体生长速率可达100-250μm/hr。

成长完后的晶体,可以对其进行电阻率、微管密度、杂质元素或者硅空缺的测量。将成长后的晶体进行切片研磨后得到晶片(或称晶圆),晶片不须退火即可进行电阻率量测。量测6英寸晶片中心140mm区域,电阻值皆大于1E7ohm-cm,如图2所示。

使用X光拓朴仪分析6英寸晶片,得到微管数量为10,整体6英寸微管密度为微管数量/6英寸晶圆面积,即为10/(7.5*7.5*3.1416)=10/176.75=0.056,亦即这个实施例的微管密度少于每平方厘米0.1个,如图3所示。

使用辉光放电质谱(Glow Discharge Mass Spectrometer,GDMS)及二次离子质谱(Secondary Ion Mass Spectroscopy,SIMS)分析6英寸晶圆的杂质元素,可得到如下表的结果,其中,N元素使用SIMS量测,其他元素使用GDMS量测,提供ppm及离子浓度两种单位,晶体内导电性杂质元素含量皆小于5E15cm^-3。

对6英寸晶圆进行电子顺磁共振(EPR)光谱分析,可得晶体中主要缺陷为硅空缺,如图4所示,利用光学检测的结果,图中所示的硅空缺浓度为5.22E11cm^-3至1.02E12cm^-3。

第二个实施例说明利用图1的成长系统成长4英寸单晶碳化硅晶球。本实施例使用的起始原料为纯度99.99%以上的高纯度碳化硅粉料,平均粒度为100至300μm,初始硅/碳比为1,长晶后重新测量余料的硅/碳比下降至0.87。

搭配上述碳化硅料源以PVT法制备4H-SiC单晶晶体,生长制程于高温真空感应炉中的石墨坩埚进行,而晶种长晶温度约为2180℃,系统使用Ar为载体气体,其系统长晶时压力约为5torr,生长时间为200小时,使用约500μm碳化硅单晶晶圆片作为晶种。

首先进行抽气制程,将4H-SiC晶种以固持器加以固定,然后进行抽气,以移除坩埚系统内的空气及其他杂质。抽完气后,进行加热制程。于加热制程中,加入惰性气体Ar作为辅助气体,并使用加热线圈加热,整个系统加热至约2100℃并持续长晶时间长达200小时。透过第二实施例的制程条件可产出晶体界面形状为凸界面的直径>140mm的单晶碳化硅晶球,其晶体生长速率可达100-250μm/hr。

成长完后的晶体,可以对其进行电阻率、微管密度、杂质元素或者硅空缺的测量。将成长后的晶体进行切片研磨后得到晶片(或称晶圆),晶片,不须退火即可进行电阻率量测。量测4英寸晶圆中心90mm区域,电阻值皆大于1E11ohm-cm,如图5所示。

使用X光拓朴仪分析4英寸晶片,得到微管数量为1,整体4英寸微管密度为微管数量/4英寸晶圆面积,即为1/(5*5*3.1416)=1/78.54=0.012,亦即这个实施例的微管密度少于每平方厘米0.02个,如图6所示。

使用GDMS及SIMS分析6英寸晶圆的杂质元素,可得到如下表的结果,晶体内导电性杂质元素含量皆小于1E16cm^-3。

对4英寸晶圆进行EPR分析,可得晶体中主要缺陷为硅空缺,如图7所示,利用光学检测的结果,图中所示的硅空缺浓度为7.07E12cm^-3。

我们将第二实施例的晶体中进行切割,并且对不同位置的切片进行硅空缺浓度分析,如图8所示。以图1的成长系统为例,较靠近晶种的切片编号为1,一共切割20片,亦即图8横轴的编号。由晶种至长晶表面,硅空缺浓度分别为1.9E12cm^-3、7E12cm^-3、5.9E12cm^-3、及3.3cm^-3。

根据前述实施例的高纯度半绝缘单晶碳化硅晶片,包括单一多形体的单晶,所述高纯度半绝缘单晶碳化硅晶片内具有硅空缺,其中硅空缺浓度至少大于5E11cm^-3,小于5E13cm^-3。

在一实施例中,根据前述实施例的高纯度半绝缘单晶碳化硅晶片,其直径大于等于90毫米。

在一实施例中,根据前述实施例的高纯度半绝缘单晶碳化硅晶片,其直径小于等于200毫米。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶片,其电阻率大于1E7 ohm-cm。

在一实施例中,根据前述实施例的高纯度半绝缘单晶碳化硅晶片,其微管密度少于每平方厘米3个。

在一实施例中,根据前述实施例的高纯度半绝缘单晶碳化硅晶片,其微管密度少于每平方厘米2个。

在一实施例中,根据前述实施例的高纯度半绝缘单晶碳化硅晶片,其微管密度少于每平方厘米1个。

在一实施例中,根据前述实施例的高纯度半绝缘单晶碳化硅晶片,其微管密度少于每平方厘米0.4个。

在一实施例中,根据前述实施例的高纯度半绝缘单晶碳化硅晶片,其微管密度少于每平方厘米0.1个。

在一实施例中,根据前述实施例成长系统所形成的高纯度半绝缘单晶碳化硅晶片,其所包括的单一多形体的单晶选自碳化硅的3C,4H,6H和15R多形体,其中4H多形体是目前最优选的。晶片可以选自碳化硅的3C,4H,6H和15R多形体,其中4H多形体是目前最优选的。可获得的晶片是沿轴取向的,例如正轴取向,或者多种离轴取向的,比如(但不限于)选自4°和3.5°和2°。

依据本申请的晶片适合用于高频功率器件,高功率器件,高温器件、光电子器件以及III族氮化物的沉积。

依据本申请的晶片适合作为单光子光源,亦即量子电脑的积体电路基板。

参考图9,展示了第二实施例的电子顺磁共振(EPR)光谱。将样品切成5.5cm×7mm的尺寸,并用9.70396×1E9 Hz的微波照射。在光谱中,碳化硅晶片在300K温度下在3460.70343G处产生零点。通过公式hυ=gμBB(h:普朗克常数,υ:频率;g:g因子;μB:Bohr磁子;B:磁场)进行计算后,实施例2编号11晶片的g因子为2.00343,这意味着硅空位包含在碳化硅中(硅空位的信号为g=2.0032±0.0004)。

参考图10,是第二实施例的晶片的光致发光光谱。某些拉曼信号对掺杂浓度和空位浓度不敏感例如,横向-光学模式。对于785nm激光激发,在851nm波长处是LO模式,在838nm波长处是4H-SiC的TO模式。在图9中,实施例二19的光致发光与LO模式拉曼信号的比(比率(PL/LO))为5.1。因此,实施例二中的硅空位密度约为5.1÷0.7=7.29(×1E12cm^-3)。实际上,LO模式峰值的强度和波数受掺杂浓度的影响很大,并导致难以通过比率(PL/LO)来推测SiC的空位密度。为了测量不同的电阻率SiC,使用TO模式的光致发光信号来测量硅空位浓度,因为它在不同晶片中的稳定性和与光致发光相同的测量面积。在图9中,实施例二的光致发光和TO模式拉曼信号的比率(比率(PL/TO))为4.50。结果,可以通过以下公式计算4H-SiC中的硅空位密度:V_Si的密度=PL/TO×7.29÷4.47=PL/TO×1.63。PL/TO比率为所对应的激发光的峰值除以激发光谱中拉曼散射TO模态的峰值(840nm附近),由此计算可得单位晶格硅空缺致发光的硅空缺密度(1PL/TO→1.630*10^12/cm^3)。

同样的方式测试实施例一,其系列中的平均空位密度最大值为3.26×1E12cm^-3。

图11为第一实施例的PL/TO比率。以第一实施例为例,选定九个测量点,PL/TO比率如图所示,而ABCDEFGHI九个测量点的PL/TO比率、硅空缺浓度与电阻率数值如下表:

图12为本申请第三实施例,其直径为60mm,图13为本申请第四实施例,其直径为120mm,图12与图13显示微管密度(Micro-pipe density,MPD)。图示中将碳化硅晶片区分成多个方格,方格里的数字代表微管数量。第三实施例的微管数量为60,除以晶片面积,可以得到微管密度为2.1/cm^2。第三实施例的微管数量为56个,除以晶片面积,可以得到微管密度为0.5/cm^2。

本申请在高纯度长晶系统下,利用控制高纯度长晶原料的Si/C比例及粒径分布,在晶体生长过程中控制长晶温度及时间,使成长系统中成为富碳(C-rich)环境。在浅能级导电元素稀缺的状态下,可以于晶体内生成本征缺陷硅空缺并控制硅空缺浓度,以本征缺陷做为其主导提升电阻率的机制,以达到半绝缘晶圆的电性范围。

虽然图式中包含了以上描述的元件,但不排除在不违反发明的精神下,使用更多其他的附加元件,以达成更佳的技术效果。此外,虽然实施例中步骤采用指定的顺序来执行,但是在不违反发明精神的情况下,熟习此技艺人士可以在达到相同效果的前提下,修改这些步骤间的顺序,所以,本申请并不局限于仅使用如上所述的顺序。此外,熟习此技艺人士亦可以将若干步骤整合为一个步骤,或者是除了这些步骤外,循序或平行地执行更多步骤,本申请亦不因此而局限。

上面结合附图对本申请的实施例进行了描述,但是本申请并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本申请的启示下,在不脱离本申请宗旨和权利要求所保护的范围情况下,还可做出很多形式,均属于本申请的保护之内。