输出电路

文献发布时间:2024-04-18 19:44:28

技术领域

本发明涉及输出电路。

背景技术

作为与输出电路相关的技术,公知有以下的技术。例如在专利文献1中记载了输出缓冲电路,该输出缓冲电路具备使输入信号延迟一定的时间的延迟电路、使输入信号反转的反转电路以及输出缓冲。输出缓冲在导通电阻上具有可变电阻部分,通过可变电阻值的变更来变更预加重的量。

专利文献1:日本特开2009-164718号公报。

从输出端子输出高电平信号或者低电平信号的输出电路具有CMOS电路,该CMOS电路包含输出高电平信号的p沟道型晶体管(p-MOS)和输出低电平信号的n沟道型晶体管(n-MOS)。在CMOS电路的输出端(即,p-MOS的漏极和n-MOS的漏极)与输出端子之间设置有用于将输出阻抗调整为所希望的大小的电阻元件。根据上述结构的输出电路,高电平信号和低电平信号经由共用的电阻元件从输出端子输出。

例如,在电源线附加了某些电路的情况下,电源侧的阻抗比接地侧的阻抗大。在该情况下,有时很难通过共用地用于高电平信号和低电平信号的电阻元件进行输出阻抗的调整。例如,在USB2.0标准中,输出阻抗被设定为36Ω±8Ω,相对于该标准的容限有可能几乎没有。

发明内容

本发明是鉴于上述的点而完成的,目的在于,抑制高电平信号输出时的输出阻抗与低电平信号输出时的输出阻抗之差。

本发明的输出电路包含:输出端子,其输出高电平信号或者低电平信号;第一电阻元件,其一端与所述输出端子连接,供所述高电平信号通过;以及第二电阻元件,其一端与所述输出端子连接,供所述低电平信号通过。

根据本发明,能够抑制高电平信号输出时的输出阻抗与低电平信号输出时的输出阻抗之差。

附图说明

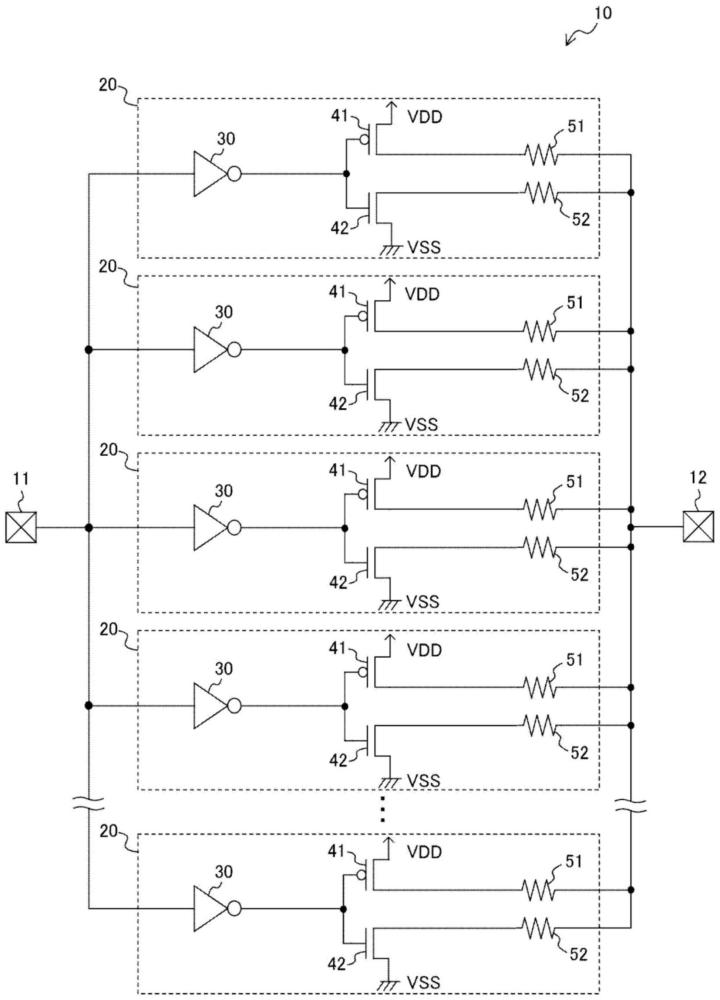

图1是表示本发明的第一实施方式的输出电路的结构的一例的图。

图2是表示比较例的输出电路的结构的一例的图。

图3是表示本发明的第二实施方式的输出电路的结构的一例的图。

图4是表示本发明的第三实施方式的输出电路的结构的一例的图。

附图标记的说明

10、10A、10B、10X…输出电路;11…输入端子;12…输出端子;20、20X…电路块;30…预驱动器;31…第一预驱动器;32…第二预驱动器;41…p-MOS;42…n-MOS;50、51、52…电阻元件;60…选择电路。

具体实施方式

以下,一边参照附图一边对本发明的实施方式进行说明。另外,在各附图中,对实质上相同或者等效的构成要素或者部分标注相同的参照附图标记。

[第一实施方式]

图1是表示本发明的第一实施方式的输出电路10的结构的一例的图。输出电路10具有:供输入信号输入的输入端子11、供与输入信号对应的高电平信号或者低电平信号输出的输出端子12、以及在输入端子11与输出端子12之间并联设置的多个电路块20。多个电路块20具有彼此相同的结构。多个电路块20分别具有预驱动器30、P沟道型晶体管41(以下,表述为p-MOS)、N沟道型晶体管42(表述为n-MOS)、电阻元件51以及电阻元件52。

预驱动器30的输入端与输入端子11连接,输出端与p-MOS41和n-MOS42的栅极连接。预驱动器30对p-MOS41和n-MOS42进行驱动。预驱动器30例如也可以具有CMOS逆变器的结构,输出使向输入端子11输入的输入信号的逻辑电平反转后的信号。

p-MOS41和n-MOS42的栅极彼此连接,构成CMOS电路。p-MOS41的源极与电源线VDD连接。p-MOS41的漏极与电阻元件51的一端连接。n-MOS42的源极与接地线VSS连接。n-MOS42的漏极与电阻元件52的一端连接。

p-MOS41在预驱动器30的输出信号为低电平的情况下处于导通状态,输出高电平信号,在预驱动器30的输出信号为高电平的情况下处于截止状态。n-MOS42在预驱动器30的输出信号为高电平的情况下处于导通状态,输出低电平信号,在预驱动器30的输出信号为低电平的情况下处于截止状态。p-MOS41为本发明的“第一晶体管”的一例。n-MOS42为本发明的“第二晶体管”的一例。

电阻元件51的一端与输出端子12连接,另一端与p-MOS41的漏极连接。从p-MOS41输出的高电平信号通过电阻元件51从输出端子12输出。电阻元件51在电路块20间可以彼此相同,也可以彼此不同。电阻元件52的一端与输出端子12连接,另一端与n-MOS42的漏极连接。从n-MOS42输出的低电平信号通过电阻元件52从输出端子12输出。电阻元件52在电路块20间可以彼此相同,也可以彼此不同。电阻元件51是本发明的“第一电阻元件”的一例。电阻元件52是本发明的“第二电阻元件”的一例。

在向输入端子11输入高电平的输入信号的情况下,在多个电路块20中的各个电路块中,p-MOS41处于导通状态。从p-MOS41中的各个输出的高电平信号经由电阻元件51中的各个电阻元件从输出端子12输出。

在将相当于p-MOS41的导通电阻的阻抗Z

Z

同样地,在将相当于n-MOS42的导通电阻的阻抗Z

Z

这里,图2是表示比较例的输出电路10X的结构的一例的图。在构成比较例的输出电路10X的电路块20X中的各个电路块中,p-MOS41的漏极与n-MOS42的漏极彼此连接,电阻元件50的一端与输出端子12连接,另一端与p-MOS41的漏极与n-MOS42的漏极的连接点连接。在比较例的输出电路10X中,从p-MOS41输出的高电平信号以及从n-MOS42输出的低电平信号都通过共用的电阻元件50从输出端子12输出。比较例的输出电路10X具有附加于电源线VDD的电路100。电路100例如也可以是对供给到电源线VDD的电源电压进行切换的开关电路。

在将相当于p-MOS41的导通电阻的阻抗Z

Z

同样地,在将相当于n-MOS42的导通电阻的阻抗Z

Z

根据比较例的输出电路10X,通过附加了电路100,从而电源侧的阻抗比接地侧的阻抗大。因此,有时很难通过共用地用于高电平信号和低电平信号的电阻元件50进行输出阻抗的调整。例如,在USB2.0标准中,输出阻抗被设定为36Ω±8Ω,相对于该标准的容限有可能几乎没有。

另一方面,根据本实施方式的输出电路10,供高电平信号通过的电阻元件51与供低电平信号通过的电阻元件52由不同的电阻元件构成。由此,能够独立地调整(1)式中的Z

[第二实施方式]

图3是表示本发明的第二实施方式的输出电路10A的结构的一例的图。输出电路10A具有选择电路60。选择电路60选择性地使多个电路块20分别包含的预驱动器30有效化。选择电路60通过对预驱动器30供给控制信号S

多个电路块20中的仅包含进行了有效化的预驱动器30的电路块20有效地发挥功能。即,通过预驱动器30的选择来设定电路块20的并联数。换言之,通过预驱动器30的选择来设定电阻元件51和电阻元件52的并联数,由此进行输出阻抗的调整。

例如,在高电平信号输出时,通过监视使施加给电源线VDD的电压变化的情况下的输出端子12处的输出电压和输出电流,能够计算高电平信号输出时的输出阻抗Z

根据本实施方式的输出电路10A,确定要进行有效化的预驱动器30的数量(即,电阻元件51和电阻元件52的并联数)以使如上述那样计算出的高电平信号输出时的输出阻抗Z

[第三实施方式]

图4是表示本发明的第三实施方式的输出电路10B的结构的一例的图。上述的第二实施方式的输出电路10A通过共用的预驱动器30来驱动构成CMOS电路的一对p-MOS41和n-MOS42。与此相对,第三实施方式的输出电路10B通过各自的预驱动器来驱动构成CMOS电路的一对p-MOS41和n-MOS42。即,输出电路10B在电路块20中的各个电路块中,具有驱动p-MOS41的第一预驱动器31以及驱动n-MOS42的第二预驱动器32。

输出电路10B具有选择电路60。选择电路60选择性地使多个电路块20分别包含的第一预驱动器31和多个第二预驱动器32有效化。第一预驱动器31的选择与第二预驱动器32的选择能够独立地进行。即,能够进行将某个电路块20的第一预驱动器31有效化而不将该电路块20的第二预驱动器32有效化这样的选择。

根据本实施方式的输出电路10B,能够通过第一预驱动器31的选择来设定电阻元件51的并联数,能够通过第二预驱动器32的选择来设定电阻元件52的并联数。即,能够独立地设定电阻元件51的并联数和电阻元件52的并联数。由此,能够使输出阻抗Z

在电阻元件51、52的电阻值各自在电路块20间彼此不同的情况下,通过分别确定要进行有效化的第一预驱动器31的组合与要进行有效化的第二预驱动器32的组合,能够使输出阻抗相对于标准的容限更大。

- 输出电路、包括输出电路的系统以及控制输出电路的方法

- 输出电路、包括输出电路的系统以及控制输出电路的方法