一种多模块产品内部低精度时钟的校准方法

文献发布时间:2023-06-19 13:49:36

技术领域

本发明涉及电子电路的测试调试技术领域,尤其涉及一种多模块产品内部低精度时钟的校准方法。

背景技术

随着物联网技术的发展,高集成化SOC方案得到了长足的发展,但对于功能较复杂的产品来说,依然存在着单个产品多控制器的情况:业务由主控芯片控制;数据安全由安全模块控制;网络通信由通信模组控制。而物联网产品中,通过串口进行数据交互较为通用,而串口的硬件协议中,是以自然时间为节拍,从而保证设置之间的正常通信。因此,就要求每个核心都需要一个准确的时钟信号以保证整个系统的时钟同步,从而达到稳定数据交互的结果。

当系统中需要的模块不具备高精度时钟时,系统的稳定性也跟着直线下降,特别是在高温或低温的环境下,因为模组时钟的温漂导致系统的崩溃。

中国专利文献CN102096372B公开了一种“卫星系统时钟基于总线方式的校准方法”。包括:低精度时钟用户通过串行数据总线和高精度时钟源相互连接,按照如下步骤进行校时:1)、低精度时钟用户生成本地的系统时钟参数TL,发送到高精度时钟源;2)、高精度时钟源接收时钟参数TL,同时生成时钟源实时时钟参数TH;相减后得到时差数据ΔT;修正固定时延得到时差数据ΔTlast;3)、低精度时钟用户取得时差数据ΔTlast,把时差数据ΔTlast加到低精度时钟用户的系统时钟上;4)、按照一定周期间隔重复进行步骤1),2),3)。上述技术方案应用高精度时钟源进行校准,成本高且需要增加额外器件使用不便。

发明内容

本发明主要解决原有的技术方案成本高且需要增加额外器件使用不便的技术问题,提供一种多模块产品内部低精度时钟的校准方法,通过外部中断功能检测高精度时钟模块发送出数据时的波形变化;低精度时钟模块使用内部高精度时钟对每次波形变化的时间间隔进行计时,通过检测每一次的变化间隔,再配合低精度时钟模块的内部时钟变化范围,从而计算出低精度时钟模块的内部时钟频率,从而修正串口的配置参数,使系统满足高度精准通信的目的。

本发明的上述技术问题主要是通过下述技术方案得以解决的:本发明包括以下步骤:

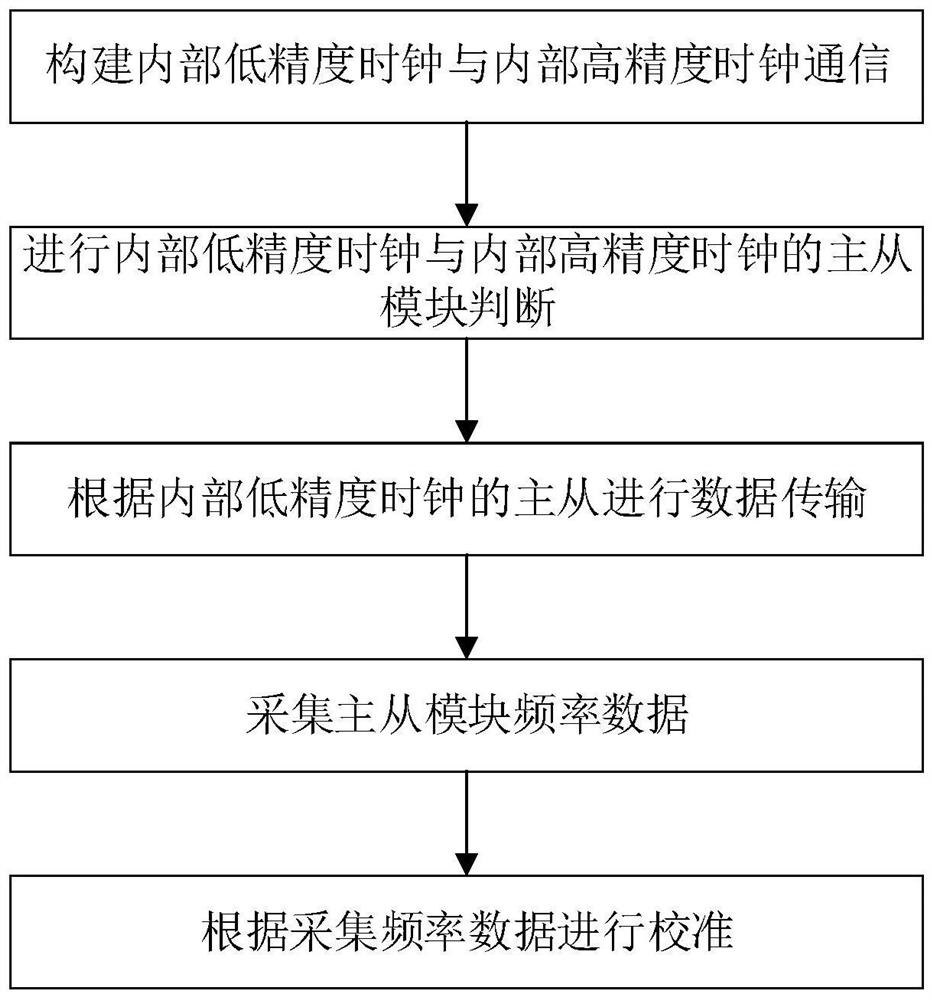

S1构建内部低精度时钟与内部高精度时钟通信;

S2进行内部低精度时钟与内部高精度时钟的主从模块判断;

S3根据内部低精度时钟的主从进行数据传输;

S4采集主从模块频率数据;

S5根据采集频率数据进行校准。

作为优选,所述的步骤S3进行内部低精度时钟的主从模块判断后,若内部低精度时钟为主模块,内部高精度时钟为从模块,则内部低精度时钟按不同波特率发送指令至从设备,通过扫频的方式尝试获得从模块的响应,利用从模块的响应波形,对主模块的内部时钟进行校准。当内部低精度时钟作为主模块时,利用从模块支持指令响应以及波特率偏差小于3%时即可正常通信的特性,低精度模块按不同波特率发送指令至从设备,通过扫频的方式尝试获得从模块的响应。

作为优选,所述的步骤S3进行内部低精度时钟的主从模块判断后,若内部低精度时钟为从模块,内部高精度时钟为主模块,则内部低精度时钟等待主模块发送数据,内部低精度时钟利用数据的波形对内部时钟进行校准。内部低精度时钟为从模块时,无需等待主模块反馈,直接利用数据的波形对内部时钟进行校准。

作为优选,所述的步骤S4采集主从模块频率数据包括:外部中断功能检测高精度时钟模块发送出数据时的波形变化,内部低精度时钟使用内部高精度时钟对每次波形变化的时间间隔进行计时。

作为优选,所述的步骤S5通信的波特率均由芯片的系统时钟通过分频产生,假设通信波特率为T时,波形变化的间隔时间为1/T秒。

作为优选,所述的步骤S5采用内部高精度时钟作为计时器,通过采集波形的变化计算每次变化花费的计时器时间,假设系统时钟为X,内部高精度时钟的分频比为n,若检测到波形变化的间隔部分计时器时间为t,那么内部高精度时钟频率为X/n,若波形变化的间隔部分计时时间为(1/(X/n))*t,此时间与1/T相同,因此得到等式

(1/(X/n))*t=1/T。

作为优选,所述的步骤S5从等式即可计算得出低精度芯片的系统时钟实际频率为:

X=(T*t)*n

即可将系统时钟根据X=(T*t)*n进行校准。

本发明的有益效果是:通过外部中断功能检测高精度时钟模块发送出数据时的波形变化;低精度时钟模块使用内部高精度时钟对每次波形变化的时间间隔进行计时,通过检测每一次的变化间隔,再配合低精度时钟模块的内部时钟变化范围,从而计算出低精度时钟模块的内部时钟频率,从而修正串口的配置参数,使系统满足高度精准通信的目的。

附图说明

图1是本发明的一种流程图。

图2是本发明的一种内部低精度时钟作为主模块的流程图。

图3是本发明的一种内部低精度时钟作为从模块的流程图。

图4是本发明的一种串口通信波形逻辑图。

具体实施方式

下面通过实施例,并结合附图,对本发明的技术方案作进一步具体的说明。

实施例:本实施例的一种多模块产品内部低精度时钟的校准方法,如图1所示,包括以下步骤:

S1构建内部低精度时钟与内部高精度时钟通信。

S2进行内部低精度时钟与内部高精度时钟的主从模块判断。

S3根据内部低精度时钟的主从进行数据传输。

如图2所示,进行内部低精度时钟的主从模块判断后,若内部低精度时钟为主模块,内部高精度时钟为从模块,利用从模块支持指令响应以及波特率偏差小于3%时即可正常通信的特性,则内部低精度时钟按不同波特率发送指令至从设备,通过扫频的方式尝试获得内部高精度时钟的响应,利用内部高精度时钟的响应波形,对主模块的内部时钟进行校准。

如图3所示,进行内部低精度时钟的主从模块判断后,若内部低精度时钟为从模块,内部高精度时钟为主模块,则内部低精度时钟等待内部高精度时钟发送数据,内部低精度时钟利用数据的波形对内部时钟进行校准。内部低精度时钟为从模块时,无需等待内部高精度时钟反馈,直接利用数据的波形对内部时钟进行校准。

S4采集主从模块频率数据。主从模块频率数据包括:外部中断功能检测高精度时钟模块发送出数据时的波形变化,内部低精度时钟使用内部高精度时钟对每次波形变化的时间间隔进行计时。

S5根据采集频率数据进行校准。

通信的波特率均由芯片的系统时钟通过分频产生,假设通信波特率为T时,波形变化的间隔时间,即图4波形中箭头部分为1/T秒。

采用内部高精度时钟作为计时器,通过采集波形的变化计算每次变化花费的计时器时间,假设系统时钟为X,内部高精度时钟的分频比为n,若检测到波形变化的间隔部分计时器时间为t,那么内部高精度时钟频率为X/n,若波形变化的间隔部分,即图4波形中箭头部分计时时间为(1/(X/n))*t,此时间与1/T相同,因此得到等式

(1/(X/n))*t=1/T。

从等式即可计算得出低精度芯片的系统时钟实际频率为:

X=(T*t)*n

即可将系统时钟根据X=(T*t)*n进行校准。

当产品包含多个模块,且个别模块均需要高精度时钟时,可以采用本方案减少部模块的高精度时钟,从而达到有效降低硬件成本的目的。

本文中所描述的具体实施例仅仅是对本发明精神作举例说明。本发明所属技术领域的技术人员可以对所描述的具体实施例做各种各样的修改或补充或采用类似的方式替代,但并不会偏离本发明的精神或者超越所附权利要求书所定义的范围。

尽管本文较多地使用了内部低精度时钟、内部高精度时钟等术语,但并不排除使用其它术语的可能性。使用这些术语仅仅是为了更方便地描述和解释本发明的本质;把它们解释成任何一种附加的限制都是与本发明精神相违背的。