时间数字转换装置、时间数字转换方法

文献发布时间:2023-06-19 13:49:36

技术领域

本申请涉及时间数字转换技术领域,具体涉及一种时间数字转换装置、时间数字转换方法。

背景技术

时间数字转换器(TDC,Time to Digital Convert)是基于高精度短时间间隔的一种测量装置,不论是电信通讯、芯片设计以及数字示波器等工程领域,还是原子物理、天文观测等理论研究,以及激光测距、卫星定位等航天军事技术领域均涉及到高精度的时间间隔测量。

然而,传统技术方案中时间数字转换器的时间结果容易受到计时停止信号的亚稳态影响,例如,如图1、图2所示,粗计数响应于测试信号中时钟信号clk的上升沿、计时开始信号start-trig的上升沿而开始粗计数,响应于测试信号中计时开始信号start-trig的下降沿而停止粗计数,如此可以获得粗计数结果Coarse-cnt即时钟信号clk的整数个周期;细计数响应于测试信号中计时开始信号start-trig的下降沿而开始细计数,响应于测试信号中计时停止信号stop-signal的上升沿而停止细计数,如此可以获得细计数结果Delay-chain-cnt即时钟信号clk的小数个周期,然后经过编码、计算后得到时间结果Rslt为粗计数结果Coarse-cnt与细计数结果Delay-chain-cnt之和。

其中,由于计时停止信号stop-signal为异步信号,响应于计时停止信号stop-signal的上升沿而停止计数时,时间数字转换器中的锁存过程容易出现亚稳态,致使时间结果Rslt出现错误。

需要注意的是,上述关于背景技术的介绍仅仅是为了便于清楚、完整地理解本申请的技术方案。因此,不能仅仅由于其出现在本申请的背景技术中,而认为上述所涉及到的技术方案为本领域所属技术人员所公知。

发明内容

本申请提供一种时间数字转换装置、时间数字转换方法,以缓解或者消除时间数字转换结果容易出现不准确或者错误的计数问题。

第一方面,本申请提供一种时间数字转换装置,其包括计时停止处理模块、同步模块、粗计时模块、细计时模块以及计算模块,计时停止处理模块用于根据计时停止信号、复位信号以及计时停止同步信号生成计时停止标志信号,计时停止标志信号的脉冲开始时间与计时停止信号的脉冲开始时间相同;同步模块与计时停止处理模块电性连接,用于根据时钟信号、复位信号以及计时停止标志信号生成计时停止同步信号;粗计时模块与同步模块电性连接,响应于计时开始信号的脉冲开始时间、时钟信号的一个脉冲开始时间而开始粗计时,且响应于计时停止同步信号的脉冲开始时间、时钟信号的另一个脉冲开始时间而停止粗计时,基于开始粗计时与停止粗计时之间的时钟信号的时钟数量得到粗计时结果;细计时模块与计时停止处理模块、同步模块电性连接,响应于计时停止标志信号的脉冲开始时间而开始细计时,响应于计时停止同步信号的脉冲开始时间而停止细计时,基于开始细计时与停止细计时之间的时钟信号的时钟数量得到细计时结果;计算模块与粗计时模块、细计时模块电性连接,用于根据时钟信号、粗计时结果与细计时结果的差值,确定时间数字转换装置的计时结果。

在其中一些实施方式中,计时停止处理模块包括第一触发器和或门,第一触发器的输入端接入高电位信号,第一触发器的触发端接入计时停止信号,第一触发器的正相输出端输出计时停止标志信号;或门的一输入端接入计时停止同步信号,或门的另一输入端接入复位信号,或门的输出端与第一触发器的复位端电性连接。

在其中一些实施方式中,同步模块包括至少一个触发器,至少一个触发器依次串联连接,至少一个触发器中第一个触发器的输入端与第一触发器的正相输出端电性连接,至少一个触发器中最后一个触发器的正相输出端与或门的一输入端电性连接,至少一个触发器的触发端均接入时钟信号,至少一个触发器的复位端均接入复位信号。

在其中一些实施方式中,同步模块包括第二触发器和第三触发器,第二触发器的输入端与第一触发器的正相输出端电性连接,第二触发器的触发端接入时钟信号,第二触发器的复位端接入复位信号;第三触发器的输入端与第二触发器的正相输出端电性连接,第三触发器的触发端接入时钟信号,第三触发器的复位端接入复位信号,第三触发器的同相输出端与或门的一输入端电性连接。

在其中一些实施方式中,细计时模块包括延时链单元、细计时锁存单元以及编码单元,延时链单元与计时停止处理模块的输出端电性连接,用于多级延时传输电位信号;细计时锁存单元与延时链单元、同步模块电性连接,用于根据计时停止同步信号锁存电位信号经过多级延时传输后的电位传输状态;编码单元与细计时锁存单元、计算模块电性连接,用于根据电位传输状态得到细计时结果。

在其中一些实施方式中,细计时模块包括细计时控制单元、延时链单元、细计时锁存单元以及编码单元,细计时控制单元与计时停止处理模块的输出端、同步模块的输出端电性连接,用于根据计时停止标志信号、计时停止同步信号输出对应的电位信号;延时链单元与细计时控制单元电性连接,用于多级延时传输电位信号;细计时锁存单元与延时链单元、同步模块电性连接,用于根据计时停止同步信号锁存电位信号经过多级延时传输后的电位传输状态;编码单元与细计时锁存单元、计算模块电性连接,用于根据电位传输状态得到细计时结果。

在其中一些实施方式中,延时链单元包括多个加法器,多个加法器依次串联连接,多个加法器中第一个加法器的第一输入端与细计时控制单元的输出端电性连接,多个加法器的第二输入端接入高电位信号,多个加法器的第三输入端接入低电位信号,多个加法器的求和输出端与细计时锁存单元电性连接,多个加法器中前一个加法器的进位输出端与多个加法器中下一个加法器的第一输入端电性连接;其中,每个加法器输入输出的数据均为二进制数据,加法器的求和输出端的输出结果为加法器的第一输入端接入的二进制数据、加法器的第二输入端接入的二进制数据以及加法器的第三输入端接入的二进制数据之和中的低位,加法器的进位输出端的输出结果为加法器的第一输入端接入的二进制数据、加法器的第二输入端接入的二进制数据以及加法器的第三输入端接入的二进制数据之和中的高位。

在其中一些实施方式中,细计时控制单元包括第一数字选择器和第二数字选择器,第一数字选择器的第一输入端接入高电位信号,第一数字选择器的第二输入端接入低电位信号,第一数字选择器的选择控制端与多个加法器中第一个加法器的输出端电性连接;第二数字选择器的第一输入端接入高电位信号,第二数字选择器的第二输入端与多个加法器中最后一个加法器的求和输出端电性连接,第二数字选择器的第三输入端与第一数字选择器的输出端电性连接,第二数字选择器的第一选择控制端与计时停止处理模块的输出端电性连接,第二数字选择器的第二选择控制端与同步模块的输出端电性连接。

在其中一些实施方式中,细计时控制单元包括第三数字选择器,第三数字选择器的第一输入端接入高电位信号,第三数字选择器的第二输入端与多个加法器中任一个加法器的输出端电性连接,第三数字选择器的选择控制端与计时停止处理模块的输出端电性连接。

在其中一些实施方式中,细计时锁存单元包括多个第四触发器,多个第四触发器的触发端与同步模块的输出端电性连接,多个第四触发器的复位端均接入复位信号,多个第四触发器的同相输出端与细计时锁存单元电性连接,一第四触发器的输入端与一加法器的求和输出端对应电性连接。

在其中一些实施方式中,细计时模块还包括计数单元,计数单元的复位端接入复位信号,计数单元的锁存端与同步模块的输出端电性连接,计数单元的输出端与计算模块电性连接,用于计算电位信号在多个加法器中传输的循环周期数量。

在其中一些实施方式中,计数单元包括第一计数器,第一计数器的复位端端接入复位信号,第一计数器的时钟端与多个加法器中任一加法器的求和输出端电性连接,第一计数器的输出端与计算模块电性连接,用于根据上升沿和下降沿进行计数以计算电位信号在多个加法器中传输的循环周期数量。

在其中一些实施方式中,计数单元包括第二计数器和第三计数器,第二计数器的复位端接入复位信号,第二计数器的时钟端与多个加法器中任一加法器的求和输出端电性连接,第二计数器的输出端与计算模块电性连接,用于根据上升沿进行计数以计算电位信号在多个加法器中传输的第一循环周期数量;第三计数器的复位端接入复位信号,第三计数器的时钟端与任一加法器的求和输出端电性连接,第三计数器的输出端与计算模块电性连接,用于根据取反后的上升沿进行计数以计算电位信号在多个加法器中传输的第二循环周期数量;其中,计算模块根据第一循环周期数量与第二循环周期数量之和得到循环周期数量。

在其中一些实施方式中,细计时模块还包括计数单元,计数单元的复位端接入复位信号,计数单元的时钟端与多个加法器中任一加法器的输出端电性连接,计数单元的锁存端与同步模块的输出端电性连接,计数单元的输出端与计算模块电性连接,用于计算电位信号在多个加法器中传输的循环周期数量。

在其中一些实施方式中,计数单元包括第一计数器,第一计数器的复位端端接入复位信号,第一计数器的时钟端与多个加法器中任一加法器的求和输出端电性连接,第一计数器的锁存端与同步模块的输出端电性连接,第一计数器的输出端与计算模块电性连接,用于根据上升沿和下降沿进行计数以计算电位信号在多个加法器中传输的循环周期数量。

在其中一些实施方式中,计数单元包括第二计数器和第三计数器,第二计数器的复位端接入复位信号,第二计数器的时钟端与多个加法器中任一加法器的求和输出端电性连接,第二计数器的锁存端与同步模块的输出端电性连接,第二计数器的输出端与计算模块电性连接,用于根据上升沿进行计数以计算电位信号在多个加法器中传输的第一循环周期数量;第三计数器的复位端接入复位信号,第三计数器的时钟端与任一加法器的求和输出端电性连接,第三计数器的锁存端与同步模块的输出端电性连接,第三计数器的输出端与计算模块电性连接,用于根据取反后的上升沿进行计数以计算电位信号在多个加法器中传输的第二循环周期数量;其中,计算模块根据第一循环周期数量与第二循环周期数量之和得到循环周期数量。

第二方面,本申请提供一种时间数字转换方法,其包括:根据计时停止信号、复位信号以及计时停止同步信号生成计时停止标志信号,计时停止标志信号的脉冲开始时间与计时停止信号的脉冲开始时间相同;根据时钟信号、复位信号以及计时停止标志信号生成计时停止同步信号;响应于计时开始信号的脉冲开始时间、时钟信号的一个脉冲开始时间而开始粗计时,且响应于计时停止同步信号的脉冲开始时间、时钟信号的另一个脉冲开始时间而停止粗计时,基于开始粗计时与停止粗计时之间的时钟信号的时钟数量得到粗计时结果;响应于计时停止标志信号的脉冲开始时间而开始细计时,响应于计时停止同步信号的脉冲开始时间而停止细计时,基于开始细计时与停止细计时之间的时钟信号的时钟数量得到细计时结果;以及根据时钟信号、粗计时结果与细计时结果的差值,确定时间数字转换装置的计时结果。

在其中一些实施方式中,根据计时停止信号、复位信号以及计时停止同步信号生成计时停止标志信号的步骤包括:构造第一触发器的输入端接入高电位信号、第一触发器的触发端接入计时停止信号;构造或门的一输入端接入计时停止同步信号、或门的另一输入端接入复位信号以及或门的输出端与第一触发器的复位端电性连接;以及配置第一触发器的正相输出端输出计时停止标志信号。

在其中一些实施方式中,根据时钟信号、复位信号以及计时停止标志信号生成计时停止同步信号的步骤包括:构造第二触发器的输入端与第一触发器的正相输出端电性连接,第二触发器的触发端接入时钟信号,第二触发器的复位端接入复位信号;构造第三触发器的输入端与第二触发器的正相输出端电性连接,第三触发器的触发端接入时钟信号,第三触发器的复位端接入复位信号,第三触发器的同相输出端与或门的一输入端电性连接;以及配置第三触发器的同相输出端输出计时停止同步信号。

本申请提供的时间数字转换装置、时间数字转换方法,通过计时停止处理模块输出的计时停止标志信号、同步模块输出的计时停止同步信号对应控制粗计时模块的粗计时结果、细计时模块的细计时结果,可以减小由于计时停止信号为异步信号所导致的亚稳态产生的概率,提高时间数字转换结果的准确性;同时,计算模块可以确定粗计时结果与细计时结果的差值为时间数字转换装置的计时结果,即使在时间数字转换过程中粗计时结果、细计时结果受到了亚稳态影响,通过粗计时结果与细计时结果的减法运算,也能够进一步抵消计时结果所受到的亚稳态影响,进而进一步提高了时间数字转换结果的准确性。

附图说明

下面结合附图,通过对本申请的具体实施方式详细描述,将使本申请的技术方案及其它有益效果显而易见。

图1为传统技术方案中时间数字转换器的结构示意图。

图2为图1所示时间数字转换器的时序示意图。

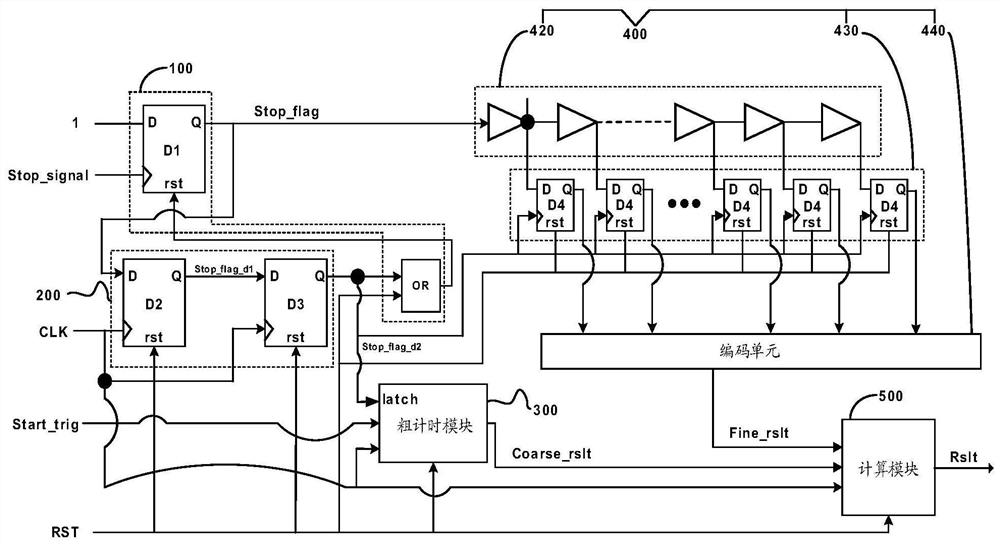

图3为本申请实施例提供的时间数字转换装置的第一种结构示意图。

图4为本申请实施例提供的触发器产生亚稳态的时序示意图。

图5为本申请实施例提供的延时链单元的流程示意图。

图6为本申请实施例提供的延时链单元的结构示意图。

图7为图3所示时间数字转换装置的时序示意图。

图8为本申请实施例提供的时间数字转换装置的第二种结构示意图。

图9为图8所示时间数字转换装置的时序示意图。

图10为图8中所示细计时控制单元的结构示意图。

图11为本申请实施例提供的时间数字转换装置的第三种结构示意图。

图12为图11中所示细计时控制单元的结构示意图。

图13为本申请实施例提供的计数单元的流程示意图。

图14为本申请实施例提供的计数单元的时序示意图。

图15为本申请实施例提供的时间数字转换方法的流程示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

请参阅图3至图14,如图3、图7或者图8、图9所示,本实施例提供了一种时间数字转换装置,其包括计时停止处理模块100、同步模块200、粗计时模块300、细计时模块400以及计算模块500,计时停止处理模块100用于根据计时停止信号Stop_signal、复位信号RST以及计时停止同步信号Stop_flag_d2生成计时停止标志信号Stop_flag,计时停止标志信号Stop_flag的脉冲开始时间与计时停止信号Stop_signal的脉冲开始时间相同,计时停止标志信号Stop_flag的脉冲持续时间小于计时停止信号Stop_signal的脉冲持续时间;同步模块200与计时停止处理模块100电性连接,用于根据时钟信号CLK、复位信号RST以及计时停止标志信号Stop_flag生成计时停止同步信号Stop_flag_d2,计时停止同步信号Stop_flag_d2的脉冲开始时间与计时停止标志信号Stop_flag的脉冲结束时间相同;粗计时模块300与同步模块200电性连接,响应于计时开始信号Start_trig的脉冲开始时间、时钟信号CLK的一个脉冲开始时间而开始粗计时,且响应于计时停止同步信号Stop_flag_d2的脉冲开始时间、时钟信号CLK的另一个脉冲开始时间而停止粗计时,基于开始粗计时与停止粗计时之间的时钟信号CLK的时钟数量得到粗计时结果Coarse_rslt;细计时模块400与计时停止处理模块100、同步模块200电性连接,响应于计时停止标志信号Stop_flag的脉冲开始时间而开始细计时,响应于计时停止同步信号Stop_flag_d2的脉冲开始时间而停止细计时,基于开始细计时与停止细计时之间的时钟信号CLK的时钟数量得到细计时结果;计算模块500与粗计时模块300、细计时模块400电性连接,用于根据时钟信号CLK、粗计时结果Coarse_rslt与细计时结果的差值,确定时间数字转换装置的计时结果。

可以理解的是,本实施例提供的时间数字转换装置,通过计时停止处理模块100输出的计时停止标志信号Stop_flag、同步模块200输出的计时停止同步信号Stop_flag_d2对应控制粗计时模块300的粗计时结果Coarse_rslt、细计时模块400的细计时结果,可以减小由于计时停止信号Stop_signal为异步信号所导致的亚稳态概率,提高时间数字转换结果的准确性;同时,计算模块500可以确定粗计时结果Coarse_rslt与细计时结果的差值为时间数字转换装置的计时结果,即使在时间数字转换过程中粗计时结果Coarse_rslt、细计时结果受到了亚稳态影响,通过粗计时结果Coarse_rslt与细计时结果的减法运算,也能够进一步抵消计时结果所受到的亚稳态影响,进而进一步提高了时间数字转换结果的准确性。

其中,图3所示的细计时结果也可以表征为图7所示的细计时结果Delay_chain_cnt。粗计时结果Coarse_rslt可以为时钟信号CLK的整数个时钟周期。细计时结果可以不包括时钟信号CLK的小数个时钟周期,也可以包括时钟信号CLK的小数个时钟周期,还可以包括时钟信号CLK的整数个时钟周期和时钟信号CLK的小数个时钟周期。

如图3所示,在其中一个实施例中,计时停止处理模块100包括第一触发器D1和或门OR,第一触发器D1的输入端接入高电位信号,第一触发器D1的触发端接入计时停止信号Stop_signal,第一触发器D1的正相输出端输出计时停止标志信号Stop_flag;或门OR的一输入端接入计时停止同步信号Stop_flag_d2,或门OR的另一输入端接入复位信号RST,或门OR的输出端与第一触发器D1的复位端电性连接。

可以理解的是,如此可以构造计时停止信号Stop_signal的上升沿与计时停止标志信号Stop_flag的上升沿位于同一时刻,计时停止标志信号Stop_flag的下降沿与计时停止同步信号Stop_flag_d2的上升沿位于同一时刻。

在其中一个实施例中,同步模块200包括至少一个触发器,至少一个触发器依次串联连接,至少一个触发器中第一个触发器的输入端与第一触发器D1的正相输出端电性连接,至少一个触发器中最后一个触发器的正相输出端与或门OR的一输入端电性连接,至少一个触发器的触发端均接入时钟信号CLK,至少一个触发器的复位端均接入复位信号RST。

可以理解的是,如此每经过一个触发器,计时停止标志信号Stop_flag被延时一个时间段,直至延时计时停止同步信号Stop_flag_d2的上升沿至计时停止标志信号Stop_flag的下降沿,然后根据计时结果的计算步骤即可得到计时结果。

在其中一个实施例中,同步模块200包括第二触发器D2和第三触发器D3,第二触发器D2的输入端与第一触发器D1的正相输出端电性连接,第二触发器D2的触发端接入时钟信号CLK,第二触发器D2的复位端接入复位信号RST;第三触发器D3的输入端与第二触发器D2的正相输出端电性连接,第三触发器D3的触发端接入时钟信号CLK,第三触发器D3的复位端接入复位信号RST,第三触发器D3的同相输出端与或门OR的一输入端电性连接。

如图3所示,在其中一个实施例中,如图3所示,在其中一个实施例中,细计时模块400包括延时链单元420、细计时锁存单元430以及编码单元440,延时链单元420与计时停止处理模块100的输出端电性连接,用于多级延时传输电位信号;细计时锁存单元430与延时链单元420、同步模块200电性连接,用于根据计时停止同步信号Stop_flag_d2锁存电位信号经过多级延时传输后的电位传输状态;编码单元440与细计时锁存单元430、计算模块500电性连接,用于根据电位传输状态得到细计时结果。

可以理解的是,如图4所示触发器的时序示意图,如果数据传输中时钟信号CLK不满足触发器的建立时间Tsu和保持时间Th,或者复位过程中复位信号RST的释放相对于有效时钟沿的恢复时间(recovery time)不满足,就可能产生亚稳态,此时触发器的输出端Q在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里Q端在0和1之间处于振荡状态,而不是等于数据输入端D的值。这段时间称为决断时间(Tmet,resolutiontime)。经过resolution time之后Q端将稳定到0或1上,但是稳定到0或者1,是随机的,与输入没有必然的关系。

有鉴于此,在同步模块200中设置第二触发器D2、第三触发器D3,经过两级触发器的延时处理,可以进一步减少亚稳态对计时精度的影响。

如图8或者图11所示,在其中一个实施例中,细计时模块400包括细计时控制单元410、延时链单元420、细计时锁存单元430以及编码单元440,细计时控制单元410与计时停止处理模块100的输出端、同步模块200的输出端电性连接,用于根据计时停止标志信号Stop_flag、计时停止同步信号Stop_flag_d2输出对应的电位信号;延时链单元420与细计时控制单元410电性连接,用于多级延时传输电位信号;细计时锁存单元430与延时链单元420、同步模块200电性连接,用于根据计时停止同步信号Stop_flag_d2锁存电位信号经过多级延时传输后的电位传输状态;编码单元440与细计时锁存单元430、计算模块500电性连接,用于根据电位传输状态得到细计时结果。

可以理解的是,如图5所示,延时链单元420可以采用反相器、缓冲器构成,初始电位状态即计时停止标志信号Stop_flag为低电位或者0时,延时链单元420中的各电位状态可以全为0或者1,以初始状态全0为例说明:当计时停止标志信号Stop_flag为高电位或者1后,电位信号1开始在延时链单元420中传播,电位信号1传播到bit(N-1)后翻转为电位信号0,电位信号0开始在延时链单元420中传播。当计时停止同步信号Stop_flag_d2的上升沿到来时,细计时锁存单元430将经过多级延时传输后的电位传输状态即计时停止同步信号Stop_flag_d2的上升沿时刻延时链单元420中的0、1对应锁存,编码单元440根据细计时锁存单元430中0、1的位置、数量得到延时链单元420的计时结果。

其中,在具有计数单元450的实施例中,延时链单元420的计时结果与计数单元450的计数结果之和为细计时模块400的细计时结果。

其中,图5中的三角符号可以表征为缓冲器,用于延时。图5中尖角加圆圈的三角符号可以表征为反相器,用于电位翻转。

如图6所示,在其中一个实施例中,延时链单元420包括多个加法器421,多个加法器421依次串联连接,多个加法器421中第一个加法器的第一输入端与细计时控制单元410的输出端电性连接,多个加法器421的第二输入端接入高电位信号,多个加法器421的第三输入端接入低电位信号,多个加法器421的求和输出端与细计时锁存单元430电性连接,多个加法器421中前一个加法器的进位输出端与多个加法器421中下一个加法器的第一输入端电性连接;其中,每个加法器输入输出的数据均为二进制数据,加法器的求和输出端的输出结果为加法器的第一输入端接入的二进制数据、加法器的第二输入端接入的二进制数据以及加法器的第三输入端接入的二进制数据之和中的低位,加法器的进位输出端的输出结果为加法器的第一输入端接入的二进制数据、加法器的第二输入端接入的二进制数据以及加法器的第三输入端接入的二进制数据之和中的高位。

可以理解的是,采用缓冲器、反相器等构成的延时链单元420,缓冲器与反相器、缓冲器与缓冲器之间走线的延时难以控制。而在本实施例中,采用加法器构成的加法进位链单元延时小,结构紧凑且实现简单。

如图3所示,在其中一个实施例中,细计时锁存单元430包括多个第四触发器D4,多个第四触发器D4的触发端与同步模块200的输出端电性连接,多个第四触发器D4的复位端均接入复位信号RST,多个第四触发器D4的同相输出端与细计时锁存单元430电性连接,一第四触发器D4的输入端与一加法器的求和输出端对应电性连接。

可以理解的是,每个第四触发器D4用于对应锁存一个电位状态。

如图3、图7所示,上述实施例中的时间数字转换装置的工作过程为如下:

时钟信号CLK与计时开始信号Start_trig为同步信号,两者的上升沿同时到来并开始粗计时。计时停止信号Stop_signal的上升沿与计时停止标志信号Stop_flag的上升沿同时到来并开始细计时。计时停止同步信号Stop_flag_d2的上升沿到来时,生成了计时停止标志信号Stop_flag的下降沿;与此同时,粗计时、细计时同时停止。计时结果为粗计时与细计时的差值。其中,Stop_flag_d1为第二触发器D2的正相输出端输出的信号。

如图8所示,在其中一个实施例中,细计时模块400还包括计数单元450,计数单元450的复位端接入复位信号RST,计数单元450的时钟端与多个加法器421中任一加法器的求和输出端电性连接,计数单元450的输出端与计算模块500电性连接,用于计算电位信号在多个加法器421中传输的循环周期数量。

在其中一个实施例中,计数单元450包括第一计数器,第一计数器的复位端接入复位信号RST,第一计数器的时钟端与多个加法器421中任一加法器的求和输出端电性连接,第一计数器的输出端与计算模块500电性连接,用于根据上升沿和下降沿进行计数以计算电位信号在多个加法器421中传输的循环周期数量。

在其中一个实施例中,计数单元450包括第二计数器和第三计数器,第二计数器的复位端接入复位信号RST,第二计数器的时钟端与多个加法器421中任一加法器的求和输出端电性连接,第二计数器的输出端与计算模块500电性连接,用于根据上升沿进行计数以计算电位信号在多个加法器421中传输的第一循环周期数量;第三计数器的复位端接入复位信号RST,第三计数器的时钟端与任一加法器的求和输出端电性连接,第三计数器的输出端与计算模块500电性连接,用于根据取反后的上升沿进行计数以计算电位信号在多个加法器421中传输的第二循环周期数量;其中,计算模块500根据第一循环周期数量与第二循环周期数量之和得到循环周期数量。

如图11所示,在其中一个实施例中,细计时模块400还包括计数单元450,计数单元450的复位端接入复位信号RST,计数单元450的时钟端与多个加法器421中任一加法器的求和输出端电性连接,计数单元450的锁存端与同步模块200的输出端电性连接,计数单元450的输出端与计算模块500电性连接,用于计算电位信号在多个加法器421中传输的循环周期数量。

其中,计数单元450可以响应于计时停止同步信号Stop_flag_d2而锁存当前的计数结果。

可以理解的是,在细计时模块400未包括计数单元450时,延时链单元420即加法进位链中的加法器数量需要覆盖时钟信号CLK的至少一个时钟周期,例如,可以为两个时钟周期,如此才可以不重复地完整记录延时链单元420中传输的电位状态,如果数量少的话,会导致数据溢出,影响计时结果。如此的话,随着时钟信号CLK的频率降低,则需要更多数量的加法器。也就是说,加法器的数量与时钟信号CLK的频率频率、每个加法器的延时相关。其中,随着每个加法器的延时增加,所需要的加法器的数量也越多。

而在本实施例中,可以采用计数单元450与短加法进位链相结合的计数方案,计数单元450每当输入延时链单元420中的一个电位状态传输一个循环时,计数单元450就加1,而短加法进位链仅需记录时钟信号CLK的一个周期内的电位状态即可,两者的结果叠加之后即为细计时结果。如此可以减少延时链单元420的长度,适应不同系统的时钟频率。对于N位长度即包括了N个加法器的延时链单元420,当细计时控制单元410的输出信号由延时链单元420中第1个加法器的输出信号themometer[0]传到延时链单元420中第N个加法器的输出信号themometer[N-1],认为信号传播了一个延时链即N个加法器的时长,此时,计数单元450的计数结果加1。

其中,实现计数单元450的第一种具体计数方法可以为:N位(bits)长度的延时链单元420,以延时链单元420中第N个加法器的输出信号themometer[N-1]作为计数单元450的计数时钟,计时停止同步信号Stop_flag_d2触发细计时锁存单元430进行锁存,但是由于延时链单元420中第N个加法器的输出信号themometer[N-1]和计时停止同步信号Stop_flag_d2为异步信号,锁存的时候可能会存在亚稳态,导致计数单元450多计或少计了1。因此,计时停止同步信号Stop_flag_d2触发细计时锁存单元430锁存后,编码单元440可以对锁存结果进行复核,通过查证延时链单元420中是在传0还是传1,判断计数单元450是否多计或少计1,能够保证计数单元450计数的正确性。

实现计数单元450的第一种具体计数方法可以为:当计时停止同步信号Stop_flag_d2的上升沿到来时,延时链单元420停止计数,细计时控制单元410保持延时链单元420中第1个加法器的输出信号themometer[0]的值不变化。用延时链单元420中第1个加法器的输出信号themometer[0]作为计数单元450的时钟信号CLK,计数单元450在该时钟信号CLK的上升沿和下降沿分别计数。对于Nbits的延时链单元420,延时链单元420中第2个加法器的输出信号themometer[1]至延时链单元420中第N个加法器的输出信号themometer[N-1]中的任一个均为延时链单元420中第1个加法器的输出信号themometer[0]延时后产生的,因此,可以采用延时链单元420中任一个加法器的输出信号themometer[0]至themometer[N-1]作为计数单元450的时钟信号CLK。

如图9所示,图8所示时间数字转换装置的工作过程为如下:

时钟信号CLK与计时开始信号Start_trig为同步信号,两者的上升沿同时到来并开始粗计时。计时停止信号Stop_signal的上升沿与计时停止标志信号Stop_flag的上升沿同时到来并开始细计时。计时停止同步信号Stop_flag_d2的上升沿到来时,生成了计时停止标志信号Stop_flag的下降沿;与此同时,粗计时、细计时同时停止。计时结果为粗计时与细计时的差值。

其中,计数单元450的计数结果CNT在细计时未开始之前为0,对延时链单元420中第1个加法器的输出信号themometer[0]的上升沿、下降沿均进行计数,则在计时停止同步信号Stop_flag_d2的上升沿到来之前,延时链单元420中第1个加法器的输出信号themometer[0]的上升沿、下降沿的数量之和即计数单元450的计数结果为8,则该计数结果减1之后即为延时链单元420已经传输的循环周期数量即为7,对应地,细计时结果包括7个整个延时链的长度和小数部分的延时链长度。

如图10所示,在其中一个实施例中,细计时控制单元410包括第一数字选择器MUX1和第二数字选择器MUX2,第一数字选择器MUX1的第一输入端接入高电位信号,第一数字选择器MUX1的第二输入端接入低电位信号,第一数字选择器MUX1的选择控制端与多个加法器421中第一个加法器的输出端电性连接;第二数字选择器MUX2的第一输入端接入高电位信号,第二数字选择器MUX2的第二输入端与多个加法器421中最后一个加法器的输出端电性连接,第二数字选择器MUX2的第三输入端与第一数字选择器MUX1的输出端电性连接,第二数字选择器MUX2的第一选择控制端与计时停止处理模块100的输出端电性连接,第二数字选择器MUX2的第二选择控制端与同步模块200的输出端电性连接。

可以理解的是,当计时停止标志信号Stop_flag为0,且计时停止同步信号Stop_flag_d2为0时,通道0打开,细计时控制单元410的输出信号保持为1,延时链单元420稳定。当计时停止标志信号Stop_flag为1时,通道1打开,细计时控制单元410的输出信号为延时链单元420中第N个加法器的输出信号themometer[N-1],开始翻转,信号开始在延时链单元420中传播。当计时停止同步信号Stop_flag_d2为1时,通道2/3打开,保持延时链单元420中第1个加法器的输出信号themometer[0]的值不变,延时链单元420停止信号传播,使延时链单元420不会再翻转。

其中,如图12所示,细计时控制单元411可以包括数字选择器MUX3,在nbits的延时链单元420中,延时链单元420中第N个加法器的输出信号themometer[N-1]作为计数单元450的计数时钟,计时停止同步信号Stop_flag_d2的上升沿到来时锁存计数单元450,但是由于延时链单元420中第N个加法器的输出信号themometer[N-1]和计时停止同步信号Stop_flag_d2为异步信号,锁存的时候可能会存在亚稳态,导致计数单元450多计或少计了1。因此,可以用计时停止同步信号Stop_flag_d2的上升沿到来时,细计时锁存单元430中的锁存结果来判断延时链单元420是在传0还是传1,由此可以判断计数单元450是否多计或少计1,保证cnt计数的正确性。

如图13、图14所示,计数结果CNT的奇偶与延时链单元420被锁存时的电位传输状态相关,当计时停止同步信号Stop_flag_d2的上升沿到来时,细计数锁存单元对延时链单元420中传输的电位进行锁存(Latch),因此,根据细计数锁存单元的锁存数据可以判断延时链单元420中是在传0还是传1。传(Send)0时,计数结果CNT应为奇数(Odd),若计数结果CNT为奇数,则计数结果CNT正确;若计数结果CNT为偶数(Even),则计数结果CNT应加1。传1时,计数结果CNT应为偶数,若计数结果CNT为偶数,则计数结果CNT正确;若计数结果CNT为奇数,则计数结果CNT应加1。如此,最终可以得到正确的最终计数结果Rslt。

具体地,计数结果CNT的获取方式如下:

第一种方法:计数单元450包括第一计数器,第一计数器的复位端接入复位信号RST,第一计数器的时钟端与多个加法器421中任一加法器的求和输出端电性连接,第一计数器的锁存端与同步模块200的输出端电性连接,第一计数器的输出端与计算模块500电性连接,用于根据上升沿和下降沿进行计数以计算电位信号在多个加法器421中传输的循环周期数量。

例如,第一计数器的触发端接入延时链单元420中第64个加法器的输出信号themometer[63],作为第一计数器的计数时钟,对第64个加法器的输出信号themometer[63]的上升沿、下降沿分别计数,实际循环周期数量为计数结果CNT-1。

第二种方法:计数单元450包括第二计数器和第三计数器,第二计数器的复位端接入复位信号RST,第二计数器的时钟端与多个加法器421中任一加法器的求和输出端电性连接,第二计数器的锁存端与同步模块200的输出端电性连接,第二计数器的输出端与计算模块500电性连接,用于根据上升沿进行计数以计算电位信号在多个加法器421中传输的第一循环周期数量;第三计数器的复位端接入复位信号RST,第三计数器的时钟端与任一加法器的求和输出端电性连接,第三计数器的锁存端与同步模块200的输出端电性连接,第三计数器的输出端与计算模块500电性连接,用于根据取反后的上升沿进行计数以计算电位信号在多个加法器421中传输的第二循环周期数量;其中,计算模块500根据第一循环周期数量与第二循环周期数量之和得到循环周期数量。

例如,第二计数器的触发端接入延时链单元420中第64个加法器的输出信号themometer[63],作为第二计数器的计数时钟,上升沿计数,共计4。第三计数器的触发端接入取反后的延时链单元420中第64个加法器的输出信号themometer[63],作为第三计数器的计数时钟,上升沿计数,共计3。实际循环周期数量为计数结果CNT-1。

在其中一个实施例中,第一触发器D1、第二触发器D2、第三触发器D3以及至少一个触发器均可以为D触发器;或者,多个第四触发器D4均可以为D触发器。

如图15所示,在其中一个实施例中,本实施例提供一种时间数字转换方法,其包括以下步骤:

步骤S10:根据计时停止信号Stop_signal、复位信号RST以及计时停止同步信号Stop_flag_d2生成计时停止标志信号Stop_flag,计时停止标志信号Stop_flag的脉冲开始时间与计时停止信号Stop_signal的脉冲开始时间相同,计时停止标志信号Stop_flag的脉冲持续时间小于计时停止信号Stop_signal的脉冲持续时间。

步骤S20:根据时钟信号CLK、复位信号RST以及计时停止标志信号Stop_flag生成计时停止同步信号Stop_flag_d2,计时停止同步信号Stop_flag_d2的脉冲开始时间与计时停止标志信号Stop_flag的脉冲结束时间相同。

步骤S30:响应于计时开始信号Start_trig的脉冲开始时间、时钟信号CLK的一个脉冲开始时间而开始粗计时,且响应于计时停止同步信号Stop_flag_d2的脉冲开始时间、时钟信号CLK的另一个脉冲开始时间而停止粗计时,基于开始粗计时与停止粗计时之间的时钟信号CLK的时钟数量得到粗计时结果Coarse_rslt。

步骤S40:响应于计时停止标志信号Stop_flag的脉冲开始时间而开始细计时,响应于计时停止同步信号Stop_flag_d2的脉冲开始时间而停止细计时,基于开始细计时与停止细计时之间的时钟信号CLK的时钟数量得到细计时结果。

以及步骤S50:根据时钟信号CLK、粗计时结果Coarse_rslt与细计时结果的差值,确定时间数字转换装置的计时结果。

可以理解的是,本实施例提供的时间数字转换方法,通过计时停止标志信号Stop_flag、计时停止同步信号Stop_flag_d2对应控制粗计时结果Coarse_rslt、细计时结果,可以缓解或者消除由于计时停止信号Stop_signal为异步信号所导致的亚稳态影响,提高时间数字转换结果的准确性;同时,可以确定粗计时结果Coarse_rslt与细计时结果的差值为时间数字转换装置的计时结果,即使在时间数字转换过程中粗计时结果Coarse_rslt、细计时结果受到了亚稳态影响,通过粗计时结果Coarse_rslt与细计时结果的减法运算,也能够进一步降低或者消除计时结果所受到的亚稳态影响,进而进一步提高了时间数字转换结果的准确性。

在其中一个实施例中,根据计时停止信号Stop_signal、复位信号RST以及计时停止同步信号Stop_flag_d2生成计时停止标志信号Stop_flag的步骤包括:构造第一触发器D1的输入端接入高电位信号、第一触发器D1的触发端接入计时停止信号Stop_signal;构造或门OR的一输入端接入计时停止同步信号Stop_flag_d2、或门OR的另一输入端接入复位信号RST以及或门OR的输出端与第一触发器D1的复位端电性连接;以及配置第一触发器D1的正相输出端输出计时停止标志信号Stop_flag。

在其中一个实施例中,根据时钟信号CLK、复位信号RST以及计时停止标志信号Stop_flag生成计时停止同步信号Stop_flag_d2的步骤包括:构造第二触发器D2的输入端与第一触发器D1的正相输出端电性连接,第二触发器D2的触发端接入时钟信号CLK,第二触发器D2的复位端接入复位信号RST;构造第三触发器D3的输入端与第二触发器D2的正相输出端电性连接,第三触发器D3的触发端接入时钟信号CLK,第三触发器D3的复位端接入复位信号RST,第三触发器D3的同相输出端与或门OR的一输入端电性连接;以及配置第三触发器D3的同相输出端输出计时停止同步信号Stop_flag_d2。

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

以上对本申请实施例所提供的时间数字转换装置、时间数字转换方法进行了详细介绍,本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例的技术方案的范围。