多存储器现场自修复选项的管理

文献发布时间:2023-06-19 13:46:35

背景技术

集成电路(IC)通常包含组合以执行各种功能的各种模块。例如,数字信号处理器(DSP)包含嵌入在IC中的处理器和存储器块。对包含多个可寻址存储器位置的存储器块进行缺陷测试,以确保IC的可操作性。为了测试这些块,特殊的测试电路(称为“内置自测试”(BIST)电路)被并入IC中。BIST电路产生测试型式以确定存储器块是否有缺陷。在一些情况下,电路提供冗余行和/或列,其用于重新配置存储器以使用冗余行和/或列而不是存储器块中的缺陷行和/或列。重新配置存储器以使用冗余行和/或列而不是有缺陷的行和/或列的过程称为物理存储器修复。

电子熔丝(例如,Efuse或fuseROM)组件也用于存储器修复。电子熔丝组件存储修复数据或修复签名以识别并修复存储器块的缺陷元件。电子熔丝组件的数目与被测存储器块数目之和直接相关。随着现代片上系统(SoC)产品中存储器块的不断增加,在制造测试期间存储器修复对于改进产量至关重要,且使用错误校正码(ECC)容忍错误已成为改进这些现场存储器块在功能操作期间可靠性的普遍方法。ECC的已知实施方案涉及将额外签名与存储器数据一起存储,其中签名满足与数据的特定数学方程。在每次存储器读取时,读取数据和签名两者,并评估读取数据的数学方程。将评估的签名与经读取以检测和校正数据中的错误的存储的签名进行比较。签名位的数目和/或所使用的数学方程确定可检测和/或校正的错误的数目。用ECC校正存储器中的错误的过程称为逻辑存储器修复。正在努力平衡IC占用面积大小、存储器测试和修复效率以及存储器修复灵活性。

发明内容

根据本发明的至少一个实例,一种系统包括处理器和耦合到所述处理器的存储器组。所述系统还包括耦合到所述存储器组的存储器修复电路。所述存储器修复电路包括第一修复电路和第二修复电路。所述存储器修复电路还包括测试控制器,所述测试控制器经配置以在所述第一修复电路与所述第二修复电路之间进行选择以执行所述存储器组的现场自修复。

根据本发明的至少一个实例,一种装置包括存储器组和耦合到所述存储器组的存储器修复电路。所述存储器修复电路包括测试电路、错误掩码电路和递增修复电路。所述存储器修复电路还包括耦合到所述测试电路、所述错误掩码电路和所述递增修复电路的测试控制器。所述测试控制器经配置以在所述错误掩码电路与所述递增修复电路之间进行选择以执行所述存储器组的现场自修复。

根据本发明的至少一个实例,一种片上系统(SoC)包括具有多个不同存储器单元的存储器组,不同存储器单元中的每一者具有其自身的修复架构。所述SoC还包括耦合到所述存储器组的存储器修复电路。所述存储器修复电路包括测试电路,所述测试电路经配置以:为所述存储器组内的不同存储器单元中的每一者提供本地通过/失败确定,提供数据字的错误校正码(ECC)感知区域化,以及提供ECC感知错误掩蔽。所述存储器修复电路还包括修复电路,所述修复电路经配置以修复所述存储器组的现场自修复。所述存储器修复电路还包括耦合到所述测试电路和所述修复电路的测试控制器,其中所述测试控制器经配置以选择性地启用和停用所述修复电路。

附图说明

针对各个实例的详细描述,现将参考附图,其中:

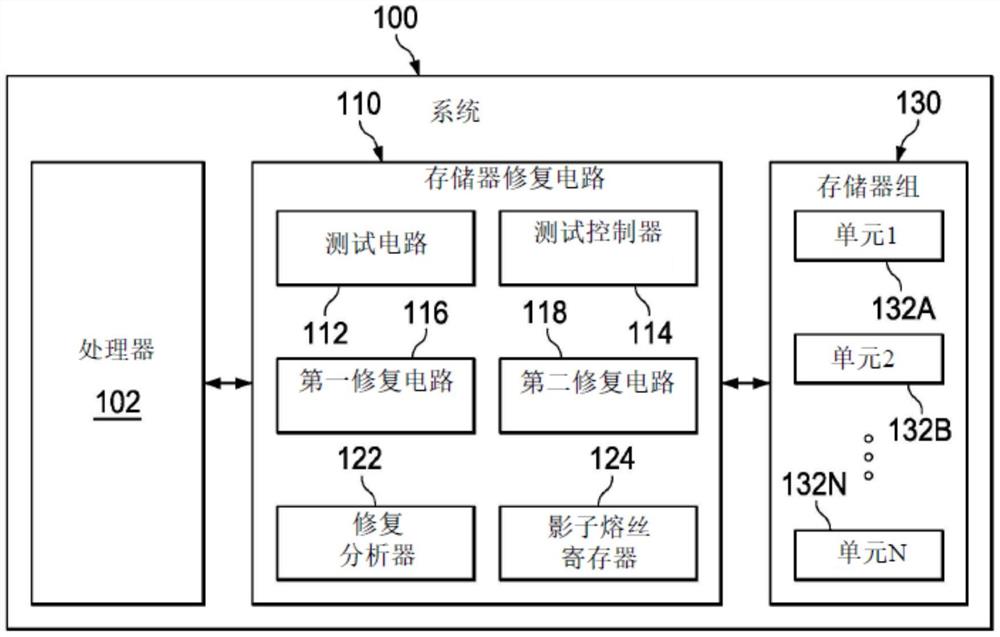

图1是展示根据一些实例的系统的框图;

图2A是展示根据一些实例的存储器修复方案的框图;

图2B是展示根据一些实例的在存储器修复中使用的错误掩码电路的框图;

图3是展示根据一些实例的存储器修复方案的框图;

图4A是展示根据一些实例的存储器修复方案的示意图;

图4B是展示根据一些实例的与图4A的存储器修复方案相关的对准和合并电路的示意图;及

图5是展示根据一些实例的与存储器修复方案相关的存储器修复方案的示意图。

具体实施方式

本文公开具有多个存储器现场自修复选项的系统以及相关的控制组件和方法。实例系统是片上系统(SoC)集成电路(IC),其中系统包含处理器和耦合到处理器的存储器组。所述系统还包含耦合到所述存储器组的存储器修复电路。在一些实例中,所述存储器修复电路包括第一修复电路和第二修复电路。所述存储器修复电路还包括测试控制器,所述测试控制器经配置以在所述第一修复电路与所述第二修复电路之间进行选择,以执行所述存储器组的现场自修复。在其它实例中,存储器修复电路包括由测试控制器选择性地启用或停用的至少一个修复电路。在一些实例中,修复电路或第一修复电路是错误掩码电路。同时,第二修复电路是递增修复电路。如本文所使用的,“错误掩码电路”是指被编程为掩蔽存储器输出数据中预定数目的位错误的电路。如本文所使用的,“递增修复电路”是指能够递增地重新配置现场存储器以使用额外的冗余行和/或列来替换有缺陷的行和/或列的电路。术语递增用于指示在现场进行的此修复或重新配置应该是除在制造测试期间已经修复的那些之外的修复或重新配置。在一些实例中,存储器组包含多个不同的存储器单元,不同的存储器单元中的每一者具有其自身的修复架构。根据需要,存储器修复电路经配置以基于不同存储器单元中的每一者的相应修复架构来调整其自身。

在一些实例中,基于现场调试和/或诊断操作启用或停用修复电路。在一些实例中,响应于修复需要和/或基于预定的修复策略,测试控制器经配置以在第一修复电路与第二修复电路之间进行选择,以执行存储器组或存储器组的个别存储器单元的现场自修复。在一个实例中,响应于测试控制器确定与第一修复电路兼容的修复可用,测试控制器选择第一修复电路来对不同存储器单元中的一者执行现场自修复。在另一实例中,响应于测试控制器确定与第一修复电路兼容的修复不可用,测试控制器选择第二修复电路以对不同存储器单元中的一者执行现场自修复。

在一些实例中,存储器修复电路包含组件,其经配置以提供:1)针对存储器组的不同存储器单元中的每一者的本地通过/失败或错误确定;2)数据字的ECC感知区域化;和3)ECC感知错误掩蔽。在一些实例中,存储器修复电路还包含用于不同存储器单元中的每一者的影子熔丝寄存器,其中每一影子熔丝寄存器经配置以在每个电子熔丝自动加载时用来自FuseROM的不同存储器单元的相应修复代码初始化。存储器修复电路经配置以为不同的存储器测试会话提供累积修复代码,并响应于基于累积修复代码识别不可修复错误而断言错误。存储器修复电路还经配置以选择性地将影子熔丝寄存器的内容重新加载到不同存储器单元中的相应一者中以执行现场自修复操作。为了提供更好的理解,使用如下图描述涉及多个存储器现场自修复选项的管理的各种存储器修复电路选项。

图1是展示根据一些实例的系统100的框图。如展示,系统100包含处理器102、耦合到处理器102的存储器修复电路110、以及耦合到存储器修复电路110的存储器组130。在不同的实例中,系统100代表IC、SoC或多裸片模块。

在图1的实例中,存储器组130包含多个存储器单元132A到132N,其对应于不同的存储器模块或不同的存储器区,其中存储器单元132A到132N中的每一者具有不同的修复架构。如本文所用,“修复架构”可指物理修复架构或逻辑修复架构。物理修复架构涉及重新配置存储器单元以根据需要使用有限数目的冗余行和/或列来克服相应存储器单元的缺陷行和/或列。相反,逻辑修复架构是指使用ECC来校正存储器输出。例如,具有ECC修复架构的存储器单元使用额外位来存储用于自动检测和校正错误的签名。同时,具有递增修复架构的存储器单元使用冗余行和/或列进行修复。此外,存储器组的一些存储器单元可具有ECC修复架构和递增修复架构两者,而存储器组的其它存储器单元只有一种修复架构,或者没有修复架构。

在图1的实例中,系统100的存储器修复由存储器修复电路110执行,存储器修复电路110包含测试电路112、测试控制器114、第一修复电路116和第二修复电路118。在一些实例中,第一修复电路116对应于ECC修复电路,且第二修复电路118对应于递增修复电路。当测试电路112检测到修复需要时,测试控制器114经配置以确定修复对于给定存储器单元是否可行(存储器单元132A到132N中的每一者可用的冗余行/列的数目是有限的)。为了做出此确定,测试控制器114从修复分析器电路122和影子熔丝寄存器124接收信息。

响应于修复需要和/或基于预定的修复策略,测试控制器114经配置以在第一修复电路116与第二修复电路116之间进行选择,以执行存储器组130或存储器组130的个别存储器单元132A到132N的现场自修复。在一个实例中,响应于测试控制器114确定与第一修复电路116兼容的修复可用,测试控制器114选择第一修复电路116来对不同存储器单元132A到132N中的一者执行现场自修复。在另一实例中,响应于测试控制器114确定与第一修复电路116兼容的修复不可用,测试控制器114选择第二修复电路118来对不同存储器单元132A到132N中的一者执行现场自修复。在一些实例中,选择性地启用或停用第一修复电路116和/或第二修复电路118。此外,在一些实例中,省略第一修复电路116和第二修复电路118中的一者,且选择性地启用或停用剩余修复电路。

在一个实例中,系统100仅包含ECC修复电路,并且选择性地启用和停用ECC修复电路。在另一实例中,系统100仅包含递增修复电路,并且选择性地启用和停用递增修复电路。在另一实例中,系统100包含ECC修复电路和递增修复电路两者,其中选择性地启用和停用ECC修复电路。在另一实例中,系统100包含ECC修复电路和递增修复电路两者,其中选择性地启用和停用递增修复电路。在另一实例中,系统100包含ECC修复电路和递增修复电路两者,其中启用或停用两个修复电路。当ECC和递增修复电路两者被启用时,当需要修复时,一者可具有更高的优先级。在一些实例中,优先等级是预定的(例如,优选为ECC修复或递增修复)。在其它实例中,可基于用户输入或预定触发器调整优先等级。

在一些实例中,存储器修复电路110的测试电路112经配置以提供:1)针对存储器组130的不同存储器单元132A到132N中的每一者的本地通过/失败或错误确定;2)数据字的ECC感知区域化;和3)ECC感知错误掩蔽。在一些实例中,存储器修复电路110还包含用于不同存储器单元132A到132N中的每一者的影子熔丝寄存器124,其中每一影子熔丝寄存器124经配置以在每个电子熔丝自动加载时用来自FuseROM的不同存储器单元的相应修复代码初始化。存储器修复电路110也包括修复分析器电路122,其经配置以为不同的存储器测试会话提供累积修复代码,并响应于基于累积修复代码识别不可修复错误而断言错误。根据需要,存储器修复电路110经配置以选择性地将影子熔丝寄存器124的内容重新加载到不同存储器单元132A到132N中的相应一者中以执行现场自修复操作。

图2A是展示根据一些实例的存储器修复方案200的框图。在存储器修复方案200中,表示各种组件,其包含内置自测试(BIST)单元202(测试电路112的实例)、存储器数据路径开关203、存储器单元204A到204C(图1中存储器单元132A到132N的实例)、存储器修复分析器电路206(图1中存储器修复分析器122中的至少一些的实例)和影子熔断寄存器210A到210C(影子熔断寄存器124的实例)。在不同的实例中,针对存储器修复方案200表示的组件是IC、SoC或多裸片模块的部分。

在存储器修复方案200中,BIST单元202在修复完成之前和之后执行各种操作(例如写和读)以测试存储器单元204A到204C。例如,BIST单元202可使用存储器数据路径开关203用一或多个测试序列测试存储器单元。数据路径开关203用于在测试会话中选择存储器单元204A到204C中的一或多者(同时或不同时)以由BIST单元202进行测试。由BIST单元202使用的测试序列可基于对存储器的操作(例如写和读)顺序、用于操作的数据背景(例如,所有0、交替0到1等)、存储器单元内字的寻址顺序(例如,增加列、减少行、乒乓(ping-pong)等)或其它选项而变化。在一些实例中,多个序列用于测试,其中每一测试序列经微调以标定存储器单元内的特定缺陷。

为了执行修复,存储器修复电路206经配置以执行各种操作。在一些实例中,存储器修复电路206包含本地错误分析,其将存储器单元的输出与期望值进行比较以识别每一存储器单元本地的错误。在一些实例中,存储器修复电路206包含对准和合并组件,其将来自不同存储器架构的错误值对准和合并到统一的存储器架构中,以跨不同存储器架构重用用于修复分析器逻辑的后续阶段的公共电路。在一些实例中,存储器修复电路206包含ECC感知错误掩码组件。ECC感知错误掩码组件启用ECC感知测试和修复选项。根据需要,存储器修复电路206可经配置以绕过ECC感知错误掩码组件。在此情况下,ECC感知测试和修复选项不可用。

如图2A中表示,存储器修复电路206还包含修复分析组件。在一些实例中,修复分析组件支持ECC选项和递增修复选项。对于ECC修复选项,修复分析组件与ECC感知错误掩码组件一起工作。因此,如果绕过ECC感知错误掩码组件,那么ECC修复选项不可用。此外,在不同的实例中,ECC修复选项和递增修复选项具有不同的优先级。在一个实例中,ECC修复选项具有比递增修复选项更高的优先级。在另一实例中,ECC修复选项具有比递增修复选项更低的优先级。

出于现场调试和诊断的原因,可启用或停用ECC修复和/或递增修复。在一些方案中,ECC修复选项是唯一可用的存储器修复选项。在此类方案中,选择性地启用或停用ECC修复。在一些方案中,只有递增修复选项可用。在此类方案中,选择性地启用或停用递增修复选项。在一些方案中,ECC选项及递增修复选项两者都可用。在此类方案中,可用的修复选项中的一者被给予更高的优先级。在一些实例中,递增修复需要重新编程FuseROM来存储额外的修复值,从而导致存储器测试的额外时延。在其它实例中,ECC修复需要计算签名并在签名不匹配的情况下校正数据,从而导致存储器测试的额外时延。对于时延敏感的应用,ECC修复或递增修复可基于其相对时延开销被给予更高的优先级。

在使用对准和合并组件的一些实例中,存储器修复电路206还包含可重新配置熔丝链组件,其帮助将熔丝编码信息从统一存储器修复架构(来源于对准/合并和修复分析操作)重新配置回到被测试的特定存储器单元的修复架构。存储器修复电路206的重新配置熔丝链组件接收来自存储器修复电路206的修复分析组件的熔丝编码信息,并更新影子熔丝寄存器210A到210C,其中影子熔丝寄存器210A存储用于存储器单元204A的修复信息(例如,跟踪所有修复的修复签名),影子熔丝寄存器210B存储用于存储器单元204B的修复信息,且影子熔丝寄存器210C存储用于存储器单元204C的修复信息。

图2B是展示根据一些实例的在存储器修复中使用的错误掩码电路250的框图。在图2B的实例中,错误掩码电路250(图2中的206中的ECC感知错误掩码的实例)能够掩蔽预定数目的错误。错误掩码电路250具有来自存储器251的输出数据、预期数据252和根据相应存储器的支持的ECC配置的预定义错误极限253(标记为“L”)作为其输入。错误掩码电路250首先计算输出数据与预期数据之间的错误254(标记为“E”),这可使用异或操作261来实现。在图2B的实例中,错误掩码电路250包含本地比较逻辑255,其将存储器输出与每一存储器单元本地的预期数据进行比较。然后,错误掩码电路250计算位错误的总数256(标记为“S”),这可使用加法操作262来实现。在逻辑263中,值256被检查为大于错误极限253。如果逻辑263的比较为假(指示错误的数目小于极限L),那么多路复用器264返回0作为输出掩蔽错误258。否则,错误掩码电路返回计算出的错误254作为输出掩蔽错误258。

图3是展示根据一些实例的存储器修复方案300的框图。在存储器修复方案300中,表示各种组件,其包含BIST单元202、存储器数据路径开关302、第一ECC感知错误掩码组件304、第二ECC感知错误掩码组件306和存储器单元308A到308C。在图3的实例中,存储器数据路径开关302执行与图2的存储器数据路径开关203相同的功能,并且使得BIST单元202能够在测试会话中同时测试一或多个存储器单元308A到308C。第一和第二ECC感知错误掩码组件304和306执行与图2B的错误掩码组件250相同的功能。在不同的实例中,针对存储器修复方案300表示的组件是IC、SoC或多裸片模块的部分。

在存储器修复方案300中,BIST单元202在修复完成之前和之后执行各种操作以测试存储器单元308A到308C。在存储器修复方案300中,存储器单元308A和308C支持ECC修复。更具体地说,存储器单元308A包含用于存储用于ECC修复的ECC签名的额外位310A。存储器单元308C还包含用于存储用以支持对存储器单元308B和308C的ECC修复的ECC签名的额外位310B。注意:额外位310B的数目相对于额外位310A的数目可具有相同的数目或不同的数目。此外,存储器单元308B在其内不包含签名位,而是依赖于存储在308C内的签名位。因此,在存储器修复方案300中,存储器单元308A到308C中的每一者包含其自身的修复架构(或无修复架构)。

具有本地比较组件304和306的错误掩码启用ECC感知测试和修复选项,并且是具有图2B的本地比较电路250的错误掩码的实例实施方案。根据需要,可绕过错误掩码组件304和306。在此情况下,ECC感知测试和修复选项不可用。因此,当第一和第二错误掩码组件304和306被启用时,存储器单元308A、308B和308C的ECC修复是可用的(其中308B和308C共享签名310B,并且具有如图2a的253中所说明的公共共享位错误极限L)。另一方面,当第一和第二错误掩码组件304和306被停用时,即使存在可用310A和310B校正的位错误,也不能对存储器单元308A、308B和308C进行ECC修复。

在图4A的存储器修复方案400中,表示各种组件,其包含BIST单元202、存储器数据路径开关302、存储器单元404A到404C、本地比较器单元405A到405C、对准和合并电路410、“或”门412、修复分析电路414和熔丝重新配置电路416。存储器修复方案400还包含影子熔丝寄存器422A到422C,“或”门418A到418C和430,以及多路复用器420A到420C和424。在对存储器单元进行任何功能或测试操作之前的系统通电或初始化序列期间,复位/清除影子熔丝寄存器422A到422C,并且通过输入425A和多路复用器424将存储在FuseROM或类似非易失性存储器中的存储器修复数据(可能来自先前的测试会话)串行加载到对应的存储器修复寄存器408A到408C中。同时,对应的影子熔丝寄存器422A到422C也通过输入425B和多路复用器420A到420C用相同的存储器修复数据串行初始化。因此,在系统初始化结束时,影子熔丝寄存器422A到422C具有与对应的存储器修复寄存器408A到408C相同的数据。在图4的实例中,测试控制器电路(例如,图1的测试控制器114)控制多路复用器424、420A到420C并启用递增修复组件410、414、416、422A到422C。在不同的实例中,针对存储器修复方案400表示的组件是IC、SoC或多裸片模块的部分。

在存储器修复方案400中,BIST单元202在修复完成之前和之后执行各种操作以测试存储器单元404A到404C。在存储器修复方案400中,存储器单元404A和404C支持ECC修复和递增修复。同时,存储器单元404B仅支持递增修复,同时依赖于存储器单元404C进行ECC修复。更具体地说,存储器单元404A包含:1)额外存储装置406A,其用以存储用于ECC修复的签名;以及2)一组冗余行/列元件408A,其用以支持递增修复。此外,存储器单元404B包含一组冗余行/列元素408B,其以支持递增修复。此外,存储器单元404C包含:1)额外存储装置406B,其用以存储用于ECC修复的签名;以及2)一组冗余行/列元件408A,其用以支持递增修复。注意:所述组ECC签名存储元件406A和406B中的每一者可具有相同数目或不同数目的位。此外,所述组冗余行/列元件408A到408C中的每一者可具有相同数目或不同数目的冗余元件。因此,在存储器修复方案400中,存储器单元404A到404C中的每一者包含其自身的修复架构。

为了在存储器修复方案400中执行存储器修复,BIST单元202测试存储器单元404A到404C以确定是否需要存储器修复。响应于来自BIST单元的测试,本地比较电路405A到405C计算来自相应存储器单元404A到404C的错误。本地比较电路405A到405C是用以计算来自存储器单元404A到404C的错误的图2B的本地比较电路255的实例。来自不同存储器单元的错误对准到统一格式并由对准和合并电路410合并在一起。来自对准和合并电路410的累积修复信息经由“或”门412提供给修复分析电路414。修复分析电路414的输出被提供回到“或”门412。对“或”门的反馈实现递增地累积修复,其中累积来自在同一存储器单元上背靠背运行的多个测试序列的错误。

修复分析电路414的输出还提供给熔丝重新配置电路416,熔丝重新配置电路416执行对准和合并电路410的逆操作,以将统一格式(由对准和合并电路410转换)的修复分析输出重新配置回到目标存储器修复架构。然后,熔丝重新配置电路416将累积修复信息(存储器单元404A到404C中的每一者的修复签名)写入影子熔丝寄存器422A到422C。“或”门418A到418C将来自影子熔丝寄存器(来自通电初始化或先前测试会话)的先前存储的修复签名与来自熔丝重新配置单元416的新修复签名合并,并且多路复用器420A到420C配置影子熔丝寄存器以存储回新的合并修复签名。

如展示,来自影子熔丝寄存器422A到422C中的每一者的输出被反馈到相应的“或”门418A到418C和相应的多路复用器420A到420C。在BIST单元202完成对所有存储器单元404A到404C的测试之后,从影子熔丝寄存器422A到422C新识别的存储器修复签名借助于通过多路复用器424的另一输入移出被存储到存储器修复寄存器408A到408C中。多路复用器420A到420C的另一输入经配置以通过传递来自存储器单元404A到404C中的每一者的相邻影子熔丝寄存器的修复信息来形成移位寄存器。如展示,影子熔丝寄存器422A(对应于存储器单元404A)的输出馈送到多路复用器424,其中多路复用器424的输出提供给存储器单元404C。当来自影子熔丝寄存器422A的数据移位到存储器修复寄存器408C中时,存储在影子熔丝寄存器420C和420B中的数据也将分别被移位到420B和420A中。此过程继续,直到用分别来自影子熔丝寄存器422A、422B和422C的数据初始化修复寄存器408A、408B和408C。“或”门430确保影子熔丝寄存器422A到422C在此过程期间使其数据重新循环回。这实现完全递增修复,其中与存储在影子寄存器422A到422C中的那些数据(来自FuseROM的初始加载或来自先前BIST执行)相同的存储在408A到408C中的先前存储器修复数据与来自新BIST测试会话的故障一起累积并修复回到相应存储器单元。在过程中的任何点(例如,在本地比较处或在对准和合并处或在修复分析处或在熔丝重新配置处或在影子熔丝累积处),如果识别出不可修复的错误或故障,那么BIST系统断言指示不可修复故障的错误。

图4B是展示根据一些实例的与图4A的存储器修复方案相关的对准和合并电路450(图4A中的对准和合并电路410的实例)的示意图。在图4B的实例中,对准和合并电路450包含经配置以执行对准功能的组件451。对准和合并电路450还包含用以执行合并功能的“或”门452。如展示,组件451包含存储器单元453到455。存储器单元453(标记为“M

返回到图4A的存储器修复方案400,根据需要执行ECC修复或递增修复。在一个实例修复方案中,BIST单元202通过向存储器单元404A到404C写入数据/从存储器单元404A到404C读取数据来测试整个存储器组。通过读取预期数据来比较写入到存储器单元404A到404C的数据以确定存储器操作是通过还是失败。响应于失败的存储器操作,执行修复,并且BIST单元202再次测试存储器单元404A到404C。根据需要,重复测试和修复过程。

在一些实例中,ECC修复相对于递增修复具有更高的优先级(例如,执行ECC修复,直到不再有错误可由ECC校正,然后执行递增修复,直到不再有冗余列可用)。在其它实例中,ECC修复相对于递增修复具有更低的优先级(例如,执行递增修复,直到不再有冗余列可用于递增修复,然后执行ECC修复,直到不再有错误可由ECC校正)。在其它实例中,ECC修复相对于递增修复的优先级可由用户选择。

在图5的存储器修复方案500中,表示各种组件,其包含BIST单元202、存储器数据路径开关302、存储器单元404A到404C、对准和合并电路410、“或”门412、修复分析电路414和熔丝重新配置电路416。存储器修复方案500还包含影子熔丝寄存器422A到422C,“或”门418A到418C和430,以及多路复用器420A到420C和424。存储器修复方案500还包括模式选择单元502和错误掩码组件504A和504B。在对存储器单元404A到404C进行任何功能或测试操作之前的系统通电或初始化序列期间,复位/清除影子熔丝寄存器422A到422C,并且存储在FuseROM或类似非易失性存储器中的存储器修复数据(可能来自先前的测试会话)通过输入425A和多路复用器424被加载到对应的存储器修复寄存器408A到408C中。与此同时,对应的影子熔丝寄存器422A到422C也通过输入425B和多路复用器420A到420C用相同的存储器修复数据初始化。因此,在系统初始化结束时,影子熔丝寄存器422A到422C具有与对应的存储器修复寄存器408A到408C相同的数据。在图5的实例中,测试控制器电路(例如,图1的测试控制器114)控制多路复用器424、420A到420C并启用递增修复组件410、414、416、422A到422C。在不同的实例中,针对存储器修复方案500表示的组件是IC、SoC或多裸片模块的部分。

在存储器修复方案500中,BIST单元202在修复完成之前和之后执行各种操作以测试存储器单元404A到404C。在存储器修复方案500中,存储器单元404A和404C支持ECC修复和递增修复。同时,存储器单元404B仅支持递增修复,同时依赖于存储器单元404C进行ECC修复。再次,存储器单元404A包含:1)额外存储器406A,其用以存储用于ECC修复的签名;以及2)一组冗余行/列元件408A,其用以支持递增修复。此外,存储器单元404B包含一组冗余行/列元素408B,其用以支持递增修复。此外,存储器单元404C包含:1)额外存储器406B,其用以存储用于ECC修复的签名;以及2)一组冗余行/列元件408A,其用以支持递增修复。所述组ECC签名存储元件406A和406B中的每一者可具有相同数目或不同数目的位。此外,所述组冗余行/列408A到408C中的每一者可具有相同数目或不同数目的冗余元件。因此,在存储器修复方案500中,存储器单元404A到404C中的每一者包含其自身的修复架构。

为了在存储器修复方案500中执行存储器修复,BIST单元202测试存储器单元404A到404C以确定是否需要存储器修复。响应于来自BIST单元202的测试,本地比较电路405A到405C计算来自相应存储器单元404A到404C的错误。本地比较电路405A到405C是用以计算来自存储器单元404A到404C的错误的图2B的本地比较电路255的实例。在存储器修复方案500中是否存在可用行/列的确定是基于冗余行/列的可用性以及模式选择单元502和错误掩码单元504A和504B的操作。例如,如果模式选择单元502经配置以绕过ECC修复,那么错误掩码单元504A和504B被停用并且不提供给BIST单元202。另一方面,如果模式选择单元502被配置为允许ECC修复,那么错误掩码单元504A和504B在将结果提供给BIST单元202之前操作并掩蔽ECC可校正错误。无论在存储器修复方案中启用还是停用ECC修复,都可执行递增修复,直到冗余列不可用为止。

基于提供的可用冗余行/列信息和ECC错误掩码输出,BIST单元202根据预定的修复优先级方案选择冗余行/列或ECC错误掩码(例如,错误掩码504A和504B)用于修复(例如,当模式选择单元502启用ECC修复时,相对于递增修复,ECC修复被分配更高或更低的优先级)。通过对准和合并电路410将所选择的修复添加到所有其它先前的修复中。来自对准和合并电路410的修复信息经由“或”门412提供给修复分析电路414。修复分析电路414的输出被提供回到“或”门412。

修复分析电路414的输出还提供给熔丝重新配置电路416,熔丝重新配置电路416执行对准和合并电路410的逆操作,以将统一格式(由对准和合并电路410转换)的修复分析输出重新配置回到目标存储器修复架构。然后,熔丝重新配置电路416将累积写入修复信息(存储器单元404A到404C中的每一者的修复签名)写入影子熔丝寄存器422A到422C。“或”门418A到418C将来自影子熔丝寄存器422A到422C(来自通电初始化或先前测试会话)的先前存储的修复签名与来自熔丝重新配置单元416的新修复签名合并,并且多路复用器420A到420C配置影子熔丝寄存器422A到422C以存储回新的合并修复签名。如展示,来自影子熔丝寄存器422A到422C中的每一者的输出被反馈到相应的“或”门418A到418C和多路复用器420A到420C。

在BIST单元202完成对所有存储器单元404A到404C的测试之后,从影子熔丝寄存器422A到422C新识别的存储器修复签名借助于通过多路复用器424的另一输入移出被存储到存储器修复寄存器408A到408C中。多路复用器420A到420C的另一输入经配置以通过传递来自存储器单元404A到404C中的每一者的相邻影子熔丝寄存器的修复信息来形成移位寄存器。再次,影子熔丝寄存器422A(对应于存储器单元404A)的输出馈送到多路复用器424,其中多路复用器424的输出提供给存储器单元404C。当来自影子熔丝寄存器422A的数据移位到存储器修复寄存器408C中时,存储在影子熔丝寄存器420C和420B中的数据也将分别被移位到420B和420A中。此过程继续,直到用分别来自影子熔丝寄存器422A、422B和422C的数据初始化修复寄存器408A、408B和408C。“或”门430确保影子熔丝寄存器422A到422C在此过程期间使其数据重新循环回。这实现完全递增修复,其中与存储在影子寄存器422A到422C中的那些数据(来自FuseROM的初始加载或来自先前BIST执行)相同的存储在408A到408C中的先前存储器修复数据与来自新BIST测试会话的故障一起累积并修复回相应存储器单元。在过程中的任何点(例如,在本地比较或ECC错误掩码处、在对准和合并处、在修复分析处、在熔丝重新配置处、在影子熔丝累积处等),如果识别出不可修复的错误或故障,那么BIST单元202断言指示不可修复故障的错误。

在一个实例修复方案中,BIST单元202通过执行写/读操作来测试存储器单元404A到404C中的每一者。通过读取预期数据来比较写入到存储器单元404A到404C的数据,以确定每一存储器操作是通过还是失败。响应于失败的存储器操作,执行修复,并且BIST单元202再次测试存储器单元404A到404C。根据需要,重复测试和修复过程。

当启用ECC感知测试时,错误掩码单元504A和504B比较数据并掩蔽ECC可校正错误。此外,在一些实例中,由BIST单元202将多个存储器单元(例如,存储器单元404B和404C)作为一个实体进行测试。当执行递增修复时,数据被写入存储器单元404A。对预期读取的数据进行比较,将其对准到统一格式,对其进行修复分析,并将其与先前的故障进行累积。新修复数据被重新配置回用于存储器单元404A的格式,并与存储器单元404A的影子熔丝寄存器422A中的先前修复一起累积。此外,从熔丝组件425A和425B(例如,FuseROM或其它非易失性存储器)初始化修复和影子(并行广播),并且以相同的顺序将修复内容从影子熔丝寄存器422A传送回到存储器单元404A。同样的过程使用存储器单元404B和404C的相应影子熔丝寄存器422B和422C针对存储器单元404B和404C重复。

在存储器修复方案500中,模式选择单元502根据需要启用或停用ECC修复。当ECC修复被启用时,根据预定的优先级方案执行ECC修复或递增修复。在一些实例中,ECC修复相对于递增修复具有更高的优先级(例如,执行ECC修复,直到不没有ECC可校正错误,然后执行递增修复,直到不再有冗余行/列可用)。在其它实例中,ECC修复相对于递增修复具有更低的优先级(例如,执行递增修复,直到没有更多冗余行/列可用于递增修复,然后执行ECC修复,直到不再有ECC可校正错误)。在其它实例中,ECC修复相对于递增修复的优先级可基于用户输入或预定规则进行调整。

在此描述中,术语“耦合(couple/couples)”意味着间接或直接有线或无线连接。因此,如果第一装置耦合到第二装置,那么那个连接可为通过直接连接或通过经由其它装置及连接的间接连接。陈述“基于”意味着“至少部分基于”。因此,如果X是基于Y,那么X可随Y及任何数目个其它因素而变。

在描述的实施例中修改是可能的,且在权利要求书的范围内,其它实施例是可能的。