具有集成电感器,电阻器和电容器的功率半导体封装

文献发布时间:2023-06-19 10:19:37

技术领域

本发明主要涉及一种半导体封装及其制造方法。更确切地说,本发明涉及一种具有一个集成的电感器、一个集成的电容器以及一个集成的电阻器的驱动金属-氧化物-硅晶体管(DrMOS)。

背景技术

传统的DrMOS在DrMOS封装外部具有一个电感器。图2所示的Yin等人的美国专利号10、111和333,在DrMOS封装中具有一个集成的电感器、一个集成的电容器以及一个集成的电阻器。本发明没有使用金属夹片。在一个示例中,封装的尺寸从7毫米×7毫米×5毫米缩小至6毫米×6毫米×5毫米。电流从20-60安培降至小于10安培。

本发明所述的功率半导体封装包括一个控制器、两个场效应晶体管(FET)以及一个集成的电感器、一个集成的电容器以及一个集成的电阻器。由于集成了电感器,其优点包括更小的外形尺寸、更好的散热和更高的电效率。通过集成方法,针对驱动器和FET动态性能、系统电感和功率FET R

发明内容

本发明提出了一种功率半导体封装,包括一个引线框、一个低端场效应晶体管(FET)、一个高端FET、一个电容器、一个电阻器、一个电感器组件、多个接合引线以及一个模塑封装。

在一个示例中,整个电感器组件都放置在高于整个低端FET、高于整个高端FET并且高于第一种多个接合引线的位置上。在另一个示例中,低端FET的底面和电感器组件的底面是共面的。

附图说明

图1表示在本发明的示例中,一种DrMOS的电路图。

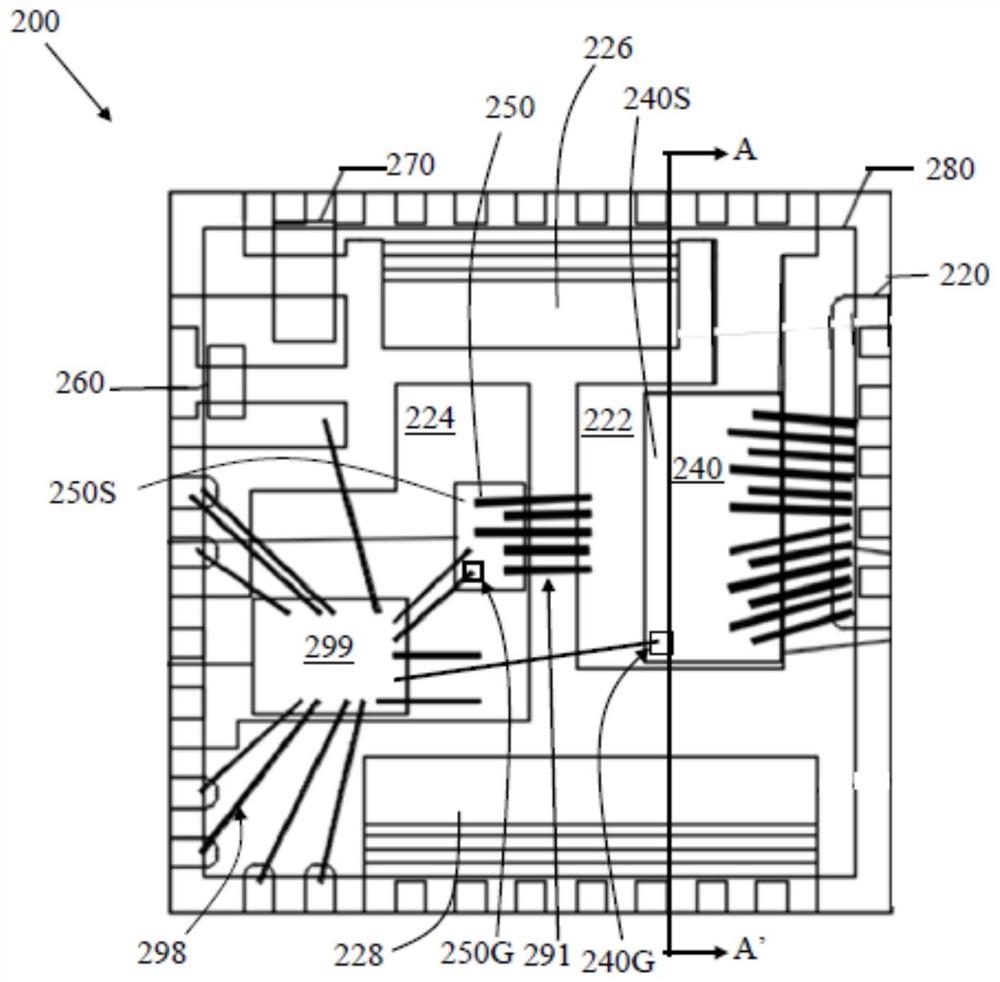

图2A和图2B分别表示在本发明的示例中,功率半导体封装沿AA’线的俯视图和剖面图。

图3A和图3B分别表示在本发明的示例中,功率半导体封装沿BB’线的俯视图和剖面图。

具体实施方式

在本发明的示例中,图1表示一种DrMOS的电路图100。该DrMOS包括一个子封装102。子封装102包括一个控制器110、一个电感器130、一个低端FET 140、一个高端FET 150、多个电容器170以及多个电阻器180。

图2A和图2B分别表示在本发明的示例中,功率半导体封装200沿AA’线的俯视图和剖面图。该功率半导体封装200包括一个引线框220、一个低端场效应晶体管(FET)240、一个高端FET 250、一个电容器260、一个电阻器270、一个电感器组件280、第一种多个接合引线291以及一个模塑封装290。引线框220包括一个第一个芯片焊盘222、一个在第一个芯片焊盘222附近的第二个芯片焊盘224、一个在第一个芯片焊盘222和第二个芯片焊盘224附近的第一个末端焊盘226、以及一个在第一个芯片焊盘222和第二个芯片焊盘224附近但又通过第一个芯片焊盘222和第二个芯片焊盘224与第一个末端焊盘226分隔开的第二个末端焊盘228。第一个末端焊盘226电连接到第一个芯片焊盘222,并作为图1所示的开关节点VSWH端口126。第二个末端焊盘228与引线框的其他部分电绝缘,并作为图1所示的Vout端口128。第一个末端焊盘226和第二个末端焊盘228放置在高于第一个芯片焊盘222和第二个芯片焊盘224的位置上。

低端FET240具有一个底面漏极电极,连接到第一个芯片焊盘222上。低端FET 240包括一个源极电极240S和一个栅极电极240G,在低端FET 240的顶面上。高端FET 250具有一个底面漏极电极,连接到第二个芯片焊盘224上。高端FET 250包括一个源极电极250S和一个栅极电极250G,在高端FET的顶面上。第一种多个接合引线291将高端FET 250的顶面源极电极连接到第一个芯片焊盘222上。

引线框的第一引线231电连接到电感器组件280的第一端口上,并且堆栈在第一个芯片焊盘226上。引线框的第二引线241连接到电感器组件280的第二端口上,并且堆栈在第二个芯片焊盘228上。第一引线231包括一个第一升高部分233,在第一个芯片焊盘222和第二个芯片焊盘224上方。第二引线241包括一个第二升高部分243,在第一个芯片焊盘222和第二个芯片焊盘224上方。至少一部分第一升高部分233构成第一个芯片焊盘226,至少一部分第二升高部分243构成第二个芯片焊盘228。第一引线231的第一升高部分233通过第一导电材料235,电子地并机械地连接到电感器组件280上。第二引线241的第二升高部分243通过第二导电材料245,电子地并机械地连接到电感器组件280上。在一个示例中,第一导电材料235和第二导电材料245中的任何一种导电材料都是由动力冶金材料制成的。在另一个示例中,第一导电材料235和第二导电材料245中的任何一种导电材料都是由一种弹性体材料制成的。在本发明的示例中,第一升高部分233的高度至少比第一芯片焊盘222和第二芯片焊盘224高250微米。第二升高部分243的高度至少比第一芯片焊盘222和第二芯片焊盘224高250微米。如图所示,第一芯片焊盘226和第一引线231形成一个整体,第二模块焊盘228和第二引线241形成一个整体。还可选择,第一末端焊盘226和第二末端焊盘228可以分别通过堆叠在第一引线231和第二引线241的部分上的导电间隔物而形成(图中没有表示出)。

模塑封装290封装了低端FET 240、高端FET 250、第一种多个接合引线291、电容器260、电阻器270、电感器组件280、第一引线231的绝大部分、第二引线241的绝大部分以及引线框220的绝大部分。

在本发明的示例中,引线框220的底面暴露于模塑封装290。第一引线231的底面暴露于模塑封装290。第二引线241的底面暴露于模塑封装290。

在本发明的示例中,电感器组件280的整体都放置在高于低端FET 240的整体、高端FET250的整体以及第一种多个接合引线291的整体的位置上。

在本发明的示例中,功率半导体封装200还包括一个集成电路(IC)299,安装在第二个芯片焊盘224上。第二种多个接合引线298将IC 299连接到引线框220的多个引线上。模塑封装290封装了IC 299。

图3A和图3B分别表示在本发明的示例中,功率半导体封装300沿BB’线的俯视图和剖面图。

功率半导体封装300包括一个引线框320、一个低端场效应晶体管(FET)340、一个高端FET 350、一个电容器360、一个电阻器370、一个电感器组件380、第一种多个接合引线391以及模塑封装390。引线框320包括第一芯片焊盘322、在第一芯片焊盘322附近的第二芯片焊盘324,以及第一末端焊盘326第一芯片焊盘322。

低端FET 340具有一个底面漏极电极,连接到第一芯片焊盘322上。低端FET 340包括一个源极电极340S和一个栅极电极340G,在低端FET 340的顶面上。高端FET 350具有一个底面漏极电极,连接到第二芯片焊盘324上。高端FET 350包括一个源极电极350S和一个栅极电极350G,在高端FET的顶面上。第一种多个接合引线391将高端FET 350的顶面源极电极连接到第一芯片焊盘322上。

模塑封装390封装低端FET340、高端FET 350、第一种多个接合引线391、电容器360、电阻器370、电感器组件380以及引线框320的绝大部分。在本发明的示例中,引线框320的底面暴露于模塑封装390。

在本发明的示例中,低端FET 340的底面341以及电感器组件380的底面381是共面的。

电感器组件380的一个第一端口通过第一导电材料335,电子地并机械地连接到第一芯片焊盘322上。电感器组件的第二端口通过第二导电材料345,电子地并机械地连接到第一末端焊盘326上。在一个示例中,第一导电材料335和第二导电材料345中的任何一种导电材料都是由一种粉末冶金材料制成的。在另一个示例中,第一导电材料335和第二导电材料345中的任何一种导电材料都是由一种弹性体材料制成的。

在本发明的示例中,功率半导体封装300还包括一个安装在第二芯片焊盘324上的集成电路(IC)399。第二种多个接合引线398将IC 399连接到引线框320的多个引线上。模塑封装390封装了IC 399。

本领域的普通技术人员可以理解,本发明公开的实施例的修改是可能存在的。例如,第一升高部分233的高度以及第二升高部分243的高度可以有所不同。本领域普通技术人员还可以想到其他修改,并且所有这样的修改被认为属于本发明的范围之内,如同权利要求所限定的那样。

- 具有集成电感器,电阻器和电容器的功率半导体封装

- 具有集成电感器的功率半导体封装及其制造方法