一种基于忆阻细胞的可重构非线性逻辑门电路

文献发布时间:2023-06-19 13:45:04

技术领域

本发明涉及一种基于忆阻细胞的可重构非线性逻辑门电路,属于忆阻器相关技术领域。

背景技术

蔡少棠教授在1971年首次提出了忆阻器这一概念,直到2008年,惠普实验室才证实了它的存在;忆阻器的出现为摩尔定律即将失效等问题的解决带来了希望,忆阻器的非易失性、纳米级尺寸等特点使得其在存储技术、神经网络等方面有着巨大的优势。

传统的细胞单元是由多个运放构成,极大的增加了电路的集成面积,并且构建的电路只能实现某一特定的逻辑功能,随着忆阻器纳米器件的出现,利用忆阻器与传统的MOS管结合实现可重构的逻辑电路成为目前微电子技术发展的一个重要研究方向。

现有技术中可重构逻辑门电路使用的是运算放大器与固定电阻,不仅集成面积大,而且不可避免的会遇到时滞,再者其实现可重构功能的方法较为复杂,即对于参数值的调整较为复杂。

发明内容

本发明提出的是一种基于忆阻细胞的可重构非线性逻辑门电路,其目的旨在解决现有技术中构建的电路只能实现某一特定逻辑功能的问题。

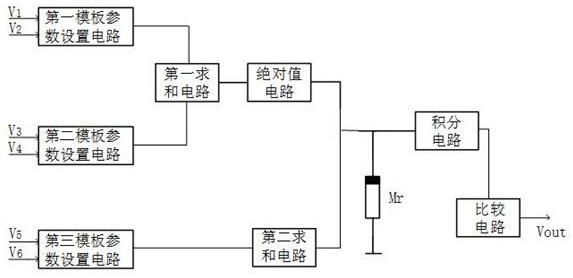

本发明的技术解决方案:一种基于忆阻细胞的可重构非线性逻辑门电路,其结构包括第一模板参数设置电路,第二模板参数设置电路,第三偏置量参数设置电路,第一求和电路,绝对值电路,第二求和电路,积分电路,比较电路;其中,第一模板参数设置电路的输出端与第一求和电路的第一输入端连接,第二模板参数设置电路的输出端与第一求和电路的第二输入端连接,第一求和电路的输出端与绝对值电路的输入端连接,第三偏置量参数设置电路的输出端与第二求和电路输入端连接,第二求和电路输出端与绝对值电路的输出端共同与积分电路的输入端、负载忆阻器Mr的一端连接,积分电路的输出端与比较电路的输入端连接,负载忆阻器Mr的另一端接地。

进一步地,所述第一模板参数设置电路的输入端与1号信号输入端子和2号信号输入端子连接,1号信号输入端子与2号信号输入端子并联,1号信号输入端子上串接有第一开关W1,2号信号输入端子上串接有第二开关W2;所述第二模板参数设置电路的输入端与3号信号输入端子和4号信号输入端子连接,3号信号输入端子与4号信号输入端子并联,3号信号输入端子上串接有第三开关W3,4号信号输入端子上串接有第四开关W4;所述第三偏置量参数设置电路的输入端与5号信号输入端子和6号信号输入端子连接,5号信号输入端子与6号信号输入端子并联,5号信号输入端子上串接有第五开关W5,6号信号输入端子上串接有第六开关W6。

进一步地,所述第一模板参数设置电路中包括第一忆阻器M1、第二忆阻器M2、第三忆阻器M3、第四忆阻器M4、第五忆阻器M5、第一NMOS管U1、第二NMOS管U2、第三NMOS管U3;第一忆阻器M1、第二忆阻器M2、第三忆阻器M3、第四忆阻器M4、第五忆阻器M5构成第一忆阻桥;第一NMOS管U1、第二NMOS管U2、第三NMOS管U3构成第一差分放大器;第一忆阻桥和第一差分放大器共同构成第一忆阻桥突触电路;其中,第一忆阻器M1与第二忆阻器M2反相串联,第三忆阻器M3与第四忆阻器M4反相串联,第五忆阻器M5的正、负两端分别与第一差分放大器的两个栅极连接,第一忆阻器M1与第三忆阻器M3同向串接,第二忆阻器M2与第四忆阻器M4同向串接,第一忆阻器M1与第三忆阻器M3的连接处引出第一忆阻桥突触电路的信号输入端,第二忆阻器M2与第四忆阻器M4的连接处接地;第一忆阻桥突触电路的信号输入端即为第一模板参数设置电路的输入端。

进一步地,所述第二模板参数设置电路中包括第六忆阻器M6、第七忆阻器M7、第八忆阻器M8、第九忆阻器M9、第十忆阻器M10、第四NMOS管U4、第五NMOS管U5、第六NMOS管U6;第六忆阻器M6、第七忆阻器M7、第八忆阻器M8、第九忆阻器M9、第十忆阻器M10构成第二忆阻桥;第四NMOS管U4、第五NMOS管U5、第六NMOS管U6构成第二差分放大器;第二忆阻桥和第二差分放大器共同构成第二忆阻桥突触电路;其中,第六忆阻器M6与第七忆阻器M7反相串联,第八忆阻器M8与第九忆阻器M9反相串联,第十忆阻器M10的正、负两端分别与第二差分放大器的两个栅极连接,第六忆阻器M6与第八忆阻器M8同向串接,第七忆阻器M7与第九忆阻器M9同向串接,第六忆阻器M6与第八忆阻器M8的连接处引出第二忆阻桥突触电路的信号输入端,第七忆阻器M7与第九忆阻器M9的连接处接地;第二忆阻桥突触电路的信号输入端即为第二模板参数设置电路的输入端。

进一步地,所述第三偏置量参数设置电路中包括第十一忆阻器M11、第十二忆阻器M12、第十三忆阻器M13、第十四忆阻器M14、第十五忆阻器M15、第七NMOS管U7、第八NMOS管U8、第九NMOS管U9;第十一忆阻器M11、第十二忆阻器M12、第十三忆阻器M13、第十四忆阻器M14、第十五忆阻器M15构成第三忆阻桥;第七NMOS管U7、第八NMOS管U8、第九NMOS管U9构成第三差分放大器;第三忆阻桥和第三差分放大器共同构成第三忆阻桥突触电路;其中,第十一忆阻器M11与第十二忆阻器M12反相串联,第十三忆阻器M13与第十四忆阻器M14反相串联,第十五忆阻器M15的正、负两端分别与第三差分放大器的两个栅极连接,第十一忆阻器M11与第十三忆阻器M13同向串接,第十二忆阻器M12与第十四忆阻器M14同向串接,第十一忆阻器M11与第十三忆阻器M13的连接处引出第三忆阻桥突触电路的信号输入端,第十二忆阻器M12与第十四忆阻器M14的连接处接地;第三忆阻桥突触电路的信号输入端即为第三偏置量参数设置电路的输入端。

进一步地,所述第一忆阻器M1、第四忆阻器M4的初始阻值相等,所述第二忆阻器M2、第三忆阻器M3、第五忆阻器M5的初始阻值相等,第一忆阻器M1和第四忆阻器M4的初始阻值大于第二忆阻器M2、第三忆阻器M3、第五忆阻器M5的初始阻值。

进一步地,所述第六忆阻器M6、第九忆阻器M9的初始阻值相等,所述第七忆阻器M7、第八忆阻器M8、第十忆阻器M10的初始阻值相等,第六忆阻器M6和第九忆阻器M9的初始阻值大于第七忆阻器M7、第八忆阻器M8、第十忆阻器M10的初始阻值。

进一步地,所述第十一忆阻器M11、第十四忆阻器M14的初始阻值相等,所述第十二忆阻器M12、第十三忆阻器M13、第十五忆阻器M15的初始阻值相等,第十一忆阻器M11和第十四忆阻器M14的初始阻值大于第十二忆阻器M12、第十三忆阻器M13、第十五忆阻器M15的初始阻值。

进一步地,所述第一求和电路包括第十PMOS管U10、第十一PMOS管U11、第十二PMOS管U12、第十三PMOS管U13;其中,第十二PMOS管U12、第十三PMOS管U13的源极分别与第十PMOS管U10、第十一PMOS管U11的漏极对应连接;第十PMOS管U10、第十一PMOS管U11的源极与电源VDD连接;第十PMOS管U10、第十一PMOS管U11的栅极互连;第十二PMOS管U12、第十三PMOS管U13的栅极互连。

进一步地,所述第二求和电路包括第十四PMOS管U14、第十五PMOS管U15、第十六PMOS管U16、第十七PMOS管U17;其中,第十四PMOS管U14、第十五PMOS管U15的漏极分别与第十六PMOS管U16、第十七PMOS管U17的源极对应连接;第十四PMOS管U14、第十五PMOS管U15的源极与电源VDD连接;第十四PMOS管U14、第十五PMOS管U15的栅极互连;第十六PMOS管U16、第十七PMOS管U17的栅极互联。

进一步地,所述绝对值电路包括第一运算放大器J1、第二运算放大器J2、第一二极管D1、第二二极管D2、第一电阻R1、第二电阻R2、第三电阻R3、第四电阻R4、第五电阻R5;其中,第一运算放大器J1的正极与地连接,第一运算放大器J1的负极与第一二极管D1的负极、第一电阻R1、第二电阻R2连接;第一二极管D1的正极与第二二极管D2的负极、第一运算放大器J1的输出端连接;第二二极管D2的正极与第二电阻R2、第三电阻R3连接;第三电阻R3与第二运算放大器J2的负极、第四电阻R4、第五电阻R5连接;第四电阻R4与第二运算放大器J2的输出端连接;第二运算放大器J2的正极与地连接;第一电阻R1与第五电阻R5连接。

进一步地,所述积分电路包括第十八NMOS管U18、第十九NMOS管U19、电容C1;其中,第十八NMOS管U18的源极与第十九NMOS管U19的漏极连接;第十八NMOS管U18的漏极与第十九NMOS管U19的源极连接;第十八NMOS管U18的漏极与电容C1连接;电容C1与电源VSS连接;第十八NMOS管U18的栅极、第十九NMOS管U19的栅极与电源VDD连接。

进一步地,所述比较电路包括第二十PMOS管U20、第二十一PMOS管U21、第六电阻Ri1、第七电阻Ri2、第八电阻Ri3、三极管Q1、第九电阻Rt;其中,第二十PMOS管U20的源极与第二十一PMOS管U21的源极连接,第八电阻Ri3一端与第二十一PMOS管U21的源极连接,第八电阻Ri3的另一端与电源VDD1连接;第二十PMOS管U20的栅极与地连接;第二十PMOS管U20的漏极与第六电阻Ri1连接;第二十一PMOS管U21的漏极与第七电阻Ri2、三极管Q1的基极连接;第六电阻Ri1与第七电阻Ri2相连后接地;三极管Q1的发射极与地连接;三极管Q1的集电极与第九电阻Rt连接;第九电阻Rt与电源Vt连接。

进一步地,一种利用如权利要求3所述的基于忆阻细胞的可重构非线性逻辑门电路进行逻辑功能重构的方法,其特征是该方法包括以下步骤:

1)在比较电路中设置参考电压;

2)利用第一模板参数设置电路设置第一模板参数

3)利用第二模板参数设置电路设置第二模板参数

4)利用第三偏置量参数设置电路设置偏置量参数作为偏置量参数

5)向第一模板参数设置电路、第二模板参数设置电路、第三偏置量参数设置电路中分别输入第二信号V2,第四信号V4,第六信号V6;根据所实现逻辑功能的需要分别将第二信号V2,第四信号V4 设置为高电平或低电平;

6)第二信号V2、第四信号V4、第六信号V6分别在第五忆阻器M5、第十忆阻器M10、第十五忆阻器M15上形成压降,第五忆阻器M5、第十忆阻器M10上的压降分别与第一模板参数

进一步地,所述第六信号V6设置为1v,所述比较电路中设置的参考电压设置为0v;则整个基于忆阻细胞的可重构非线性逻辑门电路的输出端电压为高电平的条件如下式所示:

整个基于忆阻细胞的可重构非线性逻辑门电路的输出端电压为低电平的条件如下式所示:

第二信号V2,第四信号V4分别作为第一模板参数设置电路和第二模板参数设置电路的输入电压,定义输入电压为1v时,对应逻辑“1”;输入电压为-1v,对应逻辑“0”;

此时实现异或电路的条件为:实现异或逻辑的条件为:|

进一步地,所述第一模板参数设置电路实现第一模板参数

对于第一模板参数

对于第二模板参数

对于偏置量参数

本发明一种基于忆阻细胞的可重构非线性逻辑门电路,与现有细胞单元实现可重构逻辑门技术相比,具有以下优点:

1)选用的电路元件少,本发明仅使用两个运放与多个纳米器件,极大减小了电路的集成面积,尺寸小;

2)只需改变输入脉冲的时长即可改变逻辑功能,无需更改内部电路的任何器件以及其参数值,实现了逻辑电路的可重构,并且操作简单,易于实现;

3)采用单个细胞即可实现非线性逻辑电路。

附图说明

附图1为基于忆阻细胞的可重构非线性逻辑门电路的整体结构框图。

附图2为基于忆阻细胞的可重构非线性逻辑门的一个具体应用实施例的完整电路图。

附图3为各参数值所对应的忆阻值变化波形图。

附图4为忆阻器电流变化波形图。

附图5为实施例中异或门的输入输出波形图示意图。

附图6为实施例中同或门的输入输出波形图示意图。

具体实施方式

一种基于忆阻细胞的可重构非线性逻辑门电路,其结构包括第一模板参数设置电路,第二模板参数设置电路,第三偏置量参数设置电路,第一求和电路,绝对值电路,第二求和电路,积分电路,比较电路;其中,第一模板参数设置电路的输出端与第一求和电路的第一输入端连接,第二模板参数设置电路的输出端与第一求和电路的第二输入端连接,第一求和电路的输出端与绝对值电路的输入端连接,第三偏置量参数设置电路的输出端与第二求和电路输入端连接,第二求和电路输出端与绝对值电路的输出端共同与积分电路的输入端、负载忆阻器Mr的一端连接,积分电路的输出端与比较电路的输入端连接,负载忆阻器Mr的另一端接地。

对照发图2,所述第一模板参数设置电路的输入端与1号信号输入端子和2号信号输入端子连接,1号信号输入端子与2号信号输入端子并联,1号信号输入端子上串接有第一开关W1,2号信号输入端子上串接有第二开关W2;所述第二模板参数设置电路的输入端与3号信号输入端子和4号信号输入端子连接,3号信号输入端子与4号信号输入端子并联,3号信号输入端子上串接有第三开关W3,4号信号输入端子上串接有第四开关W4;所述第三偏置量参数设置电路的输入端与5号信号输入端子和6号信号输入端子连接,5号信号输入端子与6号信号输入端子并联,5号信号输入端子上串接有第五开关W5,6号信号输入端子上串接有第六开关W6。

所述第一模板参数设置电路,第二模板参数设置电路,第三偏置量参数设置电路均为相同的参数设置电路,每个参数设置电路均包括五个忆阻器,三个MOS管,五个忆阻器构成忆阻桥,三个MOS管构成差分放大器;五个忆阻器和三个MOS管共同构成忆阻桥突触电路,忆阻桥突触电路的信号输入端子与忆阻桥连接。

所述第一求和电路和第二求和电路均为相同的求和电路,每个求和电路均由四个MOS管构成的电流源电路实现。

对照附图2,所述第一模板参数设置电路中包括第一忆阻器M1、第二忆阻器M2、第三忆阻器M3、第四忆阻器M4、第五忆阻器M5、第一NMOS管U1、第二NMOS管U2、第三NMOS管U3;第一忆阻器M1、第二忆阻器M2、第三忆阻器M3、第四忆阻器M4、第五忆阻器M5构成第一忆阻桥;第一NMOS管U1、第二NMOS管U2、第三NMOS管U3构成第一差分放大器;第一忆阻桥和第一差分放大器共同构成第一忆阻桥突触电路;其中,第一忆阻器M1与第二忆阻器M2反相串联,第三忆阻器M3与第四忆阻器M4反相串联,第五忆阻器M5的正、负两端分别与第一差分放大器的两个栅极连接,第一忆阻器M1与第三忆阻器M3同向串接,第二忆阻器M2与第四忆阻器M4同向串接,第一忆阻器M1与第三忆阻器M3的连接处引出第一忆阻桥突触电路的信号输入端,第二忆阻器M2与第四忆阻器M4的连接处接地;第一忆阻桥突触电路的信号输入端即为第一模板参数设置电路的输入端。

对照附图2,第二模板参数设置电路中包括第六忆阻器M6、第七忆阻器M7、第八忆阻器M8、第九忆阻器M9、第十忆阻器M10、第四NMOS管U4、第五NMOS管U5、第六NMOS管U6;第六忆阻器M6、第七忆阻器M7、第八忆阻器M8、第九忆阻器M9、第十忆阻器M10构成第二忆阻桥;第四NMOS管U4、第五NMOS管U5、第六NMOS管U6构成第二差分放大器;第二忆阻桥和第二差分放大器共同构成第二忆阻桥突触电路;其中,第六忆阻器M6与第七忆阻器M7反相串联,第八忆阻器M8与第九忆阻器M9反相串联,第十忆阻器M10的正、负两端分别与第二差分放大器的两个栅极连接,第六忆阻器M6与第八忆阻器M8同向串接,第七忆阻器M7与第九忆阻器M9同向串接,第六忆阻器M6与第八忆阻器M8的连接处引出第二忆阻桥突触电路的信号输入端,第七忆阻器M7与第九忆阻器M9的连接处接地;第二忆阻桥突触电路的信号输入端即为第二模板参数设置电路的输入端。

对照附图2,所述第三偏置量参数设置电路中包括第十一忆阻器M11、第十二忆阻器M12、第十三忆阻器M13、第十四忆阻器M14、第十五忆阻器M15、第七NMOS管U7、第八NMOS管U8、第九NMOS管U9;第十一忆阻器M11、第十二忆阻器M12、第十三忆阻器M13、第十四忆阻器M14、第十五忆阻器M15构成第三忆阻桥;第七NMOS管U7、第八NMOS管U8、第九NMOS管U9构成第三差分放大器;第三忆阻桥和第三差分放大器共同构成第三忆阻桥突触电路;其中,第十一忆阻器M11与第十二忆阻器M12反相串联,第十三忆阻器M13与第十四忆阻器M14反相串联,第十五忆阻器M15的正、负两端分别与第三差分放大器的两个栅极连接,第十一忆阻器M11与第十三忆阻器M13同向串接,第十二忆阻器M12与第十四忆阻器M14同向串接,第十一忆阻器M11与第十三忆阻器M13的连接处引出第三忆阻桥突触电路的信号输入端,第十二忆阻器M12与第十四忆阻器M14的连接处接地;第三忆阻桥突触电路的信号输入端即为第三偏置量参数设置电路的输入端。

所述第一忆阻器M1、第四忆阻器M4的初始阻值相等,所述第二忆阻器M2、第三忆阻器M3、第五忆阻器M5的初始阻值相等,第一忆阻器M1和第四忆阻器M4的初始阻值大于第二忆阻器M2、第三忆阻器M3、第五忆阻器M5的初始阻值;第一忆阻器M1和第四忆阻器M4的初始阻值均优选为15kΩ,第二忆阻器M2、第三忆阻器M3、第五忆阻器M5的初始阻值均优选为1kΩ。

所述第六忆阻器M6、第九忆阻器M9的初始阻值相等,所述第七忆阻器M7、第八忆阻器M8、第十忆阻器M10的初始阻值相等,第六忆阻器M6和第九忆阻器M9的初始阻值大于第七忆阻器M7、第八忆阻器M8、第十忆阻器M10的初始阻值;第六忆阻器M6和第九忆阻器M9的初始阻值均优选为15kΩ,第七忆阻器M7、第八忆阻器M8、第十忆阻器M10的初始阻值均优选为1kΩ。

所述第十一忆阻器M11、第十四忆阻器M14的初始阻值相等,所述第十二忆阻器M12、第十三忆阻器M13、第十五忆阻器M15的初始阻值相等,第十一忆阻器M11和第十四忆阻器M14的初始阻值大于第十二忆阻器M12、第十三忆阻器M13、第十五忆阻器M15的初始阻值;第十一忆阻器M11和第十四忆阻器M14的初始阻值均优选为15kΩ,第十二忆阻器M12、第十三忆阻器M13、第十五忆阻器M15的初始阻值均优选为1kΩ。

对照附图2,所述第一求和电路包括第十PMOS管U10、第十一PMOS管U11、第十二PMOS管U12、第十三PMOS管U13;其中,第十二PMOS管U12、第十三PMOS管U13的源极分别与第十PMOS管U10、第十一PMOS管U11的漏极对应连接;第十PMOS管U10、第十一PMOS管U11的源极与电源VDD连接;第十PMOS管U10、第十一PMOS管U11的栅极互连;第十二PMOS管U12、第十三PMOS管U13的栅极互连。

对照附图2,所述第二求和电路包括第十四PMOS管U14、第十五PMOS管U15、第十六PMOS管U16、第十七PMOS管U17;其中,第十四PMOS管U14、第十五PMOS管U15的漏极分别与第十六PMOS管U16、第十七PMOS管U17的源极对应连接;第十四PMOS管U14、第十五PMOS管U15的源极与电源VDD连接;第十四PMOS管U14、第十五PMOS管U15的栅极互连;第十六PMOS管U16、第十七PMOS管U17的栅极互联。

所述绝对值电路包括第一运算放大器J1、第二运算放大器J2、第一二极管D1、第二二极管D2、第一电阻R1、第二电阻R2、第三电阻R3、第四电阻R4、第五电阻R5;其中,第一运算放大器J1的正极与地连接,第一运算放大器J1的负极与第一二极管D1的负极、第一电阻R1、第二电阻R2连接;第一二极管D1的正极与第二二极管D2的负极、第一运算放大器J1的输出端连接;第二二极管D2的正极与第二电阻R2、第三电阻R3连接;第三电阻R3与第二运算放大器J2的负极、第四电阻R4、第五电阻R5连接;第四电阻R4与第二运算放大器J2的输出端连接;第二运算放大器J2的正极与地连接;第一电阻R1与第五电阻R5连接。

所述积分电路包括第十八NMOS管U18、第十九NMOS管U19、电容C1;其中,第十八NMOS管U18的源极与第十九NMOS管U19的漏极连接;第十八NMOS管U18的漏极与第十九NMOS管U19的源极连接;第十八NMOS管U18的漏极与电容C1连接;电容C1与电源VSS连接;第十八NMOS管U18的栅极、第十九NMOS管U19的栅极与电源VDD连接。

所述比较电路包括第二十PMOS管U20、第二十一PMOS管U21、第六电阻Ri1、第七电阻Ri2、第八电阻Ri3、三极管Q1、第九电阻Rt;其中,第二十PMOS管U20的源极与第二十一PMOS管U21的源极连接,第八电阻Ri3一端与第二十一PMOS管U21的源极连接,第八电阻Ri3的另一端与电源VDD1连接;第二十PMOS管U20的栅极与地连接;第二十PMOS管U20的漏极与第六电阻Ri1连接;第二十一PMOS管U21的漏极与第七电阻Ri2、三极管Q1的基极连接;第六电阻Ri1与第七电阻Ri2相连后接地;三极管Q1的发射极与地连接;三极管Q1的集电极与第九电阻Rt连接;第九电阻Rt与电源Vt连接。

所述一种基于忆阻细胞的可重构非线性逻辑门电路,其结构还包括第十电阻Ro1,第十一电阻Ro2,第十二电阻Ro3;第十电阻Ro1的一端与第十三PMOS管U13的漏极连接,第十电阻Ro1的另一端与第一电阻R1连接;第十一电阻Ro2的一端与第二运算放大器J2的输出端连接,第十一电阻Ro2的另一端与第十二电阻Ro3连接;第十二电阻Ro3的一端与第十七PMOS管U17的漏极连接,第十二电阻Ro3的另一端与负载忆阻器Mr连接。

一种利用基于忆阻细胞的可重构非线性逻辑门电路进行逻辑功能重构的方法,该方法包括以下步骤:

1)在比较电路中设置参考电压;

2)利用第一模板参数设置电路设置第一模板参数

3)利用第二模板参数设置电路设置第二模板参数

4)利用第三偏置量参数设置电路设置第三偏置量参数作为偏置量参数

5)向第一模板参数设置电路、第二模板参数设置电路、第三偏置量参数设置电路中分别输入第二信号V2,第四信号V4,第六信号V6;根据所实现逻辑功能的需要分别将第二信号V2,第四信号V4 设置为高电平或低电平;所述高电平优选为1 ,低电平优选为-1 ;所述第六信号V6优选设置为1 ;所述第二信号V2、第四信号V4、第六信号V6分别优选从2号信号输入端子、4号信号输入端子、6号信号输入端子输入。

6)第二信号V2、第四信号V4、第六信号V6分别在第五忆阻器M5、第十忆阻器M10、第十五忆阻器M15上形成压降,第五忆阻器M5、第十忆阻器M10上的压降分别与第一模板参数

所述第六信号V6设置为1v,所述比较电路中设置的参考电压设置为0v;则整个基于忆阻细胞的可重构非线性逻辑门电路的输出端电压为高电平的条件如下式所示:

整个基于忆阻细胞的可重构非线性逻辑门电路的输出端电压为低电平的条件如下式所示:

第二信号V2,第四信号V4分别作为第一模板参数设置电路和第二模板参数设置电路的输入电压,定义输入电压为1v时,对应逻辑“1”;输入电压为-1v,对应逻辑“0”;

此时实现异或电路的条件为:实现异或逻辑的条件为:|

所述第一模板参数设置电路实现第一模板参数

对于第一模板参数

对于第二模板参数

对于偏置量参数

本发明在使用时,只需根据需要利用第一模板参数设置电路,第二模板参数设置电路,第三偏置量参数设置电路进行第一模板参数、第二模板参数、偏置量参数的设置,使第一模板参数、第二模板参数、偏置量参数之间满足一定的条件关系即可实现异或逻辑功能或者同或逻辑功能,当需要在异或逻辑功能和同或逻辑功能之间切换时,只需要改变第一模板参数、第二模板参数、偏置量参数的具体设置即可,只需改变第一模板参数设置电路、第二模板参数设置电路、第三偏置量参数设置电路各自输入脉冲信号的时长即可改变逻辑功能,无需更改内部电路的任何器件以及其参数值,实现了逻辑电路的可重构,并且操作简单,易于实现。

实施例1

一种利用基于忆阻细胞的可重构非线性逻辑门电路在细胞神经网络中实现可重构非线性逻辑功能的方法,该方法包括:

步骤(1):在细胞神经网络中,利用输入信号、偏置量参数、模板参数、状态变量,可得下列状态方程:

输出方程则为:

上述方程中,V2、V4分别定义为第一模板参数设置电路和第二模板参数设置电路的输入电压,

步骤(2):假设

步骤(3):由于步骤(2)中的方程只能实现有限数量的线性函数,为了获得输入与模板参数

步骤(4):若要实现逻辑门输出高电平,即

若要实现逻辑门输出低电平,即

步骤(5):细胞实现异或电路时,各参数值

输入信号为(0,1)时,将V2=-1v,V4=1v代入步骤(3),则逻辑门输出高电平的条件为:

输入信号为(1,0)时,将V2=1v,V4=-1v代入步骤(3),则逻辑门输出高电平的条件为:

输入信号都为低电平(0,0)时,将V2=-1v,V4=-1v代入步骤(3),则逻辑门输出低电平的条件为::

综上所述:

实现异或逻辑的各参数取值范围为:|

实现同或逻辑的各参数取值范围为:|

如图2所示,本实施例设计了一种基于忆阻细胞的可重构非线性逻辑门实现电路,设置不同的参数值,即可实现异或与同或电路。

逻辑门电路中的逻辑状态是电压值,其中,定义输入电压为1v,对应逻辑“1”,输入电压为-1v,对应逻辑“0”;输出电压为0v,对应逻辑“0”,输出电压为5v,对应逻辑“1”。

根据上述对逻辑门实现条件的分析进行各参数值

表

具体的参数值设置如下:

各参数的设置由忆阻桥突触电路实现,所述第一模板参数设置电路实现

(1)对于方向的设置,在忆阻桥突触电路中,若输入正向信号,流经中间第五忆阻器M5、第十忆阻器M10、第十五忆阻器M15的电流为正向,则权重为正值;若输入负向信号,流经中间第五忆阻器M5、第十忆阻器M10、第十五忆阻器M15的电流为负向,则权重为负值;

(2)对于大小的设置,在忆阻桥突触电路中,中间忆阻器的阻值大小表示权重大小,输入电压大于中间忆阻器的阈值电压即可改变其阻值大小。

在第一模板参数设置电路中,设置第一忆阻器M1、第四忆阻器M4的初始阻值为15kΩ,第二忆阻器M2、第三忆阻器M3、第五忆阻器M5的初始阻值为1kΩ,输入信号是电压幅值为3v,脉宽为20ms,周期为100ms的脉冲信号;得到阻值的变化即权重的变化曲线如图3所示, 由图可知,第五忆阻器阻值的变化范围为(1k,13k);权重的方向可以通过流经第五忆阻器的电流方向判定;如图4看出,一开始由于第一忆阻器M1、第四忆阻器M4的初始阻值为最大值,第二忆阻器M2、第三忆阻器M3的初始阻值为最小值,根据欧姆定律可得,此时信号通路为第二忆阻器M2、第三忆阻器M3、第五忆阻器M5,流经第五忆阻器M5的电流为负向,则第五忆阻器M5之间的压差VAB为负向,代表此时第一忆阻桥突触电路的权重为负向;随着第一忆阻器M1、第四忆阻器M4的阻值逐渐减小,最终第五忆阻器M5之间的压差VAB会大于0,此时流经第五忆阻器M5的电流方向为正,代表此时权重为正向(第二模板参数、第三偏置量参数设置同理);所以根据图3、图4所对应的正负向权值,当参数值为1时,输入脉冲信号持续1.1s可获得13kΩ,即正向的权值;当参数值为-1时,输入脉冲信号持续0.9s可获得13kΩ,即负向的权值。

图2中,除了对于各参数值的设置,电路实现的另一关键步骤为,为了获得输入与各参数值之间的非线性相关,增加了绝对值模块,以实现模板参数

例如电路实现异或逻辑,图2中,当输入端第二信号V2为低电平,输入端第四信号V4为低电平时,第五忆阻器M5、第十忆阻器M10上的压降与模板参数

异或电路的输出结果如下图5所示,输入电压为(-1v,-1v)时,输出电压为低电压0v;输入电压为(-1v,1v)时,输出电压为高电压5v;输入电压为(1v,-1v)时,输出电压为高电压5v;输入电压为(1v,1v)时,输出电压为低电压0v;

为了进一步证明电路实现可重构非线性逻辑功能的正确性,本发明改变了各参数的值,验证电路实现同或逻辑的功能:由表1中可知,只需要将上述异或电路中模板参数