增强型氮化镓晶体管的结构与使用该结构的封装芯片

文献发布时间:2023-06-19 11:57:35

技术领域

本发明是一种氮化镓晶体管的结构,尤指一种掘入式和原生长晶p型氮化镓(in-situ p-GaN)的增强型氮化镓晶体管的结构。

背景技术

氮化镓高功率组件是由原本空乏型工作方式,转而更有经济效益的增强型模式。目前市场产品皆为p型氮化镓作为栅极控制,但由于氮化镓材料对于p型(p-GaN)活化不易(活化浓度<1×18cm

发明内容

本发明目的之一是提升栅极的临限电压。

本发明目的之一是提升介电层的崩溃电压。

本发明公开一种增强型氮化镓晶体管的结构,包含:一源极电极;一漏极电极;一栅极电极;一p-III族氮化物层,设置于所述栅极电之下;一III族氮化物层,接触所述p-III族氮化物层的下表面、所述漏极电极的下表面、以及所述源极电极的下表面;一III族阻障层,设置于所述III族氮化物层的下表面;以及其中,所述栅极电极或所述漏极电极至少其一为一L型电极,且所述栅极电极与所述源极电极之间、或所述栅极电极与所述漏极电极之间至少其一存在一沟槽,所述沟槽的底部终止于所述III族阻障层之中;所述栅极电极或所述漏极电极的一端设置于所述沟槽之中。

本发明公开一种封装芯片,包含:至少一增强型氮化镓晶体管的结构,所述结构包含:一源极电极;一漏极电极;一栅极电极;一p-III族氮化物层,设置于所述栅极电极之下;一III族氮化物层,接触所述p-III族氮化物层的下表面、所述漏极电极的下表面、以及所述源极电极的下表面;以及一III族阻障层,设置于所述III族氮化物层的下表面;其中,所述栅极电极或所述漏极电极至少其一为一L型电极,且所述栅极电极与所述源极电极之间、或所述栅极电极与所述漏极电极之间至少其一存在一沟槽,所述沟槽的底部终止于所述III族阻障层之中;所述栅极电极或所述漏极电极的一端设置于所述沟槽之中;以及所述封装芯片为所述结构的组合。

附图说明

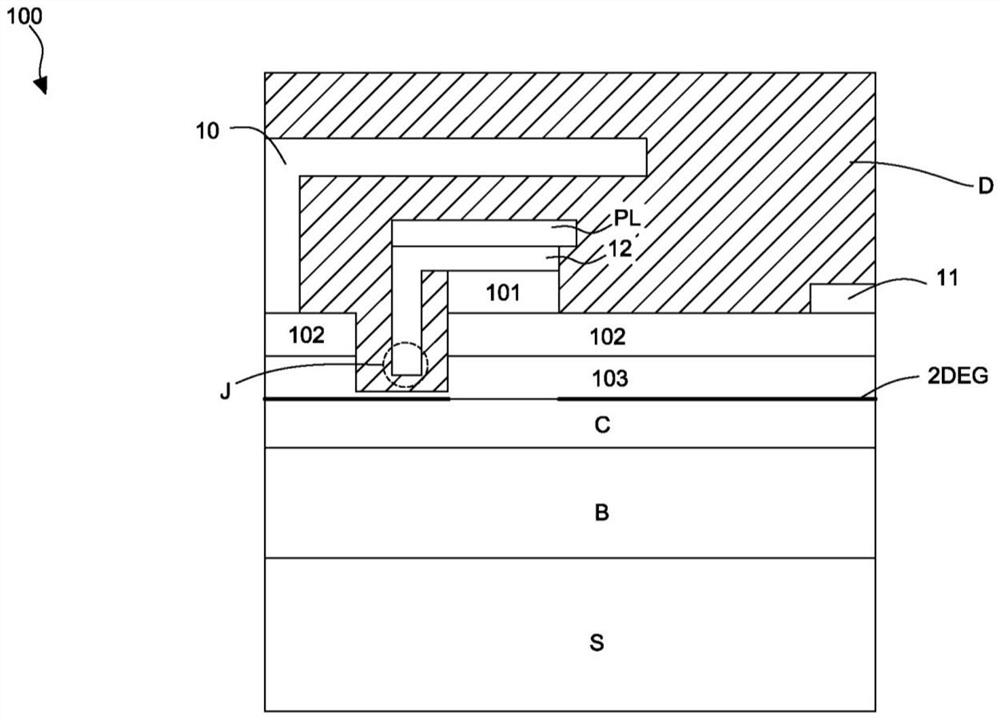

图1A显示本发明增强型氮化镓晶体管的结构一实施例的示意图。

图1B显示基板上表面凸块的侧面示意图。

图1C显示基板上表面凸块的俯视示意图。

图1D显示浓度分布图。

图1E显示掘入式栅极的能带图。

图1F显示p型氮化镓栅极的能带图。

图1G显示掘入式栅极的能带图。

图1H显示p型氮化镓栅极的能带图。

图1I显示漏极电流跟栅极电压图。

图1J显示漏极电流跟漏极电压图。

图1K显示本实施例的电场图。

图1L显示本发明增强型氮化镓晶体管的结构一实施例的示意图。

图2A显示本发明增强型氮化镓晶体管的结构一实施例的示意图。

图2B显示本发明增强型氮化镓晶体管的结构一实施例的示意图。

图3显示一封装芯片的示意图。

符号说明:

100、200 增强型氮化镓晶体管的结构

10 源极电极

11 漏极电极

12 栅极电极

101、201 p-III族氮化物层

102、202 III族氮化物层

103、203 III族阻障层

PL 场效电板

D 介电层

C 通道层

B 缓冲层

S 基板

2DEG 二维电子气

J、K 端

T 凸块

13 二极管

300 封装芯片

30 非掘入式的增强型氮化镓晶体管的结构

具体实施方式

请参考图1A,图1A显示本发明增强型氮化镓晶体管的结构一实施例的示意图。结构100包含:源极电极10、漏极电极11、栅极电极12、p-III族氮化物层101、III族氮化物层102、III族阻障层103、场效电板PL、介电层D、通道层C、缓冲层B、以及基板S。

p-III族氮化物层101,设置于栅极电极12的下;、III族氮化物层102接触p-III族氮化物层101的下表面、漏极电极11的下表面、以及源极电极10的下表面;III族阻障层103设置于III族氮化物层102的下表面。

在一实施例中,p-III族氮化物层101为P型氮化镓(p-GaN)所实现、III族氮化物层102为氮化镓(GaN)所实现。

请注意,在本实施例中,栅极电极12为一L型电极,且栅极电极12与源极电极10之间存在一沟槽R,源极电极10横跨沟槽R,且沟槽R的底部终止于III族阻障层103之中,即沟槽R的底部接近III族阻障层103与通道层C的交界;其中,栅极电极12的一端设置于沟槽R之中,而漏极电极11或源极电极10覆盖部分p-III族氮化物层101的上表面。于一实施例中,栅极电极12的一端J系垂直伸入于沟槽R中,且栅极电极12的一端J不接触III族阻障层103的侧壁,栅极电极12的一端J终止于III族阻障层103所延伸的平面。

除此之外,源极电极10亦为L型电极,栅极电极12与源极电极10之间存在沟槽R,栅极电极12另一端则接触p-III族氮化物层101的上表面。

场效电板PL覆盖部分栅极电极12,且场效电板PL凸出于栅极电极12上表面;以及介电层D填充于沟槽R并覆盖源极电极10的表面、场效电板PL的表面、漏极电极11的表面、栅极电极12的表面、p-III族氮化物层101的表面、III族氮化物层102的表面以及III族阻障层103的表面。

源极电极10为另一个L型电极,源极电极10的一端接触p-III族氮化物层101,另一端延伸于场效电板PL与III族氮化物层102之上,且源极电极10横跨沟槽R。其中,二维电子气2DEG位置如图所示。

请同时参考图1B与图1C,图1B显示基板S上表面凸块T的侧面示意图,图1C显示基板S上表面凸块T的俯视示意图,基板S上表面分布设置两个以上凸块T,凸块T呈数组形排列,且凸块T凸出于基板S上表面,而基板S设置于缓冲层B的下表面;通道层C设置于缓冲层B之上,且通道层C设置于III族阻障层103的下表面。其中,缓冲层B可为氮化铝镓(Al

凸块T的高度小于1μm,凸块T最大长度小于200nm,凸块T之间的距离为490~500nm。

在一实施例中,凸块T可为六角柱状体所实现;上述的结构100可以减少先前技术的缺陷密度,并使结构100减少漏电以及磊晶厚度(磊晶厚度可小于4μm);除此之外,因场效电板PL凸出于栅极电极12上表面、以及源极电极10为另一个L型电极,可同时维持或增加结构100的高崩溃电压。

在一实施例中,凸块T可为六角柱状体所实现;上述的结构100可以减少先前技术的缺陷密度,并使结构100减少漏电以及磊晶厚度(磊晶厚度可小于4μm);除此之外,因场效电板PL凸出于栅极电极12上表面、以及源极电极10为另一个L型电极,可同时维持或增加结构100的高崩溃电压。

顺向导通(Vth)由掘入式和p-GaN栅极空乏至通道浓度降低(Vds=10V,Vgs=0V),随着Vgs=1、5、10V电压增加信道浓度提升,如图1D浓度分布图所示,其中Electron Conc表示电子浓度;图1E~图1H能带图表示掘入式(recessed gate)和p-GaN栅极分别所需电压。

请参考图1I~图1J,图1I显示漏极电流跟栅极电压图,图1J显示漏极电流跟漏极电压图。顺向导通电压随着(Vgs>0V)由掘入式栅极增加导通电流浓度(-2V),随后;大电压(Vgs>>0)增加p-GaN栅极导通(Vgs~2V),以提升整体组件Vth=3.2V。

如图1J所示一般掘入式栅极有较大的导通电阻(Rds,on);然此本发明的结构100有相对低于传统式结构的导通电阻(Rds,on~3mΩ-cm

如图1K所示,图1K显示本实施例的电场图;在高电压下,电场会由掘入式栅极转移至p型氮化镓栅极。

请同时参考图1L,图1L显示本发明增强型氮化镓晶体管的结构一实施例的示意图,结构100的源极电极10可以被一二极管13所共享;或者本实施例的源极电极10可视为两个源极电极10的耦接。

请参考图2A,图2A显示本发明增强型氮化镓晶体管的结构一实施例的示意图。结构200包含:漏极电极11、栅极电极12、p-III族氮化物层201、III族氮化物层202、III族阻障层203、场效电板PL、介电层D、通道层C、缓冲层B、以及基板S。

p-III族氮化物层101,设置于栅极电极12之下;III族氮化物层202接触p-III族氮化物层201的下表面、漏极电极11的下表面、以及源极电极10的下表面;III族阻障层203设置于III族氮化物层202的下表面。

在一实施例中,p-III族氮化物层101为P参杂氮化镓(GaN)所实现、III族氮化物层202为氮化镓(GaN)所实现。

请注意,在本实施例中,漏极电极11为一L型电极,且栅极电极12与漏极电极11之间存在一沟槽R,且沟槽R的底部终止于III族阻障层203之中,意即沟槽R的底部接近III族阻障层203与通道层C的交界;其中,漏极电极11的一端设置于沟槽R之中,而漏极电极11或源极电极10覆盖部分p-III族氮化物层201的上表面。于一实施例中,漏极电极11的一端K系垂直伸入于沟槽R中,且漏极电极11的一端K不接触III族阻障层203的侧壁,漏极电极11的一端J终止于III族阻障层203所延伸的平面。

场效电板PL覆盖部分栅极电极12,且场效电板PL凸出于栅极电极12上表面;以及介电层D填充于沟槽R并覆盖、场效电板PL的表面、源极电极10的表面、漏极电极11的表面、栅极电极12的表面、p-III族氮化物层101的表面、III族氮化物层202的表面以及III族阻障层203的表面。

源极电极10为另一个L型电极,源极电极10的一端接触p-III族氮化物层201,另一端延伸于场效电板PL与III族氮化物层202、栅极电极12、以及沟槽R之上。

结构200的基板S上表面分布设置两个以上凸块T,凸块T呈数组形排列,且凸块T凸出于基板S上表面,而基板S设置于缓冲层B的下表面;通道层C设置于缓冲层B之上,且通道层C设置于III族阻障层203的下表面。同前所述,缓冲层B可为氮化铝镓(Al

凸块T的高度小于1μm,凸块T最大长度小于200nm,凸块T之间的距离为490~500nm。

在一实施例中,凸块T可为六角柱状体所实现;上述的结构200可以减少先前技术的缺陷密度,并使结构200减少漏电以及磊晶厚度(磊晶厚度可小于4um);除此之外,因源极电极10为一个L型电极,可同时维持或增加结构200的高崩溃电压。

请同时参考图2B,图2B显示本发明增强型氮化镓晶体管的结构一实施例的示意图,结构200的源极电极10可以被一二极管13所共享;或者本实施例的源极电极10可视为两个源极电极10的耦接。

接着请同时参考图3,图3显示一封装芯片的示意图。请注意,封装芯片300可以包含至少一个结构100或200或及其组合。

在一实施例中,封装芯片300包含两个非掘入式的增强型氮化镓晶体管的结构30、掘入式的增强型氮化镓晶体管的结构100以及掘入式的增强型氮化镓晶体管的结构200,其中至少一个非掘入式的增强型氮化镓晶体管的结构30与至少其一的结构100或200共享其源极电极10。

在一实施例中,掘入式的增强型氮化镓晶体管的结构200、非掘入式的增强型氮化镓晶体管的结构30、与结构100或200均共享其漏极电极11;除此的外,结构200的源极电极10可为克尔文源极电极(Kelvin Source)所实现。

综上所述,本发明的结构利用掘入式的增强型氮化镓晶体管的结构,可使增强型氮化镓晶体管的结构临限电压大于2V、崩溃电压大于1000V,且本发明结构无迟滞现象产生。

- 增强型氮化镓晶体管的结构与使用该结构的封装芯片

- 基于自对准场板结构的氮化镓增强型垂直功率晶体管