张弛振荡器、集成电路和电子设备

文献发布时间:2023-06-19 13:49:36

技术领域

本公开涉及集成电路技术领域,尤其涉及一种张弛振荡器、集成电路和电子设备。

背景技术

在集成电路中,时钟信号一般由振荡器产生的。张弛振荡器是应用最为普遍的一种振荡器电路,其通过对电容充放电实现振荡信号输出,调节充放电电流或电容的大小能够调节振荡信号的频率。相对于其它各种类型的振荡器,张弛振荡器具有较好的长期频率稳定性,以及较好的温度稳定性,工业界与学术界成员们也不断挖掘其长期频率稳定性与温度稳定性方面的潜力(例如对闪烁噪声的抑制,温度的检测与补偿)。然而张弛振荡器也存在缺点,其高频率偏移下的相位噪声高于环形振荡器(ring oscillator),也因此导致较差的时钟周期抖动。

发明内容

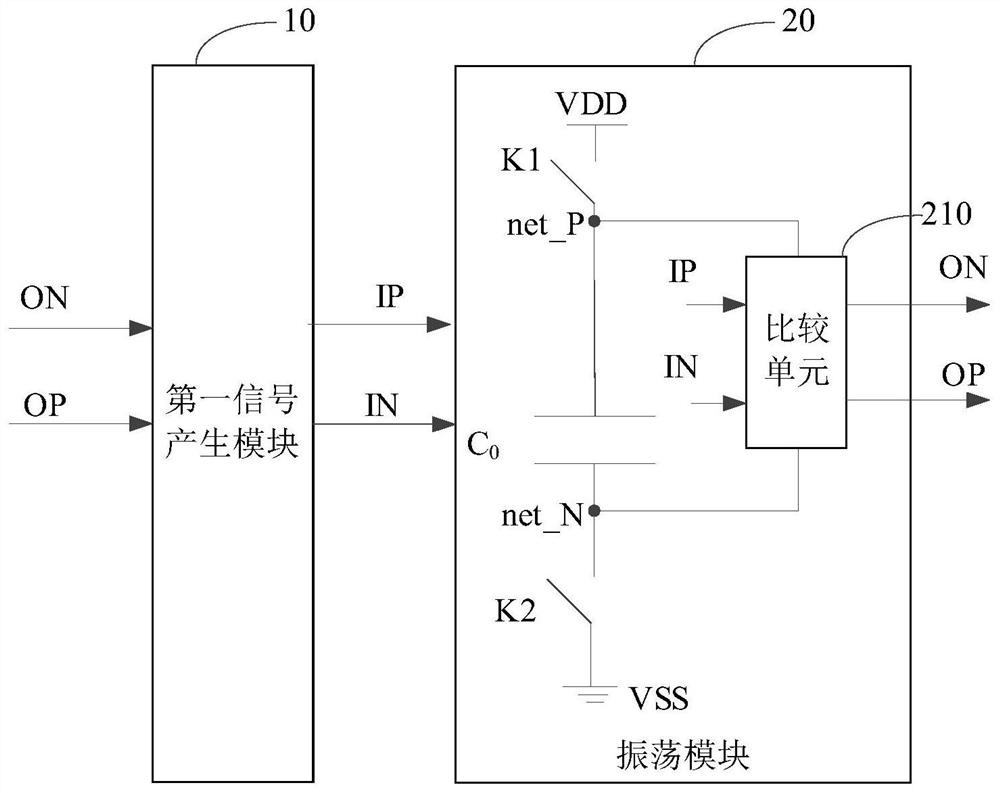

根据本公开的一方面,提供了一种张弛振荡器,所述张弛振荡器包括第一信号产生模块、振荡模块,所述振荡模块用于输出第一振荡信号及第二振荡信号,所述第一振荡信号及所述第二振荡信号相位相反,其中,

所述第一信号产生模块,连接于所述振荡模块,用于根据所述第一振荡信号及所述第二振荡信号产生第一电压信号及第二电压信号,其中,在一个工作周期中,所述第一电压信号从高于电源电压的第一电位逐渐下降到低于阈值电压的第二电位,所述第二电压信号从低于公共接地电压的第三电位逐渐上升到高于所述阈值电压的第四电位;

所述振荡模块,包括第一开关、第二开关、电容、比较单元,所述第一开关的第一端用于接收电源电压,所述第一开关的第二端连接于所述电容的第一端、所述比较单元第一端,所述第二开关的第一端接地,所述第二开关的第二端连接于所述电容的第二端、所述比较单元的第二端,所述比较单元的第一输入端用于输入所述第一电压信号,所述比较单元的第二端用于输入所述第二电压信号,

其中,在所述工作周期的预充电阶段,所述第一开关及所述第二开关被导通,以对所述电容充电,所述电容的第一端及所述电容的第二端分别被充电至所述电源电压、所述公共接地电压;

其中,在所述工作周期的比较阶段,所述第一开关及所述第二开关被断开,所述比较单元分别执行所述第一电压信号、所述第二电压信号与所述阈值电压的比较,并根据比较结果输出所述第一振荡信号及所述第二振荡信号。

在一种可能的实施方式中,所述第一电压信号与所述第二电压信号关于所述阈值电压轴对称,所述阈值电压为所述电源电压与所述公共接地电压之和的二分之一。

在一种可能的实施方式中,所述比较单元用于:

当所述第一电压信号高于所述阈值电压、所述第二电压信号低于所述阈值电压时,所述比较单元输出的第二振荡信号的电位为所述公共接地电压,所述比较单元输出的第一振荡信号的电位为所述电源电压;

当所述第一电压信号下降到低于所述阈值电压、所述第二电压信号上升到高于所述阈值电压时,所述比较单元输出的第二振荡信号的电位为所述电源电压,所述比较单元输出的第一振荡信号的电位为所述公共接地电压。

在一种可能的实施方式中,所述张弛振荡器还包括:

第二信号产生模块,连接于所述第一信号产生模块,用于根据所述第一电压信号及所述第二电压信号产生开关控制信号,以在所述预充电阶段导通所述第一开关及所述第二开关,并在所述比较阶段断开所述第一开关及所述第二开关。

在一种可能的实施方式中,所述第二信号产生模块包括第一驱动晶体管、第二驱动晶体管、第三驱动晶体管、第四驱动晶体管、第五驱动晶体管、第六驱动晶体管,其中,

所述第一驱动晶体管的栅极用于接收所述第一电压信号,所述第一驱动晶体管的源极用于接收电源电压,所述第一驱动晶体管的漏极连接于所述第二驱动晶体管的源极,

所述第二驱动晶体管的栅极用于接收所述第二电压信号,所述第二驱动晶体管的漏极连接于所述第三驱动晶体管的漏极、所述第四驱动晶体管的漏极、所述第五驱动晶体管的栅极及所述第六驱动晶体管的栅极,

所述第三驱动晶体管的栅极用于接收所述第一电压信号,所述第三驱动晶体管的源极接地,

所述第四驱动晶体管的栅极用于接收所述第二电压信号,所述第四驱动晶体管的源极接地,

所述第五驱动晶体管的源极用于接收电源电压,所述第六驱动晶体管的源极接地,所述第五驱动晶体管的漏极连接于所述第六驱动晶体管的漏极,用于输出所述开关控制信号。

在一种可能的实施方式中,所述第一信号产生模块包括斩波开关电路及信号产生单元,所述信号产生单元包括第一电阻、第二电阻、第一电容、第二电容,

所述斩波开关电路的输入端用于接收所述第一振荡信号及所述第二振荡信号,所述斩波开关电路的第一输出端连接于所述第一电阻的第一端、所述第一电容第一端,所述斩波开关电路的第二输出端连接于所述第二电阻的第一端及所述第二电容的第一端,

所述第一电容的第二端连接于所述第二电阻的第二端,用于输出所述第一电压信号;

所述第一电阻的第二端连接于所述第二电容的第二端,用于输出所述第二电压信号。

在一种可能的实施方式中,所述斩波开关电路包括第一斩波开关晶体管、第二斩波开关晶体管、第三斩波开关晶体管,第四斩波开关晶体管,

所述第一斩波开关晶体管的源极连接于所述第二斩波开关晶体管的源极,用于接收电源电压,

所述第一斩波开关晶体管的栅极用于接收所述第二振荡信号,所述第一斩波开关晶体管的漏极与所述第三斩波开关晶体管的源极相连接作为所述斩波开关电路的第一输出端,

所述第二斩波开关晶体管的栅极用于接收所述第一振荡信号,所述第二斩波开关晶体管的漏极与所述第四斩波开关晶体管的源极相连接作为所述斩波开关电路的第二输出端,

所述第三斩波开关晶体管的栅极用于接收所述第二振荡信号,所述第四斩波开关晶体管的栅极用于接收所述第一振荡信号,所述第三斩波开关晶体管的漏极及所述第四斩波开关晶体管的漏极接地。

在一种可能的实施方式中,所述比较单元包括第一比较晶体管、第二比较晶体管、第三比较晶体管、第四比较晶体管,

所述第一比较晶体管的源极及所述第三比较晶体管的源极连接于所述电容的第一端,

所述第一比较晶体管的栅极及所述第二比较晶体管的栅极相连接,用于接收所述第一电压信号,

所述第一比较晶体管的漏极及所述第二比较晶体管的漏极相连接,用于输出所述第一振荡信号,

所述第三比较晶体管的栅极及所述第四比较晶体管的栅极相连接,用于接收所述第二电压信号,

所述第三比较晶体管的漏极及所述第四比较晶体管的漏极相连接,用于输出所述第二振荡信号,

所述第二比较晶体管的源极及所述第四比较晶体管的源极连接于所述电容的第二端。

根据本公开的一方面,提供了一种集成电路,所述集成电路包括所述的张弛振荡器。

根据本公开的一方面,提供了一种电子设备,所述电子设备包括所述的集成电路。

本公开实施例提供一种张弛振荡器,包括第一信号产生模块、振荡模块,本公开实施例利用所述第一信号产生模块根据振荡模块输出的第一振荡信号及第二振荡信号产生第一电压信号及第二电压信号,第一信号产生模块具有信号增幅作用,使得比较单元的摆幅增大,即在一个工作周期中,第一电压信号会在一段时间内高于电源电压,第二电压信号会在一端时间低于公共接地电压,其中,在一个工作周期中,所述第一电压信号从高于电源电压的第一电位逐渐下降到低于阈值电压的第二电位,所述第二电压信号从低于公共接地电压的第三电位逐渐上升到高于所述阈值电压的第四电位,这样利用第一电压信号及第二电压信号可以实现对振荡模块的控制以使得振荡模块输出振荡信号,本公开实施例的振荡模块包括第一开关、第二开关、电容、比较单元,所述第一开关的第一端用于接收电源电压,所述第一开关的第二端连接于所述电容的第一端、所述比较单元第一端,所述第二开关的第一端接地,所述第二开关的第二端连接于所述电容的第二端、所述比较单元的第二端,所述比较单元的第一输入端用于输入所述第一电压信号,所述比较单元的第二端用于输入所述第二电压信号,其中,在所述工作周期的预充电阶段,所述第一开关及所述第二开关被导通,以对所述电容充电,所述电容的第一端及所述电容的第二端分别被充电至所述电源电压、所述公共接地电压;其中,在所述工作周期的比较阶段,所述第一开关及所述第二开关被断开,所述比较单元分别执行所述第一电压信号、所述第二电压信号与所述阈值电压的比较,并根据比较结果输出所述第一振荡信号及所述第二振荡信号,本公开实施例的所述振荡模块采用悬浮地放大器实现比较器,在预充电阶段下,第一振荡信号、第二振荡信号的共模被确定,在比较阶段,实现振荡信号的输出,本公开实施例不需额外设置共模反馈产生电路,也不需增加功耗,相较于相关技术中的张弛振荡器,具有占用面积小、功耗低、噪声小、性能佳的优势。

应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,而非限制本公开。根据下面参考附图对示例性实施例的详细说明,本公开的其它特征及方面将变得清楚。

附图说明

此处的附图被并入说明书中并构成本说明书的一部分,这些附图示出了符合本公开的实施例,并与说明书一起用于说明本公开的技术方案。

图1示出了根据本公开实施例的张弛振荡器的示意图。

图2示出了根据本公开实施例的张弛振荡器的工作时序示意图。

图3示出了根据本公开实施例的张弛振荡器的示意图。

具体实施方式

以下将参考附图详细说明本公开的各种示例性实施例、特征和方面。附图中相同的附图标记表示功能相同或相似的元件。尽管在附图中示出了实施例的各种方面,但是除非特别指出,不必按比例绘制附图。

在本公开的描述中,需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本公开和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本公开的限制。

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本公开的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

在本公开中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本公开中的具体含义。

在这里专用的词“示例性”意为“用作例子、实施例或说明性”。这里作为“示例性”所说明的任何实施例不必解释为优于或好于其它实施例。

本文中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,A和/或B,可以表示:单独存在A,同时存在A和B,单独存在B这三种情况。另外,本文中术语“至少一种”表示多种中的任意一种或多种中的至少两种的任意组合,例如,包括A、B、C中的至少一种,可以表示包括从A、B和C构成的集合中选择的任意一个或多个元素。

另外,为了更好地说明本公开,在下文的具体实施方式中给出了众多的具体细节。本领域技术人员应当理解,没有某些具体细节,本公开同样可以实施。在一些实例中,对于本领域技术人员熟知的方法、手段、元件和电路未作详细描述,以便于凸显本公开的主旨。

相关技术方案中,张弛振荡器的比较器的共模是通过额外的偏置电路实现的,例如通过输出头/尾的拉电流、灌电流的偏置电路来设置,然而,拉电流、灌电流限制了快速边缘跃迁所能达到的最大跨导,并增加了来自偏置电路的噪声,这两者都会对振荡器的相位噪声产生不利影响,使得噪声增大,功耗增加,因此张弛振荡器的性能较差。为了降低噪声,相关技术采用了一些方案,例如,相关技术通常采用提高功耗的方式来抑制噪声,或采用需要笨重的RC滤波器来滤除噪声,这样相关技术会进一步增加功耗,且增大电路的面积,成本更高。

本公开实施例提供一种张弛振荡器,包括第一信号产生模块、振荡模块,本公开实施例利用所述第一信号产生模块根据振荡模块输出的第一振荡信号及第二振荡信号产生第一电压信号及第二电压信号,第一信号产生模块具有信号增幅作用,使得比较单元的摆幅增大,即在一个工作周期中,第一电压信号会在一段时间内高于电源电压,第二电压信号会在一端时间低于公共接地电压,其中,在一个工作周期中,所述第一电压信号从高于电源电压的第一电位逐渐下降到低于阈值电压的第二电位,所述第二电压信号从低于公共接地电压的第三电位逐渐上升到高于所述阈值电压的第四电位,这样利用第一电压信号及第二电压信号可以实现对振荡模块的控制以使得振荡模块输出振荡信号,本公开实施例的振荡模块包括第一开关、第二开关、电容、比较单元,所述第一开关的第一端用于接收电源电压,所述第一开关的第二端连接于所述电容的第一端、所述比较单元第一端,所述第二开关的第一端接地,所述第二开关的第二端连接于所述电容的第二端、所述比较单元的第二端,所述比较单元的第一输入端用于输入所述第一电压信号,所述比较单元的第二端用于输入所述第二电压信号,其中,在所述工作周期的预充电阶段,所述第一开关及所述第二开关被导通,以对所述电容充电,所述电容的第一端及所述电容的第二端分别被充电至所述电源电压、所述公共接地电压;其中,在所述工作周期的比较阶段,所述第一开关及所述第二开关被断开,所述比较单元分别执行所述第一电压信号、所述第二电压信号与所述阈值电压的比较,并根据比较结果输出所述第一振荡信号及所述第二振荡信号,本公开实施例的所述振荡模块采用悬浮地放大器实现比较器,在预充电阶段下,第一振荡信号、第二振荡信号的共模被确定,在比较阶段,实现振荡信号的输出,本公开实施例不需额外设置共模反馈产生电路,也不需增加功耗,相较于相关技术中的张弛振荡器,具有占用面积小、功耗低、噪声小、性能佳的优势。

本公开实施例的张弛振荡器,可以应用于各种规模的集成电路中,以提供时钟或作他用,对此,本公开实施例不做限定。

请参阅图1,图1示出了根据本公开实施例的张弛振荡器的示意图。

请参阅图2,图2示出了根据本公开实施例的张弛振荡器的工作时序示意图。

如图1所示,所述张弛振荡器包括第一信号产生模块10、振荡模块20,所述振荡模块20用于输出第一振荡信号ON及第二振荡信号OP,所述第一振荡信号ON及所述第二振荡信号OP相位相反,其中,

所述第一信号产生模块10,连接于所述振荡模块20,用于根据所述第一振荡信号ON及所述第二振荡信号OP产生第一电压信号IP及第二电压信号IN,其中,如图2所示,在一个工作周期中,所述第一电压信号IP从高于电源电压VDD的第一电位逐渐下降到低于阈值电压VTH的第二电位,所述第二电压信号IN从低于公共接地电压VSS的第三电位逐渐上升到高于所述阈值电压VTH的第四电位;

所述振荡模块20,包括第一开关K1、第二开关K2、电容C

其中,在所述工作周期的预充电阶段,所述第一开关K1及所述第二开关K2被导通,以对所述电容C0充电,所述电容C0的第一端及所述电容C0的第二端分别被充电至所述电源电压VDD、所述公共接地电压VSS;

其中,在所述工作周期的比较阶段,所述第一开关K1及所述第二开关K2被断开,所述比较单元210分别执行所述第一电压信号IP、所述第二电压信号IN与所述阈值电压VTH的比较,并根据比较结果输出所述第一振荡信号ON及所述第二振荡信号OP。

在一个示例中,如图2所示,所述第一电位可以为VDD+VTH或小于VDD+VTH,所述第二电位小于所述阈值电压VTH且大于所述公共接地电压VSS,所述第三电位可以为-VDD-VTH或大于-VDD-VTH,所述第四电位可以大于所述阈值电压VTH且小于所述电源电压VDD,本公开实施例对各个电压的具体电位不做限定,本领域技术人员可以根据实际情况或需要设定。示例性的,一般而言,比较器电路存在等效输入失配电压Voffset,第二电位可以为VTH+m*Voffset,第四电位可以为VTH-n*Voffset,其中,m、n可以为正数,本公开实施例对m、n的具体大小不做限定,本领域技术人员可以根据实际情况及需要设定,示例性的,m、n可以为0.5。本公开实施例对失配电压Voffset的具体大小不做限定,对于不同的比较器电路的各个反相器而言,失配电压Voffset可以是不同的,也可能是相同的

在一种可能的实施方式中,如图2所示,所述第一电压信号IP与所述第二电压信号IN关于所述阈值电压VTH轴对称。应该说明的,此处所说的阈值电压VTH可以视为一个理想值,在实际情况中,由于电路中器件的差异,阈值电压VTH可能有不同的情况。例如,如前所述,比较器电路中的反相器可能具有不同的失配电压Voffset,因此,各个反相器的实际阈值电压可能是不同的,即所述第一电压信号IP、所述第二电压信号IN对应的阈值电压VTH可能是不同的,对此,本公开实施例不做限定。

在一个示例中,所述阈值电压VTH可以为所述电源电压VDD与所述公共接地电压VSS之和的二分之一。示例性的,所述公共接地电压VSS的点位可以为0V,则所述阈值电压VTH可以为VDD/2,本公开实施例以VSS为0进行示例性介绍。

在一个示例中,如图1及图2所示,在所述工作周期的预充电阶段,当所述第一开关K1及所述第二开关K2被导通时,节点net_P(所述电容C

本公开实施例中,工作周期中“预充电”与“比较”两个阶段不依赖准确的时间控制。在“预充电”阶段,电容C

在一种可能的实施方式中,所述比较单元210可以用于:

当所述第一电压信号IP高于所述阈值电压VTH、所述第二电压信号IN低于所述阈值电压VTH时,所述比较单元210输出的第二振荡信号OP的电位为所述公共接地电压VSS,所述比较单元210输出的第一振荡信号ON的电位为所述电源电压VDD;

当所述第一电压信号IP下降到低于所述阈值电压VTH、所述第二电压信号IN上升到高于所述阈值电压VTH时,所述比较单元210输出的第二振荡信号OP的电位为所述电源电压VDD时,所述比较单元210输出的第一振荡信号ON的电位为所述公共接地电压VSS。

通过以上方式,本公开实施例的比较单元210可以在各个周期的比较阶段实现所述第一电压信号IP、所述第二电压信号IN与所述阈值电压VTH的比较,以根据比较结果输出所述第一振荡信号ON及所述第二振荡信号OP。

本公开实施例的所述第一开关K1及所述第二开关K2的开关控制信号Pre的产生方式、来源可以是多样的,对此,本公开实施例不做限定,下面进行示例性介绍。

请参阅图3,图3示出了根据本公开实施例的张弛振荡器的示意图。

在一种可能的实施方式中,如图3所示,所述张弛振荡器还可以包括:

第二信号产生模块30,连接于所述第一信号产生模块10,用于根据所述第一电压信号IP及所述第二电压信号IN产生开关控制信号Pre,以在所述预充电阶段导通所述第一开关K1及所述第二开关K2,并在所述比较阶段断开所述第一开关K1及所述第二开关K2。

本公开实施例中开关控制信号Pre可以由以所述第一电压信号IP及所述第二电压信号IN为输入的第二信号产生模块30产生,应该说明的是,该充电过程对时序的要求非常宽松,且因为在比较单元工作时(比较阶段)所述第一开关K1及所述第二开关K2均处于断开状态,因此预充电不会引入相位噪声,不会对振荡器相噪产生影响,因此,本公开实施例的张弛振荡器允许最小功率设计,可以做到极低功耗。

应该说明的是,虽然本公开实施例以第二信号产生模块30作为开关控制信号Pre的来源进行了示例性介绍,但是,本公开不限于此,开关控制信号Pre也可以由其他电路或组件产生,其产生的方式可以是以所述第一电压信号IP及所述第二电压信号IN为输入,也可以是根据预设的逻辑时序产生,例如,本公开实施例还可以采用脉冲宽度调制PWM电路、信号产生组件等产生开关控制信号Pre,示例性的,可以根据实际情况及需要设置PWM脉宽以产生开关控制信号Pre,本公开实施例对PWM电路的具体实现方式不做限定,本领域技术人员可以利用相关技术实现。示例性的,所述信号产生组件可以按任何适当的方式实现,例如,被一个或多个应用专用集成电路(ASIC)、数字信号处理器(DSP)、数字信号处理设备(DSPD)、可编程逻辑器件(PLD)、现场可编程门阵列(FPGA)、控制器、微控制器、微处理器或其他电子元件实现。在其他的实现方式中,也可以在所述第一开关K1及所述第二开关K2预置控制逻辑,实现在各个工作周期的预充电阶段将所述第一开关K1及所述第二开关K2导通,在各个工作周期的比较阶段将所述第一开关K1及所述第二开关K2断开。

在一种可能的实施方式中,如图3所示,所述第二信号产生模块30可以包括第一驱动晶体管M1、第二驱动晶体管M2、第三驱动晶体管M3、第四驱动晶体管M4、第五驱动晶体管M5、第六驱动晶体管M6,其中,

所述第一驱动晶体管M1的栅极用于接收所述第一电压信号IP,所述第一驱动晶体管M1的源极用于接收电源电压VDD,所述第一驱动晶体管M1的漏极连接于所述第二驱动晶体管M2的源极,

所述第二驱动晶体管M2的栅极用于接收所述第二电压信号IN,所述第二驱动晶体管M2的漏极连接于所述第三驱动晶体管M3的漏极、所述第四驱动晶体管M4的漏极、所述第五驱动晶体管M5的栅极及所述第六驱动晶体管M6的栅极,

所述第三驱动晶体管M3的栅极用于接收所述第一电压信号IP,所述第三驱动晶体管M3的源极接地,

所述第四驱动晶体管M4的栅极用于接收所述第二电压信号IN,所述第四驱动晶体管M4的源极接地,

所述第五驱动晶体管M5的源极用于接收电源电压VDD,所述第六驱动晶体管M6的源极接地,所述第五驱动晶体管M5的漏极连接于所述第六驱动晶体管M6的漏极,用于输出所述开关控制信号Pre。

示例性的,第一驱动晶体管M1、第二驱动晶体管M2可以为驱动能力强的PMOS晶体管,第三驱动晶体管M3、第四驱动晶体管M4可以为驱动能力相对弱的NMOS晶体管,第五驱动晶体管M5可以为PMOS晶体管,第六驱动晶体管M6可以为NMOS晶体管,其中,第一驱动晶体管M1、第二驱动晶体管M2、第三驱动晶体管M3、第四驱动晶体管M4的输出信号net0可以用于通过第五驱动晶体管M5、第六驱动晶体管M6得到所述开关控制信号Pre。

示例性的,结合图2所示,在预充电阶段开始时,所述第一电压信号IP及所述第二电压信号IN的电平会暂时的高于VDD或低于VSS。其中,高于VDD的第一电压信号IP或第二电压信号IN足以驱动较弱的第三驱动晶体管M3、第四驱动晶体管M4,同时关闭较强的第一驱动晶体管M1、第二驱动晶体管M2,从而使net0拉到VSS,继而将开关控制信号Pre设定为VDD,闭合所述第一开关K1及所述第二开关K2。

示例性的,结合图2所示,在比较阶段,由于所述第一电压信号IP及所述第二电压信号IN接近于VDD/2,net0已提前通过强驱动能力的第一驱动晶体管M1、第二驱动晶体管M2被拉到VDD,从而将开关控制信号Pre设定为VSS,断开所述第一开关K1及所述第二开关K2。

应该说明的是,所述第一开关K1及所述第二开关K2的控制电路(第二信号产生模块30)仅仅用于协助电容C

当然,以上介绍示例性的,不应视为是对本公开实施例的限制。

本公开实施例对所述第一开关K1及所述第二开关K2的实现方式不做限定,所述第一开关K1及所述第二开关K2可以通过晶体管实现,也可以通过其他方式实现,上述示例以高电平驱动所述第一开关K1及所述第二开关K2,低电平断开所述第一开关K1及所述第二开关K2为例进行了介绍,但是本公开实施例不限于此,在一些情况下,所述第一开关K1及所述第二开关K2也可以被设置为低电平导通、高电平断开。

本公开实施例对第一信号产生模块10、振荡模块20中比较单元210的具体实现方式不做限定,本领域技术人员可以根据实际情况及需要选择合适的方式实现第一信号产生模块10、振荡模块20的比较单元210,下面对第一信号产生模块10、振荡模块20的比较单元210的可能实现方式进行示例性介绍。

在一种可能的实施方式中,如图3所示,所述第一信号产生模块10可以包括斩波开关电路110及信号产生单元120,所述信号产生单元120包括第一电阻R1、第二电阻R2、第一电容C1、第二电容C2,

所述斩波开关电路110的输入端用于接收所述第一振荡信号ON及所述第二振荡信号OP,所述斩波开关电路110的第一输出端连接于所述第一电阻R1的第一端、所述第一电容C1第一端,所述斩波开关电路110的第二输出端连接于所述第二电阻R2的第一端及所述第二电容C2的第一端,

所述第一电容C1的第二端连接于所述第二电阻R2的第二端,用于输出所述第一电压信号IP;

所述第一电阻R1的第二端连接于所述第二电容C2的第二端,用于输出所述第二电压信号IN。

本公开实施例对斩波开关电路110及信号产生单元120的具体实现方式不做限定,信号产生单元120可以包括其他形式的差分电容电阻网络。示例性的,本公开实施例可以利用信号产生单元120中电阻电容的乘积确定张弛振荡器的工作频率,各个电阻、电容的具体取值决定了其可以达到的最好的相噪性能。例如,如果将电阻缩小一半,电容增大一倍,则工作频率不变,但相位噪声将改善3dB。

在一种可能的实施方式中,如图3所示,所述斩波开关电路110可以包括第一斩波开关晶体管S1、第二斩波开关晶体管S2、第三斩波开关晶体管S3,第四斩波开关晶体管S4,

所述第一斩波开关晶体管S1的源极连接于所述第二斩波开关晶体管S2的源极,用于接收电源电压VDD,

所述第一斩波开关晶体管S1的栅极用于接收所述第二振荡信号OP,所述第一斩波开关晶体管S1的漏极与所述第三斩波开关晶体管S3的源极相连接作为所述斩波开关电路110的第一输出端,

所述第二斩波开关晶体管S2的栅极用于接收所述第一振荡信号ON,所述第二斩波开关晶体管S2的漏极与所述第四斩波开关晶体管S4的源极相连接作为所述斩波开关电路110的第二输出端,

所述第三斩波开关晶体管S3的栅极用于接收所述第二振荡信号OP,所述第四斩波开关晶体管S4的栅极用于接收所述第一振荡信号ON,所述第三斩波开关晶体管S3的漏极及所述第四斩波开关晶体管S4的漏极接地。

本公开实施例通过所述第一振荡信号ON及所述第二振荡信号OP控制斩波开关电路110的工作,交替改变斩波开关电路中各个斩波开关晶体管的导通方式,以增大信号产生单元120输出的两个电压信号的幅度,示例性的,如图2所示,在预充电阶段开始时,所述第一电压信号IP及所述第二电压信号IN的电平会暂时的高于VDD或低于VSS。当然,以上对斩波开关电路110的介绍是示例性的,本公开实施例对此不做限定,在其他的实现方式中,本领域技术人员可以采用相关技术中的斩波开关电路实现。

当然,以上对第一信号产生模块10的介绍是示例性的,本公开实施例对第一信号产生模块10的具体实现方式不做限定,在其他的实施方式中,本公开实施例也可以利用相关技术中的信号产生组件根据所述第一振荡信号及所述第二振荡信号产生第一电压信号及第二电压信号,其中,在一个工作周期中,所述第一电压信号从高于电源电压的第一电位逐渐下降到低于阈值电压的第二电位,所述第二电压信号从低于公共接地电压的第三电位逐渐上升到高于所述阈值电压的第四电位。

在一种可能的实施方式中,如图3所示,所述比较单元210可以包括第一比较晶体管Q1、第二比较晶体管Q2、第三比较晶体管Q3、第四比较晶体管Q4,

所述第一比较晶体管Q1的源极及所述第三比较晶体管Q3的源极连接于所述电容C0的第一端,

所述第一比较晶体管Q1的栅极及所述第二比较晶体管Q2的栅极相连接,用于接收所述第一电压信号IP,

所述第一比较晶体管Q1的漏极及所述第二比较晶体管Q2的漏极相连接,用于输出所述第一振荡信号ON,

所述第三比较晶体管Q3的栅极及所述第四比较晶体管Q4的栅极相连接,用于接收所述第二电压信号IN,

所述第三比较晶体管Q3的漏极及所述第四比较晶体管Q4的漏极相连接,用于输出所述第二振荡信号OP,

所述第二比较晶体管Q2的源极及所述第四比较晶体管Q4的源极连接于所述电容C0的第二端。

示例性的,第一比较晶体管Q1、第二比较晶体管Q2组成第一反相器,第三比较晶体管Q3、第四比较晶体管Q4组成第二反相器,本公开实施例通过第一反相器及第二反相器实现比较单元,并结合第一开关K1、第二开关K2、电容C0组成悬浮地比较器,以应用在张弛振荡器中,可以提高张弛振荡器的性能、降低功耗、噪声,并节约电路面积、节约成本。

以上对比较单元210的介绍示例性的,不应视为是对本公开实施例的限定,在其他的实施方式中,本领域技术人员也可以采用其他方式实现比较单元210。

本公开实施例的振荡模块的“悬浮”工作特性天然确保了输出信号的共模,整个系统中共模与差模充放电能力的差距保证了输出信号能达到满摆幅,进一步提高了振荡器的性能。相较于现有技术中的张弛振荡器,本公开实施例简化了电路元件(例如,无头/尾堆叠MOS,最大化差分增益A_diff;避免复制偏压电路和笨重的R&C噪声滤波器等),在推进FoM(Figure of Merit)的同时缩短设计所需时间。

目前,通常利用FoM对张弛振荡器的性能进行评价,下面对FoM进行介绍。

张弛振荡器相位噪声的理论极限值:

张弛振荡器相位噪声的理论极限值对应的

其中,

P

本公开实施例的张弛振荡器在不考虑全集成的条件下可以得到大于166dB的FoM,且性能在不同工艺角及温度下均保持稳定,即使考虑到全片上集成带来的条件限制,本公开实施例的张弛振荡器仍然可达到大于162dB的FoM,可见,本公开实施例的张弛振荡器具有极高的性能,接近理论极限值。

以上已经描述了本公开的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨在最好地解释各实施例的原理、实际应用或对市场中的技术的改进,或者使本技术领域的其它普通技术人员能理解本文披露的各实施例。