对电源管理系统进行记忆控制的方法和系统及设备

文献发布时间:2023-06-19 19:27:02

技术领域

本发明涉及电源技术领域,尤其涉及一种对电源管理系统进行记忆控制的方法和系统及设备。

背景技术

片上系统(SOC,System on Chip)支持正常运行状态RUN、待机状态STANDBY、停机状态STOP,RUN状态为芯片上电复位(POR)后进入,在RUN模式下芯片所有电源,时钟以及功能模块处于正常工作状态,在STOP模式下,电源模块保持供电,关闭核心时钟core clock,片上系统即电源管理系统中的CPU停止读写闪存单元flash、静态存储器sram,其它时钟源可以由系统软件决定是否关闭;在STANDBY模式下,使得片上系统功耗最低的模式。在STANDBY模式下,片上系统关闭大部分数字电路的电源,仅保留外部唤醒源,时钟模块保留128KHz低速时钟,flash进入deep power down或power off,sram进入记忆retention状态。

片上系统包括:CPU和电源管理控制器(Power management controller,PMC)等,PMC在收到CPU所发送的深度睡眠deep sleep操作之后,其会控制整个系统准备进入待机状态,其需要将CPU、闪存单元flash、静态存储器sram等进入掉电准备状态,这个过程中电源管理控制器会控制静态存储器完成对CPU的记忆操作,使得CPU在掉电过程中将运行指令写入到静态存储器中,在CPU从待机状态进入到运行模式时,电源管理控制器会控制静态存储器完成对CPU的记忆操作,使得CPU在上电过程中从静态存储器中读取运行指令。

目前静态存储器可以采用秘钥管控的方式保障记忆操作的读写控制,但如何保障记忆操作能被安全读写而导致整个电源管理系统不会跑飞就变得尤为重要。

发明内容

本发明的目的在于克服现有技术的不足,本发明提供了一种对电源管理系统进行记忆控制的方法和系统及设备,在记忆控制信号处于变化时,可以同步控制静态存储器完成读写操作,防止各功能单元在掉电过程中所出现的CPU跑飞或者挂死现象。

相应的,本发明提供了一种对电源管理系统进行记忆控制的方法,所述方法包括以下步骤:

电源控制器检测作用于静态存储器上的记忆控制信号是否从无效状态变为有效状态,若判断所述记忆控制信号从无效状态变为有效状态时,则基于外围总线请求设备管理模块发送秘钥;

电源控制器基于外围总线接收设备管理模块发送的秘钥,并将所述秘钥通过CPU记忆控制单元写入到所述静态存储器中;

所述静态存储器基于所述秘钥进行解锁处理,并将所述解锁反馈指令发送到电源控制器;

所述电源控制器控制CPU记忆控制单元对所述静态存储器进行读写操作。

所述方法还包括:

电源控制器检测静态存储器上的记忆控制信号是否从有效状态变为无效状态,若判断所述记忆控制信号从无效状态变为有效状态时,则基于外网总线请求设备管理模块发送复位指令;

电源控制器基于外围总线接收设备管理模块发送的复位指令,并停止所述秘钥写入到所述静态存储器中;

所述静态存储器在识别所述秘钥写入状态消失时,禁止所述CPU记忆控制单元从所述静态存储器中读写数据。

所述静态存储器基于所述秘钥进行解锁处理包括:

所述静态存储器在识别到所述秘钥写入时,解析静态寄存器中的安全数据是否与所述秘钥数据相一致,若所述安全数据和所述秘钥数据相一致则完成对所述静态存储器的解锁。

所述电源控制器控制CPU记忆控制单元对所述静态存储器进行读写操作包括:

在电源管理系统从正常运行状态进入到待机状态时,所述电源控制器控制CPU记忆控制单元从CPU读取运行指令存储到静态存储器中;

在电源管理系统从待机状态进入到正常运行状态时,所述电源控制器控制CPU记忆控制单元从静态存储器中重载运行指令写入到CPU。

所述方法还包括:

电源管理控制器PMC收到深度睡眠指令之后,产生CPU保持住不执行指令holdsleepn信号,并将所述holdsleepn信号发送给CPU;

控制内部低速SIRC时钟时序使得作用于CPU上的holdsleepn信号处于低有效状态,使得电源管理系统准备进入待机状态。

所述方法还包括:

电源控制器检测holdsleepn信号是否从无效状态变为有效状态;

电源控制器若检测到holdsleepn信号从无效状态变为有效状态时,则触发作用于静态存储器上的记忆控制信号从无效状态变为有效状态。

所述方法还包括:

PMC识别到唤醒源wakeup信号出现;

PMC为静态存储器输出隔离控制信号。

相应的,本发明还提供了一种电源管理系统,所述电源管理系统包括:

电源控制器,用于检测作用于静态存储器上的记忆控制信号是否从无效状态变为有效状态,若判断所述记忆控制信号从无效状态变为有效状态时,则基于外围总线请求设备管理模块发送秘钥;基于外围总线接收设备管理模块发送的秘钥,并将所述秘钥通过CPU记忆控制单元写入到所述静态存储器中;控制CPU记忆控制单元对所述静态存储器进行读写操作;

静态存储器,用于基于所述秘钥进行解锁处理,并将所述解锁反馈指令发送到电源控制器;

CPU记忆控制单元,用于在电源控制器的控制下对所述静态存储器进行读写操作。

所述电源控制器还用于检测静态存储器上的记忆控制信号是否从有效状态变为无效状态,若判断所述记忆控制信号从无效状态变为有效状态时,则基于外网总线请求设备管理模块发送复位指令;以及基于外围总线接收设备管理模块发送的复位指令,并停止所述秘钥写入到所述静态存储器中;

所述静态存储器还用于在识别所述秘钥写入状态消失时,禁止所述CPU记忆控制单元从所述静态存储器中读写数据。

相应的,本发明还提供了一种终端设备,所述终端设备包括存储器和处理器,所述处理器执行所述存储器存储的计算机指令,使得所述终端设备执行以上所述的方法。

本发明的方法及系统,电源控制器在识别到记忆控制信号的状态变化,从而触发设备管理模块发送秘钥,可以使得静态存储器处于记忆控制状态时进行解锁处理,在解锁处理完成时,记忆控制单元即可结合CPU的情况完成对静态存储器的读写操作,保障CPU不同状态切换时,CPU的运行指令可以随时响应,使得CPU和电源管理控制器所运行的机制相同,减少在状态变化过程中所出现的CPU跑飞或者挂死现象。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见的,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

图1是本发明实施例中的电源管理系统结构示意图;

图2是本发明第二实施例中的对电源管理系统进行记忆控制的方法流程图;

图3是本发明第三实施例中的对电源管理系统进行记忆控制的方法流程图;

图4是本发明第四实施例中的对电源管理系统进行记忆控制的方法流程图;

图5是本发明第五实施例终端设备的结构示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

实施例一

具体的,图1示出了本发明实施例中的电源管理系统结构示意图,该电源管理系统包括电源管理模块和设备管理模块,所述电源管理模块包括:CPU、CPU记忆控制单元、静态存储器、系统静态存储单元、闪存单元flash、模拟单元、PMC控制单元等等。

该系统支持CPU记忆retention控制,即在进入待机状态STANDBY之前控制从CPU读取运行指令存到静态存储器sram中,在待机状态STANDBY时,系统重新上电后,控制从静态存储器sram重载运行指令写入CPU中。

在正常工作模式RUN下,电源管理系统的1.1v供电由线性稳压器LDO11_MR提供;在低功耗模式下即STANDBY模式,LDO11_MR关闭,由LDO11_LR给芯片供电。其中,静态存储器以及flash的1.1v供电都由LDO11_LR提供。

在待机状态STANDBY下,CPU、CPU记忆控制单元、部分模拟单元包括振荡器,锁相环,CMP,ADC、闪存单元等没有电源供给,其属于电源关闭区域shutdown domain(shut),PMC控制单元、部分模拟单元LDO一直存在电源供给,其属于电源常开区域always-on domain(alon)。

闪存单元flash内部设置有电源开关power switch,可以通过控制供应信号SUPPLYON开关。当SUPPLYON=0时,关闭flash的1.1v和3.3v电源。

该系统支持PAD keep使能控制,及在准备进入待机状态时,主要控制shutdowndomain相关数据输出以及使能信号维持在掉电前的状态。

在系统没有掉电时,可以通过CPU与PMC握手进行abort standby(中止待命)操作,从而防止CPU操作挂死或者跑飞。

这里的电源控制器,用于检测作用于静态存储器上的记忆控制信号是否从无效状态变为有效状态,若判断所述记忆控制信号从无效状态变为有效状态时,则基于外围总线请求设备管理模块发送秘钥;基于外围总线接收设备管理模块发送的秘钥,并将所述秘钥通过CPU记忆控制单元写入到所述静态存储器中;控制CPU记忆控制单元对所述静态存储器进行读写操作;这里的静态存储器,用于基于所述秘钥进行解锁处理,并将所述解锁反馈指令发送到电源控制器;这里的CPU记忆控制单元,用于在电源控制器的控制下对所述静态存储器进行读写操作。

具体实施过程中,所述电源控制器还用于检测静态存储器上的记忆控制信号是否从有效状态变为无效状态,若判断所述记忆控制信号从无效状态变为有效状态时,则基于外网总线请求设备管理模块发送复位指令;以及基于外围总线接收设备管理模块发送的复位指令,并停止所述秘钥写入到所述静态存储器中;所述静态存储器还用于在识别所述秘钥写入状态消失时,禁止所述CPU记忆控制单元从所述静态存储器中读写数据。

电源控制器检测静态存储器上的记忆控制信号是否从有效状态变为无效状态,若判断所述记忆控制信号从无效状态变为有效状态时,则基于外网总线请求设备管理模块发送复位指令;电源控制器基于外围总线接收设备管理模块发送的复位指令,并停止所述秘钥写入到所述静态存储器中;所述静态存储器在识别所述秘钥写入状态消失时,禁止所述CPU记忆控制单元从所述静态存储器中读写数据。

具体实施过程中,所述静态存储器在识别到所述秘钥写入时,解析静态寄存器中的安全数据是否与所述秘钥数据相一致,若所述安全数据和所述秘钥数据相一致则完成对所述静态存储器的解锁。

具体实施过程中,静态存储器为可见寄存器时采用公钥解锁,静态寄存器为不可见寄存器时采用私钥解锁。

本发明实施例中的电源控制器在识别到记忆控制信号的状态变化,从而触发设备管理模块发送秘钥,可以使得静态存储器处于记忆控制状态时进行解锁处理,在解锁处理完成时,记忆控制单元即可结合CPU的情况完成对静态存储器的读写操作,保障CPU不同状态切换时,CPU的运行指令可以随时响应,使得CPU和电源管理控制器所运行的机制相同,减少在状态变化过程中所出现的CPU跑飞或者挂死现象。

实施例二

具体的,图2示出了本发明第二实施例中的对电源管理系统进行记忆控制的方法流程图,图2所示的方法依据图1所示的电源管理系统来实现,该电源管理系统支持CPU记忆retention控制,该方法包括以下步骤:

S201、CPU产生深度睡眠deep sleep指令,并将deep sleep指令发送到PMC;

SOC处于正常运行RUN状态时,在要求进入待机状态STANDBY时,为了保障状态变化,其需要经历等待PMC_WAIT_CPU_HOLD、PMC_RDCPU_REQ、PMC_ISO_ON等状态才能进入到STANDBY模式,其中:

SOC中的RUN状态进入PMC_WAIT_CPU_HOLD状态时,CPU产生深度睡眠deep sleep指令,deep sleep指令会被发送到PMC,PMC会产生CPU保持住不执行指令holdsleepn信号,在此过程中处于PMC需要等待CPU被PMC维持睡眠(hold sleep)状态即PMC_WAIT_CPU_HOLD状态,在这个状态下CPU有电源供给但不执行指令;

在CPU准备进行掉电过程中,由于系统支持CPU记忆retention控制,则系统需要进入CPU retention read请求阶段,即需要从PMC_WAIT_CPU_HOLD状态转入到PMC_RDCPU_REQ状态,在PMC_RDCPU_REQ状态下,CPU有电源供给但不执行指令,PMC会生成CPU记忆指令,然后发送到静态存储器,静态存储器将基于CPU记忆指令向CPU读取当前运行指令以及将所述运行指令写入静态存储器;若整个retention控制完成,PMC需要进入隔离isolation on使能状态即PMC_ISO_ON状态。在PMC_ISO_ON状态中,CPU被PMC hold sleep状态,PMC处于正常运行,其需要使得PMC从正常运行进入到功耗最低的模式完成系统隔离使能状态,在系统隔离使能状态完成后,片上系统关闭大部分数字电路的电压,仅保留外部唤醒源进入STANDBY模式。

隔离使能状态是指shutdown domain输出信号的隔离使能,该隔离使能有效时,输出的信号对always on domain的控制逻辑没有影响,该使能信号无效时,输出的信号是正常的控制逻辑信号。

S202、PMC收到深度睡眠指令之后,产生CPU保持住不执行指令holdsleepn信号,并将所述holdsleepn信号发送给CPU;

在经历等待PMC_WAIT_CPU_HOLD、PMC_RDCPU_REQ、PMC_ISO_ON等状态才能进入到STANDBY模式过程中,CPU仅仅是不执行指令,但得到电源模块的电源供给。

在CPU和PMC之间设置有deep sleep指令、holdsleepn信号、holdsleep_ackn来实现CPU和PMC之间的同步过程。

deep sleep指令为CPU产生的深度睡眠信号,PMC接收到该信号之后开始控制系统进入STANDBY模式。

holdsleepn信号为将CPU保持住不执行指令的信号,由PMC产生并且送入CPU,CPU接收到这一信号,会将CPU状态hold住。holdsleepn信号在进入STANDBY模式过程中,当出现PMC同步wakeup源时,会在第二拍将holdsleepn信号置为无效。

holdsleep_ackn为CPU收到holdsleepn信号后反馈的CPU被hold住的acknowledge信号,由CPU产生送入到PMC部件,holdsleep_ackn信号在holdsleepn无效的时候,第二拍后无效。

所述PMC收到深度睡眠指令之后,产生CPU保持住不执行指令holdsleepn信号,并将所述holdsleepn信号发送给CPU包括:PMC在接收到深度睡眠指令之后,基于内部低速SIRC时钟(sirc_clk)时序产生holdsleepn信号。

S203、PMC控制内部低速SIRC时钟时序使得作用于CPU上的holdsleepn信号处于低有效状态,使得电源管理系统准备进入待机状态;

S204、电源控制器检测holdsleepn信号是否从无效状态变为有效状态;

这里电源控制器通过检测holdsleepn信号的状态变化来触发记忆控制信号的状态变化,使得记忆控制信号能随着电源管理系统的变化自适应调节为待机状态。

具体的,电源控制器若检测到holdsleepn信号从无效状态变为有效状态时,则进入S205触发作用于静态存储器上的记忆控制信号从无效状态变为有效状态;若电源控制器未检测到holdsleepn信号从无效状态变为有效状态时,则返回到S203或者S204中进行相应处理。

S205、触发作用于静态存储器上的记忆控制信号从无效状态变为有效状态;

从保护静态存储器以及节省功耗的角度来看,系统要求进入睡眠模式后,系统就需要将sram的信号CEN/TCEN(在sram端口固定为1)/DFTRAMBYP(在sram端口固定为1)等按spec要求设置为固定值,并将clock gating成0,sram进入低功耗模式。

电源控制器控制sram的信号CEN/TCEN/DFTRAMBYP,以及将sramclock gating在PMC等待CPU被PMC hold sleep状态之后进行。

sram是专门用作CPU retention时存放CPU信息的,因此如果CPU retention有效,那么用作存放CPU retention的sram不能在PMC接收到deepsleep信号之后,需要等CPUretention读操作完成之后,再将CEN固定,clock gating成0,进入低功耗。

sram进入retention收到PMC控制,当PMC进入isolation enable到power down阶段,需要将sram_ret1n信号拉低即触发作用于静态存储器上的记忆控制信号从无效状态变为有效状态,即让sram进入retention状态。

S206、电源控制器检测静态存储器上的记忆控制信号是否从无效状态变为有效状态;

具体的,电源控制器若判断所述记忆控制信号从无效状态变为有效状态时,则进入到S207,否则继续S205。

S207、基于外围总线请求设备管理模块发送秘钥;

S208、电源控制器基于外围总线接收设备管理模块发送的秘钥;

S209、电源控制器将所述秘钥通过CPU记忆控制单元写入到所述静态存储器中;

S210、所述静态存储器基于所述秘钥进行解锁处理,并将所述解锁反馈指令发送到电源控制器;

所述静态存储器在识别到所述秘钥写入时,解析静态寄存器中的安全数据是否与所述秘钥数据相一致,若所述安全数据和所述秘钥数据相一致则完成对所述静态存储器的解锁。

具体实施过程中,在识别到秘钥写入时,首先检测秘钥数据的长度,若秘钥数据的长度满足预设条件时,剥离秘钥数据中的头文件和尾部校验位,提取秘钥中的安全数据,将秘钥中的安全数据和静态寄存器中的安全数据进行比较分析,在判断所述秘钥中的安全数据和所述静态寄存器中的安全数据相一致时,则完成对所述静态寄存器的解锁。

S211、所述电源控制器控制CPU记忆控制单元对所述静态存储器进行读写操作。

电源控制器在检测到sram_ret1n信号低有效产生时,PMC通过外围总线APB发送Key请求指令,连接APB的设备管理模块在收到Key请求指令之后,基于APB向电源控制器提供相关软件控制信息,如LDO,时钟等模拟功能模块所需的控制信息;静态存储器根据设备管理模块所发送的秘钥进行解锁处理,从而控制CPU记忆控制单元完成记忆控制过程。

由于系统支持CPU记忆retention控制,这里的CPU记忆控制单元会在记忆控制信号处于有效时,从CPU中读取运行指令,并将所述运行指令存到静态存储器中。

本发明实施例中的电源控制器从正常运行状态进入到待机状态时,在识别到记忆控制信号的状态变化,从而触发设备管理模块发送秘钥,可以使得静态存储器处于记忆控制状态时进行解锁处理,在解锁处理完成时,记忆控制单元即可结合CPU的情况完成对静态存储器的读写操作,保障CPU不同状态切换时,CPU的运行指令可以随时响应,使得CPU和电源管理控制器所运行的机制相同,减少在状态变化过程中所出现的CPU跑飞或者挂死现象。

实施例三

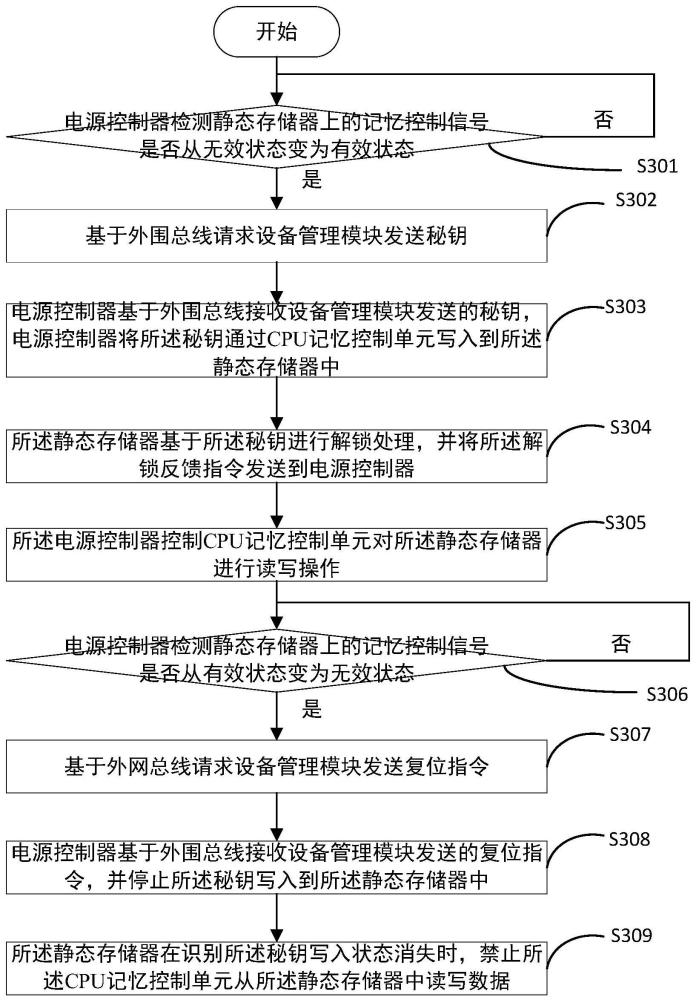

具体的,图3示出了本发明第三实施例中的对电源管理系统进行记忆控制的方法流程图,图3所示的方法依据图1所示的电源管理系统来实现,该电源管理系统支持CPU记忆retention控制,该方法包括以下步骤:

开始;

本发明实施例中的电源控制器控制CPU记忆控制单元对所述静态存储器进行读写操作存在两种情况:在电源管理系统从正常运行状态进入到待机状态时,所述电源控制器控制CPU记忆控制单元从CPU读取运行指令存储到静态存储器中;在电源管理系统从待机状态进入到正常运行状态时,所述电源控制器控制CPU记忆控制单元从静态存储器中重载运行指令写入到CPU。

S301、电源控制器检测作用于静态存储器上的记忆控制信号是否从无效状态变为有效状态,若判断所述记忆控制信号从无效状态变为有效状态时;

本发明实施例中的记忆控制信号的产生可以是在电源管理系统从正常运行状态进入到待机状态时,也可以是在电源管理系统从待机状态进入到正常运行状态时。

S302、基于外围总线请求设备管理模块发送秘钥;

S303、电源控制器基于外围总线接收设备管理模块发送的秘钥,并将所述秘钥通过CPU记忆控制单元写入到所述静态存储器中;

S304、所述静态存储器基于所述秘钥进行解锁处理,并将所述解锁反馈指令发送到电源控制器;

需要说明的是,这里静态存储器在识别到所述秘钥写入时,解析静态寄存器中的安全数据是否与所述秘钥数据相一致,若所述安全数据和所述秘钥数据相一致则完成对所述静态存储器的解锁。

具体实施过程中,在识别到秘钥写入时,首先检测秘钥数据的长度,若秘钥数据的长度满足预设条件时,剥离秘钥数据中的头文件和尾部校验位,提取秘钥中的安全数据,将秘钥中的安全数据和静态寄存器中的安全数据进行比较分析,在判断所述秘钥中的安全数据和所述静态寄存器中的安全数据相一致时,则完成对所述静态寄存器的解锁。

S305、所述电源控制器控制CPU记忆控制单元对所述静态存储器进行读写操作;

CPU记忆控制单元在电源控制器的作用下从CPU读取运行指令,并将运行指令写入到静态存储器中,从而保障CPU的运行指令能完成记忆存储功能。

需要说明的是,在电源管理系统从正常运行状态进入到待机状态时,所述电源控制器控制CPU记忆控制单元从CPU读取运行指令存储到静态存储器中;在电源管理系统从待机状态进入到正常运行状态时,所述电源控制器控制CPU记忆控制单元从静态存储器中重载运行指令写入到CPU。

S306、电源控制器检测静态存储器上的记忆控制信号是否从有效状态变为无效状态;

若判断所述记忆控制信号从无效状态变为有效状态时,则进入S306,否则继续S305步骤,这里通过判断记忆控制信号的变化从而了解到整个记忆操作完成,则需要进一步控制静态存储器的读写操作。

S307、基于外网总线请求设备管理模块发送复位指令;

S308、电源控制器基于外围总线接收设备管理模块发送的复位指令,并停止所述秘钥写入到所述静态存储器中;

S309、所述静态存储器在识别所述秘钥写入状态消失时,禁止所述CPU记忆控制单元从所述静态存储器中读写数据。

本发明实施例通过识别记忆控制信号的状态变化,使得静态存储器可以结合记忆控制信号的有效性来完成解锁处理实现对CPU运行指令的读写功能,保障CPU运行指令读写的有效性,保障CPU不同状态切换时,CPU的运行指令可以随时响应,使得CPU和电源管理控制器所运行的机制相同,减少在状态变化过程中所出现的CPU跑飞或者挂死现象。

实施例四

具体的,图4示出了本发明第二实施例中的对电源管理系统进行记忆控制的方法流程图,图4所示的方法依据图1所示的电源管理系统来实现,该电源管理系统支持CPU记忆retention控制,该方法包括以下步骤:

S401、PMC识别到唤醒源wakeup信号出现;

整个电源管理系统处于待机状态下时,PMC识别到唤醒源出现,其需要对整个电源管理系统中测CPU、CPU记忆控制单元完成上电过程,且在上电的同时需要完成记忆控制过程,从而使得静态存储器中的运行指令能被重载到CPU中,从而保障整个电源管理系统的正常运行过程。

S402、PMC为静态存储器输出隔离控制信号;

需要说明的是,SOC处于正常运行RUN模式时,在要求进入待机模式STANDBY时,为了保障状态变化,其需要经历等待PMC_WAIT_CPU_HOLD、PMC_RDCPU_REQ、PMC_ISO_ON等状态才能进入到STANDBY模式,其中:

SOC中的RUN模式进入PMC_WAIT_CPU_HOLD状态时,CPU产生深度睡眠deep sleep指令,deep sleep指令会被发送到PMC,PMC会产生CPU保持住不执行指令holdsleepn信号,在此过程中处于PMC需要等待CPU被PMC维持睡眠(hold sleep)状态即PMC_WAIT_CPU_HOLD状态,在这个状态下CPU有电源供给但不执行指令;

在CPU准备进行掉电过程中,由于系统支持CPU记忆retention控制,则系统需要进入CPU retention read请求阶段,即需要从PMC_WAIT_CPU_HOLD状态转入到PMC_RDCPU_REQ状态,在PMC_RDCPU_REQ状态下,CPU有电源供给但不执行指令,PMC会生成CPU记忆指令,并同时触发作用于静态存储器上的记忆控制信号从无效状态变为有效状态,CPU记忆控制单元向CPU读取当前运行指令以及将所述运行指令写入静态存储器;若整个retention控制完成,PMC需要进入隔离isolation on使能状态即PMC_ISO_ON状态。在PMC_ISO_ON状态中,CPU被PMC hold sleep状态,PMC处于正常运行,其需要使得PMC从正常运行进入到功耗最低的模式完成系统隔离使能状态,在系统隔离使能状态完成后,片上系统关闭大部分数字电路的电压,仅保留外部唤醒源进入STANDBY模式。

隔离使能状态是指shutdown domain输出信号的隔离使能,该隔离信号有效时,输出的信号对always on domain的控制逻辑没有影响,该隔离控制信号无效时,输出的信号是正常的控制逻辑信号。

电源管理系统从待机状态到正常运行状态时,整个系统会改变隔离使能状态,即改变隔离控制信号的有效性,使得shutdown domain能接收控制逻辑信号,即隔离控制信号从有效变为无效状态,使得整个电源管理系统上的控制逻辑信号满足正常运行。

S403、触发作用于静态存储器上的记忆控制信号从无效状态变为有效状态;

从保护静态存储器以及节省功耗的角度来看,系统要求进入睡眠模式后,系统就需要将sram的信号CEN/TCEN(在sram端口固定为1)/DFTRAMBYP(在sram端口固定为1)等按spec要求设置为固定值,并将clock gating成0,sram进入低功耗模式。

电源控制器控制sram的信号CEN/TCEN/DFTRAMBYP,以及将sramclock gating在PMC等待CPU被PMC hold sleep状态之后进行。

sram是专门用作CPU retention时存放CPU信息的,因此如果CPU retention有效,那么用作存放CPU retention的sram不能在PMC接收到deepsleep信号之后,需要等CPUretention读操作完成之后,再将CEN固定,clock gating成0,进入低功耗。

sram进入retention收到PMC控制,当PMC进入isolation enable到power down阶段,需要将sram_ret1n信号拉低即触发作用于静态存储器上的记忆控制信号从无效状态变为有效状态,即让sram进入retention状态。

S404、电源控制器检测静态存储器上的记忆控制信号是否从无效状态变为有效状态;

具体的,电源控制器若判断所述记忆控制信号从无效状态变为有效状态时,则进入到S405,否则继续S403。

S405、基于外围总线请求设备管理模块发送秘钥;

S406、电源控制器基于外围总线接收设备管理模块发送的秘钥;

S407、电源控制器将所述秘钥通过CPU记忆控制单元写入到所述静态存储器中;

S408、所述静态存储器基于所述秘钥进行解锁处理,并将所述解锁反馈指令发送到电源控制器;

需要说明的是,这里静态存储器在识别到所述秘钥写入时,解析静态寄存器中的安全数据是否与所述秘钥数据相一致,若所述安全数据和所述秘钥数据相一致则完成对所述静态存储器的解锁。

具体实施过程中,在识别到秘钥写入时,首先检测秘钥数据的长度,若秘钥数据的长度满足预设条件时,剥离秘钥数据中的头文件和尾部校验位,提取秘钥中的安全数据,将秘钥中的安全数据和静态寄存器中的安全数据进行比较分析,在判断所述秘钥中的安全数据和所述静态寄存器中的安全数据相一致时,则完成对所述静态寄存器的解锁。

S409、所述电源控制器控制CPU记忆控制单元对所述静态存储器进行读写操作;

S410、电源控制器检测静态存储器上的记忆控制信号是否从有效状态变为无效状态;

若判断所述记忆控制信号从无效状态变为有效状态时,则进入S411,否则继续S410步骤,这里通过判断记忆控制信号的变化从而了解到整个记忆操作完成,则需要进一步控制静态存储器的读写操作。

S411、基于外网总线请求设备管理模块发送复位指令;

S412、电源控制器基于外围总线接收设备管理模块发送的复位指令,并停止所述秘钥写入到所述静态存储器中;

S413、所述静态存储器在识别所述秘钥写入状态消失时,禁止所述CPU记忆控制单元从所述静态存储器中读写数据;

S414、电源管理系统进入正常运行状态。

电源控制器在检测到sram_ret1n信号低有效产生时,PMC通过外围总线APB发送Key请求指令,连接APB的设备管理模块在收到Key请求指令之后,基于APB向电源控制器提供相关软件控制信息,如LDO,时钟等模拟功能模块所需的控制信息;静态存储器根据设备管理模块所发送的秘钥进行解锁处理,从而控制CPU记忆控制单元完成记忆控制过程。

由于系统支持CPU记忆retention控制,这里的CPU记忆控制单元会在记忆控制信号处于有效时,从CPU中读取运行指令,并将所述运行指令存到静态存储器中。

本发明实施例中的电源控制器从待机状态进入到正常运行状态时,在识别到记忆控制信号的状态变化,从而触发设备管理模块发送秘钥,可以使得静态存储器处于记忆控制状态时进行解锁处理,在解锁处理完成时,记忆控制单元即可结合CPU的情况完成对静态存储器的读写操作,保障CPU不同状态切换时,CPU的运行指令可以随时响应,使得CPU和电源管理控制器所运行的机制相同,减少在状态变化过程中所出现的CPU跑飞或者挂死现象。

实施例五

为了便于更好地实施本发明实施例的上述方案,本发明还对应提供了一种终端设备50,下面结合附图来进行详细说明:

如图5示出的本发明实施例提供的终端设备的结构示意图,终端设备50可以包括处理器501、存储器504和通信模块505,处理器501、存储器504和通信模块505可以通过总线506相互连接。存储器504可以是高速随机存储记忆体(Random Access Memory,RAM)存储器,也可以是非易失性的存储器(non-volatile memory),例如至少一个磁盘存储器。存储器504可选的还可以是至少一个位于远离前述处理器501的存储系统。存储器504用于存储应用程序代码,可以包括操作系统、网络通信模块、用户接口模块以及数据处理程序,通信模块505用于与外部设备进行信息交互;处理器501被配置用于调用该程序代码,执行以下步骤:

电源控制器检测作用于静态存储器上的记忆控制信号是否从无效状态变为有效状态,若判断所述记忆控制信号从无效状态变为有效状态时,则基于外围总线请求设备管理模块发送秘钥;

电源控制器基于外围总线接收设备管理模块发送的秘钥,并将所述秘钥通过CPU记忆控制单元写入到所述静态存储器中;

所述静态存储器基于所述秘钥进行解锁处理,并将所述解锁反馈指令发送到电源控制器;

所述电源控制器控制CPU记忆控制单元对所述静态存储器进行读写操作。

以及

电源控制器检测静态存储器上的记忆控制信号是否从有效状态变为无效状态,若判断所述记忆控制信号从无效状态变为有效状态时,则基于外网总线请求设备管理模块发送复位指令;

电源控制器基于外围总线接收设备管理模块发送的复位指令,并停止所述秘钥写入到所述静态存储器中;

所述静态存储器在识别所述秘钥写入状态消失时,禁止所述CPU记忆控制单元从所述静态存储器中读写数据。

所述静态存储器基于所述秘钥进行解锁处理包括:

所述静态存储器在识别到所述秘钥写入时,解析静态寄存器中的安全数据是否与所述秘钥数据相一致,若所述安全数据和所述秘钥数据相一致则完成对所述静态存储器的解锁

需要说明的是,本发明实施例中的终端设备50中处理器的执行步骤可参考上述各方法实施例中图2-4实施例中的方法步骤的具体实现方式,这里不再赘述。

上述计算机可读存储介质可以是前述实施例所述的设备的内部存储单元,例如硬盘或内存。上述计算机可读存储介质也可以是上述设备的外部存储设备,例如配备的插接式硬盘,智能存储卡(Smart Media Card,SMC),安全数字(Secure Digital,SD)卡,闪存卡(Flash Card)等。进一步地,上述计算机可读存储介质还可以既包括上述设备的内部存储单元也包括外部存储设备。上述计算机可读存储介质用于存储上述计算机程序以及上述设备所需的其他程序和数据。上述计算机可读存储介质还可以用于暂时地存储已经输出或者将要输出的数据。

本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,可通过计算机程序来指令相关的硬件来完成,该计算机的程序可存储于计算机可读取存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。而前述的存储介质包括:ROM、RAM、磁碟或者光盘等各种可存储程序代码的介质。

以上对本发明实施例进行了详细介绍,本文中采用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。