一种多芯片三维堆叠扇出型封装结构及其封装方法

文献发布时间:2023-06-19 12:02:28

技术领域

本发明涉及一种多芯片三维堆叠扇出型封装结构及其封装方法,属于芯片封装技术领域。

背景技术

扇出型封装目前为晶圆级先进封装方法之一,由于需封装芯片的数量的不断增加,多芯片所占用的横向面积越来越大,因此,开始将多芯片进行纵向连接,以使得在相同的横向面积中封装更多的芯片,已有的纵向封装技术上下层芯片之间的连接使用的是TSV转接板,该方法存在的问题为封装后的产品中布线密度低,产品厚度高,并且产品成本较高。

发明内容

承上所述,为了弥补已有封装结构的不足,本发明提出了一种多芯片三维堆叠扇出型封装结构及其封装方法,其适用于超高密度多芯片互联,生产成本更低,更易实现生产。

本发明的技术方案:

本发明一种多芯片三维堆叠扇出型封装结构,其自上往下依次包括保护层、第一封装体、第一再布线金属层、第二封装体以及第二再布线金属层,第一封装体与第二封装体通过第一再布线金属层进行电信号连接,第一封装体设置在第一再布线金属层的上方,第二封装体设置在第一再布线金属层的下方,第二再布线金属层设置在第二封装体的下方,球栅极阵列焊球设置在第二再布线金属层的下方;

所述第一封装体包括多个芯片封装体Ⅰ以及塑封料Ⅰ,所述芯片封装体Ⅰ包括芯片Ⅰ、粘接剂层、凸块金属以及绝缘层Ⅰ,绝缘层Ⅰ分布在芯片封装体Ⅰ的正面,露出芯片Ⅰ的电极位置,在芯片Ⅰ的正面电极位置设置凸块金属,凸块金属通过绝缘层Ⅰ与凸块电极实现电信号连接,芯片Ⅰ的背面采用粘接剂层固定,粘接剂层完全包覆芯片Ⅰ,所述保护层通过粘接剂层与芯片封装体Ⅰ的背面固连,并延展至第一封装体的整个表面;

所述塑封料Ⅰ包裹多个芯片封装体Ⅰ并填充凸块金属的间隙,塑封料Ⅰ的高度与多个芯片封装体Ⅰ的背面高度齐平,塑封料Ⅰ的正面与凸块金属的高度齐平,露出凸块金属位置;

所述第一再布线金属层设置于第一封装体的下方,所述第一再布线金属层的底部设置金属焊盘Ⅰ,其与凸块金属形成电信号连接,第一再布线金属层的上方设置金属焊盘,再布线金属层的金属焊盘包括金属焊盘Ⅴ和金属焊盘Ⅵ,金属焊盘Ⅴ预留给互联金属柱,金属焊盘Ⅵ预留给芯片封装体Ⅱ,在芯片封装体Ⅱ的上方预设有金属连接层Ⅰ,在金属焊盘Ⅵ的上方预设有金属连接层Ⅱ;

所述第二封装体包括多个芯片封装体Ⅱ、塑封料Ⅱ以及多个互联金属柱,所述芯片封装体Ⅱ包括芯片Ⅱ以及绝缘层Ⅱ,绝缘层Ⅱ完全覆盖芯片Ⅱ的正面,并设有露出金属连接层Ⅰ的开口,金属连接层Ⅰ的底部与芯片Ⅱ的电极形成电信号连接,金属连接层Ⅰ的高度突出绝缘层高度,将芯片Ⅱ正装在第一再布线金属层的金属焊盘Ⅵ的上方,芯片Ⅱ的金属连接层Ⅰ和第一再布线金属层的金属焊盘Ⅵ连接,信号依次从芯片Ⅱ、芯片Ⅱ表面的金属连接层Ⅰ、第一再布线金属层的金属焊盘Ⅵ、金属连接层Ⅱ、第一再布线金属层、芯片Ⅰ;

所述互联金属柱分布在芯片封装体Ⅱ的周围,互联金属柱的底部与第二再布线金属层的金属焊盘Ⅲ形成信号连接,将芯片Ⅰ和芯片Ⅱ的信号通过第二再布线金属层、互联金属柱以及球栅极阵列焊球向下传导,所述塑封料Ⅱ填充互联金属柱和芯片封装体Ⅱ的间隙,完全包覆芯片封装体Ⅱ,塑封料Ⅱ的高度与互联金属柱的高度齐平;

所述第二再布线金属层设置在互联金属柱的下方,第二再布线金属层的金属焊盘Ⅲ和互联金属柱形成电信号连接,所述第二再布线金属层的金属焊盘Ⅳ通过回流形成球栅极阵列焊球,将信号向下传导。

可选地,所述金属焊盘Ⅰ为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层。

可选地,所述金属焊盘Ⅲ为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层。

可选地,所述球栅极阵列焊球为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层。

可选地,所述金属焊盘Ⅴ和金属焊盘Ⅵ均为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层。

可选地,所述凸块金属为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层。

可选地,所述金属连接层Ⅰ为单层金属层或者为复合金属层。

可选地,所述金属连接层Ⅱ为单层金属层或者为复合金属层,金属为导电性能优异的铜、镍、锡、银等。

可选地,所述保护层为树脂和金属的复合层。

本发明还提供了一种多芯片三维堆叠扇出型封装结构的封装方法,其实施步骤如下:

步骤一、取一片临时载片;

步骤二、在上述临时载片表面涂敷一层可释放涂层;

步骤三、将芯片Ⅰ的背面通过粘接剂倒装在可释放图层的上表面,芯片Ⅰ的正面有绝缘层Ⅰ包覆,并通过凸块金属进行电信连接;

步骤四、采用塑封料Ⅰ补充芯片封装体Ⅰ的间隙,完全包覆芯片封装体Ⅰ的金属凸块,形成重构圆片,实现扇出型封装;

步骤五、通过研磨工艺,露出被包覆的芯片封装体Ⅰ的金属凸块,塑封料Ⅰ的高度与芯片封装体Ⅰ的金属凸块高度齐平;

步骤六、在第一封装体的表面通过多次依次涂胶、曝光和显影的方式形成再布线金属层,再布线金属层的底部设置金属焊盘Ⅰ,金属焊盘Ⅰ与塑封后芯片封装体Ⅰ的上层金属凸块进行电信号连接,再布线金属层的金属焊盘包括金属焊盘Ⅴ和金属焊盘Ⅵ,金属焊盘Ⅴ预留给互联金属柱,金属焊盘Ⅵ预留给芯片封装体Ⅱ;

步骤七、在再布线金属层上方预留出芯片封装体Ⅱ的区域,在区域的下方区域的再布线金属层上表面设置金属焊盘Ⅵ,再布线金属层的上表面预设置金属焊盘Ⅴ,用于连接互联金属柱;在区域外通过涂胶、曝光、显影和电镀的方式形成互联金属柱,互联金属柱分布在芯片封装体Ⅱ的周围,其底部与再布线金属层的金属焊盘Ⅴ连接,互联金属柱与再布线金属层形成电信连接;

步骤八、将芯片封装体Ⅱ正装在再布线金属层的区域,芯片封装体Ⅱ的金属连接层Ⅰ和再布线金属层的金属焊盘Ⅵ加热或加压形成互联,芯片封装体Ⅰ与芯片封装体Ⅱ通过再布线金属层形成超高密度信号互联,金属连接层Ⅰ为单层金属层或者为复合金属层,金属为导电性能优异的铜、镍、锡、银等;

步骤九、采用塑封料Ⅱ填充互联金属柱的间隙,且完全包覆芯片封装体Ⅱ和互联金属柱;

步骤十、通过研磨工艺,将塑封料Ⅱ和互联金属柱的高度减薄,露出金属互联柱的上表面,且塑封料Ⅱ依旧保持包覆芯片封装体Ⅱ;

步骤十一、在塑封料Ⅱ的表面和互联金属柱露出的表面通过多次依次涂胶、曝光、显影以及电镀的方式形成再布线金属层,再布线金属层的金属焊盘Ⅲ和互联金属柱电信号连接,再布线金属层的上方设置金属焊盘Ⅳ,用于回流形成球栅极阵列焊球;

步骤十二、再布线金属层的金属焊盘Ⅳ上方依次通过涂胶、曝光、显影和电镀形成复合金属层,通过回流形成球栅极阵列焊球,将信号向下传导;

步骤十三、通过激光或者加热的方式将可释放涂层释放,将临时载片和第一封装体剥离,最终实现解键合的目的;

步骤十四、保护层通过粘接剂层与芯片封装体Ⅰ的背面固连,并延展至第一封装体的整个表面,保护层为树脂和金属的复合层;

步骤十五、将整张圆片通过切割划成复数颗单体,形成最终的单颗封装体。

有益效果

1.本发明芯片三维堆叠扇出型封装结构,横向多个芯片之间采用再布线金属层进行电路互联形成横向扇出型结构,纵向多个芯片之间采用互联金属柱和再布线金属层电路互联形成纵向扇出型结构,最终通过球栅极阵列导出芯片,形成高度密度互联的三维封装结构,芯片之间的互联间距小、互联密度高、传输效率高;

2.基于本发明提供的该种封装结构和制备方法,芯片背面覆盖保护层,有助于提高芯片的机械强度,虽然保护层的厚度较薄,通常只有几十微米,但保护层的厚度可以进行调控,垂直高度较低,整体厚度更薄,相比传统的扇出型封装结构或三维堆叠工艺,该方案集成度更高且更有利于实现。

附图说明

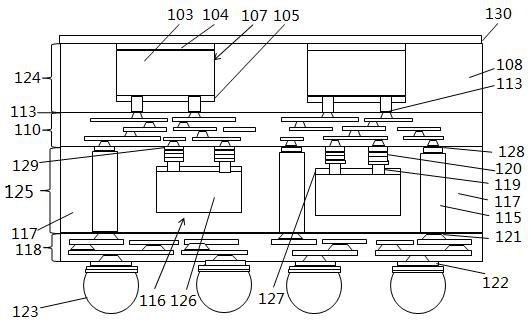

图1为本发明一种多芯片三维堆叠扇出型封装结构的剖面示意图;

图2为图1中第一封装体中的芯片封装体Ⅰ的分布示意图;

图3为图1中第二封装体中的芯片封装体Ⅱ的分布示意图;

图4A到图4O为本发明一种多芯片三维堆叠扇出型封装结构的封装方法的流程示意图;

其中:

芯片Ⅰ103

粘接剂层104

绝缘层Ⅰ105

凸块金属106

芯片封装体Ⅰ107

塑封料Ⅰ108

第一再布线金属层110

金属焊盘Ⅰ113

互联金属柱115

芯片封装体Ⅱ116

塑封料Ⅱ117

第二再布线金属层118

金属连接层Ⅰ119

金属连接层Ⅱ120

金属焊盘Ⅲ121

金属焊盘Ⅳ122

球栅极阵列焊球123

第一封装体124

第二封装体125

芯片Ⅱ126

绝缘层Ⅱ127

金属焊盘Ⅴ128

金属焊盘Ⅵ129

保护层130

临时载片101

可释放涂层102。

具体实施方式

现在将在下文中参照附图更加充分地描述本发明,在附图中示出了本发明的示例性实施例,从而本公开将本发明的范围充分地传达给本领域的技术人员。然而,本发明可以以许多不同的形式实现,并且不应被解释为限制于这里阐述的实施例。

下面结合附图和实施例对本发明进行进一步地说明。

如图1至图3所示,一种三维堆叠的扇出型封装结构,其自上往下依次包括保护层130、第一封装体124、第一再布线金属层110、第二封装体125以及第二再布线金属层118,第一封装体124与第二封装体125通过第一再布线金属层110进行电信号连接,第一封装体124设置在第一再布线金属层110的上方,第二封装体125设置在第一再布线金属层110的下方,第二再布线金属层118设置在第二封装体125的下方,球栅极阵列焊球123设置在第二再布线金属层118的下方。

第一封装体124包括多个芯片封装体Ⅰ107以及塑封料Ⅰ108;芯片封装体Ⅰ107包括芯片Ⅰ103、粘接剂层104、凸块金属106以及绝缘层Ⅰ105,绝缘层Ⅰ105分布在芯片封装体Ⅰ107的正面,露出芯片Ⅰ103的电极位置,在芯片Ⅰ103的正面电极位置设置凸块金属106,凸块金属106通过绝缘层Ⅰ105与凸块电极实现电信号连接,芯片Ⅰ103的背面采用粘接剂层104固定,粘接剂层104完全包覆芯片Ⅰ103,该粘接剂层104与芯片Ⅰ103的尺寸相同。粘接剂层104是由黏附层、填充物与支撑体混合的可导热绝缘薄膜,例如:PI(聚酰亚胺)、PBO(水晶玻璃)、BCB(苯并环丁烯)、EMC(环氧树脂塑料)、树脂等。凸块金属106为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层。

保护层130通过粘接剂层104与芯片封装体Ⅰ107的背面固连,并延展至第一封装体124的整个表面。保护层130为树脂和金属的复合层,其具有遮光、绝缘、导热、屏蔽、防止芯片氧化、隔绝水汽、防止芯片划伤、控制封装结构的厚度以及控制芯片之间的纵向连接距离的作用。

塑封料Ⅰ108包裹多个芯片封装体Ⅰ107并填充凸块金属106的间隙,塑封料Ⅰ108的高度与多个芯片封装体Ⅰ107的背面高度齐平,塑封料Ⅰ108的正面与凸块金属106的高度齐平,露出凸块金属106位置。

第一再布线金属层110设置于第一封装体124的下方,第一再布线金属层110包含绝缘层和金属层,绝缘层和金属层间隔分布,第一再布线金属层110的底部设置金属焊盘Ⅰ113,金属焊盘Ⅰ113为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层,其与凸块金属106形成电信号连接,第一再布线金属层110的上方设置金属焊盘,再布线金属层110的金属焊盘包括金属焊盘Ⅴ128和金属焊盘Ⅵ129,金属焊盘Ⅴ128和金属焊盘Ⅵ129均为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层。金属焊盘Ⅴ128预留给互联金属柱115,金属焊盘Ⅵ129预留给芯片封装体Ⅱ116,在芯片封装体Ⅱ116的上方预设有金属连接层Ⅰ119,金属连接层Ⅰ119为单层金属层或者为复合金属层,金属为导电性能优异的铜、镍、锡、银等,在金属焊盘Ⅵ129的上方预设有金属连接层Ⅱ120,金属连接层Ⅱ120为单层金属层或者为复合金属层,金属为导电性能优异的铜、镍、锡、银等。金属连接层Ⅰ119和金属连接层Ⅱ120厚度根据实际需要调整。

第二封装体125包括多个芯片封装体Ⅱ116、塑封料Ⅱ117以及多个互联金属柱115。芯片封装体Ⅱ116包括芯片Ⅱ126以及绝缘层Ⅱ127,绝缘层Ⅱ127完全覆盖芯片Ⅱ126的正面,露出金属连接层Ⅰ119的开口,金属连接层Ⅰ119的底部与芯片Ⅱ126的电极形成电信号连接,金属连接层Ⅰ119的高度突出绝缘层高度,将芯片Ⅱ126正装在第一再布线金属层110的金属焊盘Ⅵ129的上方,芯片Ⅱ126的金属连接层Ⅰ119和第一再布线金属层110的金属焊盘Ⅵ129连接,信号依次从芯片Ⅱ126、芯片Ⅱ126表面的金属连接层Ⅰ119、第一再布线金属层110的金属焊盘Ⅵ129、金属连接层Ⅱ120、第一再布线金属层110,向芯片Ⅰ103传导。

互联金属柱115分布在芯片封装体Ⅱ116的周围,互联金属柱115的底部与第二再布线金属层118的金属焊盘Ⅲ121形成信号连接,将芯片Ⅰ103和芯片Ⅱ126的信号通过第二再布线金属层118、互联金属柱115以及球栅极阵列焊球123向下传导。金属焊盘Ⅲ121为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层。

塑封料Ⅱ117填充互联金属柱115和芯片封装体Ⅱ116的间隙,完全包覆芯片封装体Ⅱ116,增强芯片封装体Ⅱ116的机械性能,塑封料Ⅱ117的高度与互联金属柱115的高度齐平。

第二再布线金属层118设置在互联金属柱115的下方,第二再布线金属层118的金属焊盘Ⅲ121和互联金属柱115形成电信号连接。第二再布线金属层118包括多层金属层和绝缘层,绝缘层和金属层间隔分布,第二再布线金属层118的金属焊盘Ⅳ122通过回流形成球栅极阵列焊球123,球栅极阵列焊球123为复合金属层,其包括铜层、镍层、锡层和银层,镍层覆盖铜层,锡层分布在镍层的外层,银层覆盖在最外层,将信号向下传导。

如图4A至图4O所示,本发明还提供了一种三维扇出型封装结构的封装方法, 其实施步骤如下:

步骤一、如图4A所示,取一片临时载片101;

步骤二、如图4B所示,在上述临时载片101表面涂敷一层可释放涂层102,可释放涂层102可以是聚合物层、金属层或者聚合物层与金属层的叠加,且能够通过加热或者激光的方式实现解键合工艺;

步骤三、如图4C所示,将芯片Ⅰ103的背面通过粘接剂104倒装在可释放图层102的上表面,芯片Ⅰ103的正面有绝缘层Ⅰ105包覆,并通过凸块金属106进行电信连接;

步骤四、如图4D所示,采用塑封料Ⅰ108补充芯片封装体Ⅰ107的间隙,完全包覆芯片封装体Ⅰ107的金属凸块106,形成重构圆片,实现扇出型封装;

步骤五、如图4E所示,通过研磨工艺,露出被包覆的芯片封装体Ⅰ107的金属凸块106,塑封料Ⅰ108的高度与芯片封装体Ⅰ107的金属凸块106高度齐平;

步骤六、如图4F所示,在第一封装体124的表面通过多次依次涂胶、曝光和显影的方式形成再布线金属层110,再布线金属层110的底部设置金属焊盘Ⅰ113,金属焊盘Ⅰ113与塑封后芯片封装体Ⅰ107的上层金属凸块106进行电信号连接,再布线金属层110的金属焊盘包括金属焊盘Ⅴ128和金属焊盘Ⅵ129,金属焊盘Ⅴ128预留给互联金属柱115,金属焊盘Ⅵ129预留给芯片封装体Ⅱ116;

步骤七、如图4G所示,在再布线金属层110上方预留出芯片封装体Ⅱ116的区域114,在预留区域114的下方区域的再布线金属层110上表面设置金属焊盘Ⅵ129,再布线金属层110的上表面预设置金属焊盘Ⅴ128,用于连接互联金属柱115;在预留区域114外通过涂胶、曝光、显影和电镀的方式形成互联金属柱115,互联金属柱115分布在芯片封装体Ⅱ116的周围,其底部与再布线金属层110的金属焊盘Ⅴ128连接,互联金属柱115与再布线金属层110形成电信连接;

步骤八、如图4H所示,将芯片封装体Ⅱ116正装在再布线金属层110的预留区域114,芯片封装体Ⅱ116的单层金属层或者复合金属层和再布线金属层110的金属焊盘Ⅵ129加热或加压形成互联,芯片封装体Ⅰ107与芯片封装体Ⅱ116通过再布线金属层110形成超高密度信号互联;

步骤九、如图4I所示,采用塑封料Ⅱ117填充互联金属柱115的间隙,且完全包覆芯片封装体Ⅱ116和互联金属柱115;

步骤十、如图4J所示,通过研磨工艺,将塑封料Ⅱ117和互联金属柱115的高度减薄,露出金属互联柱115的上表面,且塑封料Ⅱ117依旧保持包覆芯片封装体Ⅱ116;

步骤十一、如图4K所示,在塑封料Ⅱ117的表面和互联金属柱115露出的表面通过多次依次涂胶、曝光、显影以及电镀的方式形成再布线金属层118,再布线金属层118包括金属层119和绝缘层120,金属层119和绝缘层120在纵向呈间隔分布,再布线金属层118的金属焊盘Ⅲ121和互联金属柱115电信号连接,再布线金属层118的上方设置金属焊盘Ⅳ122,用于回流形成球栅极阵列焊球;

步骤十二、如图4L所示,再布线金属层118的金属焊盘Ⅳ122上方依次通过涂胶、曝光、显影和电镀形成复合金属层,其包括铜层、镍层、锡层、银层和/或合金金属层等焊料,金属焊盘Ⅳ122通过回流形成球栅极阵列焊球123,将信号向下传导。球栅极阵列焊球还可以通过植球方式将锡球和再布线金属层118的金属焊盘Ⅳ122盘通过flux连接,在回流后形成球栅极阵列焊球123;

步骤十三、如图4M所示,通过激光或者加热的方式将可释放涂层102释放,将临时载片101和第一封装体124剥离,最终实现解键合的目的;

步骤十四、如图4N所示,保护层130通过粘接剂层104与芯片封装体Ⅰ107的背面固连,并延展至第一封装体124的整个表面,保护层130为树脂和金属的复合层,其功能包括:遮光、绝缘、导热、屏蔽、防止芯片氧化、隔绝水汽、防止芯片划伤、控制封装结构的厚度以及控制芯片之间的纵向连接距离的封装体保护层;

步骤十五、如图4O所示,将整张圆片通过切割划成复数颗单体,形成最终的单颗封装体。

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步地详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种多芯片三维堆叠扇出型封装结构及其封装方法

- 一种多芯片堆叠的三维扇出型封装结构及其封装方法