存储器控制器及快闪存储器的存取方法

文献发布时间:2023-06-19 11:35:49

技术领域

本发明有关于数据存取,特别是有关于一种存储器控制器及快闪存储器的存取方法。

背景技术

随着半导体技术的进步,低密度同位元检查(low-density parity check,LDPC)码在近年来已可用超大型积体(very-large-scale integration,VLSI)电路所实现,且广泛应用于数位通讯领域(例如包括无线通讯及光纤通讯)以及数据传输领域(例如用于数据储存装置,如固态硬碟)以做为错误更正码(error correction code,ECC)。

低密度同位元检查解码器是使用具有同位元(parity bit)的线性错误校正码来进行解码,其中同位元会提供用以验证接收到的码字(codeword)的同位元方程式给LDPC解码器。举例来说,低密度同位元查核码可为一具有固定长度的二进位码,其中所有的符元(symbol)相加会等于零。

在数据的编码过程中,所有的数据位元会被重复执行并且被传送至对应的编码器,其中每个编码器会产生一同位符元(parity symbol)。码字是由k个讯息位元(information digit)以及r个检查位元(check digit)所组成。若码字总共有n位元,则表示k=n-r。上述码字可用一同位元检查矩阵来表示,其中该同位元检查矩阵具有r列(表示方程式的数量)以及n行(表示位元数),如图1所示。这些码之所以被称为“低密度”是因为相较于同位元检查矩阵中位元0的数量而言,位元1的数量相对的少。在解码过程中,每次的同位元检查皆可视为一同位元查核码,并随后与其他同位元查核码一起进行交互检查(cross-check),其中解码会在检查节点(check node)进行,而交互检查会在变数节点(variable node)进行。

低密度同位元检查解码器支持三种模式:硬判定硬解码(hard decision harddecoding)、软判定硬解码(soft decision soft decoding),以及软判定软解码(softdecision hard decoding)。图1A为同位元检查矩阵H的示意图。图1B为坦纳图(TannerGraph)的示意图。如图1A所示,在同位元检查矩阵H的每一列可形成一检查节点,例如分别为检查节点C1、C2、C3及C4。在同位元检查矩阵H的每一行可形成一变数节点,例如分别为变数节点V1、V2、V3、V4、V5、V6及V7。

坦纳图为另一种表示码字的方式,并且可用于解释当使用一位元翻转(bitflipping)演算法时,低密度同位元检查解码器的一些关于硬判定软解码的操作。

如图1B所示,在坦纳图中,方形节点C1~C4所表示的检查节点代表同位元(paritybit)的数量,且圆形节点V1~V7所表示的变数节点(variable node)是为一码字中位元的数量。如果一特定方程式与码符元(code symbol)有关,则对应的检查节点与变数节点之间会以连线来表示。被估测的资讯会沿着这些连线来传递,并且于节点上以不同的方式组合。

当开始进行LDPC解码时,变数节点将发送一估测资讯(estimate)至所有连线上的检查节点,其中这些连线包含被认为是正确的位元。接着,每个检查节点会依据对所有其他的连接的估测(connected estimate)来针对每一变数节点进行新的估测,并且将新的估测资讯传回至变数节点。新的估测是基于:同位元检查方程式迫使所有的变数节点连接至一特定检查节点,以使总和为零。

这些变数节点会接收新的估测资讯以及使用一多数规则(majority rule)(亦即硬判定),来判断所传送的原始位元的数值是否正确。若判断原始位元的数值不正确,该原始位元会被翻转(flipped)。该翻转后的位元接着会被传回至该些检查节点,且上述步骤会被迭代地执行一预定次数,直到符合这些检查节点的同位元检查方程式。若有符合这些同位元检查方程式(亦即检查节点所计算的数值符合接收自变数节点的数值),则可启用提前终止(early termination),这会使得系统在最大迭代次数达到之前就结束解码程序。

该些同位元检查限制是由进行一征状检查(syndrome check)来实施。一个有效的码字将会符合方程式:H.C

传统的位元翻转LDPC解码器为了效能及低功耗的考量,常常限制每个码字位元的数据传递以一位元为限。意即,在每次迭代的过程中,每个码字位元仅交换符号位元(signbit)的资讯。在此限制下,若要增加解码器的解码效能,例如是吞吐量(throughput)或是校正率(correction rate)相当困难。

发明内容

因此,本发明是提出一种存储器控制器及快闪存储器的存取方法,其可让低密度同位元检查解码器中的变数节点单元可执行可设定(configurable)解码策略,并可增加解码效能、提高校正率、及/或降低功耗。

本发明是提供一种存储器控制器,用于一数据储存装置,存储器控制器包括:一变数节点单元及一检查节点单元。变数节点单元是用以取得从该数据储存装置的一快闪存储器所读取的一通道值。检查节点单元是用以由该变数节点单元取得一码字差值,并依据该码字差值计算一征状值(syndrome)。在每次LDPC解码迭代的期间,变数节点单元是执行:依据该通道值及来自该检查节点单元的该征状值以决定一征状权重(syndrome weight);取得一先前LDPC解码迭代所产生的一先前码字;依据该征状权重及一预定阈值以决定该先前码字的各码字位元的一位元翻转(bit-flipping)演算法的一翻转策略,并依据该翻转策略以翻动该先前码字中之一或多个码字位元以产生一更新码字;以及将该更新码字减去该先前码字以产生该码字差值。

在一些实施例中,当该通道值是由一硬决定(hard decision)方式从该快闪存储器读取而得时,该变数节点单元在初次LDPC解码迭代时是将该通道值设定为该先前码字,并且将该先前码字中的各码字位元相应的一可靠度资讯设定为1。选择性地,当该通道值是由一软决定(soft decision)方式从该快闪存储器读取而得,该通道值中的各位元是带有相应的一可靠度资讯。

在一些实施例中,该变数节点单元包括:一翻转决定单元及一位元翻转电路。翻转决定单元包括一翻转策略查找表用以记录不同数值的该征状权重及该预定阈值所对应的该翻转策略,其中该翻转策略包括强翻转(strong flip)策略、弱翻转(weak flip)策略及未动作策略。位元翻转电路是用以依据该翻转策略以翻动该先前码字中之一或多个码字位元以及各码字位元相应的可靠度资讯以产生该更新码字及该更新码字中的各码字位元相应的该可靠度资讯。此外,位元翻转电路更将该更新码字及该更新码字中的各码字位元相应的该可靠度资讯储存至一变数节点存储器以用于下一次LDPC解码迭代。

在一些实施例中,该先前位元中的各码字位元及其可靠度资讯的组合依序包括四个状态:强”1”(strong 1)、弱”1”(weak 1)、弱”0”(weak 0)及强”0”(strong 0),其中,该强翻转策略是指将该四个状态中的一特定状态往距离2个阶数或以上的状态进行翻转,且该弱翻转策略是指将该四个状态中的该特定状态往距离1个阶数或以上的状态进行翻转,且该未动作策略是指将该四个状态中的该特定状态维持不更动。此外,当该征状权重及该预定阈值均大于一预定值且该征状权重大于或等于该预定阈值时,该征状权重及该预定阈值所相应的该翻转策略为该强翻转策略。

本发明更提供一种快闪存储器的存取方法,应用于一数据储存装置中的一存储器控制器,该方法包括下列步骤:经由一储存程序将数据储存至该数据储存装置的一快闪存储器;取得从该数据储存装置的一快闪存储器所读取的一通道值;由该变数节点单元取得一码字差值,并依据该码字差值计算一征状值(syndrome);以及在每次LDPC解码迭代的期间,执行下列步骤:依据该通道值及来自该检查节点单元的该征状值以决定一征状权重(syndrome weight);取得一先前LDPC解码迭代所产生的一先前码字;依据该征状权重及一预定阈值以决定该先前码字的各码字位元的一位元翻转(bit-flipping)演算法的一翻转策略,并依据该翻转策略以翻动该先前码字中之一或多个码字位元以产生一更新码字;以及将该更新码字减去该先前码字以产生该码字差值。

本发明更提供一种存储器控制器,用于一数据储存装置中,存储器控制器包括:一变数节点单元及一检查节点单元。变数节点单元是用以取得从该数据储存装置的一快闪存储器所读取的一通道值。检查节点单元是用以由该变数节点单元取得一码字差值,并依据该码字差值计算一征状值(syndrome)。在每次LDPC解码迭代的期间,该变数节点单元是执行:依据来自该检查节点单元的该征状值以决定一征状权重(syndrome weight);取得一先前LDPC解码迭代所产生的一先前码字;依据该通道值及该先前码字以决定在该先前码字中的各码字位元是否已被翻转过;对于该先前码字中已被翻转过各码字位元及未被翻转过各码字位元,分别选择一第一翻转策略查找表及一第二翻转策略查找表,其中该第一翻转策略查找表不同于该第二翻转策略查找表;依据该征状权重、一预定阈值及所选择的该第一翻转策略查找表或该第二翻转策略查找表以决定该先前码字的各码字位元的一位元翻转(bit-flipping)演算法的一翻转策略,并依据该翻转策略以翻动该先前码字中之一或多个码字位元以产生一更新码字;以及将该更新码字减去该先前码字以产生该码字差值。

附图说明

图1A为同位元检查矩阵的示意图。

图1B为坦纳图(Tanner Graph)的示意图。

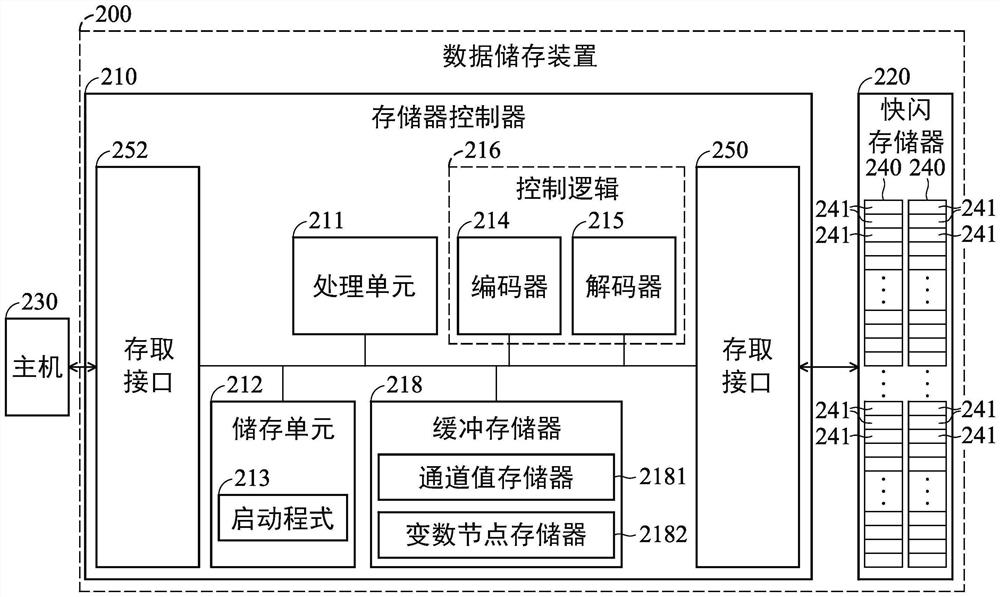

图2为依据本发明一实施例的数据储存装置的方块图。

图3为查核码检查矩阵及查核码产生矩阵的示意图。

图4为依据本发明一实施例中的解码器215的方块图。

图5为依据本发明的第一实施例中的变数节点单元的方块图。

图6A为依据本发明的第二实施例中的变数节点单元的方块图。

图6B为依据本发明的第二实施例中翻转策略的逻辑状态的示意图。

图7为依据本发明的第三实施例中的变数节点单元的方块图。

图8为依据本发明一实施例中的快闪存储器的存取方法的流程图。

符号说明

200~数据储存装置;

210~存储器控制器;

211~处理单元;

212~储存单元;

213~启动程式;

214~编码器;

215~解码器;

216~控制逻辑;

218~缓冲存储器;

2181~通道值存储器;

2182~变数节点存储器;

220~快闪存储器;

230~主机;

240~实体区块;

241~实体页面;

250、252~存取接口;

410~变数节点单元;

420~检查节点单元;

511、611、711~征状权重加总单元;

512、612、712~阈值计算单元;

513、613、713~翻转单元;

5131~比较器;

6131、7131~翻转决定单元;

5132、6132、7132~位元翻转电路;

601、701、702~翻转策略查找表;

S805-S840~步骤;

H~同位元检查矩阵;

c~列数;

t~行数;

M、K、P~矩阵;

K

syndrome~征状值;

CH_sgn~通道值;

ws~权重;

th~阈值;

Diff~码字差值;

VN_prev~先前码字;

VN_new~更新码字;

C1-C4~检查节点;

V1-V7~变数节点;

S1、S0、W1、W0~状态。

具体实施方式

以下说明是为完成发明的较佳实现方式,其目的在于描述本发明的基本精神,但并不用以限定本发明。实际的发明内容必须参考之后的权利要求范围。

必须了解的是,使用于本说明书中的"包含"、"包括"等词,是用以表示存在特定的技术特征、数值、方法步骤、作业处理、元件以及/或组件,但并不排除可加上更多的技术特征、数值、方法步骤、作业处理、元件、组件,或以上的任意组合。

于权利要求中使用如"第一"、"第二"、"第三"等词是用来修饰权利要求中的元件,并非用来表示之间具有优先权顺序,先行关系,或者是一个元件先于另一个元件,或者是执行方法步骤时的时间先后顺序,仅用来区别具有相同名字的元件。

图2为依据本发明一实施例的数据储存装置的方块图。

在一实施例中,数据储存装置200可以是可携式记忆装置(例如:符合SD/MMC、CF、MS、XD标准的记忆卡)或是固态硬碟(solid-state drive,SSD),且主机230为一可与数据储存装置200连接的电子装置,例如手机、笔记型电脑、桌上型电脑…等等。在另一实施例中,数据储存装置200可以设置在一电子装置中,例如设置在手机、笔记型电脑、桌上型电脑之中,而此时主装置130可以是该电子装置的一处理器。

如图2所示,数据储存装置200包括一存储器控制器210及一快闪存储器220,其中存储器控制器210是用以存取快闪存储器220。在一实施例中,存储器控制器210包括一处理单元211、一储存单元212、一控制逻辑216、一缓冲存储器218及存取接口250及252。处理单元211可由专用硬件电路或通用硬件所实现,具有多个处理核心的处理器或是具平行处理能力的多处理器,且上述实现方式例如可为通用处理器(General-Purpose Processor)、或微控制器(Microcontroller),但本发明并不限于此。

储存单元212可为非挥发性存储器,例如为唯读存储器(read-only memory,ROM)、可擦除式可程式化唯读存储器(erasable programmable read-only memory,EPROM)、电子可擦除式可程式化唯读存储器(electrically erasable programmable read-onlymemory,EEPROM)或电子熔丝(E-Fuse)。储存单元212是储存启动程式213,其包括启动码(Boot Code)或启动程式(Bootloader),且可由处理单元211执行,存储器控制器210基于启动程式213而完成开机,并开始控制该快闪存储器220的运作,例如,读取线上烧录(InSystem Programming,ISP)码。

快闪存储器220例如为NAND快闪存储器,且快闪存储器220包括多个实体区块(physical block)240,且各实体区块包括多个实体页面(physical page)241。

处理单元211与快闪存储器220间的数据与操作命令传递是透过数个电子信号进行协调,上述电子信号包括数据线(data line)、时脉讯号(clock signal)与控制讯号(control signal)。数据线可用以传递命令、位址、读出及写入的数据;控制讯号线可用以传递芯片致能(chip enable,CE)、位址提取致能(address latch enable,ALE)、命令提取致能(command latch enable,CLE)、写入致能(write enable,WE)等控制讯号。

存取接口250可采用双倍数据率(double data rate,DDR)通讯协定与快闪存储器220沟通,例如,开放NAND快闪(open NAND flash interface,ONFI)、双倍数据率开关(DDRToggle)或其他接口。处理单元211另可使用存取接口252透过指定通讯协定与主机230进行沟通,例如,通用序列汇流排(universal serial bus,USB)、先进技术附着(advancedtechnology attachment,ATA)、序列先进技术附着(serial advanced technologyattachment,SATA)、快速周边元件互联(peripheral component interconnect express,PCI-E)、非挥发性存储器的传输规范(Non-Volatile Memory Express,NVMe)或其他接口。

缓冲存储器218可为一挥发性存储器,例如包括一动态随机存取存储器(dynamicrandom access memory,DRAM)及/或一静态随机存取存储器(static random accessmemory,SRAM)。在此实施例,缓冲存储器218包括一通道值存储器(channel value memory,CHVMem)2181及变数节点存储器(variable node memory,VNMem)2182。通道值存储器2181是用以暂存来自存取接口250所读取的快闪存储器220的原始页面数据(或称为码字)、或是用以暂存来自主机230的主机指令。变数节点存储器2182是用以暂存在进行低密度同位元检查的解码过程中在各变数节点的变数节点数据。此外,通道值存储器2181所储存的码字例如可为硬判定或软判定的方式由快闪存储器220所读取的资讯,其中硬判定(harddecision)是采用单一读取电压阈值,故所得到的码字只有符号(sign)资讯。软判定(softdecision)则是利用多个读取电压阈值,故所得到的码字除了符号资讯之外,还带有可靠度资讯,例如每个码字位元可使用至少一位元的可靠度资讯来表示。若可靠度资讯用一位元表示,则可用0及1分别表示强(strong)及弱(weak)两种不同的可靠度,则码字位元搭配可靠度则可分为强”1”、弱”1”、弱”0”及强”0”。

控制逻辑216包括一编码器214及解码器215。在一些实施例中,编码器214、解码器215及控制逻辑216例如可由应用导向积体电路(application-specific integratedcircuit,ASIC)、现场可程式化逻辑闸阵列(field-programmable gate array,FPGA)、复杂可程式化逻辑装置(complex programmable logic device,CPLD)、或具有相同功能的逻辑电路所实现,但本发明并不限于此。

在此实施例中,编码器214例如为一低密度同位元查核码(LDPC)编码器,且可以根据来自主机230的数据来产生对应的查核码,且所产生的查核码符合一查核码检查矩阵。具体来说,参考图3,假设该查核码检查矩阵为一大小为c*t的矩阵(例如,列数c=5,行数t=48),而该查核码检查矩阵可以分为左侧的矩阵M(大小为c*(t-c))以及右侧的矩阵K(大小为c*c),为了找出与该查核码检查矩阵所对应的查核码产生矩阵,可以先找出矩阵K的反矩阵K

解码器215例如为低密度同位元查核码(LDPC)解码器。当主机230发送一读取指令至数据储存装置230,存储器控制器210是由快闪存储器220取得初始页面数据,例如又称为通道值。初始页面数据例如包括初始数据及错误校正码数据。因为初始数据及错误校正码数据在经过通道传输时可能产生错误,故解码器215可利用错误校正码数据以对初始数据及/或错误校正码数据本身进行错误校正,例如可采用一位元翻转(bit flipping)演算法进行LDPC解码。解码器215的细节将于下列实施例中详述。

图4为依据本发明一实施例中的解码器215的方块图。如图4所示,解码器215包括一变数节点单元(variable node unit,VNU)410及一检查节点单元(check node unit,CNU)420。在进行LDPC解码时,数据会在变数节点单元410及检查节点单元420之间进行迭代(iteration),直到解出正确的码字或是达到迭代次数上限为止。举例来说,当解码器215开始进行解码时,变数节点存储器2182中所暂存的先前码字的数值以及初始的征状值均被重置为0。变数节点单元410会由通道值存储器2181取得通道值或码字(例如可称为先前码字VN_prev),并进行第一次迭代的运算。变数节点单元410是将迭代运算所产生的位元翻转后的更新码字(VN_new)储存至变数节点存储器2182,并将上述更新码字与先前码字(VN_prev)的差值传送至检查节点单元420以进行征状(syndrome)值的相关运算。

若来自检查节点单元420的征状值不为0,则变数节点单元410会继续进行第二次或后续的迭代运算。举例来说,变数节点单元410会从变数节点存储器2182、检查节点单元420及通道值存储器2181分别取得先前码字VN_prev、征状值、以及通道值,并据以计算出在先前码字中的那些码字位元需要翻转。若来自检查节点单元420的征状值等于0,则变数节点单元410则会输出目前迭代过程所产生的更新码字以输出正确页面数据。因此,存储器控制器210中的处理单元211可将正确页面数据回报至主机230。

图5为依据本发明的第一实施例中的变数节点单元的方块图。请同时参考图4及图5,在第一实施例中,变数节点单元410例如包括一征状权重加总(syndrome weight sum)单元511、一阈值计算单元(threshold calculator)512及一翻转单元(flipping unit)513。

征状权重加总单元511是用以依据来自检查节点单元420所产生的征状值syndrome以及来自通道值存储器2181的通道值CH_sgn以产生每个码字位元相应的征状权重ws。

阈值计算单元512是用以计算当前解码过程所使用的一阈值(threshold)。在此实施例中,阈值计算单元512所产生用于解码过程的阈值例如可视实际解码的情况而改变。

翻转单元513是包括一比较器5131及一位元翻转电路5132。比较器5131是用以将每个码字位元的征状权重ws与上述阈值进行比较。位元翻转电路5132是依据上述比较结果决定相应的码字位元是否需要翻转,并将进行位元翻转后的更新码字VN_new储存至变数节点存储器2182。举例来说,若其中一个码字位元的征状权重ws大于或等于上述阈值th,则位元翻转电路5132会将上述码字位元进行翻转,例如从0翻转为1或是从1翻转为0。位元翻转电路5132并计算在此次迭代运算所取得的先前码字与上述更新码字的码字差值(codeworddifference)Diff,并将上述码字差值Diff传送至检查节点单元420。

其中,上述码字差值Diff的计算方式例如为VN_next-VN_prev。更新码字及先前码字均为二进位的数字表示,若更新码字VN_next为0111且先前码字VN_prev为0101,则码字差值Diff为0010。

图6A为依据本发明的第二实施例中的变数节点单元的方块图。请同时参考图4及图6A,在第二实施例中,变数节点单元410例如包括一征状权重加总(syndrome weightsum)单元611、一阈值计算单元(threshold calculator)612及一翻转单元(flip unit)613。征状权重加总单元611是用以依据来自检查节点单元420所产生的征状值syndrome以及来自通道值存储器2181的通道值CH_sgn以产生每个码字位元相应的征状权重ws。阈值计算单元612是用以计算当前解码过程所使用的一阈值(threshold)。在此实施例中,阈值计算单元612所产生用于解码过程的阈值例如为一固定值。

翻转单元613是包括一翻转决定单元6131及一位元翻转电路6132。翻转决定单元6131是用以依据当前每个码字位元的征状权重ws及上述阈值以决定翻转策略(flippingstrategy)。为了便于说明,翻转决定单元6131例如可由一翻转策略查找表601所实现,其中翻转策略查找表601可预先储存于储存单元212,且在数据储存装置200开机时,处理单元211可将翻转策略查找表601载入至缓冲存储器218或是一暂存器组(register file)。

在一实施例中,翻转策略查找表601可使用硬资讯搭配码字、或是软资讯搭配码字的方式进行查找。举例来说,对于一般正常的快闪存储器来说,其错误率约在1%以下,意即数据的正确率很高,故适合采用硬决定(hard decision)以读取页面数据。若在读取快闪存储器220的页面数据是使用硬决定时,则表示储存于通道值存储器2181中的通道值/码字不带有可靠度资讯。此时,翻转单元613例如在开始进行LDPC解码时,可将来自通道值存储器2181的各码字位元相应的可靠度资讯(例如可用1或多个位元表示)重置为1。随着解码过程中进行迭代运算,若可靠度资讯为1位元,则各码字位元的数值及相应的可靠度资讯可能会被切换为不同的数值,例如为强”1”、弱”1”、弱”0”及强”0”,其中强/弱表示可靠度资讯,且上述四种组合对应的(可靠度,码字位元)可分别表示为(1,1)、(0,1)、(0,0)及(1,0)、或是可分别表示为S1、W1、W0及S0。

在另一实施例中,图6的变数节点单元亦可接收利用软决定(soft decision,例如使用多个读取电压阈值以读取快闪存储器)所读取的页面数据,且来自通道值存储器2181的码字会带有软资讯,例如可为一或多个位元的可靠度资讯。此时,翻转单元613例如在开始进行LDPC解码时,可直接使用来自通道值存储器2181的各码字位元及相应的可靠度资讯。

在此实施例中,翻转策略查找表601利用征状权重ws及阈值th的查表结果可分为多种不同的位元翻转方式,例如为强翻转(strong flip)、弱翻转(weak flip)及不动作(donothing),其中征状权重ws及阈值th例如均为自然数。但本发明并不限于此。

举例来说,强翻转(strong flip)、弱翻转(weak flip)及未动作可分别用S、W及X表示。若查表结果表示为强翻转S时,则强”0”会被翻转为弱”1”,弱”0”会被翻转为强”1”,弱”1”会被翻转为强”0”,强”1”会被翻转为弱”0”。若查表结果表示为弱翻转S时,则强”0”会被翻转为弱”0”,弱”0”会被翻转为弱”1”,弱”1”会被翻转为弱”0”,强”1”会被翻转为弱”1”。若查表结果表示为未动作时,则强”1”、弱”1”、弱”0”及强”0”均会维持原本的数值。

强翻转、弱翻转及未动作的翻转方式整理如表1所示:

表1

需注意的是,本发明并不限定于表1中的翻转方式及数量,且本发明领域中具有通常知识者可视实际情况而设计适合的翻转方式及数量。值得说明的是,若将S1、W1、W0及S0视为依序排列的4个逻辑状态,且相邻的逻辑状态可视为阶数差1,如图6B所示。强翻转的方式表示上述状态进行翻转时会被翻转至距离两个阶数(step)或以上的状态,例如状态S1被翻转至状态W0、状态S0被翻转至状态W1,依此类推。弱翻转的方式表示上述状态进行翻转时会被翻转距离一个间隔的状态,例如状态S1被翻转至状态W1、状态S0被翻转至状态W0,依此类推。然而,无论是强翻转或弱翻转,状态S1、W1、W0及S0在进行翻转时会具有对称性,如表1所示。

在一实施例中,若征状权重ws及阈值th均为介于0~4的整数,翻转策略查找表601例如可用表2表示对应于不同征状权重ws及阈值th的翻转策略:

表2

举例来说,在翻转策略查找表601中,例如可针对提高吞吐量进行设计。当征状权重ws及阈值th的数值愈大时,表示在码字位元的错误机率较高,故会使用强翻转的方式。

在一些实施例中,翻转决定单元6131可包括多个翻转策略查找表,且不同的翻转策略查找表是对应至不同的解码目标并可进行最佳化设计,例如提高吞吐量(throughput)、提高校正率(correction rate)、或是降低功耗等等。当解码器215被设定为其中一个解码目标时,翻转决定单元6131即可从上述多个翻转策略查找表中选择相应于解码目标的翻转策略查找表。

举例来说,针对提高吞吐量的翻转策略查找表可以使用整体较积极的翻转策略并搭配较少的迭代次数。当解码器215在同样的硬件平行度之下,选择提高吞吐量的翻转策略查找表例如可增加一倍的硬解码(hard decoding)吞吐量。提高校正率的翻转策略查找表可以使用中性的翻转策略并搭配较高的迭代次数以期可对具有较多错误的码字进行错误校正,例如可在同样的校正率之下额外更正0.05%的原始位元错误率(raw bit errorrate,RBER)。降低功耗的翻转策略查找表可以使用较保守的翻转策略并搭配较少的迭代次数,故可在相同的硬件平行度之下降低解码器215的功耗。在一些实施例中,翻转决定单元6131中的部分翻转策略查找表可针对两个或以上的解码目标设计,例如可同时提高吞吐量及提高校正率,但本发明并不限于此。此外,相较于图5,使用图6中的变数节点单元的解码器可具有更佳的解码效能。

位元翻转电路6132是依据各码字位元的查表结果DR以决定相应的码字位元及其可靠度资讯R是否需要翻转,并将进行位元翻转后的更新码字VN_new及更新可靠度资讯R_new储存至变数节点存储器2182。位元翻转电路6132并计算在此次迭代运算所取得的先前码字与上述更新码字的码字差值(codeword difference)Diff,例如为VN_next-VN_prev,并将上述码字差值Diff传送至检查节点单元420。需注意的是,位元翻转电路6132是将码字差值传送至检查节点单元420,但位元翻转电路6132并未将更新可靠度资讯R_new传送至检查节点单元420,而是将更新可靠度资讯R_new储存至变数节点存储器2182以供下一次迭代运算使用。

图7为依据本发明的第三实施例中的变数节点单元的方块图。请同时参考图4及图7,在第三实施例中,变数节点单元410例如包括一征状权重加总(syndrome weight sum)单元711、一阈值计算单元(threshold calculator)712及一翻转单元(flip unit)613。在图7中的征状权重加总单元711与图6A中的征状权重加总单元611的计算方式不同,其中征状权重加总单元711是用以依据来自检查节点单元420所产生的征状值syndrome以产生每个码字位元相应的征状权重ws。阈值计算单元612是用以计算当前解码过程所使用的一阈值(threshold)。在此实施例中,阈值计算单元712所产生用于目前解码迭代过程的阈值例如为一固定值,但每次解码迭代过程的阈值并不一定相同。

翻转单元713是包括一翻转决定单元7131及一位元翻转电路7132。翻转决定单元7131是包括翻转策略查找表701及702,其中翻转策略查找表701及702分别具有不同的翻转策略。翻转策略查找表701及702可预先储存于储存单元212,且在数据储存装置200开机时,处理单元211可将翻转策略查找表701及702载入至缓冲存储器218或是一暂存器组(register file)。

翻转决定单元7131是依据来自通道值存储器2181的通道值CH_sgn以及来自变数节点存储器2182的先前码字VN_prev以决定要选择翻转策略查找表701及702的其中一者。当选定翻转策略查找表701及702的其中一者后,翻转决定单元7131即可依据当前每个码字位元的征状权重ws及上述阈值th以决定相应的翻转策略。

详细而言,通道值CH_sgn及先前码字VN_prev的长度相同,且均包括多个位元,其中通道值CH_sgn例如可视为原始码字。因为在目前迭代过程(例如迭代次数为N)的先前码字VN_prev是变数节点单元410在前次迭代(例如迭代次数为N-1)的运算中将前次迭代的先前码字VN_prev进行位元翻转后所产生的更新码字VN_new。因此,在目前迭代过程所取得的通道值CH_sgn及先前码字VN_prev可用于判断在原始码字中有那些码字位元是已经被翻转过的。

需注意的是,对于正常的快闪存储器220来说,其数据错误率约在1%以下,故在通道值CH_sgn的各个码字位元是正确位元的机率相对较高。因此,针对先前码字VN_prev中未被翻转过的码字位元,翻转决定单元7131会使用翻转策略查找表701并依据当前每个码字位元的征状权重ws及上述阈值th以决定相应的翻转策略,其中翻转策略查找表701如表3所示。针对先前码字VN_prev中已被翻转过的码字位元,翻转决定单元7131会使用翻转策略查找表702并依据当前每个码字位元的征状权重ws及上述阈值th以决定相应的翻转策略,其中翻转策略查找表702如表4所示。

表3

表4

在此实施例中,相较于翻转策略查找表701中所使用的翻转策略,在翻转策略查找表702中所使用的翻转策略更为保守,意即翻转策略查找表702中所使用的翻转策略整体的翻转阶数会比翻转策略查找表701整体的翻转阶数低。举例来说,对于数据错误率很低的正常快闪存储器220而言,若从快闪存储器220所读出的原始码字(即通道值)中的码字位元有错误的比例也很低。既然在此情况下,有部分码字位元仍然被变数节点单元410进行位元翻转,表示这些码字位元相应的征状权重ws可能偏高,且若再进行较积极(aggressive)的翻转策略,例如前述的强翻转方式,则会有较大的机率会将码字位元翻转为实际上为错误的码字位元。此时,翻转错误的码字位元仍然需要经过更多迭代次数才能进行更正,意即翻转错误受到的惩罚(penalty)也较高,故会对已翻转过的码字位元采取较保守的翻转策略,例如前述的弱翻转或未动作方式。

位元翻转电路7132是依据各码字位元的查表结果DR以决定相应的码字位元及其可靠度资讯R是否需要翻转,并将进行位元翻转后的更新码字VN_new及更新可靠度资讯R_new储存至变数节点存储器2182。位元翻转电路7132并计算在此次迭代运算所取得的先前码字与上述更新码字的码字差值(codeword difference)Diff,例如为VN_next-VN_prev,并将上述码字差值Diff传送至检查节点单元420。需注意的是,位元翻转电路7132是将码字差值传送至检查节点单元420,但位元翻转电路7132并未将更新可靠度资讯R_new传送至检查节点单元420,而是将更新可靠度资讯R_new储存至变数节点存储器2182以供下一次迭代运算使用。

在一些实施例中,图7中的征状权重加总单元711的功能是类似于图6中的征状权重加总单元611,其可依据来自检查节点单元420所产生的征状值syndrome以及来自通道值存储器2181的通道值CH_sgn以产生每个码字位元相应的征状权重ws。

此外,本发明图6及图7的实施例亦可以合并实施。举例来说,在图6中可针对解码器的不同的解码目标而选择不同的翻转策略查找表,例如提高吞吐量(throughput)、提高校正率(correction rate)、或是降低功耗等等。加入图7的实施例的设计后,在图6中的不同的翻转策略查找表均可再细分为针对未翻转过的码字位元的第一翻转策略查找表以及针对已翻转过的码字位元的第二翻转策略查找表。因此,上述实施方式可进一步增加解码器215的效能。

图8为依据本发明一实施例中的快闪存储器的存取方法的流程图。请同时参考图2及图8,快闪存储器的存取方法的流程如下所述。图8中的快闪存储器的存取方法例如在从快闪存储器读取数据时是使用策略基础式(strategy-based)位元翻转的LDPC解码方法。

在步骤S805,经由一储存程序将数据储存至数据储存装置200的快闪存储器220。举例来说,上述储存程序例如可将主机欲储存至数据储存装置200的数据经过编码流程(例如为LDPC编码),并将编码后的数据写入至快闪存储器220。

在步骤S810,变数节点单元410取得从数据储存装置200的一快闪存储器220所读取的一通道值。举例来说,从步骤S810开始为存储器控制器210从快闪存储器220读取数据所进行的解码流程,且解码流程是相对于上述编码流程。

在步骤S820,检查节点单元420由变数节点单元410取得一码字差值,并依据码字差值计算一征状值(syndrome)。

在步骤S830,在每一次LDPC解码迭代期间,变数节点单元410是执行步骤S832~S840。

在步骤S832,判断检查节点单元420所产生的征状值是否为0。若征状值为0,则结束此次解码流程。若征状值不为0,则继续执行步骤S834。

在步骤S834,依据通道值及来自检查节点单元420的征状值以决定一征状权重(syndrome weight)。其中,先前码字中的各码字位元均有相应的征状权重。

在步骤S836,取得一先前LDPC解码迭代所产生的一先前码字。举例来说,在前次迭代所产生的更新码字即为用于目前迭代中的先前码字。

在步骤S838,依据征状权重及一预定阈值以决定先前码字的各码字位元的一位元翻转演算法的一翻转策略,并依据翻转策略以翻动先前码字中之一或多个码字位元以产生一更新码字。举例来说,翻转决定单元6131包括一翻转策略查找表601用以记录不同数值的征状权重及预定阈值所对应的翻转策略,其中翻转策略包括强翻转(strong flip)策略、弱翻转(weak flip)策略及未动作策略,但本发明并不限于此。

在步骤S840,将更新码字减去先前码字以产生码字差值。需注意的是,在进行上述位元翻转的过程中,会连各码字位元的可靠度资讯一并考虑并依据翻转策略以进行位元翻转,但是位元翻转电路6132在将更新码字减去先前码字以产生码字差值后,只将码字差值传送至检查节点单元420,且更新码字中的各码字位元相应的可靠度资讯则会储存至变数节点存储器2182中。

综上所述,本发明是提供一种存储器控制器及快闪存储器的存取方法,其可让使用位元翻转(bit-flipper)的LDPC解码器中的变数节点单元可执行可设定的解码策略,例如可针对解码器的不同的解码目标进行设定,包括:提高吞吐量(throughput)、提高校正率(correction rate)、或是降低功耗等等。此外,本发明中的解码器的变数节点单元可针对已翻转过的码字位元及未翻转过的码字位元分别选择适合的翻转策略查找表,进而提高解码效能。

本发明虽以较佳实施例揭示如上,然其并非用以限定本发明的范围,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,当可做些许的更动与润饰,因此本发明的保护范围当由权利要求书界定为准。

- 存储器控制器及快闪存储器的存取方法

- 快闪存储器的存取方法及相关的存储器控制器与电子装置