机车信号主机软件系统

文献发布时间:2023-06-19 09:57:26

技术领域

本申请涉及机车信号控制领域,尤其涉及一种机车信号主机软件系统。

背景技术

列车按照地面信号显示行车时,由于风、雪、雨、雾等气候条件不良或隧道、弯道等地形条件的影响,司机往往不能在规定距离内确认地面信号显示,存在冒进的危险。尤其是在行车密度大、列车速度快及载重量大的区段,发生冒进可能性更大。机车信号车载设备通过采集轨道电路中的电信号进行译码处理后复示前方地面信号机的显示,改善司机的瞭望条件。

机车信号车载系统设备主要包括:机车信号双路接收线圈,机车信号主机及双面八显示机车信号机。机车信号主机软件系统在解码机车信号,控制信号机显示方面起到关键性作用。现有机车信号主机的软件系统在软件架构方面的复杂度高,安全性和可靠性不符合欧洲的SIL4标准。

因此,需要一种架构清晰、安全性和可靠性符合欧洲的SIL4标准的机车信号主机软件系统。

发明内容

为了解决上述技术问题或者至少部分地解决上述技术问题,本申请提供了一种机车信号主机板软件系统,解决了现有机车信号主机板软件系统架构复杂,安全性和可靠性低的问题。

所述机车信号主机板软件系统应用于二乘二取二结构的机车信号主机,所述机车信号主机包括主/备主机板,所述主/备主机板分别包括2个DSP芯片,所述软件系统包括4个相同解码系统,所述每一个解码系统部署在一个所述DSP芯片上,所述解码系统采用分层设计,各层之间采用接口进行通讯连接,所述解码系统包括:

驱动层,用于与所述DSP芯片的外接设备进行通讯;

中间层,与所述驱动层通讯连接,用于通讯协议处理;

业务层,与所述中间层通讯连接,用于机车信号解码、消息处理、状态监控及操作输出。

可选的,所述驱动层包括:

UART驱动组件,用于配置UART接口和使所述UART接口收发数据;

SPI驱动组件,用于配置SPI接口和使所述SPI接口收发数据;

McBSP驱动组件,用于配置McBSP接口和使所述McBSP接口收发数据;

GPIO驱动组件,用于配置GPIO接口和使所述GPIO接口收发数据;

定时器驱动组件,用于配置定时器模块,提供系统时间、定时器延时服务及定时器周期服务;

CPU驱动组件,用于配置PLL模块、PSC模块、、DDR2模块及EMIFA模块。

可选的,所述中间层包括:

串行通信组件,用于第一UART端口、第二UART端口的协议帧解析/封装以及第二UART端口的安全数据包校验/封装;

其中,所述第一UART端口与同一主机板中另一解码系统传输安全相关数据,所述第二UART端口与所述机车信号主机的记录板传输非安全相关数据。

可选的,所述中间层还包括:

模数数模转换组件,用于调用所述SPI驱动组件配置外接CODEC芯片和读取外接AD芯片采集的电源电压和工作温度,

还用于调用所述McBSP驱动组件读取所述CODEC芯片左声道中线圈采样数据,

还用于调用所述McBSP驱动组件向所述CODEC芯片的右声道输出标准波形数据,从所述CODEC芯片右声道中读取参考采样数据;

其中,所述线圈采样数据为所述CODEC芯片对机车信号模数转换后的数据,所述机车信号为从接收线圈获取的电信号,

所述参考采样数据为所述CODEC芯片对所述标准波形进行模数和数模转换后输出的数据,

所述电源电压是为所述DSP芯片供电的电源的电压,

所述工作温度为所述DSP芯片的外部工作环境温度。

可选的,所述中间层还包括:

输入输出管理组件,用于调用所述GPIO驱动组件输出并行信号、面板指示灯控制信号、动态电源控制信号、工作信号、线圈断线检查信号及收发切换信号,

还用于调用所述GPIO驱动组件读取外部输入条件、并行信号的状态、灯显继电器状态、主备用状态、动态电源状态及动态电源继电器状态;

其中,所述并行信号为输出到机车信号机的信号,包括灯显信号、速度等级编码信号、上下行表示信号、制式信号及绝缘节信号,

所述外部输入条件包括上下行开关状态、方式设置状态、主机板槽位信息、解码通道号,

所述并行信号的状态为输出隔离回检电路对所述并行信号进行隔离回检后输出的信号,

所述灯显继电器状态为继电器触点隔离回检电路对所述灯显继电器进行隔离回检后输出的信号,

所述动态电源状态为所述解码系统控制的动态电源的输出状态,

所述动态电源继电器状态为所述解码系统控制的动态电源继电器的状态,

所述动态电源控制信号为所述解码系统使用定时器周期服务输出的动态电源脉动信号,用于控制所述动态电源打开和关闭,

所述动态电源为机车信号机点灯电路供电的电源,

所述线圈断线检测信号为所述解码系统使用定时器周期服务向所述接收线圈输出的线圈测试脉动信号,用于检测所述接收线圈是否断线,

所述工作信号为触发所述机车信号主/备主机板切换的信号,

所述收发切换信号为控制所述第二UART端口接收/发送模式切换的信号。

可选的,所述业务层包括:

状态监控组件,用于检测所述DSP芯片外设硬件和所述解码软件是否正常工作;

信号解码组件,用于对所述线圈采样数据译码;

消息处理组件,用于根据同一主机板2个所述解码系统的译码结果进行二取二表决;

操作输出组件,用于输出所述信号信号解码组件的译码结果。

可选的,所述信号解码组件包括:

制式判别模块,用于根据所述线圈采样数据获取所述线圈采样数据的主瓣中心频率,并根据所述主瓣中心频率判别所述线圈采样数据的制式;

ZPW2000译码模块,用于对制式为ZPW2000的线圈采样数据译码;

国产移频译码模块,用于对制式为国产移频的线圈采样数据译码;

交流计数译码模块,用于对制式为交流计数的线圈采样数据译码;

载频锁定切换模块,用于根据所述ZPW2000译码模块的译码结果更新ZPW状态,所述ZPW状态是ZPW2000译码模块的的译码条件之一,

应变时间处理模块,用于控制所述ZPW2000译码模块、所述国产移频译码模块及交流计数译码模块在译码结果稳定后输出译码结果。

可选的,所述消息处理组件包括:

处理查询软件版本信息模块,用于查询所述信号主机记录板获取所述解码系统的软件版本信息;

处理查询故障信息模块,用于查询所述信号主机记录板获取所述解码系统的故障信息;

接收异步译码结果模块,用于接收同一主机板中另一解码系统的译码结果,并记录接收时间戳;

发送本机译码结果模块,用于向同一主机板中另一解码系统的发送本解码系统的译码结果;

二取二表决模块,用于表决同一主机板的两个解码系统的的软件版本信息及译码结果,若表决结果为一致,则输出所述解码系统的译码结果,若表决结果为不一致,则进入故障停机;

双通道同步模块,用于同一主机板的两个解码系统之间同步。

可选的,所述状态监控组件包括:

上电初始化模块,用于为所述解码系统的正常运行准备软件和硬件环境,包括所述DSP芯片外设初始化及所述解码系统的组件初始化;

上电自检模块,用于在上电初始化成功后执行一次上电自检项目,上电自检过程中检测出任何异常,直接进入故障停机,所述上电自检的检测项目包括:

CPU检测,用于进行指令集检测和寄存器检测,

RAM检测,用于对所述DSP芯片外DDR2 RAM进行检测,

ROM检测,对所述DSP芯片外NOR FLASH中的程序代码进行完整性检测,所述片外NOR FLASH用于存储所述解码系统,

接收线圈断线检测,用于通过向所述接收线圈发送所述线圈断线检测信号检测所述接收线圈是否断线,

工作时钟检测,用于检测PLL模块是否正常工作,

采样正确性检测,用于根据所述参考采样数据检测所述CODEC芯片的通道增益、参考电压、采样率的正确性,

电源电压检测,用于检测所述电源电压是否在第一预设范围内,

工作温度检测,用于检测所述工作温度是否在第二预设范围内,

上下行设置检测,用于检测所述上下行开关状态是否有效,

方式设置检测,用于检测所述方式设置状态是否有效,

上电主备用模块,用于上电时确定主用主机板和备用主机板;

周期自检模块,用于持续性执行周期自检项目,检测所述DSP芯片外设硬件和所述解码软件是否正常工作,所述周期自检包括上电自检检测项目,还包括:

继电器粘连检测,用于分别通过所述灯显继电器状态和所述动态电源继电器状态,检测所述灯显继电器和所述动态电源继电器是否正确动作,

输出反馈检测,用于通过比对所述并行信号的状态与所述并行信号是否一致,检测并行信号输出电路是否正常,

组件运行检测,用于通过读取所述业务层各组件的执行时间戳检测程序执行完整性和有序性,

动态电源检测,用于根据所述动态电源状态检测所述动态电源是否故障;

关闭输出模块,用于关闭所述动态电源控制信号、所述工作信号及所述并行输出信号的输出。

可选的,所述操作输出组件包括:

并行信号输出模块,根据所述消息处理组件的表决结果,调用所述输入输出管理组件输出所述并行信号;

面板指示灯控制模块,根据所述消息处理组件的表决结果,调用所述输入输出管理组件输出所述面板指示灯控制信号。

本发明提供了一种机车信号主机板软件系统,应用于二乘二取二结构的机车信号主机,所述软件系统包括4个相同解码系统,所述解码系统采用分层设计,各层之间采用接口进行通讯连接,所述解码系统包括:驱动层,用于与所述DSP芯片的外接设备进行通讯;中间层,与所述驱动层通讯连接,用于通讯协议处理;业务层,与所述中间层通讯连接,用于机车信号解码、消息处理、状态监控及操作输出。

附图说明

此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本申请的实施例,并与说明书一起用于解释本申请的原理。

为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

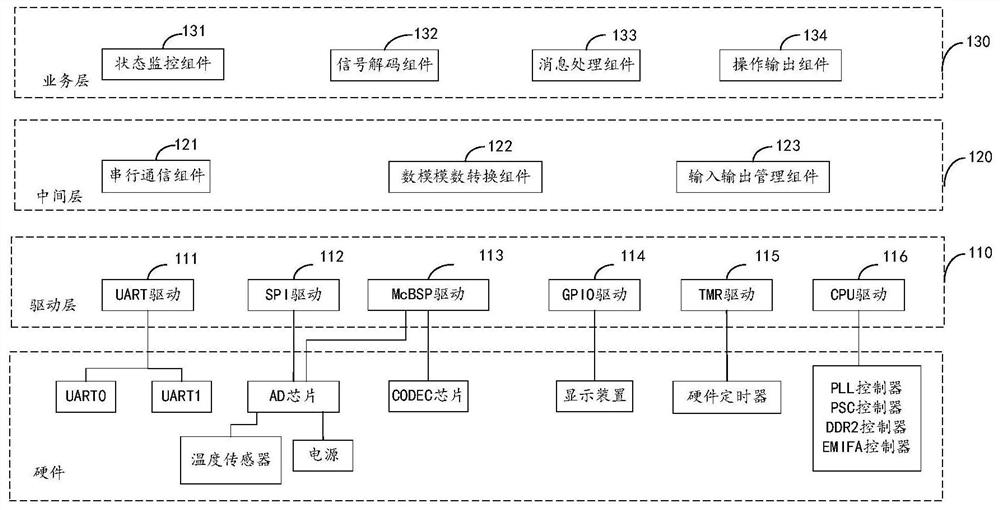

图1是根据一示例性实施例示出的一种解码系统框图;

图2是根据一示例性实施例示出的一种业务层组件执行流程图;

图3是根据一示例性实施例示出的一种信号解码组件的框图;

图4是根据一示例性实施例示出的一种信号解码组件的工作流程图;

图5是根据一示例性实施例示出的一种消息处理组件的框图;

图6是根据一示例性实施例示出的一种消息处理组件的工作流程图;

图7是根据一示例性实施例示出的一种状态监控组件的框图;

图8是根据一示例性实施例示出的一种状态监控组件的框图;

图9是根据一示例性实施例示出的一种操作输出组件的框图;

图10是根据一示例性实施例示出的一种操作输出组件的框图。

具体实施方式

为使本申请实施例的目的、技术方案和优点更加清楚,下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本申请的一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动的前提下所获得的所有其他实施例,都属于本申请保护的范围。

图1为一种解码系统框图,如图1所示,所述解码系统包括:驱动层110,用于与所述DSP芯片的外接设备进行通讯;

中间层120,与所述驱动层通讯连接,用于通讯协议处理;

业务层130,与所述中间层通讯连接,用于机车信号解码、消息处理、状态监控及操作输出。

本申请实施例中,所述驱动层110包括:

UART驱动组件111,用于配置UART接口和使所述UART接口收发数据,其中,所述UART接口包括第一UART端口及第二UART端口,所述第一UART端口与同一主机板中另一解码系统传输安全相关数据,所述第二UART端口与所述机车信号主机的记录板传输非安全相关数据;

SPI驱动组件112,用于配置SPI接口和使所述SPI接口收发数据,所述DSP芯片通过所述SPI接口与外接CODEC芯片和AD芯片连接,所述CODEC芯片与接收线圈连接,用于将所述接收线圈采集的数据数模转换后发送至所述DSP芯片,所述AD芯片分别与DSP芯片供电电源和温度传感器连接,用于采集DSP芯片电源电压和工作温度;

McBSP驱动组件113,用于配置McBSP接口和使所述McBSP接口收发数据,所述DSP芯片通过所述McBSP接口与所述CODEC芯片连接;

GPIO驱动组件114,用于配置GPI O接口和使所述GPIO接口收发数据,所述DSP芯片通过所述GPIO接口与机车信号机连接;

定时器驱动组件115,用于配置定时器模块,提供系统时间、定时器延时服务及定时器周期服务;

CPU驱动组件116,用于配置PLL模块、PSC模块、DDR2模块及EMI FA模块。

本申请实施例中,所述中间层120包括:串行通信组件121,用于所述第一UART端口、所述第二UART端口的协议帧解析/封装,通过外部输入的主机板槽位信息和解码通道号分配本机通信地址;

还用于所述第二UART端口的安全数据包校验/封装,当收发安全数据时,根据安全校验层子协议进行安全数据的校验和封装,包括序列号、时间戳、源标识、超时、反馈报文、双重校验等处理,对接收到的数据进行真实性、完整性、实时性、有序性等检查,避免安全数据受重复、丢失、插入、错序、错误、超时等危害。

本申请实施例中,所述中间层还包括:模数数模转换组件122,用于调用所述SP驱动组件配置所述CODEC芯片和读取所述AD芯片采集的所述电源电压和所述工作温度,

还用于调用所述McBSP驱动组件读取所述CODEC芯片左声道中线圈采样数据,

还用于调用所述McBSP驱动组件向所述CODEC芯片的右声道输出标准波形数据,并从所述CODEC芯片右声道中读取参考采样数据;

其中,所述线圈采样数据为所述CODEC芯片对机车信号模数转换后的数据,所述参考采样数据为所述CODEC芯片对所述标准波形进行模数和数模转换后输出的数据。

本申请实施例中,所述中间层120还包括:输入输出管理组件121,用于调用所述GPIO驱动组件114输出并行信号、面板指示灯控制信号、动态电源控制信号、工作信号、线圈断线检查信号及收发切换信号,

还用于调用所述GPIO驱动组件114读取外部输入条件、并行信号的状态、灯显继电器状态、主备用状态、动态电源状态及动态电源继电器状态;

其中,所述并行信号为输出到机车信号机的信号,包括灯显信号、速度等级编码信号、上下行表示信号、制式信号及绝缘节信号,

所述外部输入条件包括上下行开关状态、方式设置状态、所述主机板槽位信息、所述解码通道号,

所述并行信号的状态为输出隔离回检电路对所述并行信号进行隔离回检后输出的信号,

所述灯显继电器状态为继电器触点隔离回检电路对所述灯显继电器进行隔离回检后输出的信号,

所述动态电源状态为所述解码系统控制的动态电源的输出状态,

所述动态电源继电器状态为所述解码系统控制的动态电源继电器的状态,

所述动态电源控制信号为所述解码系统使用定时器周期服务输出的动态电源脉动信号,用于控制所述动态电源打开和关闭,

所述动态电源为机车信号机点灯电路供电的电源,

所述线圈断线检测信号为所述解码系统使用定时器周期服务向所述接收线圈输出的信号,用于检测所述接收线圈是否断线,

所述工作信号为触发所述机车信号主/备主机板切换的信号,

所述收发切换信号为控制所述第二UART端口接收/发送模式切换的信号。

本申请实施例中,所述业务层130包括:

状态监控组件131,用于检测所述DSP芯片外设硬件和所述解码软件是否正常工作;

信号解码组件132,用于对所述线圈采样数据译码;

消息处理组件133,用于根据同一主机板2个所述解码系统的译码结果进行二取二表决;

操作输出组件134,用于输出所述信号信号解码组件的译码结果。

图2为业务层组件执行流程图,如图2所示,

步骤210:执行状态监控组件;

步骤220:执行信号解码组件;

步骤230:执行消息处理组件;

步骤240:执行操作输出组件。

图3为信号解码组件的框图,如图3所示,包括:

制式判别模块3321,用于根据所述线圈采样数据获取所述线圈采样数据的主瓣中心频率,并根据所述主瓣中心频率判别所述线圈采样数据的制式;

ZPW2000译码模块3322,用于对制式为ZPW2000的线圈采样数据译码;

国产移频译码模块3323,用于对制式为国产移频的线圈采样数据译码;

交流计数译码模块3324,用于对制式为交流计数的线圈采样数据译码;

载频锁定切换模块3325,用于根据所述ZPW2000译码模块的译码结果更新ZPW状态,所述ZPW状态是ZPW2000译码模块的的译码条件之一;

应变时间处理模块3326,用于控制所述ZPW2000译码模块、所述国产移频译码模块及所述交流计数译码模块在译码结果稳定后输出译码结果。

由于实际信号干扰较大,在信号突变时可能出现多码交替造成译码出错,所以当机车信号变化时,需要等待信号译码结果稳定后再输出译码结果,这个等待时间总是希望足够长,以确保译码正确,但是又必须满足应变时间要求,所以需要进行应变时间处理,实质是译码结果稳定时间处理,由于信号译码只是对所选取的一段的信号进行分析处理,并没有时间属性,而信号又经过采样、传输、缓存、读取等多个步骤,而应变时间的规定是从模拟信号改变开始计算,本申请实施例中,额外处理来较为精确地确定信号改变的时间,再和译码结果的生成时间共同组成实际应变时间,当实际应变时间达到译码结果稳定时间后,才认为译码结果有效,输出译码结果。

图4为信号解码组件的工作流程图,如图4所示,流程包括:

步骤410:初始化模数数模转换组件;

步骤420:读取线圈采样数据;

步骤430:判别线圈采样数据的制式;

步骤440:根据线圈采样数据的制式选择译码模块进行译码,若所述线圈采样数据的制式为ZPW2000,则进行载频锁定切换;

步骤450:更新译码结果及运行时间戳;

其中,若各步骤执行有误,则进入故障停机。

图5为消息处理组件的框图,如图5所示,包括:

处理查询软件版本信息模块5331,用于通过所述第二UART端口查询所述信号主机记录板获取所述解码系统的软件版本信息;

处理查询故障信息模块5332,用于通过所述第二UART端口查询所述信号主机记录板获取所述解码系统的故障信息;

接收异步译码结果模块5333,用于第一UART端口接收同一主机板中另一解码系统的译码结果,并记录接收时间戳;

发送本机译码结果模块5334,用于第一UART端口向同一主机板中另一解码系统的发送本解码系统的译码结果;

二取二表决模块5335,用于从所述解码组件读取本机译码结果,从所述消息处理组件读取异步解码结果,如果这两个结果至少有一个超时,则判定为二取二表决故障;如果都没有超时,则进行比较,如果不完全一致,判定为二取二表决故障,进入故障停机;

本申请实施例中,二取二表决模块4335还采用容错机制,只有连续第一时长内判决不一致才报告表决故障,避免因双通道解码系统不完全同步或在信号突变时的误解码造成的不一致影响程序运行。本申请实施例根据实际信号持续时间长,解码系统运行周期短的特性,采用二取二表决机制和容错机制有效并且合理地检测出预期的解码不一致,也能规避偶发性解码不一致导致的误判;

双通道同步模块5336,用于同一主机板的两个解码系统之间同步。由于同一主机板的解码系统的输出信号需要共同驱动输出电路,如果输出不同步,可能造成输出信号异常闪烁等现象,因此本申请实施例采用同步机制。

图6为信号解码组件的工作流程图,如图6所示,包括:

步骤610:判断是否接收到来自所述第二UART端口的数据,若接收到,则进行步骤630,若未接收到,则跳转至步骤640;

步骤620:进行记录协议处理;

步骤630:判断是否接收到来自所述第一UART端口的数据,若接收到,则进行步骤640,若未接收到,则跳转至步骤650;

步骤640:进行解码同步协议处理;

步骤650:发送本机译码结果;

步骤660:进行二取二表决,若表决结果为一致,则进行步骤670,若不一致,则进入故障停机;

步骤670:同一主机板中两个解码系统同步;

步骤680:若同一主机板中两个解码系统同步正常,则进行步骤690,若同步超时,则进入故障停机;

步骤690:更新运行时间戳;

其中,所述记录协议处理包括查询所述信号主机记录板获取所述解码系统的软件版本信息和所述解码系统的故障信息,所述解码同步协议处理包括接收异步译码结果。

图7为状态监控组件的框图,如图7所示,包括:

上电初始化模块7341,用于为所述解码系统的正常运行准备软件和硬件环境,包括所述DSP芯片外设初始化及所述解码系统的组件初始化;

本申请实施例中,所述上电初始化模块7341是解码系统中最先被执行的模块,在本设计中,各层软件组件有清晰的上下层依赖关系,上层软件组件初始化时会同时初始化依赖的下层软件组件,驱动层软件组件初始化时会同时初始化自身管理的硬件资源,所以上电初始化是通过调用各业务层软件组件的初始化接口实现,当初始化过程中发生任何非预期的情况,各层软件组件会逐级反馈错误,上电初始化功能也会检测到初始化过程发生错误,然后直接关闭输出,进入故障停机。如果初始化过程顺利完成,将进入上电自检。

上电自检模块7342,用于在上电初始化成功后执行一次上电自检项目,上电自检过程中检测出任何异常,直接进入故障停机,所述上电自检的检测项目包括:

CPU检测,用于进行指令集检测和寄存器检测,

RAM检测,用于对所述DSP芯片外DDR2 RAM进行检测,本申请实施例中,所述解码系统不使用片内RAM,对RAM进行检测即是对片外DDR2 RAM进行检测,

ROM检测,对所述DSP芯片外NOR FLASH中的程序代码进行完整性检测,所述片外NOR FLASH用于存储所述解码系统,

接收线圈断线检测,用于通过向所述接收线圈发送第一频率的所述线圈断线检测信号,经过光耦隔离,再通过电容耦合到所述接收线圈,再经过隔离采样回检所述线圈断线检测信号,判断所述接收线圈断线是否断线,

工作时钟检测,用于检测PLL模块是否正常工作,

本申请实施例中使用TIM1作为系统时间计数器,通过检测系统时间是否准确即可反映工作时钟是否正常。硬件上使用了外部标准源产生的1Hz方波信号作为检测依据,软件上对该信号进行周期计时,如果计时结果不在0.8秒~1.2秒之间时,判定为工作时钟故障,

采样正确性检测,用于根据所述参考采样数据检测所述CODEC芯片的通道增益、参考电压、采样率的正确性,

本申请实施例中,通过向所述CODEC芯片发送标准波形数据,所述标准波形数据经过硬件回环再进入所述CODEC芯片右声道进行采集,所述解码系统对所述参考信号采样数据进行分析计算,若所述的参考信号采样数据的幅度或频率不满足预期,则判定为采样故障,

电源电压检测,用于检测所述电源电压是否在第一预设范围内,

所述DSP芯片的工作电压包括5V、3.3V、1.8V和1.2V,这些电压直接影响所述DSP的性能和是否正常工作,因此对这些电压进行检测是必要的,本申请实施例中,使用了扩展外接所述AD芯片采集这些电压,并通过SPI接口与所述DSP芯片相连,因此电源电压检测模块可通过SPI接口读取扩展AD芯片的电压采样结果并进行判断所述电源电压是否在第一预设范围内,

工作温度检测,用于检测所述工作温度是否在第二预设范围内,

本申请实施例中,所述工作温度由所述DSP芯片旁的温度传感器采集,所述温度传感器连接在AD芯片上,因此工作温度检测模块可通过SPI接口读取所述AD芯片的电压工作温度采样结果并进行判断所述工作温度是否在第二预设范围内,

上下行设置检测,用于检测所述上下行开关状态是否有效,

方式设置检测,用于检测所述方式设置状态是否有效,

本申请实施例中,方式设置是主机板内的固化设置,在硬件生产完成后就固定,系统运行过程中不会改变,如果检测到设置状态是无效状态,则判断为方式设置故障,

上电主备用模块7343,用于上电时确定主用主机板和备用主机板;

周期自检模块7344,用于持续性执行周期自检项目,检测所述DSP芯片外设硬件和所述解码软件是否正常工作,所述周期自检包括上电自检检测项目,还包括:

继电器粘连检测,用于分别通过所述灯显继电器状态和所述动态电源继电器状态,检测所述灯显继电器和所述动态电源继电器是否正确动作,

本申请实施例中,每个继电器都留有一组空节点作为检测点,通过比较操作输出组件中继电器驱动状态和输入输出管理组件中继电器状态是否一致判断继电器是否发生粘连故障,

本申请实施例中,设置所述继电器触点隔离回检电路的输出信号的采样间隔为第三时长,所述第三时长大于所述灯显继电器和所述动态电源继电器的一个周期内高电平输出时长,

输出反馈检测,用于通过比对所述并行信号的状态与所述并行信号是否一致,检测并行信号输出电路是否正常,

本申请实施例通过控制所述输出隔离回检电路的电源的通断实现输出反馈检测动态回检,通过比较所述并行信号输出状态和所述并行信号,当比较不一致时,判定为输出回检故障,

本申请实施例中,设置所述输出隔离回检电路的输出信号的采样间隔为第二时长,所述第二时长大于所述并行信号的一个周期内高电平时长,

组件运行检测,用于通过读取所述业务层各组件的执行时间戳检测程序执行完整性和有序性,

动态电源检测,用于根据所述动态电源状态检测所述动态电源是否故障;

关闭输出模块7345,用于关闭所述动态电源控制信号、所述工作信号及所述并行输出信号的输出,

本申请实施例中,关闭输出模块7345可以确保硬件逻辑的主备切换功能正常工作,一旦执行所述7345,表示本主机板处于故障状态,硬件进行主备切换操作。

图8为所述状态监控组件的工作流程图,如图8所示,包括:

步骤810:上电初始化;

步骤820:上电自检;

步骤830:确定主用主机板和备用主机板;

步骤840:周期自检;

步骤850:更新运行时间戳;

其中,若各步骤执行有误,则进入故障停机。

图9为所述操作输出组件的框图,如图9所示,包括:

并行信号输出模块9351,根据所述消息处理组件的表决结果,调用所述输入输出管理组件输出所述并行信号;

本申请实施例中,所述并行信号输出模块需要记录当前的信号输出状态,只有当信号输出状态需要改变时,才执行并行信号输出操作;执行并行信号输出操作时,适当延时并进行输出反馈检测,确保信号被成功输出。

面板指示灯控制模块9352,根据所述消息处理组件的表决结果,调用所述输入输出管理组件输出所述面板指示灯控制信号。

图10为所述操作输出组件的工作流程图,如图10所示,包括:

步骤1010:读取译码结果;

步骤1020:输出并行信号;

步骤1030:输出面板指示灯控制信号;

步骤1040:更新运行时间戳;

其中,若各步骤执行有误,则进入故障停机。

本申请实施例提供了一种机车信号主机板软件系统,应用于二乘二取二结构的机车信号主机,所述软件系统包括4个相同解码系统,所述解码系统采用分层设计,各层之间采用接口进行通讯连接,所述解码系统包括:驱动层,用于与所述DSP芯片的外接设备进行通讯;中间层,与所述驱动层通讯连接,用于通讯协议处理;业务层,与所述中间层通讯连接,用于机车信号解码、消息处理、状态监控及操作输出。本机车信号主机板软件系统采用检错码、故障检测等安全技术措施,采用二取二表决和输出反馈自检等避错和容错措施,解码系统的各功能组件软件安全完整性等级定义为SIL4。

需要说明的是,在本文中,诸如“第一”和“第二”等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

以上所述仅是本申请的具体实施方式,使本领域技术人员能够理解或实现本申请。对这些实施例的多种修改对本领域的技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本申请的精神或范围的情况下,在其它实施例中实现。因此,本申请将不会被限制于本文所示的这些实施例,而是要符合与本文所申请的原理和新颖特点相一致的最宽的范围。

- 机车信号主机软件系统

- 机车信号车载设备主机在线检测的工作系切换装置及方法