促进开关电源转换器的高侧控制

文献发布时间:2023-06-19 10:32:14

技术领域

本发明总体上涉及电源转换器,并且更具体地涉及促进开关电源转换器的高侧控制的方法、装置和系统。

背景技术

电源转换器为在各种装置中可用于将输入电压转换为期望的输出电压的电路。例如,降压转换器通过控制晶体管和/或开关以对电感器和/或电容器进行充电和/或放电以维持期望的输出电压,来将输入电压转换为较低的输出电压。一些电源转换器可以包括一个或多个电源开关,该电源开关可以同步地接通和/断开(例如,当一个开关接通时另一开关断开)以改变电源转换器中的电流路径。在一些示例中,诸如在高压电源转换器中,宽带隙器件可以用于实现用于高压和/或高温电源开关应用的电源开关。

发明内容

本文描述的示例促进开关电源转换器的高侧控制。示例装置包括:锁存器,其包括耦合到第一开关的第一源极的第一节点和耦合到第一开关的第一栅极的输出端;第一二极管,其耦合到第一节点和第二节点;第二二极管,其耦合到第二节点和接地;第二开关,其耦合到电压源和电阻器;以及第三开关,其包括耦合到电阻器和第二开关的第三栅极、耦合到第二节点的第三源极以及耦合到锁存器的第三漏极。

附图说明

图1示出了示例开关电源转换器。

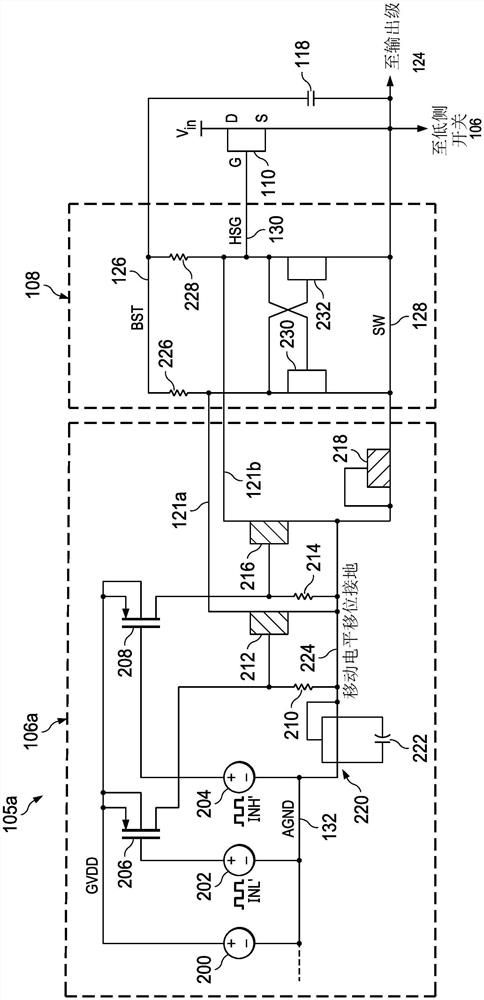

图2示出了图1的高侧电平移位器的示例电路实施方式。

图3示出了图1的高侧电平移位器的替代示例电路实施方式。

图4示出了对应于使用图2和/或3的高侧电平移位器的低侧到高侧转变的时序图。

图5示出了图1的替代示例高侧电平移位触发器。

图6示出了对应于使用图5的替代高侧电平移位触发器的低侧到高侧转变的时序图。

图7示出了图1的替代示例高侧电平移位器锁存器。

图8示出了对应于使用图8的替代高侧电平移位器锁存器的低侧到高侧转变的时序图。

图9示出了图1的示例键合焊盘。

图10为代表用以实现图1的电源转换器的可以被执行的示例机器可读指令和/或硬件配置的流程图。

图11为代表用以实现图1的电源转换器的可以被执行的示例机器可读指令和/或硬件配置的流程图。

图12为构造成执行图10-图11的机器可读指令以实现图1-图3、图5和/或图7的高侧电平移位器的处理器平台的框图。

具体实施方式

附图未按比例绘制。在任何可能情况下,在整个附图和该说明书中使用相同的附图标记来指代相同或相似的部件。

电源转换器(例如,降压转换器、升压转换器、交流(AC)-AC转换器、直流(DC)-DC转换器、AC-DC转换器等)可以在将电流从一个路径(例如,从电压源(Vdd)到输出端)切换到另一路径(例如,从输出端到接地)的半桥功率级中包括电源开关(例如,继电器、金属氧化物硅场效应晶体管(MOSFET)等)。在这种半桥开关转换器中,微控制器将控制信号输出到低侧电平移位器和/或高侧电平移位器。低侧电平移位器基于控制信号使低侧开关能够降低电源转换器的输出电压。高侧电平移位器使高侧电平移位器能够使高侧开关/晶体管增加电源转换器的输出电压。微控制器可以将(一个或多个)控制信号输出到电平移位器以在高侧控制(例如,通过启用高侧开关并禁用低侧开关)和低侧控制(例如,通过禁用高侧开关和启用低侧开关)之间以一频率和/或脉冲宽度调制切换以产生期望的输出电压。

电源转换器中的电平移位器将接收到的逻辑标准(例如,微控制器的3.3伏(V)或5V输出代表逻辑值“1”)下的数字控制信号转换为对应于足够高以控制高侧开关的电压的第二逻辑标准(例如,另一电压(例如400V)代表逻辑值“1”)。在某些半桥转换器中,高侧电平移位器包括一个或多个锁存器,该锁存器用于保持状态信息(例如,逻辑“1”或逻辑“0”),以触发足够高以启用高侧开关的输出电压或足够低以禁用高侧开关的输出电压。例如,当微控制器的输出对应于逻辑值“1”(例如3.3V或5V等)时,一个或多个锁存器向高侧开关的栅极输出电压,该电压升至自举(bootstrap)节点电位以启用高侧开关。在这样的示例中,当微控制器的输出对应于逻辑值“0”(例如0V或接地)时,一个或多个锁存器向高侧开关的栅极输出电压,高侧开关的栅极处的电压与开关节点处的电压相同,从而禁用低侧开关。自举节点对应于耦合到开关节点的自举电容器,自举电容器两端的电压对应于自举节点处的电压,该电压高于开关节点处的电压。开关节点对应于耦合到高侧开关的源极、低侧开关的漏极以及电源转换器的输出级的节点。

氮化镓(GaN)开关为宽带隙晶体管,该晶体管可以用于实现电源转换器的开关器件。GaN开关(例如,晶体管)具有非常高的击穿电压(例如,可以大于[最小击穿]V的反向偏置击穿电压)、高的电子迁移率和饱和速度。因此,GaN开关用于大功率和/或高频电源转换器或其他高压开关器件中。这样的系统具有寄生电感和寄生电容。GaN晶体管在硅层与晶体管的源极、栅极和漏极之间包含一层厚的高电阻GaN层。

一些宽带隙器件(诸如GaN晶体管)缺少固有的体二极管。因此,当在半桥开关转换器中实现GaN晶体管时,开关节点(例如,将半桥连接到输出级的节点)可能变为负。例如,当在低侧控制期间和/或死区时间期间(例如,低侧控制和高侧控制之间的持续时间,此时高侧晶体管和低侧晶体管均被禁用)从接地汲取的电流量足够高(例如,4安培(A)或更高),则随着电源转换器的电感器通过低侧晶体管/开关汲取负电流,开关节点处的电压可能会变为负。如果开关节点处的电压变得太负(例如,-4V、-5V等),则电平移位器将无法触发一个或多个锁存器。因此,电源转换器可能无法触发高侧控制。本文所述的示例包括提供移动电平移位接地的电路,当开关电压为负时,该移动电平移位接地跟踪开关节点处的电压,以比开关电压高预设电压。以这种方式,移动电平移位接地处的电压将总是足够低,以确保可以基于对应于移动电平移位接地的电压差来触发锁存器。当开关节点处的电压为正时,当开关电压为正时,移动电平移位接地处的电压跟踪接地,以比接地高预设电压。以这种方式,当开关电压为负时,电平移位器可以控制高侧开关。

而且,一些开关转换器包括键合线和/或键合焊盘以将电源转换器的部件耦合在一起。键合线和/或键合焊盘具有固有的寄生电容。这样的电容可以下拉或上拉电源转换器的一个或多个电平移位器中的和/或与其耦合的一个或多个节点(例如,将锁存器的节点上拉到自举节点以上和/或将锁存器的节点下拉到开关节点以下),从而在电平移位器中的节点处引起不期望的电压偏移。这种不期望的电压偏移可能导致电平移位器中的一个或多个锁存器在应该翻转状态信息时不翻转状态信息或在不应该翻转状态信息时翻转状态信息。此外,某些电源转换器可能具有器件不匹配。器件不匹配对应于电路中的器件之间的差异,理想情况下,这些器件应相同且具有相同的操作参数以准确地起作用。由于在高压反向偏置应力下电压阈值移动,因此基于GaN的电路中的不匹配可能高于基于硅的电路。本文所述的示例包括在电平移位器的锁存器中提供两个单独的迟滞路径的电路。迟滞路径向锁存器的一侧添加电阻,在高转换速率转变之后(例如,当电平移位器中的状态信息被校正和/或丢失时),该电阻将锁存器的内部节点拉至先前状态。以这种方式,由键合线、键合焊盘和/或器件的寄生电容(例如,晶体管的漏极-源极电容)引起的不期望的电压偏移将不会在(一个或多个)锁存器中引起不期望的状态信息翻转。

本文描述的一些示例将屏蔽应用于键合焊盘和/或键合线以降低寄生电容。例如,可以添加屏蔽,其中,可以使用二维电子气层(2-DEG)或与电平移位器处的开关节点相连的较低水平金属来屏蔽焊盘上的高电压。使用本文所述的此类示例,减小了寄生电容以降低寄生电容的影响。

图1示出了示例电源转换器100(例如,开关电源转换器),以将输入电压(Vin)转换为期望的输出电压。电源转换器100包括示例控制器102、示例输入缓冲器104、示例高侧电平移位器105a、105b(包括示例高侧电平移位触发器106a、106b和示例高侧电平移位器锁存器108)、示例高侧开关110、示例低侧电平移位器(包括示例低侧电平移位触发器112和示例低侧电平移位器锁存器114)、示例低侧开关116、示例二极管120、示例管芯间键合焊盘122、示例输出级124、示例自举节点126、示例开关节点128、示例高侧栅极节点130和示例接地节点132。在一些示例中,电源转换器100为用于实现输入缓冲器104、高侧电平移位器105b、高侧开关110、低侧电平移位触发器112、低侧开关116和/或二极管120的氮化镓(GaN)管芯。

图2的控制器102为输出对应于(一个或多个)逻辑值(例如,“1”或“0”)的(一个或多个)控制信号的控制器。例如,控制器102可以在输入高侧节点(INH)上输出第一逻辑值“1”,并且在输入低侧节点(INL)上输出第二逻辑值“0”以触发高侧控制(例如,通过启用开关110并禁用开关116以使输入电压对输出级124充电)。而且,控制器102可以在输入高侧节点(INH)上输出第二逻辑值“0”,并且在输入低侧节点(INL)上输出第一逻辑值“1”以触发低侧控制(例如,通过禁用开关110并启用开关116以使输出级124向接地放电)。在一些示例中,控制器102在高侧控制和低侧控制之间(例如,反之亦然)的短持续时间内在低侧节点和输入高侧节点两者处都输出第二逻辑值“0”以触发死区时间(例如,其中高侧开关110和低侧开关116均被禁用),以防止直通(例如,从Vin到接地的短路)。控制器102以一频率或脉冲宽度调制来切换在输入节点上输出的逻辑值,使得输出级124处的电压对应于期望的输出电压。控制器102经由输入节点将逻辑信号输出到输入缓冲器104以发起对开关110、116的控制。在控制器102的输出被高侧电平移位触发器106a、106b和/或低侧电平移位触发器112处理之前,输入缓冲器104存储控制器102的输出。

一旦图1的输入缓冲器104缓冲来自控制器102的控制信号,该控制信号就被传输到(高侧)HS电平移位触发器106a、106b和低侧电平移位触发器112以触发高侧控制或低侧控制。例如,如果输入高侧节点上的控制信号逻辑为高(例如,“1”)并且输入低侧节点上的控制信号逻辑为低(例如,“0”),则高电平移位触发器106a、106b触发高侧电平移位器锁存器108以在高侧栅极节点130处输出高逻辑值(例如,足够高以启用高侧开关110的电压)以启用高侧开关110,并且低侧电平移位触发器112触发低侧电平移位器锁存器114以在低侧开关116的栅极处输出低逻辑值(例如,足够低以禁用低侧开关116的电压)以禁用低侧开关116。另外,如果输入高侧节点上的控制信号逻辑为低并且输入低侧节点上的控制信号逻辑为高,则高侧电平移位触发器106a、106b触发高侧电平移位器锁存器108以在高侧栅极节点130处输出低逻辑值以禁用高侧开关110,并且低侧电平移位触发器112触发低侧电平移位器锁存器114以在低侧开关116的栅极处输出高逻辑值以启用低侧开关116。在死区时间期间(例如,此时控制器102在高侧输入和输入低侧上均输出低逻辑值以防止直通),高侧电平移位触发器106a、106b和低侧移位触发器112均触发相应的电平移位器锁存器108、114以在开关110、116的栅极处输出电压以禁用开关110、116。在一些示例中,电平移位器锁存器108、114可以包括两个锁存器。下面结合图7进一步描述两锁存器电平移位器实施方式的示例。

图1的开关110、116为晶体管(例如,高侧开关110为高侧晶体管,并且低侧开关116为低侧晶体管)。例如,如图1所示,开关110、116为氮化镓高电子迁移率晶体管(GaN HEMT)。然而,开关110、116可以为任何类型的开关(例如,场效应晶体管、金属氧化物场效应晶体管等)。当高侧开关110被启用并且低侧开关116被禁用时(例如,在高侧控制期间),输入电压被耦合到输出级124,从而使得对应于输出级124的输出电压朝着输入电压增加。当高侧开关110被禁用并且低侧开关116被启用时(例如,在低侧控制期间),输出级124接地,从而使对应于输出级124的输出电压降低。当两个开关110、116均被禁用时(例如,在死区时间期间),输出级124与开关116的源极处的接地连接以及开关110的漏极处的输入电压隔离,以防止输入电压短接到地。如上所述,控制器102在输入节点(例如,INH和INL)上在高逻辑值和低逻辑值之间切换,以预设的频率和/或脉冲宽度调制切换至输出级124的电流方向/来自输出级124的电流方向(例如,从输入电压到输出级124或从输出级124到接地)以实现期望的输出电压。在一些示例中,控制器102在从低侧控制切换到高侧控制和/或从高侧控制切换到低侧控制之前输出对应于死区时间的(一个或多个)控制信号,以防止直通。在一些示例中,诸如使用图3的HS电平移位触发器106b,可以在不引起高侧电平移位器锁存器108中的问题的情况下流过开关节点128的最大负载电流取决于Vt和Rdson。因此,最大负载电流(I_load)=0.6Vt/Rdson_LS,其中Vt为图3的开关300、302的阈值电压,并且Rdson_LS为低侧开关116在启用(例如,接通)时的漏极-源极电阻。基于以上公式,可以通过选择低侧开关116以具有低于高侧开关110的Rdson来增加最大电流。

图1的电容器118为自举电容器,该电容器将开关节点128处的电压自举到自举节点126处的较高电压。例如,自举电容器118通过存储对应于GVDD电压(例如,电压源/输入电压)的电荷来提供超过输入电压的功率的偏置电压。以这种方式,自举节点126处的电压比开关节点128处的电压高GVDD。例如,如果高侧开关110被启用并且输入电压为400V,则开关节点128处的电压约为400V。在这种示例中,如果由GVDD提供并存储在电容器118中的电压为6V,则自举节点126处的电压为406V。以这种方式,高侧电平移位器锁存器108可以在高侧栅极节点130处输出自举节点126处的电压以启用高侧开关110,或者可以在高侧栅极节点130处输出开关节点128处的电压以禁用高侧开关110。

图1的二极管120(例如,自举二极管)有助于对自举电容器118进行充电。例如,当开关节点128处的电压下降到低电压时(例如,在低侧控制期间),二极管120允许GVDD对自举电容器118充电。当开关节点128处的电压上升到高电压时(例如,在高侧控制期间),二极管120将GVDD与自举节点126隔离,从而在自举节点126处创建比开关节点高GVDD的电压。在图1所示的示例中,二极管120为GaN晶体管,其栅极耦合到其源极。因此,GaN晶体管像二极管一样操作,其中GaN晶体管的源极为二极管的阳极,并且GaN晶体管的漏极为二极管的阴极。可替代地,可以可替代地使用作为或充当二极管的任何类型的电路。

图1的键合焊盘122、123为连接电源转换器100中的部件的互连焊盘。在一些示例中,键合焊盘122、123连接到在不同管芯(例如,低侧管芯和高侧管芯)中实现的部件。例如,输入缓冲器104、HS电平移位触发器106a、106b、低侧电平移位触发器112、低侧电平移位器锁存器114、开关116和二极管120可以在低侧管芯中实现,而HS电平移位器锁存器108和开关110可以在高侧管芯中实现。在这样的示例中,连接的任何部件连接到在不同管芯中实现的部件需要一个或多个键合焊盘122、123以在不同管芯之间进行连接。键合焊盘122、123对应于一些寄生电容,这些寄生电容可以产生不期望的接地路径,这可以导致位移电流和/或可以导致HS电平移位器锁存器108中的两个开关的栅极被拉至高于自举节点126处的电压或被拉至低于开关节点128处的电压,这将导致锁存器不能锁存到状态(例如,高输出状态或低输出状态)。在一些示例中,相比于连接到键合焊盘122的器件的阻抗/电阻,某些键合焊盘122的寄生电容可以忽略不计。在一些示例中,由一些键合焊盘122的寄生电容引起的电荷量可能小。然而,施加到键合焊盘123的键合焊盘123电压摆幅大(例如,0V至400V)。因此,键合焊盘123的寄生电容可以向连接至键合焊盘的器件提供大量的不想要的电荷。如下面进一步描述的,结合图9,通过在键合焊盘122的背面上包括2-DEG层(其中接触件连接到2-DEG层),键合焊盘123减小了寄生电容的影响。接触件可以耦合到开关节点128以减小电源转换器100中的寄生电容的量。

在低侧到高侧转变期间和/或在低侧与高侧转变之间的死区时间期间,图1的开关节点128处的电压可以大程度地变为负(例如,-4.3V)。例如,在死区时间期间,由于两个开关110、116的栅极都接地,因此输出级124中的电感器将试图迫使电流从接地流到输出级124。因此,开关节点128处的电压大程度地变为负,以允许由电感器强制的电流流向输出级124。当开关节点128达到这样的负电压时,由于开关节点128处的负电压,一些高侧电平移位器可能无法基于INH信号触发器来翻转状态以触发高侧控制。然而,如下文进一步描述的,HS电平移位器105a、105b包括提供移动电平移位接地的电路,以允许电平移位器105a、105b即使在开关节点128大程度地为负时也能够启用高侧控制。

图2为图1的电平移位器105a的电路实施方式。图2的电平移位器105a包括图1的高侧电平移位触发器106a、高侧电平移位器锁存器108,自举节点126、开关节点128和接地节点132。图2的电平移位器105a进一步包括第一示例输入电压200(例如,代表图1的GVDD)和第二示例输入电压202(例如,代表来自图1的控制器102的输入低侧节点(INL)处的电压),以及第三示例输入电压204(例如,代表来自图1的控制器102的输入高侧节点(INH)处的电压)。图2的电平移位器105a进一步包括示例开关206、208、212、216、230、232、示例电阻器210、214、226、228、示例二极管218、220和示例电容器222。尽管图1的电平移位锁存器108用一个锁存器实现,但是电平移位锁存器108可以用任意数量的锁存器实现,如下面结合图7进一步描述的。

图2的输入电压200(例如,电压源)代表图1中施加的GVDD电压。输入电压200耦合到接地(例如,模拟接地节点132)。第一输入电压204代表由图1的控制器102在输入高侧节点(INH)上输出的控制信号,并且第二输入电压202代表由图1的控制器102在输入低侧节点(INL)上输出的控制信号。如上所述,在INH节点处的高逻辑值对应于启用HS开关110,并且在INL节点处的高逻辑值对应于禁用HS开关110。输入电压202、204耦合到接地(例如,模拟接地节点132)。

图2的开关206、208为晶体管,当被启用时(例如,基于来自施加到相应的开关206、208的栅极的相应的输入电压202、204的逻辑信号),这些晶体管允许电流经由相应的电阻器210、214从输入电压200流到接地,以在相应的开关212、216的栅极处创建电压。在图2中,开关206、208为p沟道金属氧化物半导体晶体管。可替代地,开关206、208可以为n沟道金属氧化物半导体晶体管(例如,具有连接调整以确保对应于高侧控制的逻辑信号启用高侧开关110)、GaN晶体管(例如,如下文结合图3进一步描述的)和/或任何其他类型的开关。

图2的开关212、216为晶体管,当被启用时,这些晶体管允许电流经由相应的电阻器226、228从自举节点126流到移动电平移位接地节点224。当将高于阈值电压的电压施加到相应的开关212、216的栅极时,启用开关212、216。如图2所示,开关212、216为GaN开关。可替代地,可以使用任何类型的开关。

图2的二极管218、220由GaN晶体管实现。可替代地,二极管218、220可以为实现二极管的功能的任何器件(例如,以允许电流在一个方向上流动并且防止电流在第二方向上流动)。例如,GaN实施方式的源极对应于二极管218的阳极(例如,耦合到移动电平移位接地节点224),并且GaN实施方式的漏极对应于二极管218的阴极(例如,耦合到开关节点128)。而且,GaN实施方式的源极对应于二极管220的阳极(例如,耦合到移动电平移位接地节点224),并且GaN实施方式的漏极对应于二极管220的阴极(例如,耦合到模拟接地节点132)。二极管218、220产生对应于阈值电压的电压降。二极管218允许电流从移动电平移位接地节点224流到开关(SW)节点128,并且防止电流从SW节点128流到移动电平移位接地节点224。而且,二极管220允许电流从移动电平移位接地节点224流到模拟接地(AGND)节点132。以这种方式,当SW节点128处的电压为正时,移动电平移位接地节点224与SW节点128隔离,并且移动电平移位接地节点224处的电压比AGND节点处的电压(例如,0V)高一个阈值电压(例如,2V)。而且,当SW节点128处的电压为负时,移动电平移位接地节点224与AGND节点132隔离,并且移动电平移位接地节点处的电压比SW节点128处的电压高一个阈值电压(例如,2V)。因此,二极管218、220被实现为产生移动电平移位接地节点224,当SW节点128处的电压为负时,该移动电平移位接地节点224跟踪SW节点128(例如,比SW节点128处的电压高一个阈值电压),并且当SW节点128处的电压为正时,该移动电平移位接地节点224跟踪AGND 132(例如,比AGND节点132处的电压高一个阈值电压/对应于从开关节点224到AGND 132的二极管220两端的电压差)。

当开关节点128处的电压上升到高电压时,图2的电容器222吸收阻塞二极管218的充电电流。以这种方式,电容器222将从AGND 132到移动电平移位接地节点224的电压降保持为低,直到电平移位动作完成为止(例如,在开关节点128处的电压稳定到高电压电平之后)。

图2的电阻器226、228提供了电流流到接地的路径(例如,基于开关212、216的启用),以在相应开关230、232的栅极处产生电压以存储状态信息(例如,高状态输出或低状态输出),该状态信息对应于在高侧栅极节点130上输出足够高以启用开关110的电压或足够低以禁用开关110的电压。在一些示例中,可以用p沟道晶体管和/或p沟道GaN晶体管代替电阻器226、228。

图2的开关230、232为基于施加到相应的开关230、232的栅极的电压而锁存到状态信息的晶体管。开关230、232被实现为使得当开关230接通时,开关232断开,并且当开关230断开时,开关232接通。当开关230断开并且开关232接通时,高侧栅极节点130处的电压(例如,锁存器输出)对应于低逻辑状态(例如,足够低以禁用开关110的电压)。当开关230接通并且开关232断开时,高侧栅极节点130处的电压对应于高逻辑状态(例如,足够高以启用开关110的电压)。

在操作中,当第一输入电压200为高并且第二输入电压202为低时(例如,对应于高侧控制),开关206被启用并且开关208被禁用。因此,输入电压200(例如,GVDD)被施加到电阻器210以在电阻器210两端创建电压降(例如,因为在低侧/死区时间控制期间,移动电平移位接地节点224处的电压为低或是负的)。该电压降对应于施加到开关212的栅极的电压,该电压足够高以启用开关212,从而经由电阻器226提供从自举节点126到接地的路径。因为在移动电平移位接地节点224处的电压跟踪SW节点电压,所以即使在自举节点126处的电压为0时,在移动电平移位接地节点224处的电压也将总是足够低以引起电阻器226两端的电压降,这对应于开关230、232的翻转。以此方式,施加到开关212的栅极的电压足够高以启用开关212(例如,翻转锁存器的状态)。因此,高侧栅极节点130处的电压与自举节点126处的电压(例如,足够高以启用开关110以进行高侧控制的电压)大致相同。

在不包括移动电平移位接地节点224的系统中(例如,没有二极管218、220的系统),AGND节点132用于触发锁存器。然而,这样的系统不能翻转锁存器,因为在死区时间期间,自举节点126处的电压可能非常小或为零。例如,如果在死区时间期间SW节点128处的电压为-6V,则自举节点126处的电压将为0V。由于AGND节点132的电压也为0V,因此电阻226、228中的任一者两端都不会有电压降。因此,这样的系统将不能翻转锁存器来启动高侧控制。然而,由于二极管218产生对应于移动电平移位接地节点224处的电压的电压降,该电压比SW节点128处的电压高阈值电压,因此移动电平移位接地节点224处的电压将是小于自举节点126处的电压的某个电压。例如,如果自举节点126处的电压为0V,则SW节点128处的电压为-6V,并且移动电平移位接地节点224处的电压为-4V。因此,电阻器226两端将仍然存在电压降(例如,0V至-4V),以促进在死区时间期间的开关230、232的状态切换(例如,翻转)。

图3为图1的电平移位器105b的替代电路实施方式。图3包括图1和/或图2的高侧电平移位触发器106b、高侧电平移位器锁存器108、自举节点126、开关节点128和接地节点132、第一示例输入电压200和第二示例输入电压202、第三示例输入电压204、开关212、216、230、232、电阻器210、214、226、228、二极管218、220和电容器222。图3进一步包括基于GaN的开关(例如,晶体管)300、302。

图3的GaN晶体管300以与图1的开关206、208基本上相似的方式操作。然而,因为GaN晶体管300被实现为n沟道GaN晶体管,所以输入电压202、204被翻转,使得INH输入处的电压对应于高侧控制,并且INL输入处的电压对应于低侧控制。可替代地,可以使用反相门/电路,并且输入电压202、204可以保持与图2中相同。然而,图3的电路的操作与图2基本上相似,其中启用GaN晶体管300对应于在高侧栅极节点130处输出高逻辑值(例如,用于低侧控制和/或死区时间),并且启用晶体管302对应于在高侧栅极节点130处输出低逻辑值(例如,用于高侧控制)。

图4为对应于图1的电源转换器100的低侧控制到高侧控制转变的示例时序图400。时序图400包括示例高侧输入电压402、示例栅极电压404(例如,对应于图2的开关212的栅极处的电压)、示例移动电平移位接地电压406以及示例开关节点电压408。图4的时序图400对应于电源转换器,该电源转换器的负载在死区时间期间汲取-4安培(A)。

在时间t0之前,电源转换器100在低侧控制中操作(例如,此时低侧开关116被启用并且高侧开关110被禁用,从而致使开关节点128处的电压朝着接地放电)。在时间t0之后,电源转换器100在死区时间(例如,此时低侧开关116被禁用且高侧开关110被禁用)操作以防止直通。如上所述,输出级124的电感器在死区时间期间从接地汲取电流。因此,在死区时间期间,开关节点电压408变为负(例如,-4.5V)。因为二极管218产生从移动电平移位接地节点224到开关节点128的电压降,所以移动电平移位接地电压406比开关节点电压408高一个二极管阈值电压(例如,-2.7V)。而且,在移动电平移位接地节点224处的电压为负时,由于电阻器210两端的电压差,栅极电压404同样变为负。在t1处,高侧输入电压增加以触发高侧控制。因此,开关206、300被启用以在电阻器210两端产生电压差,这对应于栅极电压404的增加。如上所述,基于栅极电压404启用开关212使电平移位器锁存器108通过禁用开关232并启用开关230以使开关节点电压408增加到足够高以启用高侧开关110的电压,来翻转输出状态。在时间t1处(例如,在高侧控制期间),移动电平移位接地电压406开始跟踪模拟接地(例如,AGND节点132)处的电压。

图5为图1的高侧电平移位触发器106a、106b的替代电路实施方式,其可被实现为用于在低侧控制期间将更大的电流量汲取到接地(例如,-4A至-6A或更高)。图5的高侧电平移位触发器106a、106b包括图1、图2和/或图3的开关节点128、开关212、216、300、302、二极管218、220、电容器222和移动电平移位接地节点224。图5的高侧电平移位触发器106a、106b进一步包括示例二极管500、504、506、508、510、514、516、518和电阻器502、512。

图5的高侧电平移位触发器106a、106b包括二极管500、504、506、508、510、514和电阻器502、512,以在对应于更负的开关节点电压128的低侧控制/死区时间期间,处理由图1的输出级124的电感器汲取的较大量的电流。例如,使用欧姆定律,图2或图3的电平移位触发器106a、106b可以处理的最大负载电流为0.6VT/Rdson_LS,其中VT为阈值电压,并且Rdson_LS为开关116的漏极-源极电阻。如上所述,增加最大负载电流的一种方法是使Rdson_LS低于Rdson_HS(例如,开关110的漏极-源极电阻)。可替代地,可以将第三二极管500、510添加到高侧电平移位触发器106a、106b,以调整对应于更高的最大负载电流的使用欧姆定律的公式。例如,对于第三二极管,I_load=0.9VT/Rdson_LS,其对应更高的负载电流。在一些示例中,可以将一个或多个电荷泵添加到开关300、302的栅极以注入足够的电流以在相应的电阻器210、214两端创建电压降以在开关212、216的栅极处产生足以启用开关212、216的电压。

图6为对应于使用图5的高侧电平移位触发器106a、106b的电源转换器100的低侧控制到高侧控制转变的示例时序图600。时序图600包括示例栅极电压602(例如,对应于图5的开关300的栅极处的电压)、示例漏极电压604(例如,对应于图5的二极管500的漏极处的电压)、示例栅极电压605(例如,对应于图5的开关212的栅极处的电压)、示例移动电平移位接地电压606和示例开关节点电压608。时序图600对应于死区时间期间负载电流达到-6A的情况。

最初,时序图600开始于电源转换器100以死区时间操作(例如,此时低侧开关116被禁用且高侧开关110被禁用)以防止直通。如上所述,输出级124的电感器在死区时间期间从接地汲取电流。因此,在死区时间期间,开关节点电压608变为负(例如,-6V)。因为二极管218产生从移动电平移位接地节点224到开关节点128的电压降,所以移动电平移位接地电压606比开关节点电压608高一个二极管阈值电压(例如,-4V)。而且,在移动电平移位接地节点224为负时,由于电阻器210两端的电压差,栅极电压605和漏极电压604同样变为负。在t1处,高侧输入电压增加以触发高侧控制。因此,开关206、300被启用以通过二极管500在电阻器210两端产生电压差,这对应于漏极电压604和栅极电压605的增加。如上所述,基于栅极电压605启用开关212使电平移位器锁存器108通过禁用开关232并启用开关230以使开关节点电压608增加到足够高以启用高侧开关110的电压,来翻转输出状态。在时间t1处(例如,在高侧控制期间),移动电平移位接地电压606开始跟踪模拟接地(例如,AGND节点132)处的电压。

图7示出了包括双向迟滞的图1的高侧电平移位器锁存器108的替代电路实施方式。图7的高侧电平移位器锁存器108包括示例第一迟滞电路700、示例开关701、703、708、710、示例电阻702、704、示例第二迟滞电路706、第一示例锁存器712、第二示例锁存器714、示例电路715、示例驱动器716、示例电路718,以及示例节点720、721、723、722、724、726、728、730、732、734。

在从低侧控制到高侧控制的转变的期间,由于键合焊盘123的寄生电容,位移电流可以流动。在一些示例中,位移电流可以使开关230、232两者的栅极处的电压被驱动到接地,从而导致高侧电平移位器锁存器108中的错误并且丢失所存储的状态信息。当发生这种错误时,第一迟滞电路700和第二迟滞电路706恢复高侧电平移位器锁存器108的先前状态。第一迟滞电路700根据先前存储的状态向电阻器226、228中的一个电阻器提供另一并联电阻(例如,并联的一个或多个电阻器),并且第二迟滞电路706根据先前存储的状态经由开关230、232中的一个开关提供朝向开关节点128的更强路径(例如,对先前为高的锁存器的一侧的较高的电阻和路径,以及对先前为低的锁存器的一侧的较低的电阻和路径)。以此方式,如果由于寄生电容而施加到开关230、232的栅极的电压都为零,则较强侧将沿正确方向上拉以维持所存储的状态信息(例如,锁存器维持其先前状态)。

图7的第一迟滞电路700包括开关701、703和电阻器702、704。当第一开关701被启用时(例如,基于轨-轨驱动器节点730的输出),电阻器702向电阻器226提供额外的电阻(例如,通过并联连接,从而降低了对自举节点126的总电阻),从而向自举节点126提供了更强的上拉路径。具有更强的路径对应于自举节点126处的电压更快地上拉,从而通过向开关232的栅极提供正确的电压来使锁存器返回到先前的状态。当第二开关703被启用时,电阻器704向电阻器228提供额外的电阻(例如,通过并联连接),从而通过电阻器228向自举节点126提供更强的上拉路径。

图7的第二迟滞电路706包括开关708、710,以向开关节点128提供强路径。例如,当启用第一开关708时,开关708在对应于电阻器226的锁存器的一侧上提供更强的接地路径,从而导致较慢地上拉至自举节点126处的电压,从而通过向开关232的栅极提供正确的电压而使锁存器返回到先前的状态。

图7的第一锁存器712对应于图2和图3中描述的锁存器。例如,第一锁存器712包括图2和图3的电阻器226、228和开关230、232。而且,锁存器712包括附加部件(例如,二极管钳位器、开关、电阻器、电容器等)以处理共模电流。例如,附加部件将不同节点处的电压钳位到自举速率电位或开关节点速率电位。

图7的第二锁存器714以与第一锁存器712基本相似的方式操作。第二锁存器714接收第一锁存器712的每一侧上的电压(例如,第一锁存器输出节点721、723处的电压),并且基于接收到的电压来调整状态以在第二锁存器输出节点724、726上产生第二锁存器输出逻辑信号。第二锁存器输出节点724、726上的电压耦合到轨-轨驱动器输出节点728、730、732、734,轨-轨驱动器输出节点728、730、732、734耦合到开关701、703、708、710的栅极。缓冲器输出节点730、728被设计为输出高于自举节点电位上的电压的电压,以有效地驱动n沟道器件。例如,轨-轨驱动器输出节点730、732耦合到开关701、708,并且轨-轨驱动器输出节点728、734耦合到开关703、710。以这种方式,迟滞电路700、706的开关701、703、708、710使用先前存储的状态信息以确保在第一锁存器712中引起错误的寄生电容(例如,通过基于附加的电阻/路径将第一锁存器712设置为先前存储的状态信息,两个节点720、722处的0V不会在第二锁存器714中引起错误)。

图7的电路715在启动期间强迫预定义电流状态。以这种方式,预定义状态信息将在启动时由第一锁存器712和第二锁存器714设置。电路716对应于轨-轨驱动器,该驱动器输出自举节点126处的电压或对应于高侧栅极节点130上第二锁存器714的(一个或多个)输出的开关节点128处的电压。电路716可以用于确保使用足够的电流以预定义速度驱动开关110的栅极。电路718提供欠压保护和启动钳位,以在加电期间定义锁存器的状态。

图8为对应于使用图7的高侧电平移位器锁存器108的电源转换器100的低侧控制到高侧控制转变的示例时序图800。时序图800包括第一示例控制电压802(例如,对应于图2和/或图3的开关212的漏极处的电压,其对应于第一侧上的第一锁存器712)、第二示例控制电压804(例如,对应于图2和/或图3的开关216的漏极处的电压,其对应于第二第一侧上的第一锁存器712)、对应于节点720处的电压的示例第一锁存器输出电压806、对应于节点722处的电压的示例第一锁存器输出电压808、对应于节点724处的电压的示例第二锁存器输出电压810、对应于节点726处的电压的示例第二锁存器输出电压812和对应于开关节点128的示例电压814。电压802-812相对于开关节点128处的电压814。例如,当电压810为6V时,它比开关节点128处的电压814高6V。

在时间t0之前,电源转换器100在低侧控制或死区时间中操作。在时间t0处,第一低侧控制电压802变低,并且第二低侧控制电压804变高,指示从低侧控制到高侧控制的转变。因此,在时间t0和t1之间,第一锁存器输出电压806和第二锁存器输出电压810下降到低电压,而第一锁存器输出电压808和第二锁存器输出电压812上升到高电压。在时间t1和t2之间,电源转换器100的部件上的寄生电容使控制电压802、804以及类似地使第一锁存器输出电压806、808下降到低电压。然而,迟滞电路700、706使电平移位器锁存器108维持其先前存储的状态(例如,对应于在时间t0和t1之间发生的高侧状态)。以这种方式,第二锁存器输出810、812维持其电压电平,并且开关节点电压814增加到高电压而没有对应于寄生电容的任何错误。

图9示出了图1的一个键合焊盘122的示例。键合焊盘包括示例键合焊盘连接端子900、示例2-DEG层902以及连接至开关节点128的示例接触件904。

如上所述,键合焊盘对应于寄生电容的量。寄生电容可以导致不期望的接地路径。因此,可以使用屏蔽来将由寄生电容引起的接地路径重定向到至SW节点128的路径,从而限制了对图7的节点720、722的寄生感应电流影响。

图9的键合焊盘123包括键合焊盘端子900,该键合焊盘端子900使用键合线将一个部件连接到另一部件。在键合焊盘端子900的背面上,键合焊盘123包括对应于一些电阻的2-DEG层902(例如2-DEG片)和连接至2-DEG层902的接触件904。2-DEG层902为导电层,这是实现屏蔽的方式。接触件904连接到SW节点128。以这种方式,与接地相反,寄生电容被连结到SW节点128。以这种方式,节点720、722上的寄生电流最小,并且减小了寄生电容的影响。

尽管在图2、图3、图5和图7中示出了实现图1的高侧电平移位器105a、105b的示例方式,但是在图2、图3、图5和图7中示出的一个或多个元件、过程和/或器件可以以任何其他方式来组合、划分、重新布置、省略、消除和/或实现。此外,HS电平移位触发器106a、106b、HS电平移位器锁存器108和/或更一般地图1-图3、图5和图7的高侧电平移位器105a、105b可以由硬件、软件、固件来实现和/或由硬件、软件和/或固件的任何组合来实现。因此,例如,HS电平移位触发器106a、106b、HS电平移位器锁存器108和/或更一般地图1-图3、图5和图7的高侧电平移位器105a、105b中的任一者都可以通过以下方式实现:一个或多个模拟或数字电路、逻辑电路、(一个或多个)可编程处理器、(一个或多个)可编程控制器、(一个或多个)图形处理单元(GPU)、(一个或多个)数字信号处理器(DSP)、(一个或多个)专用集成电路(ASIC)、(一个或多个)可编程逻辑器件(PLD)和/或(一个或多个)现场可编程逻辑器件(FPLD)。当阅读本专利的任何装置或系统权利要求以涵盖纯软件和/或固件实施方式时,HS电平移位触发器106a、106b、HS电平移位器锁存器108和/或更一般地图1-图3、图5和图7的高侧电平移位器105a、105b中的至少一者特此明确地定义为包括非暂时性计算机可读存储器件或存储磁盘,诸如存储器、数字多功能盘(DVD)、压缩盘(CD)、蓝光光盘等,其包括软件和/或固件。更进一步,图1的HS电平移位器105a、105b可以包括附加于或替代图1-图4、图5和图7中所示的那些的一个或多个元件、过程和/或器件,和/或可以包括一个以上的任何或所有所示的元件、过程和器件。如本文所用,短语“通信”(包括其变体)涵盖直接通信和/或通过一个或多个中间部件的间接通信,并且不需要直接的物理(例如,有线)通信和/或恒定的通信,而是另外包括以周期性间隔、计划间隔、非周期性间隔和/或一次性事件的选择性通信。

在图10和图11中示出了表示用于实现图1的电源转换器100的示例硬件逻辑、机器可读指令、硬件实现的状态机和/或其任何组合的流程图。机器可读指令可以为由计算机处理器(诸如,下面结合图12讨论的处理器平台1200中示出的处理器1212)执行的可执行程序或可执行程序的一部分。该程序可以体现在在存储在非暂时性计算机可读存储介质(诸如,CD-ROM、软盘、硬盘驱动器、DVD、蓝光盘或与处理器1212相关联的存储器)上的软件中,但是整个程序和/或其部分可以替代地由除处理器1212之外的器件执行和/或体现在固件或专用硬件中。此外,尽管参考图10-图11中所示的流程图描述了该程序,但是可以可替代地使用实现电源转换器100的许多其他方法。例如,可以改变框的执行顺序,和/或可以改变、消除或组合所描述的一些框。附加地或替代地,任何或所有框可以由被构造成在不执行软件或固件的情况下执行对应的操作的一个或多个硬件电路(例如,分立和/或集成模拟和/或数字电路、FPGA、ASIC、比较器、运算放大器(op-amp)、逻辑电路等)实现。

如上所述,图10-图11的过程可以使用存储在非暂时性计算机和/或机器可读介质(诸如硬盘驱动器、闪存、只读存储器、压缩盘、数字通用盘、高速缓存、随机存取存储器和/或存储信息达任何持续时间(例如,延长的时间段、永久地、用于短暂实例、用于暂时缓冲和/或用于信息的高速缓存)的任何其他存储器件或存储盘)上的可执行指令(例如,计算机和/或机器可读指令)来实现。如本文所用,术语“非暂时性计算机可读介质”明确地定义为包括任何类型的计算机可读存储器件和/或存储盘,并且排除传播信号并排除传输介质。

在本说明书中,术语“和/或”(当以诸如A、B和/或C的形式使用时)是指A、B、C的任何组合或子集,诸如:(a)仅A;(b)仅B;(c)仅C;(d)A与B;(e)A与C;(f)B与C;(g)A与B与C。而且,如本文所用,短语“A或B中的至少一者”(或“A和B中的至少一者”)是指包括以下任一者的实施方式:(a)至少一个A;(b)至少一个B;(c)至少一个A和至少一个B。

图10为代表可以由图1的电源转换器100执行以基于来自控制器102的控制信号来控制高侧开关110的示例机器可读指令和/或硬件配置的示例流程图1000。尽管结合图1的电源转换器100描述了图10的流程图1000,但是可以结合任何类型的开关电源转换器来描述流程图1000。

在框1002处,HS电平移位触发器106a、106b接收禁用高侧信号。例如,开关208可以在开关208的栅极处接收低逻辑值,并且开关206可以在开关206的栅极处接收高逻辑值(例如,对应于启用开关208并且禁用开关206)。在另一个示例中,图3的开关300可以在开关300的栅极处接收低逻辑值,并且开关302可以在开关302的栅极处接收高逻辑值(例如,对应于禁用开关300并且启用开关302)。在框1004处,电源转换器100禁用高侧开关110,如下面结合图11进一步描述的。在低侧控制期间,开关节点128处的电压达到零伏和/或负电压。因此,在低侧控制期间,自举电容器118基于GVDD和SW节点128之间的电压差(例如,经由二极管120)充电。如上面结合图1进一步描述的,由于自举电容器118在低侧控制期间被充电,因此自举节点126处的电压比自举电容器118在高侧控制期间的开关节点128高GVDD。

在框1005处,低侧电平移位器锁存器114通过向低侧开关116的栅极施加高电压来启用低侧开关116。在低侧电平移位器锁存器114启用低侧开关116之后,电源转换器100保持在低侧模式,直到从控制器102接收到高侧开关信号为止。在一些示例中,控制器102输出控制信号以在低侧/高侧转变之间的持续时间内禁用高侧开关110和低侧开关116两者以防止直通。在框1006处,HS电平移位触发器106a、106b确定是否已经接收到高侧开关信号。例如,当开关206的栅极处的电压为低逻辑值并且开关208的栅极处的电压为高逻辑值时,HS电平移位触发器106a、106b确定接收到高侧开关信号。在另一示例中,当开关300的栅极处的电压为高逻辑值并且开关302的栅极处的电压为低逻辑值时,HS电平移位触发器106a、106b确定接收到高侧开关信号。

如果HS电平移位触发器106a、106b确定未接收到高侧开关信号(框1006:否),则过程继续,保持高侧开关110禁用。如果HS电平移位触发器106a、106b确定接收到高侧开关信号(框1006:是),则LS电平移位触发器112和LS电平移位器锁存器114禁用低侧开关116(框1007)(例如,通过向低侧开关116的栅极施加低电压)。在框1008处,二极管218产生从移动电平移位接地节点224到开关节点128的电压降。例如,在从低到高切换或从死区时间到高侧切换期间,开关节点128处的电压可以为负。因此,二极管218产生电压降,使得移动电平移位节点接地224处的电压比开关节点128处的电压高一个阈值电压(例如0.7V、1.5V、2V等)。因为移动电平移位接地节点224可以为负的,由于开关节点128处的大程度的负电压,所以二极管220防止电流从移动电平移位接地节点224流到AGND节点132。因此,当开关节点128处的电压为负时,移动电平移位接地节点224处的电压跟踪开关节点128处的电压。

在框1010处,施加到开关206、300的栅极的电压启用开关206、300以经由第一电阻器210将电流从输入电压200(例如,GVDD)汲取到移动电平移位接地节点224,从而在第一电阻器210两端产生电压降。在框1012处,电阻器210两端的电压(例如,开关212的栅极处的电压)启用开关212。在框1014处,因为启用开关212产生了经由电阻器226从自举节点126到移动电平移位接地节点224的路径,所以电阻器226在开关232的栅极处产生低电压以禁用开关232。在框1016处,响应于启用开关212,高侧电平移位器锁存器108的锁存器触发高逻辑锁存器状态,因为没有经由电阻器228接地的路径,从而导致自举节点126处的电压(例如,足够高以启用开关110的电压)被输出到开关110的栅极以启用高侧控制。

在框1018处,HS电平移位触发器106a、106b确定是否已经接收到低侧开关信号。例如,HS电平移位触发器106a、106b确定当开关206的栅极处的电压为高并且开关208的栅极处的电压为低时或者如果开关300的栅极处的电压为低并且开关302的栅极处的电压为高,是否接收到低侧开关信号。如果HS电平移位触发器106a、106b确定尚未接收到低侧开关信号(框1018:否),则过程继续处于高侧控制。如果HS电平移位触发器106a、106b确定已经接收到低侧开关信号(框1018:是),则过程返回到框1004以禁用高侧开关110。

图11为代表可以由图1的电源转换器100执行以禁用高侧开关110的示例机器可读指令和/或硬件配置的示例流程图1004,如上面结合图10的框1004所述。尽管结合图1的电源转换器100描述了图11的流程图1004,但是可以结合任何类型的开关电源转换器来描述流程图1004。

在框1102处,二极管220产生从移动电平移位接地节点224到模拟接地(AGND)节点132的电压降。如以上结合图2所述,在高侧控制期间,开关节点128处的电压为正。因此,二极管218防止电流从开关节点128流到移动电平移位接地节点224。以这种方式,移动电平移位接地节点224处的电压跟踪AGND节点132处的0V的电压。因此,当SW节点128处的电压为正时,移动电平移位接地节点224处的电压比AGND节点132处的接地电压高一个阈值电压(例如,对应于二极管220的阈值电压)。

在框1104处,施加到开关208、302的栅极的电压启用开关208、302以经由电阻器214将电流从输入电压200汲取到移动电平移位接地节点224,从而在电阻器214两端产生电压降。在框1106处,电阻器214两端的电压(例如,开关216的栅极处的电压)启用开关216。在框1108处,因为启用开关216产生了经由电阻器228从自举节点126到移动电平移位接地节点224的路径,所以电阻器228在开关230的栅极处产生低电压以禁用开关230。在框1110处,高侧电平移位器锁存器108的锁存器响应于启用开关216而触发到低逻辑锁存器状态,因为高侧栅极节点130连结到开关节点128,从而使开关节点128处的电压(例如,对应于足够低以禁用开关110的电压)被输出到开关110的栅极以启用低侧控制。在框1110之后,过程返回到图10的框1006。

图12为示例处理器平台1200的框图,该处理器平台1200被构造为执行图10-图11的指令以实现图图1-图3、图5和/或图7的HS电平移位器105a、105b和/或控制器102。处理器平台1200可以为例如服务器、自学习机(例如,神经网络)、互联网器具、微控制器或任何其他类型的计算器件。

所示示例的处理器平台1200包括处理器1212。所示示例的处理器1212为硬件。例如,处理器1212可以由来自任何期望的系列或制造商的一个或多个集成电路、逻辑电路、微处理器、GPU、DSP或控制器实现。硬件处理器可以为基于半导体的(例如,基于硅的)器件。在该示例中,处理器实现高侧电平移位触发器106a、106b和/或HS电平移位器锁存器108。

所示示例的处理器1212包括本地存储器1213(例如,高速缓存)。所示示例的处理器1212经由总线1218与包括易失性存储器1214和非易失性存储器1216的主存储器通信。易失性存储器1214可以由同步动态随机存取存储器(SDRAM)、动态随机存取存储器(DRAM)、

所示示例的处理器平台1200还包括接口电路1220。接口电路1220可以通过任何类型的接口标准来实现,诸如以太网接口、通用串行总线(USB)、

在所示示例中,一个或多个输入器件1222连接到接口电路1220。(一个或多个)输入器件1222允许用户将数据和/或命令输入到处理器1212中。(一个或多个)输入器件可以由例如传感器、麦克风、相机(静态或视频)、键盘或按钮来实现。

一个或多个输出器件1224还连接到所示示例的接口电路1220。输出器件1224可以例如由显示器件(例如,发光二极管(LED)、有机发光二极管(OLED)、液晶显示器(LCD)、阴极射线管显示器(CRT)、原位切换(IPS)显示器、触摸屏等)、触觉输出器件和/或扬声器实现。因此,所示示例的接口电路1220通常包括图形驱动卡、图形驱动芯片和/或图形驱动处理器。

所示示例的接口电路1220还包括通信器件,诸如发射器、接收器、收发器、调制解调器、住宅网关、无线接入点和/或网络接口,以促进经由网络1226与外部机器(例如,任何种类的计算器件)的数据交换。该通信可以经由例如以太网连接、数字用户线(DSL)连接、电话线连接、同轴缆线系统、卫星系统、直线对传式(line-of-site)无线系统、蜂窝电话系统等。

所示示例的处理器平台1200还包括用于存储软件和/或数据的一个或多个大容量存储器件1228。这种大容量存储器件1228的示例包括软盘驱动器、硬盘驱动器、压缩盘驱动器、蓝光盘驱动器、独立磁盘冗余阵列(RAID)系统和数字通用盘(DVD)驱动器。

图10-图11的机器可执行指令1232可以被存储在大容量存储器件1228中,存储在易失性存储器1214中,存储在非易失性存储器1216中,和/或存储在可移除非暂时性计算机可读存储介质(诸如CD或DVD)上。

示例1包括一种装置,该装置包括:锁存器,其包括耦合到第一开关的第一源极的第一节点和耦合到第一开关的第一栅极的输出端;第一二极管,其耦合到第一节点和第二节点;第二二极管,其耦合到第二节点和接地;第二开关,其耦合到电压源和第二节点;以及第三开关,其包括耦合到第二开关的第三栅极、耦合到第二节点的第三源极以及耦合到锁存器的第三漏极。

示例2包括示例1所述的装置,其中电压源耦合到接地。

示例3包括示例1所述的装置,其中第一开关为耦合到电源转换器的输出级的高侧开关。

示例4包括示例3所述的装置,进一步包括耦合到电源转换器的输出级的低侧开关,该低侧开关包括比高侧开关的第二漏极-源极电阻低的第一漏极-源极电阻。

示例5包括示例1所述的装置,进一步包括:第四开关,其耦合到电压源;以及第五开关,其包括耦合到第四开关的第五栅极、耦合到第二节点的第五源极以及耦合到锁存器的第五漏极。

示例6包括示例5所述的装置,其中第二开关经由第一电阻器耦合到第二节点,并且第五开关经由第二电阻器耦合到第二节点。

示例7包括示例1所述的装置,其中第一二极管包括第一阳极和第一阴极,其中第一阳极耦合到第二节点并且第一阴极耦合到第一节点。

示例8包括示例7所述的装置,其中第二二极管包括第二阳极和第二阴极,其中第二阳极耦合到第二节点并且第二阴极耦合到接地。

示例9包括示例1所述的装置,进一步包括用以将第二开关耦合到锁存器的键合焊盘,该键合焊盘包括耦合到接触件的二维电子气层,该接触件耦合到第一节点。

示例10包括示例9所述的装置,其中二维电子气层和耦合到第一节点的接触件减小了寄生电容。

示例11包括一种装置,该装置包括:锁存器,其基于锁存器的第一状态或第二状态将对应于第一节点的第一电压或对应于第二节点的第二电压输出到电源转换器的晶体管,第二节点耦合到晶体管的源极;第一二极管,当对应于第二节点的第二电压为负时,第一二极管创建从第三节点到第二节点的第一电压降,并且当对应于第二节点的第二电压为正时,第一二极管防止第一电流从第二节点流到第三节点;以及第二二极管,当第三节点处的第三电压为正时,第二二极管创建从第三节点到接地的第二电压降,并且当第三节点处的第三电压为负时,第二二极管防止第二电流从接地流到第三节点。

示例12包括示例11所述的装置,进一步包括:第一晶体管,其基于第一控制信号,允许第三电流通过第一电阻器从电压源流到第三节点;以及第二晶体管,其在第一晶体管允许第三电流流过第一电阻器时启用,该第二晶体管的启用产生从锁存器的第一节点到第三节点的第一路径,锁存器响应于第二晶体管的启用而触发锁存器的第一状态。

示例13包括示例12所述的装置,进一步包括:第三晶体管,其基于第二控制信号,允许第四电流通过第二电阻器从电压源流到第三节点;以及第四晶体管,其在第三晶体管允许第四电流流过第二电阻器时启用,该第四晶体管的启用产生从锁存器的第一节点到第三节点的第二路径,锁存器响应于第四晶体管的启用而触发锁存器的第二状态。

示例14包括示例11所述的装置,其中晶体管为包括第一漏极-源极电阻的高侧晶体管,该装置进一步包括低侧晶体管,该低侧晶体管包括比第一漏极-源极电阻低的第二漏极-源极电阻。

示例15包括示例11所述的装置,进一步包括迟滞电路,该迟滞电路基于锁存器的先前状态向锁存器的第一侧或锁存器的第二侧添加电阻。

示例16包括示例15所述的装置,其中迟滞电路用于添加电阻以防止由寄生电容引起的锁存器的错误。

示例17包括示例11所述的装置,其中当第二电压为负时,第三节点处的第三电压对应于第二节点处的第二电压,并且当第二电压为正时,第三节点处的第三电压对应于第三节点与接地之间的电压差。

示例18包括示例11所述的装置,进一步包括用以将第一二极管耦合到锁存器的键合焊盘,该键合焊盘包括耦合到第二节点以减小寄生电容的二维电子气层。

示例19包括一种方法,该方法包括:在锁存器处,基于控制信号将对应于第一节点的第一电压或对应于第二节点的第二电压输出到电源转换器的高侧晶体管,第二节点耦合到高侧晶体管的源极;当对应于第二节点的第二电压为负时,产生从第三节点到第二节点的第一电压降,并且当对应于第二节点的第二电压为正时,防止第一电流从第二节点流到第三节点;当第三节点处的第三电压为正时,产生从第三节点到接地的第二电压降,并且当第三节点处的第三电压为负时,防止第二电流从接地流到第三节点。

示例20包括示例19所述的方法,进一步包括基于锁存器的先前状态向锁存器的第一侧或锁存器的第二侧添加电阻,以添加电阻从而防止由寄生电容引起的锁存器的错误。

示例21包括示例19所述的方法,其中当第二电压为负时,第三节点处的第三电压对应于第二节点处的第二电压,并且当第二电压为正时,第三节点处的第三电压对应于第三节点与接地之间的电压差。根据前述内容,应当理解,已经描述了促进开关电源转换器的高侧控制的示例方法、装置和制品。所描述的方法、装置和制品即使在电源转换器的开关节点为负的情况下,也通过促进低侧控制到高侧控制转变来改善使用电源转换器的效率。所描述的方法、装置和制品相应地针对电源转换器的功能的一种或多种改进。

在权利要求的范围内,在所描述的实施例中可以进行修改,并且其他实施例也是可能的。

- 促进开关电源转换器的高侧控制

- 高侧晶体管的驱动电路、开关电路、DC/DC转换器的控制器