基于存储器的处理器

文献发布时间:2023-06-19 11:14:36

相关申请的交叉引用

本申请案要求于2018年9月6日申请的第61/727,653号美国临时专利申请的优先权,该申请通过引用的方式并入本文中。

技术领域

本公开大体上关于用于促进存储器密集型操作的装置。具体而言,本公开关于包括耦接至专用存储器组的处理元件的硬件芯片。本公开还关于用于改良存储器芯片的功率效率及速度的装置。具体而言,本公开关于用于在存储器芯片上实施部分刷新或甚至无刷新的系统及方法。本公开还关于大小可选择的存储器芯片及存储器芯片上的双端口能力。

背景技术

随着处理器速度及存储器大小均继续增大,对有效处理速度的显着限制为冯诺依曼(von Neumann)瓶颈。冯诺依曼瓶颈由常规计算机架构所导致的吞吐量限制造成。具体而言,相较于由处理器进行的实际计算,自存储器至处理器的数据传送常会遇到瓶颈。因此,用以对存储器进行读取及写入的时钟循环的数量随着存储器密集型处理程序而显着增大。这些时钟循环导致较低的有效处理速度,这是因为对存储器进行读取及写入会消耗时钟循环,该时钟循环无法用于对数据执行操作。此外,处理器的计算带宽通常大于处理器用以存取存储器的总线的带宽。

这些瓶颈对于以下各项特别明显:存储器密集型处理程序,诸如神经网络及其他机器学习算法;数据库建构、索引搜寻及查询;以及包括比数据处理操作多的读取及写入操作的其他任务。

另外,可用数字数据的容量及粒度的快速增长已产生开发机器学习算法的机会且已启用新技术。然而,这也为数据库及平行计算的领域带来棘手的挑战。例如,社交媒体及物联网(IoT)的兴起以创记录的速率产生数字数据。此新数据可用以产生用于多种用途的算法,范围为新广告技术至工业处理程序的更精确控制方法。然而,新数据难以储存、处理、分析及处置。

新数据资源可为巨大的,有时为大约千兆(peta)字节至泽(zetta)字节。此外,这些数据资源的增长速率可能超过数据处理能力。因此,数据科学家已转向平行数据处理技术,以应对这些挑战。为了提高计算能力且处置大量数据,科学家已尝试产生能够进行平行密集型计算的系统及方法。但这些现有系统及方法跟不上数据处理要求,常常因为所使用的技术受该技术对用于数据管理、整合分隔数据及分析分段数据的额外资源的需求限制。

为了促进对大数据集的操控,工程师及科学家现在正设法改良用以分析数据的硬件。例如,新的半导体处理器或芯片(例如本文中所描述的半导体处理器或芯片)可通过在以更适合存储器操作而非算术计算的技术制造的单一基板中并入存储器及处理功能而特定地针对数据密集型任务设计。利用特定地针对数据密集型任务而设计的集成电路,有可能满足新的数据处理要求。然而,应对大数据集的数据处理的此新方法需要解决芯片设计及制造中的新问题。例如,若针对数据密集型任务而设计的新芯片利用用于普通芯片的制造技术及架构制造,则该新芯片将具有不良的效能和/或不可接受的良率。此外,若该新芯片经设计以利用当前数据处置方法进行操作,则该新芯片将具有不良的效能,这是因为当前方法可限制芯片处置平行操作的能力。

本公开描述用于减轻或克服上文所阐述的问题中的一个或多个以及现有技术中的其他问题的解决方案。

发明内容

在本公开的一些实施例中,一种存储器芯片可包括:多个存储器组;一数据储存器,其被配置为储存指示多个存储器组中的一个或多个区段的存取操作的存取信息;以及一刷新控制器,其被配置为至少部分地基于所储存的存取信息而执行该一个或多个区段的刷新操作。

本公开的一些实施例可包括一种非暂时性计算机可读介质,其储存在由至少一个处理器执行时使该至少一个处理器进行以下操作的指令:接收较高阶计算机代码;识别要由该较高阶计算机代码存取的在与一存储器芯片相关联的多个存储器组上分布的多个存储器区段;评估该较高阶计算机代码以识别在多个存储器存取循环上出现的多个存储器读取命令;致使与多个存储器读取命令相关联的数据跨越多个存储器区段中的每个的一分布,使得在多个存储器存取循环中的每个期间存取多个存储器区段中的每个。

本公开的一些实施例可包括一种非暂时性计算机可读介质,其储存在由至少一个处理器执行时使该至少一个处理器进行以下操作的指令:接收较高阶计算机代码;识别要由该较高阶计算机代码存取的在与一存储器芯片相关联的多个存储器组上分布的多个存储器区段;评估该较高阶计算机代码以识别多个存储器存取命令,每个存储器存取指令涉及多个存储器区段中的一个或多个;基于对多个存储器存取命令的分析且对于多个存储器区段当中的每个存储器区段,追踪自该存储器区段的最后一次存取起所累积的一时间量;及响应于自任何特定存储器区段的最后一次存取起的一时间量将超过预定阈值的一判定,将被配置为致使对该特定存储器区段的存取的一存储器刷新命令或一存储器存取命令中的至少一个引入至该较高阶计算机代码中。

在本公开的一些实施例中,具有一软件可配置的存储器刷新控制件的种存储器芯片可包括:多个存储器组及包括于多个存储器组中的每个中的多个存储器区段;及一刷新控制器,其包括一数据储存元件,该数据储存元件储存至少一个存储器刷新图案,该至少一个存储器刷新图案要被实施以刷新包括于多个存储器组中的每个中的多个存储器区段,并且其中该存储器刷新图案可使用软件来配置,以识别在一刷新循环期间,一特定存储器组中的多个存储器区段中的哪些需刷新,而该特定存储器组中的多个存储器区段中的哪些在该刷新循环期间不需刷新。

根据本公开的一实施例为一种用于从晶圆生产大小可选择的存储器芯片的方法。该方法包括形成包含一群组的晶粒及一耦接电路的晶圆(wafer),其中该群组中的晶粒(die)包含存储器单元,并且其中该耦接电路耦接至该群组中的晶粒。该方法还包括通过以下操作中的至少一个形成大小可选择的存储器芯片:切割包含该群组的晶粒及该耦接电路的该晶圆的一区,以提供包含该群组的晶粒的单一存储器芯片;及配置与该群组的晶粒相关联的至少一个控制器以将该群组的晶粒共同作为单一存储器芯片来控制;及切割该晶圆的区,该晶圆的每个区包括该群组的晶粒以提供多个分开的存储器芯片。

根据本公开的另一实施例为一种用于从晶圆生产大小可选择的存储器芯片的方法。该方法包括:在该晶圆上形成多个存储器芯片,多个存储器芯片沿着一或多行布置;及形成对应于该一或多行的至少一个共享的输入输出总线,其中该至少一个共享的输入输出总线将多个存储器芯片中的至少两个相电连接以共同用作单一芯片。该方法还可以包括自该晶圆切下多个存储器芯片中的具有该共享的输入输出总线的至少一个对应部分的至少两个,使得至少一个存储器控制器可配置以控制多个存储器芯片中的该至少两个,以共同用作单一芯片。

根据本公开的另一实施例为一种包括具有可选择大小的存储器芯片的晶圆。该晶圆可包括沿着该晶圆的一或多行布置的多个存储器芯片及对应于该一或多行的至少一个共享的输入输出总线。该晶圆还可以包括多个切割形状,多个切割形状包括多个存储器芯片且不包括该共享的输入输出总线的至少一部分。

本公开的一些实施例可包括提供双端口功能性的一种存储器实例。该存储器实例可包括:多个存储器组,其沿着至少一行及至少一列布置;至少一个列多任务器,其被配置为在单一时钟循环期间接收用于读取或写入的两个地址;及一行解码器,其被配置为与该至少一个列多任务器协作以进行以下操作:基于该两个地址启动一字线,其中该两个地址共享一字线地址;在一存储器存取循环期间通过解码对应于该两个地址中的第一地址的一比特线自该至少一个列多任务器取回该第一地址;及在该存储器存取循环期间通过解码对应于该两个地址中的第二地址的一比特线自该至少一个列多任务器取回该第二地址

在本公开的其他实施例中,提供双端口功能性的一种存储器实例可包括:多个存储器组,其沿着至少一行及至少一列布置;至少一个行多任务器或至少一个列多任务器,其被配置为在单一时钟循环期间接收用于读取或写入的两个地址;以及一行解码器及一列解码器,该解码器被配置为协作进行以下操作:在一第一循环期间自该至少一个行多任务器或该至少一个列多任务器取回该两个地址中的第一地址,且解码对应于该第一地址的字线及比特线;及在该第一循环之后的一第二循环期间,自该至少一个行多任务器或该至少一个列多任务器取回该两个地址中的第二地址,且解码对应于该第二地址的字线及比特线。

在本公开的一些实施例中,一种存储器实例可包括:多个存储器组,其沿着至少一行及至少一列布置;至少一个行电路及至少一个列电路,该电路被配置为用作开关;以及一行解码器及一列解码器,该解码器被配置为协作进行以下操作:在一存储器时钟循环期间,通过以下操作取回两个地址中的第一地址:通过传输一个或多个控制信号以闭合对应于该第一地址的开关元件中的多个组件来启动对应于该第一地址的该至少一个行电路及该至少一个列电路中的对应者,及使用存储器芯片的至少一个行多任务器及至少一个列多任务器以解码对应于该第一地址的字线及比特线;及在该存储器时钟循环期间,通过以下操作取回两个地址中的第二地址:通过传输一个或多个控制信号以闭合对应于该第二地址的该开关元件中的多个组件来启动对应于该第二地址的该至少一个行电路及该至少一个列电路中的对应者,及使用该至少一个行多任务器及该至少一个列多任务器以解码对应于该第二地址的字线及比特线。

在本公开的其他实施例中,一种用于双端口存取的存储器垫可包括:多个存储器胞元,其沿着至少一行及至少一列布置且包含多个电容性元件;至少两个行解码器,其用于启动该至少一行;至少两个列多任务器,其用于启动该至少一列;及第一多条导线,其将该存储器胞元连接至该至少两个行解码器中的第一行解码器及该至少两个列多任务器中的第一列多任务器;及第二多条导线,其将该存储器胞元连接至该至少两个行解码器中的第二行解码器及该至少两个列多任务器中的第二列多任务器。

在本公开的一些实施例中,一种集成电路可包含:一存储器单元,其包含存储器胞元、一输出端口及读取电路系统;以及一处理单元。该读取电路系统可包含:一缩减单元;及用于经由该输出端口输出多达第一数量的比特的存储器内读取路径的第一群组。该处理单元可被配置为将一读取请求发送至该存储器单元以自该存储器单元读取第二数量的比特。该缩减单元可被配置为在由该读取请求触发的读取操作期间基于该第一数量的比特及该第二数量的比特而控制该存储器内读取路径。

本公开的另一实施例可包括集成电路,包含:一存储器单元,其包含存储器胞元、一输出端口及写入电路系统;以及一处理单元。该写入电路系统可包含:一缩减单元;及用于经由该输出端口输出多达第一数量的比特的存储器内写入路径的第一群组。该处理单元可被配置为将一写入请求发送至该存储器单元以写入来自该存储器单元的第二数量的比特。该缩减单元可被配置为在由该写入请求触发的写入操作期间基于该第一数量的比特及该第二数量的比特而控制该存储器内写入路径。

本公开的一些实施例可包括一种用于缩减一集成电路的能量的方法。该方法可包括:通过该集成电路的处理单元将一读取请求发送至该集成电路的存储器单元以自该存储器单元读取第二数量的比特;其中该存储器单元包含存储器胞元、一输出端口及读取电路系统,该读取电路系统包含一缩减单元,及用于经由该输出端口输出多达第一数量的比特的存储器内读取路径的第一群组;及通过该缩减单元在由该读取请求触发的读取操作期间基于该第一数量的比特及该第二数量的比特而控制该存储器内读取路径。

在本公开的一些实施例中,一种存储器单元可包括:一第一存储器垫;一第二存储器垫;及一启动单元,其被配置为启动包括于该第一存储器垫中的存储器胞元的一第一群组,而不启动包括于该第二存储器垫中的存储器胞元的一第二群组,其中存储器胞元的该第一群组及存储器胞元的该第二群组均属于该存储器单元的单一行。

本公开的另一实施例可包括一存储器单元,包含:一第一存储器垫;一第二存储器垫;及一启动单元,其被配置为将一启动信号供应至该第一存储器垫的存储器胞元的一第一群组,且延迟该启动信号至该第二存储器垫的存储器胞元的第二群组的一供应,至少直至存储器胞元的该第一群组的启动已完成。存储器胞元的该第一群组及存储器胞元的该第二群组可属于该存储器单元的单一行。

在本公开的一些实施例中,一种存储器单元可包含一第一存储器垫、一第二存储器垫及一隔离单元。该隔离单元可被配置为在该第一存储器垫的第一存储器胞元被启动的初始启动时段期间将该第一存储器胞元与该第二存储器垫的第二存储器胞元相隔离;及在该初始启动时段之后将该第一存储器胞元耦接至该二存储器胞元;其中该第一存储器胞元及该第二存储器胞元属于该存储器单元的单一行。

一些实施例可包括一种用于操作一存储器单元的方法。该方法可包括通过一启动单元启动包括于该存储器单元的第一存储器垫中的存储器胞元的第一群组,而不启动包括于该存储器单元的第二存储器垫中的存储器胞元的第二群组。存储器胞元的该第一群组及存储器胞元的该第二群组可均属于该存储器单元的单一行。

在本公开的一些实施例中,一种集成电路可包含:一基板;一存储器阵列,其安置于该基板上;一处理阵列,其安置于该基板上;及一接口,其安置于该基板上。该存储器阵列可包含多个存储器组,该处理阵列可包含多个测试单元,多个测试单元可被配置为测试该多个存储器组以提供测试结果,且该接口可被配置为在该集成电路外部输出指示该测试结果的信息。

本公开的另一实施例可包括一种集成电路,包含:一基板;一存储器阵列,其安置于该基板上;一处理阵列,其安置于该基板上;及一接口,其安置于该基板上。该存储器阵列可包含多个存储器组,该接口可被配置为接收包含指令的配置信息,该处理阵列可被配置为执行该指令以存取该存储器阵列,执行计算操作且提供结果,且该接口可被配置为在该集成电路外部输出指示该结果的信息。

本公开的一些实施例可包括一种用于测试一集成电路的存储器组的方法。该方法可包括接收测试一集成电路的存储器组的一请求,该集成电路包含一基板、安置于该基板上且包含该存储器组的存储器阵列、安置于该基板上的处理阵列及安置于该基板上的接口;其中该处理阵列包含多个测试单元;通过多个测试单元且响应于该请求而测试该多个存储器组以提供测试结果;及通过该接口及在该集成电路外部输出指示该测试结果的信息。

在本公开的一些实施例中,一种用于测试一集成电路的存储器组的方法可包含:通过一集成电路的接口接收包含指令的配置信息,该集成电路包含一基板、包含存储器组且安置于该基板上的存储器阵列、安置于该基板上的处理阵列及安置于该基板上的接口;通过该处理阵列执行该指令,该执行通过存取该存储器阵列、执行计算操作及提供结果来进行;及通过该接口及在该集成电路外部输出指示该结果的信息。

根据本公开的其他实施例,非暂时性计算机可读储存媒体可储存程序指令,该程序指令由至少一个处理设备执行且执行本文中所描述的方法中的任一者。

前文的一般性描述和下文的详细描述仅是示例性和说明性的,并不限制权利要求。

附图说明

并入于本公开中且构成本公开的一部分的随附图式说明各种所公开实施例。在图式中:

图1为中央处理单元(CPU)的示意图。

图2为图形处理单元(GPU)的示意图。

图3A为符合所公开实施例的示例性硬件芯片的一实施例的示意图。

图3B为符合所公开实施例的示例性硬件芯片的另一实施例的示意图。

图4为由符合所公开实施例的示例性硬件芯片执行的通用命令的示意图。

图5为由符合所公开实施例的示例性硬件芯片执行的专门命令的示意图。

图6为供用于符合所公开实施例的示例性硬件芯片中的处理群组的示意图。

图7A为符合所公开实施例的处理群组的矩形阵列的示意图。

图7B为符合所公开实施例的处理群组的椭圆形阵列的示意图。

图7C为符合所公开实施例的硬件芯片的阵列的示意图。

图7D为符合所公开实施例的硬件芯片的另一阵列的示意图。

图8为描绘用于编译一系列指令以供在符合所公开实施例的示例性硬件芯片上执行的示例性方法的流程图。

图9为存储器组的示意图。

图10为存储器组的示意图。

图11为符合所公开实施例的具有子组控制件的示例性存储器组的一实施例的示意图。

图12为符合所公开实施例的具有子组控制件的示例性存储器组的另一实施例的示意图。

图13为符合所公开实施例的示例性存储器芯片的功能方块图。

图14为符合所公开实施例的示例性冗余逻辑区块集合的功能方块图。

图15为符合所公开实施例的示例性逻辑区块的功能方块图。

图16为符合所公开实施例的与总线连接的示例性逻辑区块的功能方块图。

图17为符合所公开实施例的串联连接的示例性逻辑区块的功能方块图。

图18为符合所公开实施例的成二维阵列连接的示例性逻辑区块的功能方块图。

图19为符合所公开实施例的处于复杂连接中的示例性逻辑区块的功能方块图。

图20为说明符合所公开实施例的冗余区块启用处理程序的示例性流程图。

图21为说明符合所公开实施例的地址指派处理程序的示例性流程图。

图22为符合所公开实施例的示例性处理设备的功能方块图。

图23为符合所公开实施例的示例性处理设备的功能方块图。

图24包括符合所公开实施例的示例性存储器配置图。

图25为说明符合所公开实施例的存储器配置处理程序的示例性流程图。

图26为说明符合所公开实施例的存储器读取处理程序的示例性流程图。

图27为说明符合所公开实施例的处理程序执行的示例性流程图。

图28为符合本公开的具有刷新控制器的存储器芯片的一实施例。

图29A为符合本公开的一实施例的刷新控制器。

图29B为符合本公开的另一实施例的刷新控制器。

图30为符合本公开的通过刷新控制器执行的处理程序的一实施例的流程图。

图31为符合本公开的由编译程序实施的处理程序的一实施例的流程图。

图32为符合本公开的由编译程序实施的处理程序的另一实施例的流程图。

图33展示符合本公开的通过所储存图案配置的示例刷新控制器。

图34为符合本公开的由刷新控制器内的软件实施的处理程序的示例流程图。

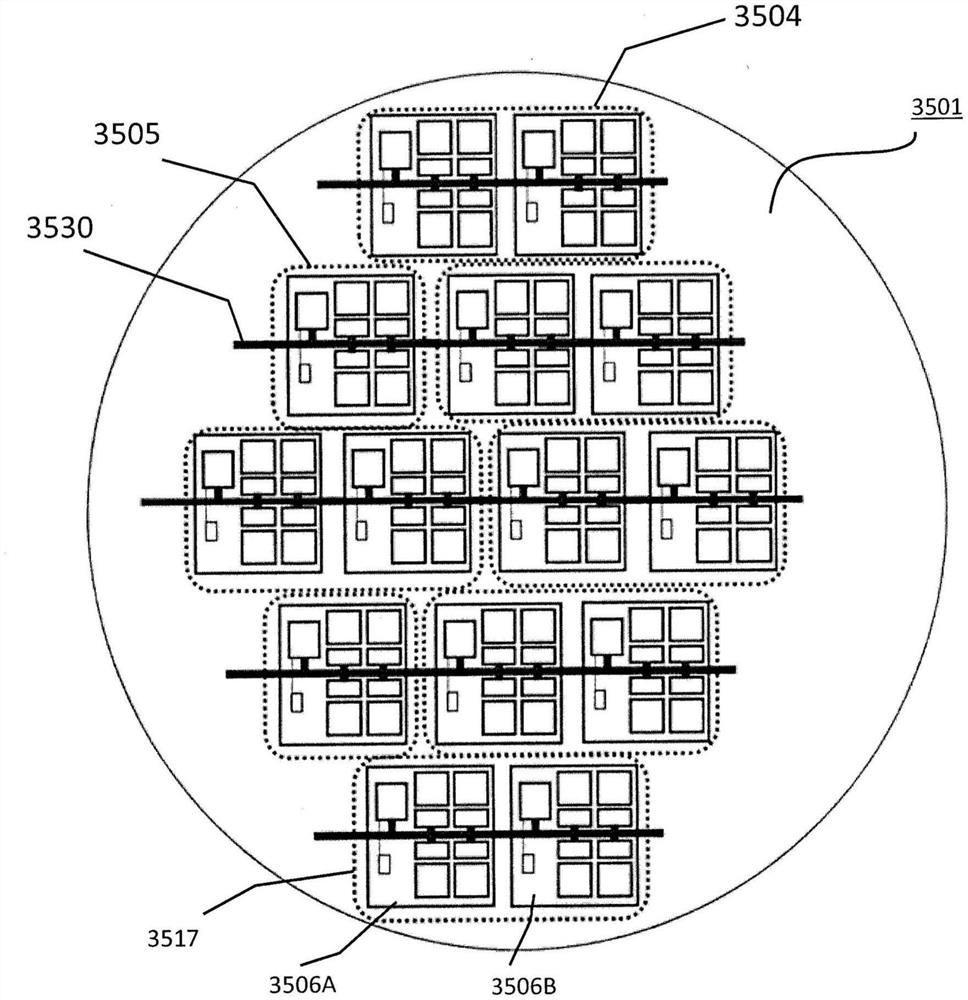

图35A展示符合本公开的包括晶粒的示例晶圆。

图35B展示符合本公开的连接至输入/输出总线的示例存储器芯片。

图35C展示符合本公开的包括成行布置且连接至输入输出总线的存储器芯片的示例晶圆。

图35D展示符合本公开的形成群组且连接至输入输出总线的两个存储器芯片。

图35E展示符合本公开的示例晶圆,其包括以六边形晶格置放且连接至输入输出总线的晶粒。

图36A至图36D展示符合本公开的连接至输入/输出总线的存储器芯片的各种可能配置。

图37展示符合本公开的共享胶合逻辑(glue logic)的晶粒的示例分组。

图38A至图38B展示符合本公开的穿过晶圆的示例切割。

图38C展示符合本公开的晶圆上的晶粒的示例布置及输入输出总线的布置。

图39展示符合本公开的具有互连处理器子单元的晶圆上的示例存储器芯片。

图40为符合本公开的从晶圆布局存储器芯片的群组的处理程序的一示例流程图。

图41A为符合本公开的从晶圆布局存储器芯片的群组的处理程序的另一示例流程图。

图41B至图41C为符合本公开的判定用于从晶圆切割存储器芯片的一个或多个群组的切割图案的处理程序的示例流程图。

图42为符合本公开的提供沿着列的双端口存取的存储器芯片内的电路系统的示例。

图43为符合本公开的提供沿着行的双端口存取的存储器芯片内的电路系统的示例。

图44为符合本公开的提供沿着行和列两者的双端口存取的存储器芯片内的电路系统的示例。

图45A为使用复制存储器阵列或垫的双读取。

图45B为使用复制存储器阵列或垫的双写入。

图46为符合本公开的具有用于沿着列的双端口存取的开关元件的存储器芯片内的电路系统的示例。

图47A为符合本公开的用于在单端口存储器阵列或垫上提供双端口存取的一处理程序的示例流程图。

图47B为符合本公开的用于在单端口存储器阵列或垫上提供双端口存取的另一处理程序的示例流程图。

图48为符合本公开的提供沿着行和列两者的双端口存取的存储器芯片内的电路系统的另一示例。

图49为符合本公开的用于存储器垫内的双端口存取的开关元件的示例。

图50为符合本公开的具有被配置为存取部分字的缩减单元的示例集成电路。

图51为用于使用如关于图50所描述的缩减单元的存储器组。

图52为符合本公开的使用集成至PIM逻辑中的缩减单元的存储器组。

图53为符合本公开的使用PIM逻辑以启动用于存取部分字的开关的存储器组。

图54A为符合本公开的具有用于撤销启动以存取部分字的分段列多任务器的存储器组。

图54B为符合本公开的用于存储器中的部分字存取的处理程序的示例流程图。

图55为包括多个存储器垫的现有存储器芯片。

图56为符合本公开的具有用于在线断开期间缩减功率消耗的启动电路的存储器芯片的一实施例。

图57为符合本公开的具有用于在线断开期间缩减功率消耗的启动电路的存储器芯片的另一实施例。

图58为符合本公开的具有用于在线断开期间缩减功率消耗的启动电路的存储器芯片的又一实施例。

图59为符合本公开的具有用于在线断开期间缩减功率消耗的启动电路的存储器芯片的再一实施例。

图60为符合本公开的具有用于在线断开期间缩减功率消耗的全局字线及区域字线的存储器芯片的一实施例。

图61为符合本公开的具有用于在线断开期间缩减功率消耗的全局字线及区域字线的存储器芯片的另一实施例。

图62为符合本公开的用于依序断开存储器中的线的处理程序的流程图。

图63为用于存储器芯片的现有测试器。

图64为用于存储器芯片的另一现有测试器。

图65为符合本公开的使用与存储器在相同基板上的逻辑单元测试存储器芯片的一实施例。

图66为符合本公开的使用与存储器在相同基板上的逻辑单元测试存储器芯片的另一实施例。

图67为符合本公开的使用与存储器在相同基板上的逻辑单元测试存储器芯片的又一实施例。

图68为符合本公开的使用与存储器在相同基板上的逻辑单元测试存储器芯片的再一实施例。

图69为符合本公开的使用与存储器在相同基板上的逻辑单元测试存储器芯片的另一实施例。

图70为符合本公开的用于测试存储器芯片的处理程序的流程图。

图71为符合本公开的用于测试存储器芯片的另一处理程序的流程图。

具体实施方式

以下详细描述参考随附图式。在任何方便之处,在图式及以下描述中使用相同参考编号来指代相同或类似部分。虽然本文中描述了若干说明性实施例,但修改、调适及其他实施为可能的。例如,可对图式中所说明的组件进行替代、添加或修改,且可通过替代、重排序、移除步骤或添加步骤至所公开方法来修改本文中所描述的说明性方法。因此,以下详细描述不限于所公开实施例及示例。反而,适当范畴由所附权利要求界定。

如贯穿本公开所使用,术语「硬件芯片」指半导体晶圆(诸如,硅或其类似物),其上形成有一个或多个电路元件(诸如,晶体管、电容器、电阻器和/或其类似物)。该电路元件可形成处理元件或存储器元件。「处理元件」指代共同执行至少一个逻辑功能(诸如,算术功能、逻辑门、其他布尔运算(Boolean operations)或其类似物)的一个或多个电路元件。处理元件可为通用处理元件(诸如,可配置的多个晶体管)或专用处理元件(诸如,经设计以执行特定逻辑功能的特定逻辑门或多个电路元件)。「存储器元件」指可用以储存数据的一个或多个电路元件。「存储器元件」也可被称作「存储器胞元」。存储器元件可为动态(使得需要电刷新以维持数据储存)、静态(使得数据在失去电力之后持续存在至少一段时间)或非易失性的存储器。

处理元件可接合以形成处理器子单元。「处理器子单元」因此可包含可执行至少一个任务或指令(例如,属于一处理器指令集)的处理元件的最小分组。例如,一子单元可包含被配置为共同执行指令的一个或多个通用处理元件、与经配置成以互补方式执行指令的一个或多个专用处理元件配对的一个或多个通用处理元件,或其类似物。该处理器子单元可以以阵列布置在一基板(例如,一晶圆)上。尽管「阵列」可包含矩形形状,但阵列中的子单元的任何布置可形成于基板上。

存储器元件可接合以形成存储器组(memory bank)。例如,存储器组可包含沿着至少一条导线(或其他导电连接件)链接的存储器元件的一个或多个线。此外,存储器元件可在另一方向上沿着至少一条添加导线链接。例如,存储器元件可沿着字线及比特线布置,如下文所解释。尽管存储器组可包含线,但组中的元件的任何布置可用以在基板上形成组。此外,一个或多个组可电接合至至少一个存储器控制器以形成存储器阵列。尽管存储器阵列可包含组的矩形布置,但阵列中的组的任何布置可形成于基板上。

如贯穿本公开进一步所使用,「总线」指基板的组件之间的任何通信连接件。例如,导线或线(形成电连接件)、光纤(形成光学连接件)或进行元件之间的通信的任何其他连接件可被称作「总线」。

常规处理器使通用逻辑电路与共享存储器配对。共享存储器可储存用于由逻辑电路执行的指令集以及用于指令集的执行且由指令集的执行产生的数据两者。如下文所描述,一些常规处理器使用高速缓存系统来缩减执行自共享存储器提取时的延迟;然而,常规高速缓存系统保持共享。常规处理器包括中央处理单元(CPU)、图形处理单元(GPU)、各种特殊应用集成电路(ASIC)或其类似物。图1展示CPU的示例,且图2展示GPU的示例。

如图1所示,CPU 100可包含处理单元110,处理单元110可包括一个或多个处理器子单元,诸如处理器子单元120a及处理器子单元120b。尽管图1中未描绘,但每一处理器子单元可包含多个处理元件。此外,处理单元110可包括一个或多个层级的片上高速缓存。此类高速缓存元件通常与处理单元110形成于相同半导体晶粒上,而非经由形成于基板中的一个或多个总线连接至处理器子单元120a及120b,该基板含有处理器子单元120a及120b以及高速缓存元件。对于常规处理器中的第一阶(L1)及第二阶(L2)高速缓存,直接在相同晶粒上而非经由总线连接的布置为常用的。替代地,在早期处理器中,L2高速缓存系使用子单元与L2高速缓存之间的背侧总线而在处理器子单元当中共享。背侧总线通常大于下文所描述的前侧总线。因此,因为高速缓存要供晶粒上的所有处理器子单元共享,所以高速缓存130可与处理器子单元120a及120b在相同晶粒上形成或经由一个或多个背侧总线以通信方式耦接至处理器子单元120a及120b。在不具有总线(例如,高速缓存直接形成于晶粒上)的实施例以及使用背侧总线的实施例两者中,高速缓存在CPU的处理器子单元之间共享。

此外,处理单元110与共享存储器140a及存储器140b通信。例如,存储器140a及140b可表示共享动态随机存取存储器(DRAM)的存储器组。尽管描绘为具有两个存储器组,但大部分常规存储器芯片包括介于八个与十六个之间的存储器组。因此,处理器子单元120a及120b可使用共享存储器140a及140b储存数据,该数据接着由处理器子单元120a及120b进行操作。然而,此布置导致存储器140a及140b与处理单元110之间的总线在处理单元110的时钟速度超过总线的数据传送速度时成为瓶颈。对于常规处理器,通常系如此情况,从而导致低于基于时钟速率及晶体管数量的规定处理速度的有效处理速度。

如图2中所展示,GPU中也存在类似缺陷。GPU 200可包含处理单元210,处理单元210可包括一个或多个处理器子单元(例如,子单元220a、220b、220c、220d、220e、220f、220g、220h、220i、220j、220k、220l、220m、220n、220o及220p)。此外,处理单元210可包括一个或多个层级的片上高速缓存和/或寄存器档案。此类高速缓存元件通常与处理单元210形成于相同半导体晶粒上。实际上,在图2的实施例中,高速缓存210与处理单元210形成于相同晶粒上且在所有处理器子单元当中共享,而高速缓存230a、230b、230c及230d分别形成于处理器子单元的子集上且专用于该处理器子单元。

此外,处理单元210与共享存储器250a、250b、250c及250d通信。例如,存储器250a、250b、250c及250d可表示共享DRAM的存储器组。因此,处理单元210的处理器子单元可使用共享存储器250a、250b、250c及250d储存数据,该数据接着由该处理器子单元进行操作。然而,此布置导致存储器250a、250b、250c及250d与处理单元210之间的总线成为瓶颈,其类似于上文关于CPU所描述的瓶颈。

图3A为描绘示例性硬件芯片300的实施例的示意图。硬件芯片300可包含经设计以缓解上文关于CPU、GPU及其他常规处理器所描述的瓶颈的分布式处理器。分布式处理器可包括在空间上分布于单一基板上的多个处理器子单元。此外,如上文所解释,在本公开的分布式处理器中,对应存储器组还在空间上分布于基板上。在一些实施例中,分布式处理器可与一组指令相关联,且分布式处理器的处理器子单元中的每一个可负责执行包括于该组指令中的一个或多个任务。

如图3A中所描绘,硬件芯片300可包含多个处理器子单元,例如,逻辑及控制子单元320a、320b、320c、320d、320e、320f、320g及320h。如图3A中进一步所描绘,每一处理器子单元可具有一专用存储器实例。例如,逻辑及控制子单元320a可操作地连接至专用存储器实例330a,逻辑及控制子单元320b可操作地连接至专用存储器实例330b,逻辑及控制子单元320c可操作地连接至专用存储器实例330c,逻辑及控制子单元320d可操作地连接至专用存储器实例330d,逻辑及控制子单元320e可操作地连接至专用存储器实例330e,逻辑及控制子单元320f可操作地连接至专用存储器实例330f,逻辑及控制子单元320g可操作地连接至专用存储器实例330g,且逻辑及控制子单元320h可操作地连接至专用存储器实例330h。

尽管图3A将每个存储器实例描绘为单一存储器组,但硬件芯片300可包括两个或多于两个存储器组作为用于硬件芯片300上的处理器子单元的专用存储器实例。此外,尽管图3A将每一处理器子单元描绘为包含逻辑组件及用于专用存储器组的控制件两者,但硬件芯片300可使用用于存储器组的控制件,该控制件至少部分地与该逻辑组件分开。此外,如图3A中所描绘,可将两个或多于两个处理器子单元及其对应存储器组分组成例如处理群组310a、310b、310c及310d。「处理群组」可表示上面形成有硬件芯片300的基板上的空间区别。因此,处理群组可包括用于群组中的存储器组的其他控制件,例如,控制件340a、340b、340c及340d。另外或替代地,「处理群组」可表示用于编译代码以供在硬件芯片300上执行的目的的逻辑分组。因此,用于硬件芯片300的编译程序(下文进一步描述)可在硬件芯片300上的处理群组之间划分整组指令。

此外,主机350可将指令、数据及其他输入提供至硬件芯片300且自该硬件芯片读取输出。因此,一组指令可全部在单一晶粒上,例如在代管硬件芯片300的晶粒上执行。实际上,晶粒外的仅有通信可包括指令至硬件芯片300的加载、发送至硬件芯片300的任何输入及从硬件芯片300读取的任何输出。因此,所有计算及存储器操作可在晶粒上(在硬件芯片300上)执行,这是因为硬件芯片300的处理器子单元与硬件芯片300的专用存储器组通信。

图3B为另一示例性硬件芯片300'的实施例的示意图。尽管描绘为硬件芯片300的替代,但图3B中所描绘的架构可至少部分地与图3A中所描绘的架构组合。

如图3B中所描绘,硬件芯片300'可包含多个处理器子单元,例如,处理器子单元350a、350b、350c及350d。如图3B中进一步所描绘,每一处理器子单元可具有多个专用存储器实例。例如,处理器子单元350a可操作地连接至专用存储器实例330a及330b,处理器子单元350b可操作地连接至专用存储器实例330c及330d,处理器子单元350c可操作地连接至专用存储器实例330e及330f,且处理器子单元350d可操作地连接至专用存储器实例330g及330h。此外,如图3B中所描绘,可将处理器子单元及其对应存储器组分组成例如处理群组310a、310b、310c及310d。如上文所解释,「处理群组」可表示上面形成有硬件芯片300'的基板上的空间区别和/或用于编译代码以供在硬件芯片300'上执行的目的的逻辑分组。

如图3B中进一步所描绘,处理器子单元可经由总线彼此通信。例如,如图3B所展示,处理器子单元350a可经由总线360a与处理器子单元350b通信,经由总线360c与处理器子单元350c通信,且经由总线360f与处理器子单元350d通信。类似地,处理器子单元350b可经由总线360a与处理器子单元350a通信(如上文所描述),经由总线360e与处理器子单元350c通信,且经由总线360d与处理器子单元350d通信。此外,处理器子单元350c可经由总线360c与处理器子单元350a通信(如上文所描述),经由总线360e与处理器子单元350b通信(如上文所描述),且经由总线360b与处理器子单元350d通信。因此,处理器子单元350d可经由总线360f与处理器子单元350a通信(如上文所描述),经由总线360d与处理器子单元350b通信(如上文所描述),且经由总线360b与处理器子单元350c通信(如上文所描述)。本领域技术人员将理解,可使用比图3B中所描绘的总线少的总线。例如,可消除总线360e,使得处理器子单元350b与350c之间的通信经由处理器子单元350a和/或350d传递。类似地,可消除总线360f,使得处理器子单元350a与处理器子单元350d之间的通信经由处理器子单元350b或350c传递。

此外,本领域技术人员将理解,可使用除图3A及图3B中所描绘的架构以外的架构。例如,各具有单处理器子单元及存储器实例的处理群组的阵列可布置在基板上。处理器子单元可另外或替代地形成用于对应的专用存储器组的控制器的部分、用于对应的专用存储器的存储器垫的控制器的部分,或其类似物。

鉴于上文所描述的架构,相较于传统架构,硬件芯片300及300'可显着提高存储器密集型任务的效率。例如,数据库操作及人工智能算法(诸如,神经网络)为存储器密集型任务的示例,对于存储器密集型任务,传统架构在效率上低于硬件芯片300及300'。因此,硬件芯片300及300'可被称作数据库加速器处理器和/或人工智能加速器处理器。

上文所描述的硬件芯片架构可被配置为用于代码执行。例如,每一处理器子单元可与硬件芯片中的其他处理器子单元隔开而个别地执行代码(定义一组指令)。因此,替代依赖于操作系统来管理多线程处理或使用多任务处理(其为并发的而非平行的),本公开的硬件芯片可允许处理器子单元完全平行地操作。

除上文所描述的完全平行实施以外,指派给每一处理器子单元的指令中的至少一些可重叠。例如,分布式处理器上的多个处理器子单元可执行重叠指令作为例如操作系统或其他管理软件的实施,同时执行非重叠指令以便在操作系统或其他管理软件的内容背景内执行平行任务。

图4描绘通过处理群组410进行的用于执行通用命令的示例性处理程序400。例如,处理群组410可包含本公开的硬件芯片(例如,硬件芯片300、硬件芯片300'或其类似物)的一部分。

如图4中所描绘,命令可发送至与专用存储器实例420配对的处理器子单元430。外部主机(例如,主机350)可将该命令发送至处理群组410以供执行。替代地,主机350可能已发送包括该命令的指令集以用于储存于存储器实例420中,使得处理器子单元430可从存储器实例420取回命令且执行所取回的命令。因此,该命令可由处理元件440执行,该处理元件为可配置以执行所接收的命令的通用处理元件。此外,处理群组410可包括用于存储器实例420的控制件460。如图4中所描绘,控制件460可执行处理元件440在执行所接收的命令时所需的对存储器实例420的任何读取和/或写入。在执行命令之后,处理群组410可将命令的结果输出至例如外部主机或输出至相同硬件芯片上的不同处理群组。

在一些实施例中,如图4中所描绘,处理器子单元430还可以包括地址生成器450。「地址生成器」可包含多个处理元件,多个处理元件被配置为判定用于执行读取及写入的一个或多个存储器组中的地址,且也可对位于所判定地址处的数据执行操作(例如,加法、减法、乘法或其类似物)。例如,地址生成器450可判定用于对存储器进行的任何读取或写入的地址。在一个示例中,地址生成器450可通过在不再需要读取值时用基于命令所判定的新值覆写读取值来提高效率。另外或替代地,地址生成器450可选择可用地址以用于储存来自命令执行的结果。此可允许为后一时钟循环调度结果读出,这对于外部主机较为便利。在另一示例中,地址生成器450可在诸如向量或矩阵乘法累加(multiply-accumulate)计算的多循环计算期间判定读取及写入的地址。因此,地址生成器450可维持或计算用于读取数据及写入多循环计算的中间结果的存储器地址,使得处理器子单元430可继续处理而不必储存这些存储器地址。

图5描绘通过处理群组510进行的用于执行专门命令的示例性处理程序500。例如,处理群组510可包含本公开的硬件芯片(例如,硬件芯片300、硬件芯片300'或其类似物)的一部分。

如图5中所描绘,专门命令(例如,乘法累加命令)可发送至与专用存储器实例520配对的处理元件530。外部主机(例如,主机350)可将该命令发送至处理元件530以供执行。因此,该命令可由处理元件530在来自主机的给定信号下执行,该处理元件为可配置以执行特定命令(包括所接收的命令)的专门处理元件。替代地,处理元件530可从存储器实例520取回命令以供执行。因此,在图5的示例中,处理元件530为乘法累加(MAC)电路,该电路被配置为执行从外部主机接收或从存储器实例520取回的MAC命令。在执行命令之后,处理群组410可将命令的结果输出至例如外部主机或输出至相同硬件芯片上的不同处理群组。尽管关于单一命令及单一结果来描绘,但可接收或取回并执行多个命令,且多个结果可在输出之前在处理群组510上组合。

尽管在图5中描绘为MAC电路,但额外或替代的专门电路可包括于处理群组510中。例如,可实施MAX读取命令(其传回向量的最大值)、MAX0读取命令(也被称作整流器的常用功能,其传回整个向量,而且传回为0的最大值),或其类似物。

尽管分开地描绘,但图4的一般处理群组410及图5的专门处理群组510可组合。例如,通用处理器子单元可耦接至一个或多个专门处理器子单元以形成处理器子单元。因此,通用处理器子单元可用于不可由一个或多个专门处理器子单元执行的所有指令。

本领域技术人员将理解,可通过专门逻辑电路来处置神经网络实施及其他记忆密集型任务。例如,数据库查询、封包检测、字符串比较及其他功能在由本文中所描述的硬件芯片执行的情况下可提高效率。

在符合本公开的硬件芯片上,专用总线可在该芯片上的处理器子单元之间和/或在该处理器子单元与其对应的专用存储器组之间传送数据。使用专用总线可降低仲裁成本,这是因为竞争请求系不可能的或容易使用软件而非使用硬件来避免。

图6示意性地描绘处理群组600的示意图。处理群组600可供用于硬件芯片(例如,硬件芯片300、硬件芯片300'或其类似物)中。处理器子单元610可经由总线630连接至存储器620。存储器620可包含随机可存取存储器(RAM)元件,其储存用于由处理器子单元610执行的数据及代码。在一些实施例中,存储器620可为N路存储器(其中N为等于或大于1的数字,其暗示交错的存储器620中的区段的数量)。因为处理器子单元610经由总线630耦接至专用于处理器子单元610的存储器620,所以N可保持相对较小而不损害执行效能。此表示对常规多路寄存器档案或高速缓存的改良,其中较低N通常导致较低执行效能,且较高N通常导致大的面积及功率损失。

可根据例如一个或多个任务中所涉及的数据的大小而调整存储器620的大小、通路的数量及总线630的宽度以满足使用处理群组600的系统的任务及应用程序实施的要求。存储器元件620可包含此项技术中已知的一个或多个类型的存储器,例如,易失性存储器(诸如,RAM、DRAM、SRAM、相变RAM(PRAM)、磁阻式RAM(MRAM)、电阻式RAM(ReRAM)或其类似物)或非易失性存储器(诸如,快闪存储器或ROM)。根据一些实施例,存储器元件620的一部分可包含第一存储器类型,而另一部分可包含另一存储器类型。例如,存储器元件620的代码区可包含ROM元件,而存储器元件620的数据区可包含DRAM元件。此分割的另一示例为将神经网络的权重储存于快闪存储器中,而将用于计算的数据储存于DRAM中。

处理器子单元610包含处理元件640,该处理元件可包含处理器。该处理器可为管线式或非管线式的,可为定制精简指令集计算(RISC)元件或其他处理方案,实施于此项技术中已知的任何商业集成电路(IC)(诸如,ARM、ARC、RISCV等)上,如本领域技术人员所了解。处理元件640可包含控制器,该控制器在一些实施例中包括算术逻辑单元(ALU)或其他控制器。

根据本公开的一些实施例,执行所接收或所储存的代码的处理元件640可包含通用处理元件,且因此为灵活的并能够执行广泛多种处理操作。当比较在特定操作的执行期间所消耗的功率时,非专用电路系统通常比特定操作专用电路系统消耗更多功率。因此,当执行特定的复杂算术计算时,处理元件640可比专用硬件消耗更多功率且执行效率更低。因此,根据一些实施例,处理元件640的控制器可经设计以执行特定操作(例如,加法或「移动」操作)。

在本公开的一实施例中,特定操作可由一个或多个加速器650执行。每一加速器可为专用的且经编程以执行特定计算(诸如,乘法、浮点向量运算或其类似物)。通过使用加速器,每个处理器子单元的每次计算所消耗的平均功率可降低,且计算吞吐量此后增大。可根据系统经设计以实施的应用程序(例如,执行神经网络、执行数据库查询或其类似物)而选择加速器650。加速器650可由处理元件640配置且可与处理元件串接地操作以用于降低功率消耗且加速计算及计算。加速器可另外或替代地用以在诸如智能型直接存储器存取(DMA)周边设备的处理群组600的存储器与MUX/DEMUX/输入/输出端口(例如,MUX 650及DEMUX 660)之间传送数据。

加速器650可被配置为执行多种功能。例如,一个加速器可被配置为执行常用于神经网络中的16比特浮点计算或8比特整数计算。加速器功能的另一示例为常用于神经网络的训练阶段期间的32比特浮点计算。加速器功能的又一示例为查询处理,诸如用于数据库中的查询处理。在一些实施例中,加速器650可包含用以执行这些功能的专门处理元件和/或可根据储存于存储器元件620上的配置数据而配置使得其可加以修改。

加速器650可另外或替代地实施存储器移动的可配置的脚本处理列表以对数据至/从存储器620或至/从其他加速器和/或输入/输出的移动进行计时。因此,如下文进一步所解释,使用处理群组600的硬件芯片内部的所有数据移动可使用软件同步而非硬件同步。例如,一个处理群组(例如,群组600)中的加速器可每十个循环将数据从其输入端传送至其加速器,接着在下一个循环输出数据,藉此使信息从处理群组的存储器流送至另一存储器。

如图6中进一步所描绘,在一些实施例中,处理群组600还可包含连接至其输入端口的至少一个输入多任务器(MUX)660及连接至其输出端口的至少一个输出DEMUX 670。这些MUX/DEMUX可由来自处理元件640和/或来自加速器650中的一个的控制信号(未图标)控制,该控制信号系根据正由处理元件640进行的当前指令和/或由加速器650中的加速器执行的操作而判定。在一些情境中,可能需要处理群组600(根据来自其代码存储器的预定义指令)将数据从其输入端口传送至其输出端口。因此,除DEMUX/MUX中的每个连接至处理元件640及加速器650以外,输入MUX(例如,MUX 660)中的一个或多个也可经由一个或多个总线直接连接至输出DEMUX(例如,DEMUX 670)。

图6的处理群组600可排成阵列以形成分布式处理器,例如,如图7A中所描绘。处理群组可安置于基板710上以形成阵列。在一些实施例中,基板710可包含诸如硅的半导体基板。另外或替代地,基板710可包含电路板,诸如可挠性电路板。

如图7A中所描绘,基板710可包括安置于其上的多个处理群组,诸如处理群组600。因此,基板710包括存储器阵列,该存储器阵列包括多个组,诸如组720a、720b、720c、720d、720e、720f、720g及720h。此外,基板710包括处理阵列,该处理阵列可包括多个处理器子单元,诸如子单元730a、730b、730c、730d、730e、730f、730g及730h。

此外,如上文所解释,每一处理群组可包括一处理器子单元及专用于该处理器子单元的一个或多个对应的存储器组。因此,如图7A中所描绘,每一子单元与一对应的专用存储器组相关联,例如:处理器子单元730a与存储器组720a相关联,处理器子单元730b与存储器组720b相关联,处理器子单元730c与存储器组720c相关联,处理器子单元730d与存储器组720d相关联,处理器子单元730e与存储器组720e相关联,处理器子单元730f与存储器组720f相关联,处理器子单元730g与存储器组720g相关联,处理器子单元730h与存储器组720h相关联。

为了允许每一处理器子单元与其对应的专用存储器组通信,基板710可包括将处理器子单元中的一个连接至其对应的专用存储器组的第一多个总线。因此,总线740a将处理器子单元730a连接至存储器组720a,总线740b将处理器子单元730b连接至存储器组720b,总线740c将处理器子单元730c连接至存储器组720c,总线740d将处理器子单元730d连接至存储器组720d,总线740e将处理器子单元730e连接至存储器组720e,总线740f将处理器子单元730f连接至存储器组720f,总线740g将处理器子单元730g连接至存储器组720g,且总线740h将处理器子单元730h连接至存储器组720h。此外,为了允许每一处理器子单元与其他处理器子单元通信,基板710可包括将处理器子单元中的一个连接至处理器子单元中的另一个的第二多个总线。在图7A的示例中,总线750a将处理器子单元730a连接至处理器子单元750e,总线750b将处理器子单元730a连接至处理器子单元750b,总线750c将处理器子单元730b连接至处理器子单元750f,总线750d将处理器子单元730b连接至处理器子单元750c,总线750e将处理器子单元730c连接至处理器子单元750g,总线750f将处理器子单元730c连接至处理器子单元750d,总线750g将处理器子单元730d连接至处理器子单元750h,总线750h将处理器子单元730h连接至处理器子单元750g,总线750i将处理器子单元730g连接至处理器子单元750g,且总线750j将处理器子单元730f连接至处理器子单元750e。

因此,在图7A中所展示的示例布置中,多个逻辑处理器子单元布置成至少一行及至少一列。该第二多个总线将每一处理器子单元连接至相同行中的至少一个邻近处理器子单元且连接至相同列中的至少一个邻近处理器子单元。图7A可被称作「部分块连接」。

图7A中所展示的配置可经修改以形成「完全块连接」。完全块连接包括连接对角线处理器子单元的额外总线。例如,该第二多个总线可包括处理器子单元730a与处理器子单元730f之间、处理器子单元730b与处理器子单元730e之间、处理器子单元730b与处理器子单元730g之间、处理器子单元730c与处理器子单元730f之间、处理器子单元730c与处理器子单元730h之间以及处理器子单元730d与处理器子单元730g之间的额外总线。

完全块连接可用于卷积计算,在卷积计算中,使用储存于附近处理器子单元中的数据及结果。例如,在卷积图像处理期间,每一处理器子单元可接收图像的块(诸如,像素或像素群组)。为了计算卷积结果,每一处理器子单元可从所有八个邻近处理器子单元获取数据,该邻近处理器子单元中的每个已接收对应块。在部分块连接中,来自对角线邻近处理器子单元的数据可经由连接至该处理器子单元的其他邻近处理器子单元传递。因此,芯片上的分布式处理器可为人工智能加速器处理器。

在卷积计算的特定实施例中,可跨越多个处理器子单元来划分N×M图像。每一处理器子单元可在其对应块上通过A×B滤波器执行卷积。为了对块之间的边界上的一个或多个像素执行滤波,每一处理器子单元可能需要来自相邻处理器子单元的数据,该相邻处理器子单元具有包括相同边界上的像素的块。因此,针对每一处理器子单元产生的代码配置该子单元以计算卷积且每当需要来自邻近子单元的数据时从第二多个总线提取。将数据输出至第二多个总线的对应命令被提供至该子单元以确保所需数据传送的适当时序。

图7A的部分块连接可修改为N部分块连接。在此修改中,第二多个总线可进一步将每一处理器子单元连接至在图7A的总线延其所沿的四个方向(也即,上、下、左及右)上在该处理器子单元的阈值距离内(例如,在n个处理器子单元内)的处理器子单元。可对完全块连接进行类似修改(以产生N完全块连接),使得第二多个总线进一步将每一处理器子单元连接至在除两个对角线方向以外的图7A的总线延其所沿的四个方向上在该处理器子单元的阈值距离内(例如,在n个处理器子单元内)的处理器子单元。

其他布置也是可能的。例如,在图7B中所展示的布置中,总线750a将处理器子单元730a连接至处理器子单元730d,总线750b将处理器子单元730a连接至处理器子单元730b,总线750c将处理器子单元730b连接至处理器子单元730c,且总线750d将处理器子单元730c连接至处理器子单元730d。因此,在图7B中所展示的示例布置中,多个处理器子单元布置成星形图案。第二多个总线将每一处理器子单元连接至星形图案内的至少一个邻近处理器子单元。

其他布置(未示出)也是可能的。例如,可使用相邻者连接布置,使得多个处理器子单元布置在一个或多个线中(例如,类似于图7A中所描绘的情况)。在相邻者连接布置中,第二多个总线将每一处理器子单元连接至相同线中在左方的处理器子单元、相同线中在右方的处理器子单元、相同线中在左方及右方两者的处理器子单元,等等。

在另一实施例中,可使用N线性连接布置。在N线性连接布置中,第二多个总线将每一处理器子单元连接至在该处理器子单元的阈值距离内(例如,在n个处理器子单元内)的处理器子单元。N线性连接布置可与线阵列(上文所描述)、矩形阵列(图7A中所描绘)、椭圆形阵列(图7B中所描绘)或任何其他几何阵列共同使用。

在又一实施例中,可使用N对数连接布置。在N对数连接布置中,第二多个总线将每一处理器子单元连接至在该处理器子单元的二的幂的阈值距离内(例如,在2

可组合上文所描述的连接方案中的任一者以用于相同硬件芯片中。例如,可在一个区中使用完全块连接,而在另一区中使用部分块连接。在另一实施例中,可在一个区中使用N线性连接布置,而在另一区中使用N完全块连接。

替代存储器芯片的处理器子单元之间的专用总线或除该专用总线以外,也可使用一个或多个共享总线以互连分布式处理器的所有处理器子单元(或处理器子单元的子集)。仍可通过使用由处理器子单元执行的代码对共享总线上的数据传送进行计时来避免共享总线上的冲突,如下文进一步所解释。替代共享总线或除共享总线以外,也可使用可配置总线以动态地连接处理器子单元以形成连接至分开总线的处理器单元的群组。例如,可配置总线可包括晶体管或可由处理器子单元来控制以将数据传送引导至选定处理器子单元的其他机构。

在图7A及图7B两者中,处理阵列的多个处理器子单元在空间上分布于存储器阵列的多个离散存储器组当中。在其他替代实施例(未示出)中,多个处理器子单元可聚集在基板的一个或多个区中,且多个存储器组可聚集在基板的一个或多个其他区中。在一些实施例中,可使用空间分布与聚集的组合(未图标)。例如,基板的一个区可包括处理器子单元的丛集,基板的另一区可包括存储器组的丛集,且基板的又一区可包括分布于存储器组当中的处理阵列。

本领域技术人员将认识到,在基板上将处理器群组600排成阵列并非排他性实施例。例如,每一处理器子单元可与至少两个专用存储器组相关联。因此,可替代处理群组600或与处理群组600组合地使用图3B的处理群组310a、310b、310c及310d,以形成处理阵列及存储器阵列。可使用包括例如三个、四个或多于四个专用存储器组的其他处理群组(未示出)。

多个处理器子单元中的每个可被配置为相对于包括于多个处理器子单元中的其他处理器子单元独立地执行与特定应用程序相关联的软件代码。例如,如下文所解释,指令的多个子系列可分组为机器码且被提供至每一处理器子单元以供执行。

在一些实施例中,每一专用存储器组包含至少一个动态随机存取存储器(DRAM)。替代地,存储器组可包含诸如静态随机存取存储器(SRAM)、DRAM、快闪存储器或其类似物的存储器类型的混合。

在常规处理器中,处理器子单元之间的数据共享通常通过共享存储器来执行。共享存储器通常需要大部分芯片面积和/或执行由额外硬件(诸如,仲裁器)管理的总线。如上文所描述,该总线造成瓶颈。此外,可在芯片外部的共享存储器通常包括缓存一致性机制及更复杂的高速缓存(例如,L1高速缓存、L2高速缓存及共享DRAM),以便将准确且最新的数据提供至处理器子单元。如下文进一步所解释,图7A及图7B中所描绘的专用总线允许无硬件管理(诸如,仲裁器)的硬件芯片。此外,使用如图7A及图7B中所描绘的专用存储器允许消除复杂的高速缓存层及一致性机制。

反而,为了允许每一处理器子单元存取由其他处理器子单元计算和/或储存于专用于其他处理器子单元的存储器组中的数据,提供总线,该总线的时序系使用由每一处理器子单元个别地执行的代码动态地执行。此情形允许消除如常规地所使用的大部分(若非全部)总线管理硬件。此外,这些总线上的直接传送替换复杂的高速缓存机制,以缩减在存储器读取及写入期间的延时时间。

如图7A及图7B中所描绘,本公开的存储器芯片可独立地操作。替代地,本公开的存储器芯片可与诸如存储器设备(例如,一个或多个DRAM组)、系统单芯片、场可编程门阵列(FPGA)或其他处理和/或存储器芯片的一个或多个额外集成电路可操作地连接。在这些实施例中,由该架构执行的一系列指令中的任务可在存储器芯片的处理器子单元与额外集成电路的任何处理器子单元之间进行划分(例如,通过编译程序,如下文所描述)。例如,其他集成电路可包含将指令和/或数据输入至存储器芯片且从其接收输出的主机(例如,图3A的主机350)。

为了将本公开的存储器芯片与一个或多个额外集成电路互连,存储器芯片可包括存储器接口,诸如遵从联合电子设备工程委员会(Joint Electron Device EngineeringCouncil;JEDEC)标准或其变体中的任一者的存储器接口。一个或多个额外集成电路接着可连接至该存储器接口。因此,若该一个或多个额外集成电路连接至本公开的多个存储器芯片,则数据可经由该一个或多个额外集成电路在存储器芯片之间共享。另外或替代地,该一个或多个额外集成电路可包括用以连接至本公开的存储器芯片上的总线的总线,使得该一个或多个额外集成电路可与本公开的存储器芯片串接地执行代码。在这些实施例中,该一个或多个额外集成电路进一步辅助分布式处理,即使该额外集成电路可与本公开的存储器芯片在不同基板上亦如此。

此外,本公开的存储器芯片可排成阵列以便形成分布式处理器的阵列。例如,一个或多个总线可将存储器芯片770a连接至额外存储器芯片770b,如图7C中所描绘。在图7C的实施例中,存储器芯片770a包括处理器子单元与专用于每一处理器子单元的一个或多个对应的存储器组,例如:处理器子单元730a与存储器组720a相关联,处理器子单元730b与存储器组720b相关联,处理器子单元730e与存储器组720c相关联,且处理器子单元730f与存储器组720d相关联。总线将每一处理器子单元连接至其对应的存储器组。因此,总线740a将处理器子单元730a连接至存储器组720a,总线740b将处理器子单元730b连接至存储器组720b,总线740c将处理器子单元730e连接至存储器组720c,且总线740d将处理器子单元730f连接至存储器组720d。此外,总线750a将处理器子单元730a连接至处理器子单元750e,总线750b将处理器子单元730a连接至处理器子单元750b,总线750c将处理器子单元730b连接至处理器子单元750f,且总线750d将处理器子单元730e连接至处理器子单元750f。例如,如上文所描述,可使用存储器芯片770a的其他布置。

类似地,存储器芯片770b包括处理器子单元与专用于每一处理器子单元的一个或多个对应的存储器组,例如:处理器子单元730c与存储器组720e相关联,处理器子单元730d与存储器组720f相关联,处理器子单元730g与存储器组720g相关联,且处理器子单元730h与存储器组720h相关联。总线将每一处理器子单元连接至其对应的存储器组。因此,总线740e将处理器子单元730c连接至存储器组720e,总线740f将处理器子单元730d连接至存储器组720f,总线740g将处理器子单元730g连接至存储器组720g,且总线740h将处理器子单元730h连接至存储器组720h。此外,总线750g将处理器子单元730c连接至处理器子单元750g,总线750h将处理器子单元730d连接至处理器子单元750h,总线750i将处理器子单元730c连接至处理器子单元750d,且总线750j将处理器子单元730g连接至处理器子单元750h。例如,如上文所描述,可使用存储器芯片770b的其他布置。

存储器芯片770a及770b的处理器子单元可使用一个或多个总线来连接。因此,在图7C的实施例中,总线750e可将存储器芯片770a的处理器子单元730b与存储器芯片770b的处理器子单元730c连接,且总线750f可将存储器芯片770a的处理器子单元730f与存储器770b的处理器子单元730c连接。例如,总线750e可用作至存储器芯片770b的输入总线(且因此用作存储器芯片770a的输出总线),而总线750f可用作至存储器芯片770a的输入总线(且因此用作存储器芯片770b的输出总线),或反之亦然。替代地,总线750e及750f均可用作存储器芯片770a与770b之间的双向总线。

总线750e及750f可包括直接导线或可在高速连接上交错,以便缩减用于存储器芯片770a与集成电路770b之间的芯片间接口的接脚。此外,用于存储器芯片本身中的上文所描述的连接布置中的任一者可用以将存储器芯片连接至一个或多个额外集成电路。例如,存储器芯片770a及770b可使用完全块或部分块连接而非如图7C所展示仅使用两个总线来连接。

因此,尽管使用总线750e及750f来描绘,但架构760可包括更少总线或额外总线。例如,可使用处理器子单元730b与730c之间或处理器子单元730f与730c之间的单一总线。替代地,可使用例如处理器子单元730b与730d之间、处理器子单元730f与730d之间或其类似物的额外总线。

此外,尽管描绘为使用单一存储器芯片及一额外集成电路,但多个存储器芯片可使用如上文所解释的总线来连接。例如,如图7C的实施例中所描绘,存储器芯片770a、770b、770c及770d连接成一阵列。类似于上文所描述的存储器芯片,每个存储器芯片包括处理器子单元及专用存储器组。因此,此处不重复对这些组件的描述。

在图7C的实施例中,存储器芯片770a、770b、770c及770d连接成一回路。因此,总线750a连接存储器芯片770a与770d,总线750c连接存储器芯片770a与770b,总线750e连接存储器芯片770b与770c,且总线750g连接存储器芯片770c与770d。尽管存储器芯片770a、770b、770c及770d可利用完全块连接、部分块连接或其他连接布置来连接,但图7C的实施例允许存储器芯片770a、770b、770c及770d之间的更少接脚连接。

本公开的实施例可使用大小与常规处理器的共享存储器相比相对较大的专用存储器。使用专用存储器而非共享存储器允许继续获得效率增益而不会随着存储器增大而逐渐缩减。此允许诸如神经网络处理及数据库查询的存储器密集型任务比在常规处理器中更高效地执行,在常规处理器中,增大共享存储器的效率增益由于冯诺伊曼瓶颈而逐渐缩减。

例如,在本公开的分布式处理器中,安置于分布式处理器的基板上的存储器阵列可包括多个离散存储器组。离散存储器组中的每个可具有大于一兆字节(megabyte)的容量;以及安置于该基板上的处理阵列,该处理阵列包括多个处理器子单元。如上文所解释,该处理器子单元中的每个可与多个离散存储器组中的对应的专用存储器组相关联。在一些实施例中,多个处理器子单元可在空间上分布于存储器阵列内的多个离散存储器组当中。通过将至少一兆字节的专用存储器而非几兆字节的共享高速缓存用于大型CPU或GPU,本公开的分布式处理器获得在常规系统中由于CPU及GPU中的冯诺依曼瓶颈而不可能达成的效率。

不同存储器可用作专用存储器。例如,每一专用存储器组可包含至少一个DRAM组。替代地,每一专用存储器组可包含至少一个静态随机存取存储器组。在其他实施例中,不同类型的存储器可在单一硬件芯片上组合。

如上文所解释,每一专用存储器可为至少一兆字节。因此,每一专用存储器组可大小相同,或多个存储器组中的至少两个存储器组可具有不同大小。

此外,如上文所描述,该分布式处理器可包括:第一多个总线,其各将多个处理器子单元中的一个连接至一对应的专用存储器组;及第二多个总线,其各将多个处理器子单元中的一个连接至多个处理器子单元中的另一个。

如上文所解释,本公开的硬件芯片可使用软件而非硬件来管理数据传送。具体而言,因为总线上的传送、对存储器进行的读取及写入以及处理器子单元的计算的时序通过处理器子单元所执行的指令的子系列设定,所以本公开的硬件芯片可执行代码以防止总线上的冲突。因此,本公开的硬件芯片可避免常规地用以管理数据传送的硬件机构(诸如,芯片内的网络控制器、处理器子单元之间的封包剖析器及封包传送器、总线仲裁器、用以避免仲裁的多个总线,或其类似物)。

若本公开的硬件芯片常规地传送数据,则利用总线连接N个处理器子单元将需要由仲裁器控制的总线仲裁或宽MUX。反而,如上文所描述,本公开的实施例可在处理器子单元之间使用仅为导线、光学缆线或其类似物的总线,其中该处理器子单元个别地执行代码以避免总线上的冲突。因此,本公开的实施例可节省基板上的空间以及材料成本及效率损失(例如,由于仲裁导致的功率及时间消耗)。相较于使用先进先出(FIFO)控制器和/或信箱的其他架构,效率及空间增益甚至更大。

此外,如上文所解释,除一个或多个处理元件以外,每一处理器子单元也可包括一个或多个加速器。在一些实施例中,加速器可从总线而非从处理元件进行读取及写入。在这些实施例中,可通过允许加速器在处理元件执行一个或多个计算的相同循环期间传输数据来获得额外效率。然而,这些实施例需要用于加速器的额外材料。例如,可能需要额外晶体管以用于制造加速器。

代码也可考虑处理器子单元(例如,包括形成处理器子单元的部分的处理元件和/或加速器)的内部行为,包括时序及延时。例如,编译程序(如下文所描述)可执行当产生控制数据传送的指令子系列时考虑时序及延时的预处理。

在一个实施例中,多个处理器子单元可经指派计算神经网络层的任务,该神经网络层含有全部连接至较大多个神经元的前一层的多个神经元。假设前一层的数据均匀地散布在多个处理器子单元之间,执行该计算的一种方式可为配置每一处理器子单元,以依次将前一层的数据传输至主总线,且接着每一处理器子单元将此数据乘以子单元实施的对应神经元的权重。因为每一处理器子单元计算多于一个神经元,所以每一处理器子单元将数次传输前一层的数据,该次数等于神经元的数量。因此,每一处理器子单元的代码与用于其他处理器子单元的代码不相同,这是因为该子单元将在不同时间进行传输。

在一些实施例中,分布式处理器可包含基板(例如,诸如硅的半导体基板和/或诸如可挠性电路板的电路板),该基板具有:安置于该基板上的存储器阵列,该存储器阵列包括多个离散存储器组;及安置于该基板上的处理阵列,该处理阵列包括多个处理器子单元,如描绘于例如图7A及图7B中。如上文所解释,该处理器子单元中的每个可与多个离散存储器组中的对应的专用存储器组相关联。此外,如描绘于例如图7A及图7B中,分布式处理器还可包含多个总线,多个总线中的每个将多个处理器子单元中的一个连接至多个处理器子单元中的至少另一者。

如上文所解释,多个总线可用软件来控制。因此,多个总线可能不含时序硬件逻辑组件,使得在处理器子单元之间及跨越多个总线中的对应者的数据传送不受时序硬件逻辑组件控制。在一个实施例中,多个总线可能不含总线仲裁器,使得在处理器子单元之间及跨越多个总线中的对应者的数据传送不受总线仲裁器控制。

在一些实施例中,如描绘于例如图7A及图7B中,分布式处理器还可包含第二多个总线,该第二多个总线将多个处理器子单元中的一个连接至一对应的专用存储器组。类似于上文所描述的多个总线,第二多个总线可能不含时序硬件逻辑组件,使得处理器子单元与对应的专用存储器组之间的数据传送不受时序硬件逻辑组件控制。在一个实施例中,第二多个总线可能不含总线仲裁器,使得处理器子单元与对应的专用存储器组之间的数据传送不受总线仲裁器控制。

如本文中所使用,词组「不含」未必暗示诸如时序硬件逻辑组件(例如,总线仲裁器、仲裁树、FIFO控制器、信箱或其类似物)的组件的绝对不存在。这些组件仍可包括于描述为「不含」这些组件的硬件芯片中。反而,词组「不含」指硬件芯片的功能;也即,「不含」时序硬件逻辑组件的硬件芯片控制其数据传送的时序而不使用包括于其中的时序硬件逻辑组件(若存在)。例如,硬件芯片执行包括指令的子系列的代码,该指令控制该硬件芯片的处理器子单元之间的数据传送,即使该硬件芯片包括时序硬件逻辑组件作为防范由于所执行代码中的错误的冲突的辅助预防措施亦如此。

如上文所解释,多个总线可包含介于多个处理器子单元中的对应者之间的导线或光纤中的至少一个。因此,在一个实施例中,不含时序硬件逻辑组件的分布式处理器可仅包括导线或光纤,而无总线仲裁器、仲裁树、FIFO控制器、信箱或其类似物。

在一些实施例中,多个处理器子单元被配置为根据由多个处理器子单元执行的代码跨越多个总线中的至少一个传送数据。因此,如下文所解释,编译程序可组织指令的子系列,每一子系列包含由单处理器子单元执行的代码。该子系列指令可指示处理器子单元何时将数据传送至总线中的一个上及何时从总线取回数据。当该子系列以串接方式跨越分布式处理器执行时,处理器子单元之间的传送的时序可通过包括于该子系列中的用以传送及取回的指令来控制。因此,代码规定跨越多个总线中的至少一个的数据传送的时序。编译程序可产生要由单处理器子单元执行的代码。另外,编译程序可产生要由处理器子单元的群组执行的代码。在一些状况下,编译程序可将所有处理器子单元共同视为该处理器子单元系一个超处理器(例如,分布式处理器),且编译程序可产生用于由其定义的超处理器/分布式处理器执行的代码。

如上文所解释且如图7A及图7B中所描绘,多个处理器子单元可在空间上分布于存储器阵列内的多个离散存储器组当中。替代地,多个处理器子单元可聚集在基板的一个或多个区中,且多个存储器组可聚集在基板的一个或多个其他区中。在一些实施例中,可使用空间分布与聚集的组合,如上文所解释。

在一些实施例中,分布式处理器可包含基板(例如,包括硅的半导体基板和/或诸如可挠性电路板的电路板),该基板具有安置于其上的存储器阵列,该存储器阵列包括多个离散存储器组。处理阵列也可安置于基板上,该处理阵列包括多个处理器子单元,如描绘于例如图7A及图7B中。如上文所解释,该处理器子单元中的每个可与多个离散存储器组中的对应的专用存储器组相关联。此外,如描绘于例如图7A及图7B中,该分布式处理器还可包含多个总线,多个总线中的每个将多个处理器子单元中的一个连接至多个离散存储器组中的对应的专用存储器组。

如上文所解释,多个总线可用软件来控制。因此,多个总线可能不含时序硬件逻辑组件,使得处理器子单元与多个离散存储器组中的对应的专用离散存储器组之间及跨越多个总线中的对应者的数据传送不受时序硬件逻辑组件控制。在一个实施例中,多个总线可能不含总线仲裁器,使得在处理器子单元之间及跨越多个总线中的对应者的数据传送不受总线仲裁器控制。

在一些实施例中,如描绘于例如图7A及图7B中,分布式处理器还可包含第二多个总线,该第二多个总线将多个处理器子单元中的一个连接至多个处理器子单元中的至少另一者。类似于上文所描述的多个总线,第二多个总线可能不含时序硬件逻辑组件,使得处理器子单元与对应的专用存储器组之间的数据传送不受时序硬件逻辑组件控制。在一个实施例中,第二多个总线可能不含总线仲裁器,使得处理器子单元与对应的专用存储器组之间的数据传送不受总线仲裁器控制。

在一些实施例中,分布式处理器可使用软件时序组件与硬件时序组件的组合。例如,分布式处理器可包含基板(例如,包括硅的半导体基板和/或诸如可挠性电路板的电路板),该基板安置于其上的存储器阵列,该存储器阵列包括多个离散存储器组。处理阵列也可安置于基板上,该处理阵列包括多个处理器子单元,如描绘于例如图7A及图7B中。如上文所解释,该处理器子单元中的每个可与多个离散存储器组中的对应的专用存储器组相关联。此外,如描绘于例如图7A及图7B中,分布式处理器还可包含多个总线,多个总线中的每个将多个处理器子单元中的一个连接至多个处理器子单元中的至少另一者。此外,如上文所解释,多个处理器子单元可被配置为执行软件,该软件控制跨越多个总线的数据传送的时序,以避免与多个总线中的至少一个上的数据传送冲突。在此实施例中,软件可控制数据传送的时序,但传送本身可至少部分地由一个或多个硬件组件控制。

在这些实施例中,分布式处理器还可包含第二多个总线,该第二多个总线将多个处理器子单元中的一个连接至一对应的专用存储器组。类似于上文所描述的多个总线,多个处理器子单元可被配置为执行软件,该软件控制跨越该第二多个总线的数据传送的时序,以避免与该第二多个总线中的至少一个上的数据传送冲突。在此实施例中,如上文所解释,软件可控制数据传送的时序,但传送本身可至少部分地由一个或多个硬件组件控制。

如上文所解释,本公开的硬件芯片可跨越包括于形成硬件芯片的基板上的处理器子单元平行地执行代码。另外,本公开的硬件芯片可执行多任务处理。例如,本公开的硬件芯片可执行区域多任务处理,其中硬件芯片的处理器子单元的一个群组执行一个任务(例如,音频处理),而硬件芯片的处理器子单元的另一群组执行另一任务(例如,图像处理)。在另一实施例中,本公开的硬件芯片可执行时序多任务处理,其中硬件芯片的一个或多个处理器子单元在第一时间段期间执行一个任务且在第二时间段期间执行另一任务。也可使用区域多任务处理与时序多任务处理的组合,使得一个任务可在第一时间段期间指派给处理器子单元的第一群组,而另一任务可在第一时间段期间指派给处理器子单元的第二群组,此后,第三任务可在第二时间段期间指派给包括于第一群组及第二群组中的处理器子单元。

为了组织供在本公开的存储器芯片上执行的机器码,机器码可在存储器芯片的处理器子单元之间进行划分。例如,存储器芯片上的处理器可包含基板及安置于该基板上的多个处理器子单元。该存储器芯片还可包含安置于该基板上的对应的多个存储器组,多个处理器子单元中的每个连接至不被多个处理器子单元中的任何其他处理器子单元共享的至少一个专用存储器组。该存储器芯片上的每一处理器子单元可被配置为独立于其他处理器子单元执行一系列指令。每一系列指令可通过以下操作执行:根据定义该系列指令的代码而配置处理器子单元的一个或多个一般处理元件和/或根据在定义该系列指令的该代码中所提供的序列而启动处理器子单元的一个或多个特殊处理元件(例如,一个或多个加速器)。

因此,每一系列指令可定义要由单处理器子单元执行的一系列任务。单一任务可包含在由处理器子单元中的一个或多个处理元件的架构定义的指令集内的指令。例如,该处理器子单元可包括特定寄存器,且单一任务可将数据推送至寄存器上,从寄存器提取数据,对寄存器内的数据执行算术函数,对寄存器内的数据执行逻辑运算,或其类似物。此外,处理器子单元可针对任何数量的操作数来配置,诸如0操作数处理器子单元(也被称作「堆栈机」)、1操作数处理器子单元(也被称作累加机)、2操作数处理器子单元(诸如,RISC)、3操作数处理器子单元(诸如,复杂指令集计算机(CISC))或其类似物。在另一实施例中,处理器子单元可包括一个或多个加速器,且单一任务可启动一加速器以执行特定功能,诸如MAC功能、MAX功能、MAX-0功能或其类似物。

该系列指令还可以包括用于对存储器芯片的专用存储器组进行读取及写入的任务。例如,一任务可包括将一段数据写入至专用于执行该任务的处理器子单元的存储器组、从专用于执行该任务的处理器子单元的存储器组读取一段数据,或其类似物。在一些实施例中,读取及写入可由处理器子单元与存储器组的控制器串接地执行。例如,处理器子单元可通过将控制信号发送至控制器以执行读取或写入来执行读取或写入任务。在一些实施例中,该控制信号可包括用于读取及写入的特定地址。替代地,处理器子单元可听从存储器控制器以选择可用于读取及写入的地址。

另外或替代地,读取及写入可由一个或多个加速器与存储器组的控制器串接地执行。例如,该加速器可产生用于存储器控制器的控制信号,此类似于处理器子单元如何产生控制信号,如上文所描述。

在上文所描述的实施例中的任一者中,地址生成器也可用以引导对存储器组的特定地址的读取及写入。例如,该地址生成器可包含被配置为产生用于读取及写入的存储器地址的处理元件。该地址生成器可被配置为产生地址以便提高效率,例如通过将稍后计算的结果写入至与先前计算的不再需要的结果相同的地址。因此,地址生成器可响应于来自处理器子单元(例如,来自包括于其中的处理元件或来自其中的一个或多个加速器)的命令抑或与处理器子单元串接地产生用于存储器控制器的控制信号。另外或替代地,地址生成器可基于一些配置或寄存器产生地址,例如产生巢套循环结构,从而以某一图案在存储器中的某些地址上进行反复。

在一些实施例中,每一系列指令可包含定义对应的一系列任务的一组机器码。因此,上文所描述的该系列任务可囊封于包含该系列指令的机器码内。在一些实施例中,如下文关于图8所解释,该系列任务可由编译程序定义,该编译程序被配置为将较高阶系列的任务作为多个系列的任务分布于多个逻辑电路当中。例如,编译程序可基于较高阶系列的任务产生多个系列的任务,使得串接地执行对应的每一系列任务的处理器子单元执行与由较高阶系列的任务所概述的功能相同的功能。

如下文进一步所解释,较高阶系列的任务可包含用人类可读程序设计语言编写的一组指令。对应地,每一处理器子单元的该系列任务可包含较低阶系列任务,该任务中的每个包含以机器码编写的一组指令。

如上文关于图7A及图7B所解释,存储器芯片还可包含多个总线,每个总线将多个处理器子单元中的一个连接至多个处理器子单元中的至少另一者。此外,如上文所解释,多个总线上的数据传送可使用软件来控制。因此,跨越多个总线中的至少一个的数据传送可通过包括于连接至多个总线中的至少一个的处理器子单元中的该系列指令预定义。因此,包括于该系列指令中的任务中的一个可包括将数据输出至总线中的一个或从总线中的一个提取数据。这些任务可由处理器子单元的处理元件或由包括于处理器子单元中的一个或多个加速器执行。在后一实施例中,处理器子单元可执行计算或在相同循环中将控制信号发送至对应存储器组,在该循环期间,加速器从总线中的一个提取数据或将数据置放于总线中的一个上。

在一个实施例中,包括于连接至多个总线中的至少一个的处理器子单元中的该系列指令可包括发送任务,该发送任务包含针对连接至多个总线中的至少一个的处理器子单元的用以将数据写入至多个总线中的至少一个的命令。另外或替代地,包括于连接至多个总线中的至少一个的处理器子单元中的该系列指令可包括接收任务,该接收任务包含针对连接至多个总线中的至少一个的处理器子单元的用以从多个总线中的至少一个读取数据的命令。

除将代码分布在处理器子单元当中以外或替代将代码分布在处理器子单元当中,可在存储器芯片的存储器组之间划分数据。例如,如上文所解释,存储器芯片上的分布式处理器可包含安置于存储器芯片上的多个处理器子单元及安置于存储器芯片上的多个存储器组。多个存储器组中的每个可被配置为储存独立于储存在多个存储器组的其他者中的数据的数据,且多个处理器子单元中的一个可连接至多个存储器组当中的至少一个专用存储器组。例如,每一处理器子单元可存取专用于该处理器子单元的一个或多个对应存储器组的一个或多个存储器控制器,且其他处理器子单元不可存取这些对应的一个或多个存储器控制器。因此,储存于每个存储器组中的数据对于专用处理器子单元可为唯一的。此外,储存于每个存储器组中的数据可独立于储存在其他存储器组中的存储器,这是因为无存储器控制器可在存储器组之间共享。

在一些实施例中,如下文关于图8所描述,储存于多个存储器组中的每个中的数据可由编译程序定义,该编译程序被配置为将数据分布于多个存储器组当中。此外,该编译程序可被配置为使用分布于对应处理器子单元当中的多个较低阶任务将定义于较高阶系列的任务中的数据分布于多个存储器组当中。

如下文进一步所解释,较高阶系列的任务可包含用人类可读程序设计语言编写的一组指令。对应地,每一处理器子单元的该系列任务可包含较低阶系列任务,该任务中的每个包含以机器码编写的一组指令。

如上文关于图7A及图7B所解释,存储器芯片还可包含多个总线,每个总线将多个处理器子单元中的一个连接至多个存储器组当中的一个或多个对应的专用存储器组。此外,如上文所解释,多个总线上的数据传送可使用软件来控制。因此,跨越多个总线中的特定总线的数据传送可由连接至多个总线中的该特定总线的对应处理器子单元来控制。因此,包括于该系列指令中的任务中的一个可包括将数据输出至总线中的一个或从总线中的一个提取数据。如上文所解释,这些任务可由(i)处理器子单元的处理元件或(ii)包括于处理器子单元中的一个或多个加速器执行。在后一实施例中,处理器子单元可执行计算或在相同循环中使用将该处理器子单元连接至其他处理器子单元的总线,在该循环期间,加速器从连接至一个或多个对应的专用存储器组的总线中的一个提取数据或将数据置放于该总线中的一个上。

因此,在一个实施例中,包括于连接至多个总线中的至少一个的处理器子单元中的该系列指令可包括发送任务。该发送任务可包含针对连接至多个总线中的至少一个的处理器子单元的用以将数据写入至多个总线中的至少一个以供储存于一个或多个对应的专用存储器组中的命令。另外或替代地,包括于连接至多个总线中的至少一个的处理器子单元中的该系列指令可包括接收任务。该接收任务可包含针对连接至多个总线中的至少一个的处理器子单元的用以从多个总线中的至少一个读取数据以供储存于一个或多个对应的专用存储器组中的命令。因此,这些实施例中的发送任务及接收任务可包含控制信号,该控制信号沿着多个总线中的至少一个发送至一个或多个对应的专用存储器组中的一个或多个存储器控制器。此外,发送任务及接收任务可与由处理子单元的另一部分(例如,由处理子单元的一个或多个不同加速器)执行的计算或其他任务并发地由处理子单元的一个部分(例如,由处理子单元的一个或多个加速器)执行。此并发执行的实施例可包括MAC中继命令,其中接收、相乘及发送被串接地执行。

除将数据分布于存储器组当中以外,也可跨越不同存储器组复制数据的特定部分。例如,如上文所解释,存储器芯片上的分布式处理器可包含安置于存储器芯片上的多个处理器子单元及安置于存储器芯片上的多个存储器组。多个处理器子单元中的每个可连接至多个存储器组当中的至少一个专用存储器组,且多个存储器组中的每个存储器组可被配置为储存独立于储存在多个存储器组的其他者中的数据的数据。此外,储存于多个存储器组当中的一个特定存储器组中的数据中的至少一些可包含储存于多个存储器组中的至少另一存储器组中的数据的复制者。例如,该系列指令中所使用的数字、字符串或其他类型的数据可储存于专用于不同处理器子单元的多个存储器组中,而非从一个存储器组传送至存储器芯片中的其他处理器子单元。

在一个实施例中,平行字符串匹配可使用上文所描述的数据复制。例如,可将多个字符串与相同字符串进行比较。常规处理器可依序将多个字符串中的每一字符串与相同字符串进行比较。在本公开的硬件芯片上,可跨越存储器组复制相同字符串,使得处理器子单元可平行地将多个字符串中的分开字符串与所复制字符串进行比较。

在一些实施例中,如下文关于图8所描述,跨越多个存储器组当中的一个特定存储器组及多个存储器组中的至少另一存储器组复制的至少一些数据由编译程序定义,该编译程序被配置为跨越存储器组复制数据。此外,该编译程序可被配置为使用分布于对应处理器子单元当中的多个较低阶任务来复制至少一些数据。

数据的复制可适用于跨越不同计算重复使用数据的相同部分的特定任务。通过复制数据的这些部分,不同计算可分布于存储器芯片的处理器子单元当中以用于平行执行,而每一处理器子单元可将数据的该部分储存于专用存储器组中且从专用存储器组存取所储存部分(而非跨越连接处理器子单元的总线推送及提取数据的该部分)。在一个实施例中,跨越多个存储器组当中的一个特定存储器组及多个存储器组中的至少另一存储器组复制的至少一些数据可包含神经网络的权重。在此实施例中,该神经网络中的每一节点可由多个处理器子单元当中的至少一个处理器子单元定义。例如,每一节点可包含由定义该节点的至少一个处理器子单元执行的机器码。在此实施例中,权重的复制可允许每一处理器子单元执行机器码以至少部分地实现对应节点,同时仅存取一个或多个专用存储器组(而非与其他处理器子单元执行数据传送)。因为对专用存储器组进行的读取及写入的时序独立于其他处理器子单元,而处理器子单元之间的数据传送的时序需要时序同步(例如,使用软件,如上文所解释),所以复制存储器以避免处理器子单元之间的数据传送可进一步提高总体执行的效率。

如上文关于图7A及图7B所解释,存储器芯片还可包含多个总线,每个总线将多个处理器子单元中的一个连接至多个存储器组当中的一个或多个对应的专用存储器组。此外,如上文所解释,多个总线上的数据传送可使用软件来控制。因此,跨越多个总线中的特定总线的数据传送可由连接至所述多个总线中的该特定总线的对应处理器子单元来控制。因此,包括于该系列指令中的任务中的一个可包括将数据输出至总线中的一个或从总线中的一个提取数据。如上文所解释,这些任务可由(i)处理器子单元的处理元件或(ii)包括于处理器子单元中的一个或多个加速器执行。如上文进一步所解释,这些任务可包括包含控制信号的发送任务和/或接收任务,该控制信号沿着多个总线中的至少一个发送至一个或多个对应的专用存储器组中的一个或多个存储器控制器。

图8描绘用于编译一系列指令以供在例如如图7A及图7B中所描绘的本公开的示例性存储器芯片上执行的方法800的流程图。方法800可通过任何常规处理器(无论系通用抑或专用的)实施。

方法800可作为形成编译程序的计算机程序的一部分执行。如本文中所使用,「编译程序」指将较高级语言(例如,程序性语言,诸如C、FORTRAN、BASIC或其类似物;面向对象式语言,诸如Java、C++、Pascal、Python或其类似物;等等)转换成较低级语言(例如,组合代码、目标代码、机器码或其类似物)的任何计算机程序。编译程序可允许人类以人类可读语言来程序设计一系列指令,接着将该人类可读语言转换成机器可执行语言。

在步骤810处,处理器可将与该系列指令相关联的任务指派给处理器子单元中的不同处理器子单元。例如,该系列指令可分成子群组,该子群组要跨越处理器子单元平行地执行。在一个实施例中,可将神经网络分成其节点,且可将一个或多个节点指派给分开的处理器子单元。在此实施例中,每一子群组可包含跨越不同层连接的多个节点。因此,处理器子单元可实施来自神经网络的第一层的节点、来自连接至由相同处理器子单元实施的来自第一层的节点的第二层的节点,及类似节点。通过基于节点的连接来指派节点,可缩减处理器子单元之间的数据传送,此可导致效率提高,如上文所解释。

如上文图7A及图7B中所描绘而解释,处理器子单元可在空间上分布于安置于存储器芯片上的多个存储器组当中。因此,任务的指派可至少部分地为空间划分以及逻辑划分。

在步骤820处,处理器可产生用以在存储器芯片的成对的处理器子单元之间传送数据的任务,每一对处理器子单元由一总线连接。例如,如上文所解释,该数据传送可使用软件来控制。因此,处理器子单元可被配置为在同步时间将数据推送于总线上及提取总线上的数据。所产生的任务可因此包括用于执行数据的此同步推送及提取的任务。

如上文所解释,步骤820可包括预处理以考虑处理器子单元的内部行为,包括时序及延时。例如,处理器可使用处理器子单元的已知时间及延时(例如,将数据推送至总线的时间、从总线提取数据的时间、计算与推送或提取之间的延时,或其类似物)以确保所产生的任务同步。因此,包含由一个或多个处理器子单元进行的至少一次推送及由一个或多个处理器子单元进行的至少一次提取的数据传送可同时发生,而不会由于处理器子单元之间的时序差、处理器子单元的延时或其类似物而引起延迟。

在步骤830处,处理器可将所指派及产生的任务分组成子系列指令的多个群组。例如,该子系列指令可各包含供单处理器子单元执行的一系列任务。因此,子系列指令的多个群组中的每个可对应于多个处理器子单元中的不同处理器子单元。因此,步骤810、820及830可导致将该系列指令分成子系列指令的多个群组。如上文所解释,步骤820可确保不同群组之间的任何数据传送同步。

在步骤840处,处理器可产生对应于子系列指令的多个群组中的每个的机器码。例如,可将表示子系列指令的较高阶代码转换成可由对应处理器子单元执行的较低阶代码,诸如机器码。

在步骤850处,处理器可根据划分将对应于子系列指令的多个群组中的每个的所产生机器码指派给多个处理器子单元中的对应处理器子单元。例如,处理器可用对应处理器子单元的识别符来标记每一子系列指令。因此,当将子系列指令上传至存储器芯片以供执行(例如,由图3A的主机350)时,每一子系列可配置一正确的处理器子单元。

在一些实施例中,将与该系列指令相关联的任务指派给处理器子单元中的不同处理器子单元可至少部分地取决于存储器芯片上的处理器子单元中的两者或多于两者之间的空间接近性。例如,如上文所解释,可通过缩减处理器子单元之间的数据传送的数量来提高效率。因此,处理器可将跨越处理器子单元中的多于两者移动数据的数据传送减至最少。因此,处理器可结合一个或多个优化算法(诸如,贪婪算法)使用存储器芯片的已知布局,以便将子系列指派给处理器子单元,其指派方式使邻近传送达至最大(至少区域地)且使至非相邻处理器子单元的传送减至最少(至少区域地)。

方法800可包括针对本公开的存储器芯片的进一步优化。例如,处理器可基于划分将与该系列指令相关联的数据分组且根据该分组将数据指派给存储器组。因此,该存储器组可保存用于指派给每个存储器组所专用于的每一处理器子单元的子系列指令的数据。

在一些实施例中,将数据分组可包括判定在存储器组中的两者或多于两者中复制的数据的至少一部分。例如,如上文所解释,可跨越多于一个子系列指令使用一些数据。此数据可跨越专用于经指派不同子系列指令的多个处理器子单元的存储器组复制。此优化可进一步缩减跨越处理器子单元的数据传送。

可将方法800的输出输入至本公开的存储器芯片以供执行。例如,一存储器芯片可包含多个处理器子单元及对应的多个存储器组,每一处理器子单元连接至专用于该处理器子单元的至少一个存储器组,且该存储器芯片的该处理器子单元可被配置为执行由方法800产生的机器码。如上文关于图3A所解释,主机350可将由方法800产生的机器码输入至处理器子单元以供执行。

在常规存储器组中,控制器设置在组层级处。每一组包括多个垫,所述多个垫通常以矩形方式布置,但可按任何几何形状布置。每一垫包括多个存储器胞元,所述多个存储器胞元还通常以矩形方式布置,但可按任何几何形状布置。每一胞元可储存单一数据比特(例如,取决于该胞元保持在高电压抑或低电压下)。

此常规架构的实施例描绘于图9及图10中。如图9中所展示,在组层级处,多个垫(例如,垫930-1、930-2、940-1及940-2)可形成组900。在常规矩形组织中,可跨越全局字线(例如,字线950)及全局比特线(例如,比特线960)控制组900。因此,行解码器910可基于传入控制信号(例如,对从地址读取的请求、对写入至地址的请求或其类似物)选择正确字线,且全局感测放大器920(和/或全局列解码器,图9中未展示)可基于该控制信号选择正确比特线。放大器920也可在读取操作期间放大来自选定组的任何电压电平。尽管描绘为将行解码器用于初始选择且沿着列执行放大,但组可另外或替代地将列解码器用于初始选择且沿着行执行放大。

图10描绘垫1000的实施例。例如,垫1000可形成诸如图9的组900的存储器组的一部分。如图10中所描绘,多个胞元(例如,胞元1030-1、1030-2及1030-3)可形成垫1000。每一胞元可包含储存至少一个数据比特的电容器、晶体管或其他电路系统。例如,一胞元可包含电容器或可包含正反器(flip-flop),该电容器经充电以表示「1」且放电以表示「0」,该正反器具有表示「1」的第一状态及表示「0」的第二状态。常规垫可包含例如512个比特×512个比特。在垫1000形成MRAM、ReRAM或其类似物的一部分的实施例中,一胞元可包含晶体管、电阻器、电容器或用于隔离储存至少一个数据比特的材料的离子或一部分的其他机构。例如,一胞元可包含具有表示「1」的第一状态及表示「0」的第二状态的电解质离子、硫族化物玻璃的一部分,或其类似物。

如图10中进一步所描绘,在常规矩形组织中,可跨越区域字线(例如,字线1040)及区域比特线(例如,比特线1050)控制垫1000。因此,字线驱动器(例如,字线驱动器1020-1、1020-2、……、1020-x)可基于来自与存储器组(垫1000形成该存储器组的一部分)相关联的控制器的控制信号(例如,对从地址读取的请求、对写入至地址的请求、刷新信号)而控制选定字线以执行读取、写入或刷新。此外,区域感测放大器(例如,区域放大器1010-1、1010-2、……、1010-x)和/或区域列解码器(图10中未展示)可控制选定比特线以执行读取、写入或刷新。该区域感测放大器也可在读取操作期间放大来自选定胞元的任何电压电平。尽管描绘为将字线驱动器用于初始选择且沿着列执行放大,但垫可替代地将比特线驱动器用于初始选择且沿着行执行放大。

如上文所解释,复制大量垫以形成存储器组。可将存储器组群聚以形成存储器芯片。例如,存储器芯片可包含八个至三十二个存储器组。因此,使处理器子单元与常规存储器芯片上的存储器组配对可产生仅八个至三十二个处理器子单元。因此,本公开的实施例可包括具有额外子组阶层的存储器芯片。本公开的这些存储器芯片可接着包括具有用作与处理器子单元配对的专用存储器组的存储器子组的处理器子单元,以允许较大数量的子处理器,此可接着达成存储器内计算的较高平行性及效能。

在本公开的一些实施例中,组900的全局行解码器及全局感测放大器可用子组控制器来替换。因此,存储器组的控制器可将控制信号引导至适当的子组控制器,而非将控制信号发送至存储器组的全局行解码器及全局感测放大器。引导可动态地加以控制或可为硬联机的(例如,经由一个或多个逻辑门)。在一些实施例中,熔断器可用以指示每一子组或垫的控制器是否阻断控制信号或传递控制信号至适当的子组或垫。在这些实施例中,可因此使用熔断器来撤销启动故障子组。

在这些实施例中的一个实施例中,一存储器芯片可包括多个存储器组,每个存储器组具有一组控制器及多个存储器子组,每个存储器子组具有一子组行解码器及一子组列解码器以允许对该存储器子组上的位置进行读取及写入。每一子组可包含多个存储器垫,每个存储器垫具有多个存储器胞元且可具有在内部的区域行解码器、列解码器和/或区域感测放大器。该子组行解码器及该子组列解码器可处理用于子组存储器上的存储器内计算的来自组控制器或来自子组处理器子单元的读取及写入请求,如下文所描述。另外,每个存储器子组可进一步具有一控制器,该控制器被配置为判定处理来自组控制器的读取请求及写入请求和/或将读取请求及写入请求转送至下一层级(例如,垫上的行解码器及列解码器的下一层级),抑或阻断该请求,例如以允许内部处理元件或处理器子单元存取存储器。在一些实施例中,该组控制器可同步至系统时钟。然而,该子组控制器可不同步至系统时钟。

如上文所解释,子组的使用可允许在存储器芯片中包括比在处理器子单元与常规芯片的存储器组配对的情况下更大数量的处理器子单元。因此,每一子组可进一步具有使用子组作为专用存储器的处理器子单元。如上文所解释,该处理器子单元可包含RISC、CISC或其他通用处理子单元和/或可包含一个或多个加速器。另外,该处理器子单元可包括地址生成器,如上文所解释。在上文所描述的实施例中的任一者中,每一处理器子单元可被配置为使用专用于该处理器子单元的子组的行解码器及列解码器而不使用组控制器来存取该子组。与子组相关联的处理器子单元也可处置存储器垫(包括下文所描述的解码器及存储器冗余机构)和/或判定是否转送且因此处置来自上部层级(例如,组层级或存储器层级)的读取或写入请求。

在一些实施例中,子组控制器还可以包括储存子组的状态的寄存器。因此,在该寄存器指示该子组处于使用中时,若该子组控制器接收到来自存储器控制器的控制信号,则该子组控制器可传回错误。在每一子组还包括一处理器子单元的实施例中,若该子组中的该处理器子单元正存取与来自存储器控制器的外部请求冲突的存储器,则该寄存器可指示错误。

图11展示使用子组控制器的存储器组的另一实施例的实施例。在图11的实施例中,组1100具有行解码器1110、列解码器1120,及具有子组控制器(例如,控制器1130a、1130b及1130c)的多个存储器子组(例如,子组1170a、1170b及1170c)。该子组控制器可包括地址解算器(例如,解算器1140a、1140b及1140c),该地址解算器可判定是否将请求传递至由子组控制器控制的一个或多个子组。

该子组控制器还可以包括一个或多个逻辑电路(例如,逻辑1150a、1150b及1150c)。例如,包含一个或多个处理元件的逻辑电路可允许执行诸如刷新子组中的胞元、清除子组中的胞元或其类似物的一个或多个操作而无需来自组1100外部的处理请求。替代地,逻辑电路可包含处理器子单元,如上文所解释,使得处理器子单元具有由子组控制器控制的任何子组作为对应的专用存储器。在图11的实施例中,逻辑1150a可具有子组1170a作为对应的专用存储器,逻辑1150b可具有子组1170b作为对应的专用存储器,且逻辑1150c可具有子组1170c作为对应的专用存储器。在上文所描述的实施例中的任一者中,逻辑电路可具有至子组的总线,例如,总线1131a、1131b或1131c。如图11中进一步所描绘,该子组控制器可各包括多个解码器,诸如子组行解码器及子组列解码器,以允许处理元件或处理器子单元或发布命令的较高阶存储器控制器对存储器子组上的地址进行读取及写入。例如,子组控制器1130a包括解码器1160a、1160b及1160c,子组控制器1130b包括解码器1160d、1160e及1160f,且子组控制器1130c包括解码器1160g、1160h及1160i。基于来自组行解码器1110的请求,子组控制器可使用包括于子组控制器中的解码器来选择字线。所描述系统可允许子组的处理元件或处理器子单元在不中断其他组及甚至其他子组的情况下存取存储器,藉此允许每一子组处理器子单元与其他子组处理器子单元平行地执行存储器计算。

此外,每一子组可包含多个存储器垫,每个存储器垫具有多个存储器胞元。例如,子组1170a包括垫1190a-1、1190a-2、……、1190a-x;子组1170b包括垫1190b-1、1190b-2、……、1190b-x;且子组1170c包括垫1190c-1、1190c-2、……、1190c-3。如图11中进一步所描绘,每一子组可包括至少一个解码器。例如,子组1170a包括解码器1180a,子组1170b包括解码器1180b,且子组1170c包括解码器1180c。因此,组列解码器1120可基于外部请求而选择全局比特线(例如,比特线1121a或1121b),而由组行解码器1110选择的子组可使用其列解码器基于来自子组所专用于的逻辑电路的区域请求而选择区域比特线(例如,比特线1181a或1181b)。因此,每一处理器子单元可被配置为使用子组的行解码器及列解码器来存取专用于该处理器子单元的子组而无需使用组行解码器及组列解码器。因此,每一处理器子单元可存取对应子组而不会中断其他子组。此外,当对子组的请求在处理器子单元外时,子组解码器可向组解码器反映所存取的数据。替代地,在每一子组仅具有一行存储器垫的实施例中,区域比特线可为垫的比特线,而非子组的比特线。

可使用以下实施例的组合:使用子组行解码器及子组列解码器的实施例;及图11中所描绘的实施例。例如,可消除组行解码器,但保留组列解码器且使用区域比特线。

图12展示具有多个垫的存储器子组1200的实施例的实施例。例如,子组1200可表示图11的子组1100的一部分或可表示存储器组的替代实施。在图12的实施例中,子组1200包括多个垫(例如,垫1240a及1240b)。此外,每一垫可包括多个胞元。例如,垫1240a包括胞元1260a-1、1260a-2、……、1260a-x,且垫1240b包括胞元1260b-1、1260b-2、……、1260b-x。

每一垫可经指派将指派给垫的存储器胞元的地址的范围。这些地址可在生产时配置,使得垫可到处移动且使得故障垫可被撤销启动且保持未使用(例如,使用一个或多个熔断器,如下文进一步所解释)。

子组1200接收来自存储器控制器1210的读取及写入请求。尽管图12中未描绘,但来自存储器控制器1210的请求可经由子组1200的控制器来筛选且引导至子组1200的适当垫以进列地址解算。替代地,来自存储器控制器1210的请求的地址的至少一部分(例如,较高比特)可传输至子组1200的所有垫(例如,垫1240a及1240b),使得仅当垫的经指派地址范围包括命令中所指定的地址时,每一垫方可处理完整地址及与该地址相关联的请求。类似于上文所描述的子组引导,垫判定可动态地加以控制或可为硬联机的。在一些实施例中,熔断器可用以判定每一垫的地址范围,以还允许通过指派不合法地址范围来停用故障垫。垫可另外或替代地通过其他常用方法或熔断器的连接来停用。

在上文所描述的实施例中的任一者中,子组的每一垫可包括用于选择垫中的字线的行解码器(例如,行解码器1230a或1230b)。在一些实施例中,每一垫还可以包括熔断器及比较器(例如,1220a及1220b)。如上文所描述,比较器可允许每一垫判定是否处理传入请求,且熔断器可允许每一垫在发生故障的情况下撤销启动。替代地,可使用组和/或子组的行解码器,而非使用每一垫中的行解码器。

此外,在上文所描述的实施例中的任一者中,包括于适当垫中的列解码器(例如,列解码器1250a或1250b)可选择区域比特线(例如,比特线1251或1253)。区域比特线可连接至存储器组的全局比特线。在子组具有其自身的区域比特线的实施例中,胞元的区域比特线可进一步连接至子组的区域比特线。因此,可经由胞元的列解码器(和/或感测放大器)、接着经由子组的列解码器(和/或感测放大器)(在包括子组列解码器和/或感测放大器的实施例中)且接着经由组的列解码器(和/或感测放大器)来读取选定胞元中的数据。

垫1200可经复制及排成阵列以形成存储器组(或存储器子组)。例如,本公开的存储器芯片可包含多个存储器组,每个存储器组具有多个存储器子组,且每个存储器子组具有用于处理对存储器子组上的位置进行的读取及写入的子组控制器。此外,每个存储器子组可包含多个存储器垫,每个存储器垫具有多个存储器胞元且具有一垫行解码器及一垫列解码器(例如,如图12中所描绘)。该垫行解码器及该垫列解码器可处理来自子组控制器的读取及写入请求。例如,该垫解码器可接收所有请求且基于每一垫的已知地址范围判定(例如,使用比较器)是否处理请求,或该垫解码器可基于子组(或组)控制器对垫的选择而仅接收在已知地址范围内的请求。

除使用处理子单元来共享数据以外,本公开的存储器芯片中的任一者也可使用存储器控制器(或子组控制器或垫控制器)来共享数据。例如,本公开的存储器芯片可包含:多个存储器组(例如,SRAM组、DRAM组或其类似物),每个存储器组具有一组控制器、一行解码器及一列解码器,以允许对该存储器组上的位置进行读取及写入;以及多个总线,其将多个组控制器中的每一控制器连接至多个组控制器中的至少一个其他控制器。所述多个总线可类似于如上文所描述的连接处理子单元的总线,但所述多个总线直接地而非经由处理子单元来连接该组控制器。此外,尽管描述为连接组控制器,但总线可另外或替代地连接符组控制器和/或垫控制器。

在一些实施例中,可在不中断连接至一个或多个处理器子单元的存储器组的主总线上的数据传送的情况下存取所述多个总线。因此,存储器组(或子组)可在与将数据传输至不同存储器组(或子组)或从不同存储器组(或子组)传输数据相同的时钟循环中将数据传输至对应处理器子单元或从对应处理器子单元传输数据。在每一控制器连接至多个其他控制器的实施例中,该控制器可能可配置以用于选择其他控制器中的另一个用于发送或接收数据。在一些实施例中,每一控制器可连接至至少一个相邻控制器(例如,空间邻近控制器对可彼此连接)。

本公开大体上系有关于具有用于芯片上数据处理的主要逻辑部分的存储器芯片。该存储器芯片可包括冗余逻辑部分,该冗余逻辑部分可替换有缺陷的主要逻辑部分以提高芯片的制造良率。因此,该芯片可包括片上组件,该片上组件允许基于对该逻辑部分的个别测试来配置存储器芯片中的逻辑区块。该芯片的此特征可提高良率,这是因为具有专用于逻辑部分的较大面积的存储器芯片更容易发生制造故障。例如,具有大冗余逻辑部分的DRAM存储器芯片可容易发生制造问题,此降低良率。然而,实施冗余逻辑部分可导致提高良率及可靠性,这是因为该实施使DRAM存储器芯片的制造商或使用者能够在维持高平行性的同时接通或断开全部逻辑部分。应注意,在此处及贯穿本公开,可识别某些存储器类型(诸如,DRAM)的实施例,以便促进解释所公开实施例。然而,应理解,在这些情况下,识别的存储器类型并不意欲为限制性的。确切而言,诸如DRAM、快闪存储器、SRAM、ReRAM、PRAM、MRAM、ROM或任何其他存储器的存储器类型可与所公开实施例共同使用,即使在本公开的某一章节中特定地识别较少实施例亦如此。

图13为符合所公开实施例的示例性存储器芯片1300的功能方块图。存储器芯片1300可实施为DRAM存储器芯片。存储器芯片1300也可实施为任何类型之易失性或非易失性存储器,诸如快闪存储器、SRAM、ReRAM、PRAM和/或MRAM等。存储器芯片1300可包括基板1301,该基板中布置有地址管理器1302、包括多个存储器组1304(a,a)至1304(z,z)的存储器阵列1304、存储器逻辑1306、商业逻辑1308及冗余商业逻辑1310。存储器逻辑1306及商业逻辑1308可构成主要逻辑区块,而冗余商业逻辑1310可构成冗余区块。此外,存储器芯片1300可包括配置开关,该配置开关可包括撤销启动开关1312及启动开关1314。撤销启动开关1312及启动开关1314也可安置于基板1301中。在本申请案中,存储器逻辑1306、商业逻辑1308及冗余商业逻辑1310也可统称为「逻辑区块」。

地址管理器1302可包括行和列解码器或其他类型的存储器辅助设备。替代地或另外,地址管理器1302可包括微控制器或处理单元。

在一些实施例中,如图13中所展示,存储器芯片1300可包括单一存储器阵列1304,该存储器阵列可将多个存储器区块以二维阵列布置在基板1301上。然而,在其他实施例中,存储器芯片1300可包括多个存储器阵列1304,且存储器阵列1304中的每个可按不同配置布置存储器区块。例如,存储器阵列中的至少一个中的存储器区块(也被称为存储器组)可按径向分布配置以促进地址管理器1302或存储器逻辑1306至存储器区块之间的路由。

商业逻辑1308可用以进行与用以管理存储器本身的逻辑无关的应用程序的存储器内计算。例如,商业逻辑1308可实施与AI相关的功能,诸如用作启动功能的浮点、整数或MAC运算。此外,商业逻辑1308可实施数据库相关功能,如最小值、最大值、排序、计数以及其他。存储器逻辑1306可执行与存储器管理相关的任务,包括(但不限于)读取、写入及刷新操作。因此,可在组层级、垫层级或垫群组层级中的一个或多个中添加商业逻辑。商业逻辑1308可具有一个或多个地址输出及一个或多个数据输入/输出。例如,商业逻辑1308可通过至地址管理器1302的行\列线来寻址。然而,在某些实施例中,逻辑区块可另外或替代地经由数据输入\输出来寻址。

冗余商业逻辑1310可为商业逻辑1308的再制品。此外,冗余商业逻辑1310可连接至撤销启动开关1312和/或启动开关1314,其可包括小的熔断器\反熔断器,且用于逻辑停用或启用实例中的一个(例如,预设连接的实例)且启用其他逻辑区块中的一个(例如,预设断开的实例)。在一些实施例中,如关于图15进一步所描述,区块的冗余在诸如商业逻辑1308的逻辑区块内可为区域的。

在一些实施例中,存储器芯片1300中的逻辑区块可通过专用总线连接至存储器阵列1304的子集。例如,存储器逻辑1306、商业逻辑1308及冗余商业逻辑1310的集合可连接至存储器阵列1304中的第一行存储器区块(也即,存储器区块1304(a,a)至1304(a,z))。专用总线可允许相关联逻辑区块快速地存取存储器区块的数据,而不要求经由例如地址管理器1302开放通信线。

多个主要逻辑区块中的每个可连接至多个存储器组1304中的至少一个。另外,诸如冗余商业区块1310的冗余区块可连接至存储器实例1304(a,a)至1304(z,z)中的至少一个。冗余区块可再制多个主要逻辑区块中的至少一个,诸如存储器逻辑1306或商业逻辑1308。撤销启动开关1312可连接至所述多个主要逻辑区块中的至少一个,且启动开关1314可连接至所述多个冗余区块中的至少一个。

在这些实施例中,在侦测到与多个主要逻辑区块中的一个(存储器逻辑1306和/或商业逻辑1308)相关联的故障后,撤销启动开关1312可被配置为停用多个主要逻辑区块中的该者。同时,启动开关1314可被配置为启用多个冗余区块中的再制多个主要逻辑区块中的一个的冗余区块,诸如冗余逻辑区块1310。

此外,可统称为「配置开关」的启动开关1314及撤销启动开关1312可包括用以配置开关的状态的外部输入。例如,启动开关1314可被配置为使得外部输入中的启动信号产生闭合开关条件,而撤销启动开关1312可被配置为使得外部输入中的撤销启动信号产生断开开关条件。在一些实施例中,1300中的所有配置开关可默认为撤销启动,且在测试指示相关联逻辑区块起作用且信号施加于外部输入中之后变得被启动或启用。替代地,在一些状况下,1300中的所有配置开关可默认为经启用,且可在测试指示相关联逻辑区块不起作用且撤销启动信号施加于外部输入中之后被撤销启动或停用。

无关于最初启用抑或停用配置开关,在侦测到与相关联逻辑区块相关联的故障后,配置开关可停用相关联逻辑区块。在最初启用配置开关的状况下,配置开关的状态可改变至停用,以便停用相关联逻辑区块。在最初停用配置开关的状况下,配置开关的状态可保持在其停用状态中,以便停用相关联逻辑区块。例如,可操作性测试的结果可指示,某一逻辑区块不操作或该逻辑区块不能在某些规格内操作。在这些状况下,可停用逻辑区块,可能不启用其对应配置开关。

在一些实施例中,配置开关可连接至两个或多于两个逻辑区块,且可被配置为在不同逻辑区块之间进行选择。例如,配置开关可连接至商业逻辑区块1308及冗余逻辑区块1310两者。配置开关可启用冗余逻辑区块1310,同时停用商业逻辑1308。

替代地或另外,多个主要逻辑区块中的至少一个(存储器逻辑1306和/或商业逻辑1308)可通过第一专用连接件连接至多个存储器组或存储器实例1304的子集。接着,多个冗余区块中的再制多个主要逻辑区块中的至少一个的至少一个冗余区块(诸如,冗余商业逻辑1310)可通过第二专用连接件连接至相同多个存储器组或实例1304的子集。

此外,存储器逻辑1306可具有不同于商业逻辑1308的功能及能力。例如,虽然存储器逻辑1306可经设计以实现存储器组1304中的读取及写入操作,但商业逻辑1308可经设计以执行存储器内计算。因此,若商业逻辑1308包括第一商业逻辑区块且商业逻辑1308包括第二商业逻辑区块(如冗余商业逻辑1310),则有可能将有缺陷的商业逻辑1308断开且重新连接冗余商业逻辑1310使得不会失去任何能力。

在一些实施例中,配置开关(包括撤销启动开关1312及启动开关1314)可用熔断器、反熔断器或可编程设备(包括可一次性可编程设备)或其他形式的非易失性存储器来实施。

图14为符合所公开实施例的示例性冗余逻辑区块集合1400的功能方块图。在一些实施例中,冗余逻辑区块集合1400可安置于基板1301中。冗余逻辑区块集合1400可包括分别连接至开关1312及1314的商业逻辑1308及冗余商业逻辑1310中的至少一个。此外,商业逻辑1308及冗余商业逻辑1310可连接至地址总线1402及数据总线1404。

在一些实施例中,如图14中所展示,开关1312及1314可将逻辑区块连接至时钟节点。以此方式,配置开关可将逻辑区块与时钟信号接合或脱离,以有效地启动或撤销启动逻辑区块。然而,在其他实施例中,开关1312及1314可将逻辑区块连接至其他节点以用于启动或撤销启动。例如,配置开关可将逻辑区块连接至电压供应节点(例如,VCC)或连接至接地节点(例如,GND)或时钟信号。以此方式,逻辑区块可由配置开关启用或停用,这是因为该配置开关可产生开路或截断逻辑区块供电。

在一些实施例中,如图14中所展示,地址总线1402及数据总线1404可在逻辑区块的相对侧中,该逻辑区块并联地连接至该总线中的每个。以此方式,可通过逻辑区块集合1400促进不同片上组件的路由。

在一些实施例中,多个撤销启动开关1312中的每个将多个主要逻辑区块中的至少一个与时钟节点耦接,且多个启动开关1314中的每个可将多个冗余区块中的至少一个与时钟节点耦接,以允许连接\断开时钟以作为简单的启动\撤销启动机制。

冗余逻辑区块集合1400的冗余商业逻辑1310允许设计者基于面积及路由而选择值得复制的区块。例如,芯片设计者可选择较大区块进行复制,这是因为较大区块可更容易出错。因此,芯片设计者可决定复制大的逻辑区块。另一方面,设计者可偏好复制较小逻辑区块,这是因为较小逻辑区块容易复制而无显着的空间损失。此外,使用图14中的配置,设计者可容易取决于每个区域的错误的统计数据来选择复制逻辑区块。

图15为符合所公开实施例的示例性逻辑区块1500的功能方块图。该逻辑区块可为商业逻辑1308和/或冗余商业逻辑1310。然而,在其他实施例中,示例性逻辑区块可描述存储器逻辑1306或存储器芯片1300的其他组件。

逻辑区块1500呈现在小型处理器管线内使用逻辑冗余的又一实施例。逻辑区块1500可包括寄存器1508、取得电路1504、解码器1506及写回电路1518。此外,逻辑区块1500可包括计算单元1510及复制计算单元1512。然而,在其他实施例中,逻辑区块1500可包括其他单元,该其他单元不包含控制器管线,但包括包含所需商业逻辑的分散的处理元件。

计算单元1510及复制计算单元1512可包括能够执行数字计算的数字电路。例如,计算单元1510及复制计算单元1512可包括算术逻辑单元(ALU)以对二进制数执行算术及逐比特操作。替代地,计算单元1510及复制计算单元1512可包括对浮点数进行操作的浮点单元(FPU)。此外,在一些实施例中,计算单元1510及复制计算单元1512可实施数据库相关功能,如最小值、最大值、计数及比较操作以及其他。

在一些实施例中,如图15中所展示,计算单元1510及复制计算单元1512可连接至开关电路1514及1516。当经启动时,该开关电路可启用或停用该计算单元。

在逻辑区块1500中,复制计算单元1512可再制计算单元1510。此外,在一些实施例中,寄存器1508、取得电路1504、解码器1506及写回电路1518(统称为区域逻辑单元)的大小可小于计算单元1510。因为较大元件更容易在制造期间出现问题,所以设计者可决定复制较大单元(诸如,计算单元1510)而非复制较小单元(诸如,区域逻辑单元)。然而,取决于历史良率及错误率,除复制大单元(或整个区块)以外或替代复制大单元(或整个区块),设计者也可选择复制区域逻辑单元。例如,计算单元1510可比寄存器1508、取得电路1504、解码器1506及写回电路1518大,且因此更容易出错。设计者可选择复制计算单元1510而非复制逻辑区块1500中的其他元件或整个区块。

逻辑区块1500可包括多个区域配置开关,所述多个区域配置开关中的每个连接至计算单元1510或复制计算单元1512中的至少一个中的至少一者。当侦测到计算单元1510中的故障时,区域配置开关可被配置为停用计算单元1510且启用复制计算单元1512。

图16展示符合所公开实施例的与总线连接的示例性逻辑区块的功能方块图。在一些实施例中,逻辑区块1602(其可表示存储器逻辑1306、商业逻辑1308或冗余商业逻辑1310)可彼此独立,可经由总线连接,且可通过特定地寻址该逻辑区块而在外部启动。例如,存储器芯片1300可包括许多逻辑区块,每个逻辑区块具有一ID号。然而,在其他实施例中,逻辑区块1602可表示由存储器逻辑1306、商业逻辑1308或冗余商业逻辑1310中的若干个(一个或多个)构成的较大单元。

在一些实施例中,逻辑区块1602中的每个可与其他逻辑区块1602冗余。所有区块可作为主要或冗余区块来操作的此完全冗余性可改良制造良率,这是因为设计者可断开故障单元同时维持整个芯片的功能性。例如,设计者可能够停用容易出错但维持类似计算能力的逻辑区域,这是因为所有复制区块可连接至相同的地址总线及数据总线。例如,逻辑区块1602的初始数量可大于目标容量。因而,停用一些逻辑区块1602将不会影响目标容量。

连接至逻辑区块的总线可包括地址总线1614、命令线1616及数据线1618。如图16中所展示,逻辑区块中的每个可独立于总线中的每一线而连接。然而,在某些实施例中,逻辑区块1602可按阶层式结构连接以促进路由。例如,总线中的每一线可连接至将该线路由至不同逻辑区块1602的多任务器。

在一些实施例中,为了在不知晓内部芯片结构(其可能由于启用及停用单元而改变)的情况下允许外部存取,逻辑区块中的每个可包括熔断ID,诸如熔断标识1604。熔断标识1604可包括判定ID的开关(如熔断器)的阵列,且可连接至管理电路。例如,熔断标识1604可连接至地址管理器1302。替代地,熔断标识1604可连接至较高存储器地址单元。在这些实施例中,熔断标识1604可能可配置以用于特定地址。例如,熔断标识1604可包括可编程的非易失性设备,其基于从管理电路接收到的指令而判定最终ID。

存储器芯片上的分布式处理器可设计成具有图16中所描绘的配置。在芯片唤醒时或在工厂测试时执行为BIST的测试程序可将运行ID号指派给通过测试协议的多个主要逻辑区块(存储器逻辑1306及商业逻辑1308)中的区块。测试程序也可将不合法ID号指派给未通过测试协议的多个主要逻辑区块中的区块。测试程序也可将运行ID号指派给通过测试协议的多个冗余区块中的区块(冗余逻辑区块1310)。因为冗余区块替换发生故障的主要逻辑区块,所以经指派运行ID号的多个冗余区块中的区块可等于或大于经指派不合法ID号的多个主要逻辑区块中的区块,藉此停用区块。此外,多个主要逻辑区块中的每个及多个冗余区块中的每个可包括至少一个熔断标识1604。另外,如图16中所展示,连接逻辑区块1602的总线可包括命令线、数据线及地址线。

然而,在其他实施例中,连接至总线的所有逻辑区块1602将开始被停用且不具有ID号。逐个地测试,每一良好逻辑区块将得到运行ID号,且不工作的这些逻辑区块将保留不合法ID,此将停用这些区块。以此方式,冗余逻辑区块可通过替换在测试处理程序期间已知有缺陷的区块来改良制造良率。

地址总线1614可将管理电路耦接至多个存储器组中的每个、多个主要逻辑区块中的每个及多个冗余区块中的每个。这些连接允许管理电路在侦测到与主要逻辑区块(诸如,商业逻辑1308)相关联的故障后将无效地址指派给多个主要逻辑区块中的一个且将有效地址指派给多个冗余区块中的一个。

例如,如图16A中所展示,不合法ID被配置至所有逻辑区块1602(a)至1602(c)(例如,地址0xFFF)。在测试之后,逻辑区块1602(a)及1602(c)经验证为起作用,而逻辑区块1602(b)不起作用。在图16A中,无阴影逻辑区块可表示成功地通过功能性测试的逻辑区块,而阴影逻辑区块可表示未通过功能性测试的逻辑区块。因而,测试程序针对起作用的逻辑区块将不合法ID改变为合法ID,而为不作用的逻辑区块保留不合法ID。作为一实施例,在图16A中,逻辑区块1602(a)及1602(c)的地址从0xFFF分别改变为0x001及0x002。相比之下,逻辑区块1602(b)的地址仍为不合法地址0xFFF。在一些实施例中,ID通过编程对应熔断标识1604来改变。

来自逻辑区块1602的测试的不同结果可产生不同配置。例如,如图16B中所展示,地址管理器1302最初可将不合法ID指派给所有逻辑区块1602(也即,0xFFF)。然而,测试结果可指示两个逻辑区块1602(a)及1602(b)起作用。在这些状况下,对逻辑区块1602(c)的测试可能并非必要的,这是因为存储器芯片1300可能仅需要两个逻辑区块。因此,为了将测试资源减至最少,可仅根据1300的产品定义所需的起作用逻辑区块的最小数量来测试逻辑区块,以使其他逻辑区块未经测试。图16B还展示表示通过功能性测试的经测试逻辑区块的无阴影逻辑区块及表示未测试逻辑区块的阴影逻辑区块。

在这些实施例中,在起动时执行BIST的生产测试器(外部或内部的,自动或人工的)或控制器可针对起作用的经测试逻辑区块将不合法ID改变为运行ID,而为未测试逻辑区块保留不合法ID。作为一实施例,在图16B中,逻辑区块1602(a)及1602(b)的地址从0xFFF分别改变为0x001及0x002。相比之下,未测试逻辑区块1602(c)的地址仍为不合法地址0xFFF。

图17为符合所公开实施例的串联连接的示例性单元1702及1712的功能方块图。图17可表示整个系统或芯片。替代地,图17可表示含有其他起作用区块的芯片中的区块。

单元1702及1712可表示包括诸如存储器逻辑1306和/或商业逻辑1308的多个逻辑区块的完整单元。在这些实施例中,单元1702及1712也可包括执行操作所需的元件,诸如地址管理器1302。然而,在其他实施例中,单元1702及1712可表示诸如商业逻辑1308或冗余商业逻辑1310的逻辑单元。

图17呈现单元1702及1712可能需要在其本身之间通信的实施例。在此类状况下,单元1702及1712可串联连接。然而,非工作单元可破坏逻辑区块之间的连续性。因此,当单元由于缺陷而需要被停用时,单元之间的连接可包括旁路选项。该旁路选项也可为旁路单元本身的部分。

在图17中,单元可串联连接(例如,1702(a)至1702(c)),且发生故障的单元(例如,1702(b))可在其有缺陷时被绕过。该单元可进一步与开关电路并联地连接。例如,在一些实施例中,单元1702及1712可与开关电路1722及1728连接,如图17中所描绘。在图17中所描绘的实施例中,单元1702(b)有缺陷。例如,单元1702(b)未通过电路功能性测试。因此,可使用例如启动开关1314(图17中未展示)来停用单元1702(b),和/或可启动开关电路1722(b)以绕过单元1702(b)且维持逻辑区块之间的连接性。

因此,当多个主要单元串联连接时,所述多个单元中的每个可与一并联开关并联地连接。在侦测到与多个单元中的一个相关联的故障后,可启动连接至所述多个单元中的该者的并联开关以连接所述多个单元中的两者。

在其他实施例中,如图17中所展示,开关电路1728可包括将致使一个或多个循环延迟的一或更多个取样点,以维持单元的不同线之间的同步。当停用一单元时,邻近逻辑区块之间的连接的短路可能会产生与其他计算的同步误差。例如,若一任务需要来自A线及B线两者的数据,且A及B中的每个系由独立的一系列单元承载,则停用一单元将导致将需要进一步数据管理的线之间的去同步。为了防止去同步,样本电路1730可仿真由经停用单元1712(b)引起的延迟。然而,在一些实施例中,并联开关可包括反熔断器而非取样电路1730。

图18为符合所公开实施例的成二维阵列连接的示例性单元的功能方块图。图18可表示整个系统或芯片。替代地,图18可表示含有其他起作用区块的芯片中的区块。

单元1806可表示包括诸如存储器逻辑1306和/或商业逻辑1308的多个逻辑区块的自主单元。然而,在其他实施例中,单元1806可表示诸如商业逻辑1308的逻辑单元。在方便时,图18的论述可参考图13(例如,存储器芯片1300)中所识别且上文所论述的元件。

如图18中所展示,单元可布置成二维阵列,其中单元1806(其可包括或表示存储器逻辑1306、商业逻辑1308或冗余商业逻辑1310中的一个或多个)经由开关箱1808及连接箱1810互连。此外,为了控制二维阵列的配置,二维阵列可在二维阵列的周边中包括I/O区块1804。

连接箱1810可为可编程且可重配置的设备,其可对从I/O区块1804输入的信号作出响应。例如,连接箱可包括来自单元1806的多个输入接脚且也可连接至开关箱1808。替代地,连接箱1810可包括将可编程逻辑胞元的接脚与路由轨线连接的开关的群组,而开关箱1808可包括连接不同轨线的开关的群组。

在某些实施例中,连接箱1810及开关箱1808可通过诸如开关1312及1314的配置开关实施。在这些实施例中,连接箱1810及开关箱1808可由生产测试器或在芯片起动时所执行的BIST来配置。

在一些实施例中,连接箱1810及开关箱1808可在测试单元1806的电路功能性之后进行配置。在这些实施例中,I/O区块1804可用以将测试信号发送至单元1806。取决于测试结果,I/O区块1804可发送编程信号,该编程信号以停用未通过测试协议的单元1806且启用通过测试协议的单元1806的方式来配置连接箱1810及开关箱1808。

在这些实施例中,多个主要逻辑区块及多个冗余区块可成二维栅格安置于基板上。因此,多个主要单元1806中的每个及多个冗余区块中的每个(诸如,冗余商业逻辑1310)可用开关箱1808互连,且输入区块可安置于二维栅格的每一线及每一列的周边中。

图19为符合所公开实施例的处于复杂连接中的示例性单元的功能方块图。图19可表示整个系统。替代地,图19可表示含有其他起作用区块的芯片中的区块。

图19的复杂连接包括单元1902(a)至1902(f)及配置开关1904(a)至1904(f)。单元1902可表示包括诸如存储器逻辑1306和/或商业逻辑1308的多个逻辑区块的自主单元。然而,在其他实施例中,单元1902可表示诸如存储器逻辑1306、商业逻辑1308或冗余商业逻辑1310的逻辑单元。配置开关1904可包括撤销启动开关1312及启动开关1314中的任一者。

如图19中所展示,该复杂连接可包括两个平面中的单元1902。例如,复杂连接可包括在z轴上分开的两个独立基板。替代地或另外,单元1902可布置在基板的两个表面中。例如,出于缩减存储器芯片1300的面积的目的,基板1301可布置在两个重叠表面中且与在三维上布置的配置开关1904连接。配置开关可包括撤销启动开关1312和/或启动开关1314。

基板的第一平面可包括「主」单元1902。这些区块可预设为经启用。在这些实施例中,第二平面可包括「冗余」单元1902。这些单元可默认为经停用。

在一些实施例中,配置开关1904可包括反熔断器。因此,在测试单元1902之后,区块可通过将某些反熔断器切换至「始终接通」及停用选定单元1902来连接于起作用单元的块中,即使该单元在不同平面中亦如此。在图19中所呈现的实施例中,「主」单元中的一个(单元1902(e))不工作。图19可将不起作用区块或未测试区块表示为阴影区块,而经测试或起作用区块可为无阴影的。因此,配置开关1904被配置为使得不同平面中的逻辑区块中的一个(例如,单元1902(f))变为作用中。以此方式,即使主逻辑区块中的一个有缺陷,存储器芯片仍通过替换备用逻辑单元而工作。

图19另外展示不测试或启用第二平面中的单元1902中的一个(也即,1902(c)),这是因为主逻辑区块起作用。例如,在图19中,两个主单元1902(a)及1902(d)通过功能性测试。因此,单元1902(c)未被测试或启用。因此,图19展示特定地选择取决于测试结果而变为在作用中的逻辑区块的能力。

在一些实施例中,如图19中所展示,并非第一平面中的所有单元1902均可具有对应的备用或冗余区块。然而,在其他实施例中,所有单元可彼此冗余以实现完全冗余,其中所有单元均为主要或冗余的。此外,虽然一些实施可遵循图19中所描绘的星形网络拓朴,但其他实施可使用并联连接、串联连接和/或将不同元件与配置开关并联地或串联地耦接。

图20为说明符合所公开实施例的冗余区块启用处理程序2000的示例性流程图。可针对存储器芯片1300且特别地针对DRAM存储器芯片实施启用处理程序2000。在一些实施例中,处理程序2000可包括以下步骤:测试存储器芯片的基板上的多个逻辑区块中的每个的至少一个电路功能性;基于测试结果识别多个主要逻辑区块中的故障逻辑区块;测试存储器芯片的基板上的至少一个冗余或额外逻辑区块的至少一个电路功能性;通过将外部信号施加至撤销启动开关来停用至少一个故障逻辑区块;及通过将该外部信号施加至启动开关来启用该至少一个冗余区块,该启动开关与该至少一个冗余区块连接且安置于该存储器芯片的该基板上。以下图20的描述进一步详述处理程序2000的每一步骤。

处理程序2000可包括测试诸如商业区块1308的多个逻辑区块(步骤2002)及多个冗余区块(例如,冗余商业区块1310)。测试可在封装之前使用例如用于晶圆上测试的探测站进行。然而,步骤2000也可在封装之后执行。

步骤2002中的测试可包括将有限序列的测试信号施加至存储器芯片1300中的每个逻辑区块或存储器芯片1300中的逻辑区块的子集。该测试信号可包括请求预期得到0或1的计算。在其他实施例中,测试信号可请求读取存储器组中的特定地址或写入特定存储器组中。

可在步骤2002中实施测试技术以测试逻辑区块在反复处理程序下的响应。例如,该测试可涉及通过传输将数据写入存储器组中的指令及接着验证写入数据的完整性来测试逻辑区块。在一些实施例中,该测试可包括利用反转数据重复算法。

在替代实施例中,步骤2002的测试可包括运行逻辑区块的模型以基于一组测试指令产生目标存储器图像。接着,可对存储器芯片中的逻辑区块执行相同序列的指令,且可记录结果。模拟的残余存储器图像也可与自测试获得的图像进行比较,且任何失配可标示为故障。

替代地,在步骤2002中,该测试可包括阴影模型化,在阴影模型化中会产生诊断,但未必预测结果。反而,使用阴影模型化的测试可对存储器芯片及模拟两者平行地执行。例如,当存储器芯片中的逻辑区块完成指令或任务时,仿真可经发信以执行相同指令。一旦存储器芯片中的逻辑区块完成该指令,便可将两个模型的架构状态进行比较。若存在失配,则标示故障。

在一些实施例中,可在步骤2002中测试所有逻辑区块(包括例如存储器逻辑1306、商业逻辑1308或冗余商业逻辑1310中的每个)。然而,在其他实施例中,可在不同测试回合中仅测试逻辑区块的子集。例如,在第一测试回合中,可仅测试存储器逻辑1306及相关联区块。在第二回合中,可仅测试商业逻辑1308及相关联区块。在第三回合中,取决于前两个回合的结果,可测试与冗余商业逻辑1310相关联的逻辑区块。

处理程序2000可继续至步骤2004。在步骤2004中,可识别故障逻辑区块,且也可识别故障冗余区块。例如,未通过步骤2002的测试的逻辑区块可在步骤2004中识别为故障区块。然而,在其他实施例中,最初仅可识别某些故障逻辑区块。例如,在一些实施例中,仅可识别与商业逻辑1308相关联的逻辑区块,且仅在需要故障冗余区块以替代故障逻辑区块的情况下识别故障冗余区块。此外,识别故障区块可包括在存储器组或非易失性存储器上写入经识别故障区块的标识信息。

在步骤2006中,可停用故障逻辑区块。例如,使用配置电路,可通过将故障逻辑区块与时钟、接地和/或电源节点断开来停用故障逻辑区块。替代地,可通过以避开逻辑区块的布置来配置连接箱来停用故障逻辑区块。另外,在其他实施例中,可通过从地址管理器1302接收不合法地址来停用故障逻辑区块。

在步骤2008中,可识别复制故障逻辑区块的冗余区块。即使一些逻辑区块已发生故障,为了支持存储器芯片的相同能力,在步骤2008中,可识别可用且可复制故障逻辑区块的冗余区块。例如,若执行向量的乘法的逻辑区块经判定为发生故障,则在步骤2008中,地址管理器1302或片上控制器可识别还执行向量的乘法的可用冗余逻辑区块。

在步骤2010中,可启用在步骤2008中所识别的冗余区块。与步骤2006的停用操作相比,在步骤2010中,可通过将经识别冗余区块连接至时钟、接地和/或电源节点来启用该经识别冗余区块。替代地,可通过以连接经识别冗余区块的布置来配置连接箱来启用经识别冗余区块。另外,在其他实施例中,可通过在测试程序运行时间接收运列地址来启用经识别冗余区块。

图21为说明符合所公开实施例的地址指派处理程序2100的示例性流程图。可针对存储器芯片1300且特别地针对DRAM存储器芯片实施地址指派处理程序2100。如关于图16所描述,在一些实施例中,存储器芯片1300中的逻辑区块可连接至数据总线且具有地址标识。处理程序2100描述地址指派方法,该地址指派方法停用故障逻辑区块且启用通过测试的逻辑区块。处理程序2100中所描述的步骤将描述为由生产测试器或在芯片起动时所执行的BIST执行;然而,存储器芯片1300的其他组件和/或外部设备也可执行处理程序2100的一个或多个步骤。

在步骤2102中,测试器可通过在芯片层级将不合法标识指派给每个逻辑区块来停用所有逻辑区块及冗余区块。

在步骤2104中,测试器可执行逻辑区块的测试协议。例如,测试器可针对存储器芯片1300中的逻辑区块中的一个或多个执行步骤2002中所描述的测试方法。

在步骤2106中,取决于步骤2104中的测试的结果,测试器可判定逻辑区块是否有缺陷。若逻辑区块无缺陷(步骤2106:否),则地址管理器可在步骤2108中将运行ID指派给经测试逻辑区块。若逻辑区块有缺陷(步骤2106:是),则地址管理器1302可在步骤2110中为有缺陷逻辑区块保留不合法ID。

在步骤2112中,地址管理器1302可选择复制有缺陷逻辑区块的冗余逻辑区块。在一些实施例中,复制有缺陷逻辑区块的冗余逻辑区块可具有与有缺陷逻辑区块相同的组件及连接。然而,在其他实施例中,冗余逻辑区块可具有不同于有缺陷逻辑区块的组件和/或连接,但能够执行等效操作。例如,若有缺陷逻辑区块经设计以执行向量的乘法,则选定冗余逻辑区块将能够执行向量的乘法,即使选定冗余逻辑区块不具有与有缺陷单元相同的架构亦如此。

在步骤2114中,地址管理器1302可测试冗余区块。例如,测试器可将步骤2104中应用的测试技术应用于经识别冗余区块。

在步骤2116中,基于步骤2114中的测试的结果,测试器可判定冗余区块是否有缺陷。在步骤2118中,若冗余区块无缺陷(步骤2116:否),则测试器可将运行ID指派给经识别冗余区块。在一些实施例中,处理程序2100可在步骤2118之后返回至步骤2104,以产生测试存储器芯片中的所有逻辑区块的反复循环。

若测试器判定冗余区块有缺陷(步骤2116:是),则在步骤2120中,测试器可判定额外冗余区块是否可用。例如,测试器可向存储器组查询关于可用冗余逻辑区块的信息。若冗余逻辑区块可用(步骤2120:是),则测试器可返回至步骤2112且识别再制有缺陷逻辑区块的新的冗余逻辑区块。若冗余逻辑区块不可用(步骤2120:否),则在步骤2122中,测试器可产生错误信号。该错误信号可包括有缺陷逻辑区块及有缺陷冗余区块的信息。

本公开所公开的实施例还包括分布式高效能处理器。该处理器可包括介接存储器组及处理单元的存储器控制器。该处理器可能可配置以加快将数据递送至处理单元以用于计算。例如,若处理单元需要两个数据例项以执行任务,则存储器控制器可被配置为使得通信线独立地提供对来自两个数据例项的信息的存取。所公开的存储器架构试图将与复杂高速缓存及复杂寄存器档案方案相关联的硬件要求降至最低。通常,处理器芯片包括允许核心直接与寄存器一起工作的高速缓存阶层。然而,高速缓存操作需要相当大的晶粒面积且消耗额外功率。所公开的存储器架构通过在存储器中添加逻辑组件来避免使用高速缓存阶层。

所公开架构还实现数据在存储器组中的策略性(或甚至优化)置放。即使存储器组具有单一端口及高延时,所公开的存储器架构也可通过将数据策略性地定位于存储器组的不同区块中来实现高效能及避免存储器存取瓶颈。以将数据的连续串流提供至处理单元为目标,编译优化步骤可针对特定或一般任务判定数据应如何储存于存储器组中。接着,介接处理单元及存储器组的存储器控制器可被配置为在特定处理单元需要数据以执行操作时向该特定处理单元授权存取。

存储器芯片的配置可由处理单元(例如,配置管理者)或外部接口执行。该配置也可由编译程序或其他SW工具写入。此外,存储器控制器的配置可基于存储器组中的可用端口及存储器组中的数据的组织。因此,所公开架构可向处理单元提供来自不同存储器区块的恒定数据流或同时信息。以此方式,存储器内的计算任务可通过避免延时瓶颈或高速缓存要求来快速地处理。

此外,储存于存储器芯片中的数据可基于编译优化步骤进行布置。编译可允许建置处理程序,其中处理器将任务高效地指派给处理单元而无存储器延时相关联的延迟。该编译可由编译程序执行且被传输至连接至基板中的外部接口的主机。通常,某些存取图案的高延时和/或少量端口将导致需要数据的处理单元的数据瓶颈。然而,所公开编译可按使得处理单元能够甚至在不利存储器类型的情况下仍连续地接收数据的方式将数据定位于存储器组中。

此外,在一些实施例中,配置管理器可基于任务所需的计算向所需处理单元发信。芯片中的不同处理单元或逻辑区块可具有针对不同任务的专门硬件或架构。因此,取决于将执行的任务,可选择处理单元或处理单元群组来执行任务。基板上的存储器控制器可能可配置以根据处理子单元的选择来投送数据或授权存取,以改良数据传输速度。例如,基于编译优化及存储器架构,当需要处理单元以执行任务时,可授权该处理单元对存储器组的存取。

此外,芯片架构可包括片上组件,该片上组件通过缩减存取存储器组中的数据所需的时间来促进数据的传送。因此,本公开描述用于能够使用简单的存储器实例执行特定或一般任务的高效能处理器的芯片架构连同编译优化步骤。存储器实例可具有高的随机存取延时和/或少量端口,诸如DRAM设备或其他存储器定向技术中所使用的这些存储器实例,但所公开架构可通过实现从存储器组至处理单元的连续(或几乎连续)数据流来克服这些缺点。

在本申请案中,同时通信可指一时钟循环内的通信。替代地,同时通信可指在预定时间量内发送信息。例如,同时通信可指在几奈秒内的通信。

图22提供符合所公开实施例的示例性处理设备的功能方块图。图22A展示处理设备2200的第一实施例,其中存储器控制器2210使用多任务器连接第一存储器区块2202及第二存储器区块2204。存储器控制器2210也可连接至少一配置管理器2212、一逻辑区块2214及多个加速器2216(a)至2216(n)。图22B展示处理设备2200的第二实施例,其中存储器控制器2210使用总线连接存储器区块2202及2204,该总线连接存储器控制器2210与至少一配置管理器2212、一逻辑区块2214及多个加速器2216(a)至2216(n)。此外,主机2230可在处理设备2200外部且经由例如外部接口连接至处理设备。

存储器区块2202及2204可包括DRAM垫或垫群组、DRAM组、MRAM\PRAM\RERAM\SRAM单元、快闪存储器垫或其他存储器技术。存储器区块2202及2204可替代地包括非易失性存储器、快闪存储器设备、电阻式随机存取存储器(ReRAM)设备或磁阻式随机存取存储器(MRAM)设备。

存储器区块2202及2204可另外包括多个存储器胞元,所述多个存储器胞元在多条字线(未示出)与多条比特线(未示出)之间布置成行和列。每一行存储器胞元的栅极可连接至多条字线中的各别者。每一列存储器胞元可连接至多条比特线中的各别者。

在其他实施例中,存储器区域(包括存储器区块2202及2204)由简单的存储器实例建置。在本申请案中,术语「存储器实例」可与术语「存储器区块」互换使用。存储器实例(或区块)可具有不良特性。例如,存储器可为仅单端口存储器且可具有高随机存取延时。替代地或另外,存储器在列及线改变期间可能无法存取且面临与例如电容充电和/或电路系统设置相关的数据存取问题。然而,通过允许存储器实例与处理单元之间的专用连接及以考虑区块的特性的某一方式来布置数据,图22中所呈现的架构仍促进存储器设备中的平行处理。

在一些设备架构中,存储器实例可包括若干端口,以促进平行操作。然而,在这些实施例中,当数据基于芯片架构来编译及组织时,芯片仍可达成改良效能。例如,编译程序可通过提供指令及组织数据置放来改良存储器区域中的存取的效率,因此即使使用单端口存储器,仍能够容易存取存储器区域。

此外,存储器区块2202及2204可为单一芯片中的存储器的多个类型。例如,存储器区块2202及2204可为eFlash及eDRAM。另外,存储器区块可包括具有ROM实例的DRAM。

存储器控制器2210可包括用以处置存储器存取及将结果传回至模块的其余部分的逻辑电路。例如,存储器控制器2210可包括地址管理器及诸如多任务器的选择设备,以在存储器区块与处理单元之间投送数据或授权对存储器区块的存取。替代地,存储器控制器2210可包括用以驱动DDR SDRAM的双数据速率(DDR)存储器控制器,其中数据在系统的存储器时钟的上升边缘及下降边缘上传送。

此外,存储器控制器2210可构成双通道存储器控制器。双通道存储器的并入可促进存储器控制器2210对平行存取线的控制。该平行存取线可被配置为具有相同长度,以在结合使用多个线时促进数据同步。替代地或另外,该平行存取线可允许存取存储器组的多个存储器端口。

在一些实施例中,处理设备2200可包括可连接至处理单元的一个或多个多任务器。该处理单元可包括可直接至多任务器的配置管理器2212、逻辑区块2214及加速器2216。另外,存储器控制器2210可包括来自多个存储器组或区块2202及2204的至少一个数据输入端,及连接至多个处理单元中的每个的至少一个数据输出端。通过此配置,存储器控制器2210可经由两个数据输入端同时从存储器组或存储器区块2202及2204接收数据,且经由两个数据输出端同时将经由接收的数据传输至至少一个选定处理单元。然而,在一些实施例中,至少一个数据输入端及至少一个数据输出端可实施于单一端口中,以允许仅读取或写入操作。在这些实施例中,单一端口可实施为包括数据线、地址线及命令线的数据总线。

存储器控制器2210可连接至多个存储器区块2202及2204中的每个,且也可经由例如选择开关连接至处理单元。基板上的处理单元(包括配置管理器2212、逻辑区块2214及加速器2216)也可独立地连接至存储器控制器2210。在一些实施例中,配置管理器2212可接收要执行的任务的指示,且作为响应,根据储存于存储器中或从外部供应的配置而配置存储器控制器2210、加速器2216和/或逻辑区块2214。替代地,存储器控制器2210可由外部接口配置。该任务可能需要可用以从多个处理单元选择至少一个选定处理单元的至少一次计算。替代地或另外,该选择可至少部分地基于选定处理单元执行至少一次计算的能力。作为响应,存储器控制器2210可授权对存储器组的存取,或使用专用总线和/或以管线式存储器存取在至少一个选定处理单元与至少两个存储器组之间投送数据。

在一些实施例中,至少两个存储器区块中的第一存储器区块2202可布置在多个处理单元的第一侧上;且至少两个存储器组中的第二存储器组2204可布置在所述多个处理单元的与该第一侧相对的第二侧上。另外,用以执行任务的选定处理单元(例如,加速器2216(n))可被配置为在至第一存储器组或第一存储器区块2202的通信线开放的时钟循环期间存取第二存储器组2204。替代地,该选定处理单元可被配置为在至第一存储器区块2202的通信线开放的时钟循环期间将数据传送至第二存储器区块2204。

在一些实施例中,存储器控制器2210可实施为独立元件,如图22中所展示。然而,在其他实施例中,存储器控制器2210可嵌入于存储器区域中或可沿着加速器2216(a)至2216(n)安置。

处理设备2200中的处理区域可包括配置管理器2212、逻辑区块2214及加速器2216(a)至2216(n)。加速器2216可包括具有预定义功能的多个处理电路且可由特定应用程序定义。例如,加速器可为处置模块之间的存储器移动的向量乘法累加(MAC)单元或直接存储器存取(DMA)单元。加速器2216也可能够计算其自身地址且向存储器控制器2210请求数据或将数据写入至存储器控制器。例如,配置管理器2212可向加速器2216中的至少一个发信该加速器可存取存储器组。接着,加速器2216可配置存储器控制器2210以投送数据或向加速器本身授权存取。此外,加速器2216可包括至少一个算术逻辑单元、至少一个向量处置逻辑单元、至少一个字符串比较逻辑单元、至少一个寄存器及至少一个直接存储器存取件。

配置管理器2212可包括用以配置加速器2216及指示任务的执行的数字处理电路。例如,配置管理器2212可连接至存储器控制器2210及多个加速器2216中的每个。配置管理器2212可具有其自身的专用存储器以保存加速器2216的配置。配置管理器2212可使用存储器组以经由存储器控制器2210取得命令及配置。替代地,配置管理器2212可经由外部接口来编程。在某些实施例中,配置管理器2212可用具有自身的高速缓存阶层的片上精简指令集计算机(RISC)或片上复杂CPU来实施。在一些实施例中,也可省略配置管理器2212,且加速器可经由外部接口来配置。

处理设备2200也可包括外部接口(未示出)。该外部接口允许从上部层级(此存储器组控制器,其接收来自外部主机2230或片上主处理器的命令)对存储器进行存取,或从外部主机2230或片上主处理器对存储器进行存取。该外部接口可通过经由存储器控制器2210将配置或代码写入至存储器以供配置管理器2212或单元2214及2216本身稍后使用来允许对配置管理器2212及加速器2216进行编程。然而,该外部接口也可直接编程处理单元而不经由存储器控制器2210进行路由。在配置管理器2212为微控制器的状况下,配置管理器2212可允许经由外部接口将代码从主存储器加载至控制器区域存储器。存储器控制器2210可被配置为响应于接收到来自外部接口的请求而中断任务。

该外部接口可包括与逻辑电路相关联的多个连接器,该连接器提供至处理设备上的多种元件的无胶合接口。该外部接口可包括:用于数据读取的数据I/O输入端及用于数据写入的输出端;外部地址输出端;外部CE0芯片选择接脚;低有效芯片选择器;字节启用接脚;用于存储器循环的等待状态的接脚;写入启用接脚;输出启用有效接脚;及读取写入启用接脚。因此,该外部接口具有所需输入端及输出端以控制处理程序且从处理设备获得信息。例如,该外部接口可符合JEDEC DDR标准。替代地或另外,外部接口可符合其他标准,诸如SPI\OSPI或UART。

在一些实施例中,该外部接口可安置于芯片基板上且可连接外部主机2230。外部主机可经由外部接口存取存储器区块2202及2204、存储器控制器2210以及处理单元。替代地或另外,外部主机2230可对存储器进行读取及写入,或可经由读取及写入命令向配置管理器2212发信以执行操作,诸如开始处理程序和/或停止处理程序。此外,外部主机2230可直接配置加速器2216。在一些实施例中,外部主机2230能够直接对存储器区块2202及2204执行读取/写入操作。

在一些实施例中,配置管理器2212及加速器2216可被配置为取决于目标任务而使用直接总线来连接设备区域与存储器区域。例如,当加速器2216的子集能够执行任务执行所需的计算时,加速器的该子集可与存储器实例2204连接。通过进行此分开,有可能确保专用加速器获得存储器区块2202及2204所需的带宽(BW)。此外,具有专用总线的此配置可允许将大存储器分裂成较小实例或区块,这是因为将存储器实例连接至存储器控制器2210允许甚至在具有高行延时时间的情况下也可快速存取不同存储器中的数据。为达成连接的平行化,存储器控制器2210可用数据总线、地址总线和/或控制总线连接至存储器实例中的每个。

存储器控制器2210的上述包括可消除对处理设备中的高速缓存阶层或复杂寄存器档案的要求。尽管可添加高速缓存阶层以得到添加的能力,但处理设备处理设备2200中的架构可允许设计者基于处理操作而添加足够存储器区块或实例且在无高速缓存阶层的情况下相应地管理该实例。例如,处理设备处理设备2200中的架构可通过实施管线式存储器存取来消除对高速缓存阶层的需求。在管线式存储器存取中,处理单元可在某些数据线可开放(或启动)而其他数据线接收或传输数据的每个循环中接收持续数据流。使用独立通信线的持续数据流可能由于线改变而实现改良的执行速度及最小延时。

此外,图22中的所公开架构实现管线式存储器存取,有可能将数据组织在少量存储器区块中且节省由线切换造成的功率损耗。例如,在一些实施例中,编译程序可向主机2230传达数据在存储器组中的组织或用以将数据组织在存储器组中的方法,以促进在给定任务期间存取数据。接着,配置管理器2212可定义哪些存储器组且在一些状况下存储器组的哪些端口可由加速器存取。存储器组中的数据的位置与数据访问方法之间的此同步通过以最小延时将数据馈入至加速器来改良计算任务。例如,在配置管理器2212包括RISC\CPU的实施例中,该方法可用脱机软件(SW)来实施,且接着配置管理器2212可经编程以执行该方法。该方法可用可由RISC/CPU计算机执行的任何语言来开发且可在任何平台上执行。该方法的输入可包括存储器控制器后方的存储器的配置及数据本身,连同存储器存取的图案。此外,该方法可用特定于实施例的语言或机器语言来实施,且也可仅为以二进制或文字表示的一系列配置值。

如上文所论述,在一些实施例中,编译程序可将指令提供至主机2230以用于在准备管线式存储器存取时将数据组织在存储器区块2202及2204中。该管线式存储器存取通常可包括以下步骤:接收多个存储器组或存储器区块2202及2204的多个地址;根据所接收的地址使用独立数据线存取所述多个存储器组;经由第一通信线将来自第一地址的数据供应至多个处理单元中的至少一个且开放至第二地址的第二通信线,该第一地址在所述多个存储器组中的第一存储器组中,该第二地址在所述多个存储器组中的第二存储器组2204中;及在第二时钟循环内,经由该第二通信线将来自该第二地址的数据供应至所述多个处理单元中的该至少一者且开放至第一线中的第一存储器组中的第三地址的第三通信线。在一些实施例中,该管线式存储器存取可在两个存储器区块连接至单一端口的情况下执行。在这些实施例中,存储器控制器2210可将两个存储器区块隐藏在单一端口后,但利用管线式存储器访问方法将数据传输至处理单元。

在一些实施例中,编译程序可在主机2230上执行,之后执行任务。在这些实施例中,编译程序可能够基于存储器设备的架构而判定数据流的配置,这是因为该配置将为编译程序已知的。

在其他实施例中,若存储器区块2204及2202的配置在脱机时间系未知的,则管线式方法可在主机2230上执行,该主机可在开始计算之前将数据布置在存储器区块中。例如,主机2230可将数据直接写入存储器区块2204及2202中。在这些实施例中,诸如配置管理器2212及存储器控制器2210的处理单元在运行时间之前可能不会具有关于所需硬件的信息。接着,可能有必要延迟对加速器2216的选择,直至任务开始运行。在这些情形中,处理单元或存储器控制器2210可随机地选择加速器2216且产生测试数据存取图案,该存取图案可在执行任务时加以修改。