或非型闪存器件及其制造方法

文献发布时间:2023-06-19 11:57:35

技术领域

本发明涉及集成电路制造领域,特别涉及一种或非型闪存器件及其制 造方法。

背景技术

或非(NOR)型闪存(Flash)器件是基于Intel公司提出的ETOX结构发展 而来的,是一种非易失性存储器,即芯片断电后仍能保存存储器件的内部 信息。或非型闪存器件作为一种非易失性存储器具有高密度、低价格和电 可编程、擦除的特点,被广泛应用到便携式电子产品中,如手机、数码相 机、智能卡等。

在或非型闪存器件的工艺技术中,随着非易失性闪存技术对应的节点 缩小,或非型闪存器件上存储单元区的深宽比(AR aspect ratio)也在不断 变大,65nm的或非型闪存器件上存储单元区的深宽比小于1.2,55nm以及 50nm的或非型闪存器件上存储单元区的深宽比已经大于1.4,参阅图1, 图1是55nm技术节点下或非型闪存器件上存储单元区的结构示意图,从 图1中可以看出,存储单元区包括多个栅极01,其中存在两个栅极01之 间的深宽比大于1.4,高的深宽比对栅极01间的层间介质的填充造成了很 大的困难。同时,随着非易失性闪存技术对应的节点缩小,或非型闪存器 件上的外围器件区的侧墙太薄,参阅图2,图2是现有的或非型闪存器件 上外围器件区的结构示意图,从图2中可以看出,外围器件区包括一个栅 极,外围器件区的侧墙02太薄在高压操作时会发生击穿或产生热载流子效 应(HCI hot carrier injection)等威胁或非型闪存器件可靠性的风险。

或非型闪存器件中存储单元区与外围器件区的结构由具体的工艺决 定,参阅图3a~3i,图3a~3i是现有工艺中各个工艺阶段中存储单元区与外 围器件区的结构示意图,从图3a~3i中可以看出,现有的或非型闪存器件 器件的制造方法一般包括如下步骤:

S1:提供一包括存储单元区和外围器件区的晶圆片,所述存储单元区 和所述外围器件区自下而上依次包括硅衬底11、氧化物层12、浮栅层13、 栅间介质层14,去除所述外围器件区上的栅间介质层14和浮栅层13,在 所述晶圆片上沉积一多晶硅层15,参阅图3a;

S2:将所述存储单元区的多晶硅层15减薄,参阅图3b;

S3:在所述晶圆片上形成所述存储单元区的栅极21和所述外围器件区 的栅极22,参阅图3c;

S4:对所述晶圆片进行第一次侧墙沉积与第一次侧墙蚀刻,以使所述 存储单元区的栅极的侧壁外围形成第一侧墙23以及所述外围器件区的栅 极的侧壁外围形成第一侧墙24,所述存储单元区的第一侧墙23和所述外 围器件区的第一侧墙24均为氧化物层16-氮化物层17-氧化物层18的结构, 参阅图3d;

S5:对所述存储单元区的所述栅极21之间硅衬底11以及所述外围器 件区的所述栅极22两边的硅衬底11进行轻浅掺杂离子注入,参阅图3e;

S6:对所述晶圆片进行第二次侧墙沉积与第二次侧墙蚀刻,以使所述 存储单元区的所述第一侧墙23外围以及所述外围器件区的所述第一侧墙 24外围形成由氮化物层组成的第二侧墙25,参阅图3f;

S7:对所述外围器件区的栅极22两边的硅衬底11进行源漏极离子注 入,参阅图3g;

S8:对所述晶圆片进行酸洗,去除所述第二侧墙25,参阅图3h;

S9:在所述存储单元区的栅极21的顶部和所述外围器件区的栅极22 的顶部以及硅衬底11被注入离子的部分形成金属硅化物27,参阅图3i。

当所述或非型闪存器件的技术节点小于55nm的时候,上述步骤S1~S9 中,步骤S8中的酸洗会对步骤S4中形成的第一侧墙的底部造成侵蚀,即 第一侧墙底部的氮化物损失,使得在步骤S9中形成的所述金属硅化物的可 能伸入到所述第一侧墙被侵蚀的部位,造成均匀性变差,有潜在漏电和干 扰失效的风险;且完成上述步骤后,所述存储单元区的栅极间的层间介质 的填充会由于所述存储单元区的深宽比过高而变得困难。

因此,如何对现有的或非型闪存器件的制造工艺进行改善,以使得在 技术节点变小的同时,避免存储单元区的深宽比过高对后续层间介质填充 造成困难,增大所述外围器件区的侧墙厚度以保证足够的击穿电压,以及 提高产品均匀性,进而提高或非型闪存器件的可靠性是目前亟需解决的问 题。

发明内容

本发明的目的在于提供一种或非型闪存器件及其制作方法,使得在技 术节点变小的同时,避免存储单元区的深宽比过高对后续层间介质填充造 成困难,增大所述外围器件区的侧墙厚度以保证足够的击穿电压,以及提 高产品均匀性,进而提高或非型闪存器件的可靠性。

为实现上述目的,本发明提供了一种或非型闪存器件的制造方法,包 括:

S1:提供一包括存储单元区和外围器件区的晶圆片,去除外围器件区 上的栅间介质层和浮栅层,在所述晶圆片上沉积一多晶硅层,然后再在多 晶硅层上沉积一氮化物层;

S2:蚀刻去除存储单元区的氮化物层和一定厚度的多晶硅层;

S3:在所述晶圆片上形成所述存储单元区的栅极和所述外围器件区的 栅极;

S4:对所述晶圆片进行第一次侧墙沉积与第一次侧墙蚀刻,以使所述 存储单元区的栅极和所述外围器件区的栅极的侧壁上形成第一侧墙,所述 第一侧墙为氧化物层-氮化物层-氧化物层的结构;

S5:对所述存储单元区的所述栅极之间的硅衬底以及所述外围器件区 的所述栅极的两边的硅衬底进行轻浅掺杂离子注入;

S6:对所述晶圆片进行第二次侧墙沉积与第二次侧墙蚀刻,以使所述 存储单元区的栅极和所述外围器件区的栅极的所述第一侧墙外围形成由氧 化物层组成的第二侧墙;

S7:去除所述外围器件区的栅极顶部的氮化物层以及第一侧墙中的一 部分氮化物层,去除所述存储单元区的第一侧墙中的一部分氮化物层;

S8:蚀刻去除所述存储单元区的栅极外围的一部分氧化物层,以及所 述外围器件区的栅极外围的一部分氧化物层;

S9:对所述外围器件区的栅极两边的硅衬底进行源漏极离子注入;

S10:在所述存储单元区的栅极的顶部和所述外围器件区的栅极的顶部 以及硅衬底中被注入离子的部分形成金属硅化物层。

可选的,所述栅间介质层为氧化物-氮化物-氧化物结构。

可选的,所述S1中,采用蚀刻去除所述外围器件区上的栅间介质层和 浮栅层。

可选的,所述S3中具体包括:通过光刻定义出所述存储单元区的栅极 图形,通过蚀刻产生所述存储单元区的所述栅极;通过光刻定义出所述外 围器件区的栅极图形,通过蚀刻产生所述外围器件区的所述栅极。

可选的,所述S8中,所述存储单元区的所述栅极和所述外围器件区的 所述栅极的外围的氧化物层被蚀刻至与所述栅极外围的氮化物层同一高 度。

可选的,所述源漏极离子注入与所述轻浅掺杂离子注入相比,源漏极 离子注入进所述硅衬底的剂量更大、深度更深。

可选的,所述的氧化物为氧化硅,所述的氮化物为氮化硅。

本发明还提供了一种或非型闪存器件,采用本发明提供的所述或非型 闪存器件的制造方法形成。

可选的,所述或非型闪存器件包括存储单元区和外围器件区,所述存 储单元区和所述外围器件区设置于一硅衬底上;

所述存储单元区包括栅极,部分所述存储单元区的所述栅极之间的硅 衬底上设置有有源区,所述存储单元区的所述栅极的顶部和所述有源区覆 盖有一层金属硅化物,所述存储单元区的所述栅极的侧壁上设置有侧墙;

所述外围器件区包括栅极,所述外围器件区的所述栅极的两边分别设 置有源极和漏极,所述外围器件区的所述栅极的顶部和所述源极以及所述 漏极覆盖设置有一层金属硅化物,所述外围器件区的所述栅极的侧壁上设 置有侧墙

与现有技术相比,本发明的技术方案具有以下有益效果:

1、本发明的或非型闪存器件的制造方法,通过在多晶硅上沉积一氮化 物层,并采用氧化物作为第二次侧墙沉积的材料,使得外围器件区的栅极 的侧墙厚度得到提高,且使得存储单元区的深宽比得到降低,同时由氧化 物组成的第二侧墙保护了第一侧墙底部的氮化物,提高了产品的均匀性, 进而使得或非型闪存器件的可靠性得到提高。

2、本发明的或非型闪存器件,由于采用本发明提供的所述或非型闪存 器件的制造方法,使得外围器件区的栅极的侧墙厚度得到提高,且使得存 储单元区的深宽比得到降低,同时由氧化物组成的第二侧墙保护了第一侧 墙底部的氮化物,提高了产品的均匀性,进而使得或非型闪存器件的可靠 性得到提高。

附图说明

图1是现有的或非型闪存器件中存储单元区的结构示意图;

图2是现有的或非型闪存器件中外围器件区的结构示意图;

图3a~3i是现有的或非型闪存器件的制造方法中的器件示意图;

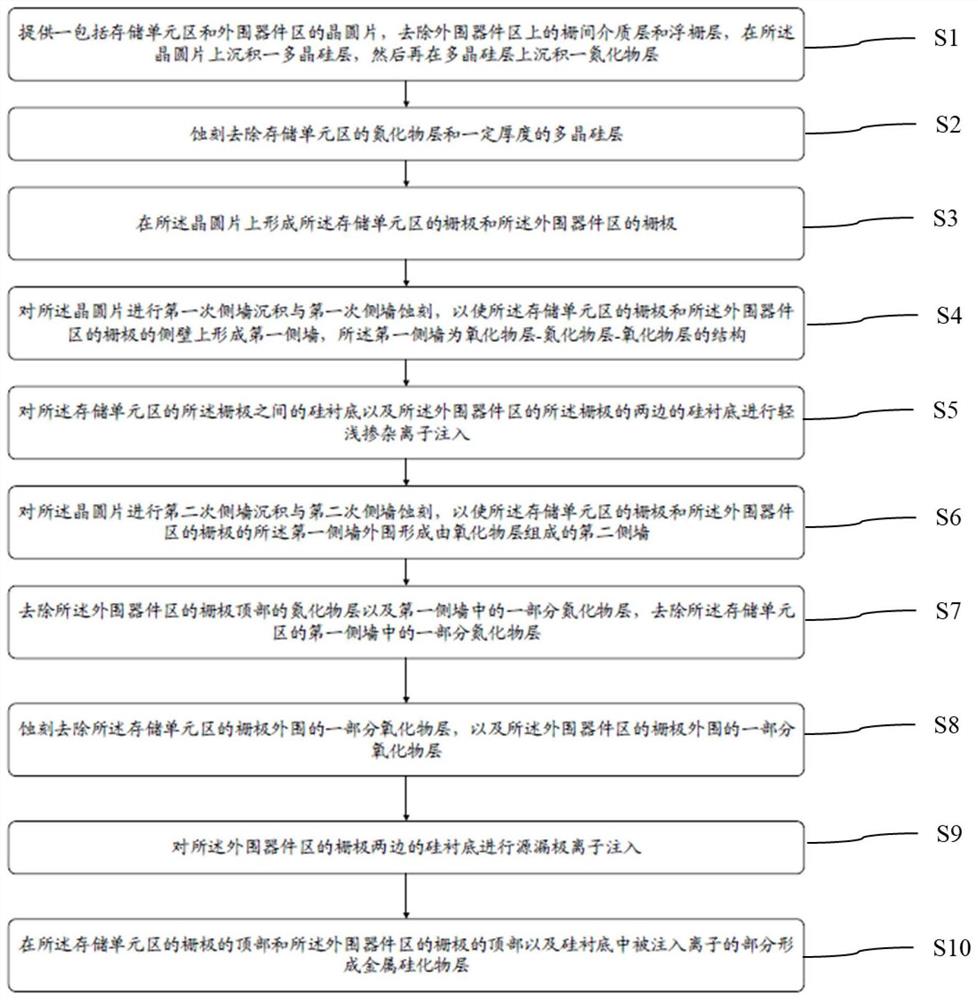

图4是本发明一实施例的或非型闪存器件制造方法的流程图;

图5a~5k是本发明一实施例的或非型闪存器件制造方法中的器件示意 图;

图6是本发明一实施例的或非型闪存器件的结构示意图。

其中,附图的附图标记说明如下:

01-栅极;02,03,04-侧墙;10-氮化物;11,31-硅衬底;12,32-氧化 物层;13,33-浮栅层;14,34-栅间介质层;15,35-多晶硅层;16,36-氧 化物层;17,37-氮化物层;18,38-氧化物层;19-氧化物层;21,41-存储 单元区的栅极;22,42-外围器件区的栅极;23,43-第一侧墙;24,44-第 一侧墙;25,45-第二侧墙;27,47-金属硅化物层。

具体实施方式

为使本发明的目的、优点和特征更加清楚,以下结合附图4~6对本发 明提出的或非型闪存器件及其制造方法作进一步详细说明。需说明的是, 附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地 辅助说明本发明实施例的目的。

本发明一实施例提供一种或非型闪存器件的制造方法,参阅图4,图4 是本发明一实施例的或非型闪存器件制造方法的流程图,所述或非型闪存 器件的制造方法包括:

S1:提供一包括存储单元区和外围器件区的晶圆片,去除外围器件区 上的栅间介质层和浮栅层,在所述晶圆片上沉积一多晶硅层,然后再在多 晶硅层上沉积一氮化物层;

S2:蚀刻去除存储单元区的氮化物层和一定厚度的多晶硅层;

S3:在所述晶圆片上形成所述存储单元区的栅极和所述外围器件区的 栅极;

S4:对所述晶圆片进行第一次侧墙沉积与第一次侧墙蚀刻,以使所述 存储单元区的栅极和所述外围器件区的栅极的侧壁上形成第一侧墙,所述 第一侧墙为氧化物层-氮化物层-氧化物层的结构;

S5:对所述存储单元区的所述栅极之间的硅衬底以及所述外围器件区 的所述栅极的两边的硅衬底进行轻浅掺杂离子注入;

S6:对所述晶圆片进行第二次侧墙沉积与第二次侧墙蚀刻,以使所述 存储单元区的栅极和所述外围器件区的栅极的所述第一侧墙外围形成由氧 化物层组成的第二侧墙;

S7:去除所述外围器件区的栅极顶部的氮化物层以及第一侧墙中的一 部分氮化物层,去除所述存储单元区的第一侧墙中的一部分氮化物层;

S8:蚀刻去除所述存储单元区的栅极外围的一部分氧化物层,以及所 述外围器件区的栅极外围的一部分氧化物层;

S9:对所述外围器件区的栅极两边的硅衬底进行源漏极离子注入;

S10:在所述存储单元区的栅极的顶部和所述外围器件区的栅极的顶部 以及硅衬底中被注入离子的部分形成金属硅化物层。

下面参阅图5a~5j更为详细地介绍本实施例提供的闪存器件的制造方 法,图5a~5j是图4所示的或非型闪存器件的制造方法中的器件示意图。

首先,按照步骤S1,提供一包括存储单元区和外围器件区的晶圆片, 所述存储单元区和所述外围器件区自下而上依次包括硅衬底层31、氧化层 32、浮栅层33和栅间介质层34,所述栅间介质层34为氧化物-氮化物-氧 化物的结构,通过光刻打开外围器件区并去除外围器件区上的栅间介质层 34和浮栅层33,在所述晶圆片上沉积一多晶硅层35,然后再沉积一氮化 物层10,参阅图5a;

然后,按照步骤S2,通过光刻打开存储单元区,通过蚀刻去除存储单 元区的氮化物层10和一定厚度的多晶硅层35,参阅图5b;

按照步骤S3,在所述晶圆片上形成所述存储单元区的栅极41和所述 外围器件区的栅极42,具体地,通过光刻定义出所述存储单元区的栅极的 图形,通过蚀刻产生所述存储单元区的栅极41,再通过光刻定义出所述外 围器件区的栅极图形,通过蚀刻产生所述外围器件区的栅极42,参阅图5c;

然后,按照步骤S4,先对所述晶圆片进行第一次侧墙沉积,参阅图5d, 所述晶圆片上形成氧化物层36-氮化物层37-氧化物层38的结构,所述存储 单元区的所述栅极41和所述外围器件区的所述栅极42被所述氧化物层36- 氮化物层37-氧化物层38的结构包裹,所述栅极之间裸露的硅衬底覆盖一 层氧化物层36-氮化物层37-氧化物层38结构;

按照步骤S4,再对所述晶圆片进行第一次侧墙蚀刻,参阅图5e,所述 存储单元区的所述栅极41的顶部和所述外围器件区的所述栅极42的顶部 的氧化物层36-氮化物层37-氧化物层38结构被蚀刻掉,所述栅极之间的硅 衬底上的氧化物层36-氮化物层37-氧化物层38结构被蚀刻掉,所述存储单 元区的栅极41外围形成第一侧墙43以及所述外围器件区的栅极42的外围 形成第一侧墙44,即所述第一侧墙44由氧化物层36-氮化物层37-氧化物层38构成,由于所述外围器件区的栅极42顶部具有氮化物10,与现有技 术相比,参阅图3d,在第一次侧墙蚀刻之后,本实施例的所述外围器件区 的栅极42的高度更高,所以所述外围器件区的栅极42的外围会形成更宽 的第一侧墙44;

然后,按照步骤S5,通过光刻分别打开存储单元区和外围器件区,对 所述栅极之间的裸露的硅衬底进行轻浅掺杂离子注入,即所述硅衬底31被 所述栅极和所述第一侧墙阻挡的部分未被注入离子,参阅图5f;

然后,按照步骤S6,先对所述晶圆片进行第二次侧墙沉积,参阅图5g, 所述第二次侧墙沉积的材料为氧化物,所述存储单元区上的栅极41和所述 外围器件区的栅极42被所述氧化物层19包裹,所述栅极之间裸露的硅衬 底31覆盖一层氧化物;

按照步骤S6,再对所述晶圆片进行第二次侧墙蚀刻,所述存储单元区 的栅极41顶部和所述外围器件区的栅极42顶部的氧化物层19被蚀刻掉, 所述栅极之间的硅衬底31上的氧化物层19被蚀刻掉,所述存储单元区的 所述栅极41和所述外围器件区的所述栅极42侧壁上的所述第一侧墙外围 形成由氧化物层19组成的第二侧墙45,由于所述外围器件区的顶部具有 氮化物10,与现有技术相比,参阅图3g,在第二次侧墙蚀刻之后,本实施 例的所述外围器件区的栅极42的高度更高,所示所述外围器件区的栅极 42的第一侧墙44外会形成更宽的第二侧墙45,参阅图5h,所述外围器件 区的侧墙厚度增加,提高了器件在高压操作时的可靠性;

然后,按照步骤S7,对所述晶圆片进行酸洗,将所述外围器件区的栅 极42顶部的氮化硅10去除,将所述外围器件区的所述第一侧墙44中的氮 化物层37去除一部分直至与栅极42的高度相同,同时将所述存储单元区 的栅极41外围的第一侧墙43中的氮化物层37去除一部分,参阅图5i,同 时,与现有技术相比,参阅图3h,由于本实施例第二次侧墙沉积采用材料 是氧化物,因此在酸洗的过程中,在所述存储单元区和所述外围器件区中, 所述第二侧墙45的氧化物层19保护了所述第一侧墙44中的氮化物层37, 没有造成所述第一侧墙底部的氮化物损失,保持了器件的均匀性,从而提 高了器件的可靠性;

然后,按照步骤S8,进行一次氧化物蚀刻,去除所述存储单元区的栅 极41的侧墙上部的一部分氧化物层36以及氧化物层38直至所述氧化物层 36以及氧化物层38的高度与所述栅极41外围第一侧墙43中的氮化物层 37的高度相同,此时,由于氮化物层37的高度在步骤S7中降低了一部分, 因此所述存储单元区的栅极41外围的侧墙高度将低于所述栅极41的高度, 即在存储单元区中,所述栅极之间的深宽比将由于深度的降低而降低,有 利于后续层间介质的填充;所述外围器件区的栅极42的侧墙上部的氧化物 层36与氧化物层38也会被蚀刻与栅极42的高度相同;

然后,按照步骤S9,对所述外围器件区的栅极两边的硅衬底进行源漏 极离子注入,参阅图5j;

最后,按照步骤S10,通过自对准硅化物工艺在栅极的顶部和所述栅 极之间裸露的硅衬底上形成金属硅化物47,参阅图5k。

其中,所述氧化物可以为氧化硅,所述氮化物可以为氮化硅。

从上述步骤S1~S10中可知,本发明的技术方案在不增加光罩的情况 下,通过在多晶硅沉积后又沉积一氮化物层,并在后续的步骤中去除所述 存储器件区的栅极顶部的氮化物,保留所述外围器件区的栅极顶部的氮化 物,使得所述外围器件区的栅极高度得到提高,进而使得所述外围器件区 的栅极得到宽度更大的侧墙,避免了在高压操作时被击穿,同时避免了热 载流子效应的产生,提高了器件的可靠性;本发明的技术方案还采用氧化 物作为第二次侧墙沉积的材料,使得所述氧化物在后续的酸洗步骤中能够 保护第一侧墙中的形成的氮化物,提高了均匀性,降低了潜在漏电和干扰 失效的风险;另外,本发明的技术方案还使得所述存储单元区的深宽比得 到降低,有利于后续层间介质的填充。

综上所述,本发明提供的或非型闪存器件的制造方法,包括:提供一 包括存储单元区和外围器件区的晶圆片,去除外围器件区上的栅间介质层 和浮栅层,对所述晶圆片进行多晶硅沉积,然后再在多晶硅层上沉积一氮 化物层;去除存储单元区的氮化硅层和一定厚度的多晶硅层;在所述晶圆 片上形成所述存储单元区的栅极和所述外围器件区的栅极;对所述晶圆片 进行第一次侧墙沉积,在所述晶圆片上形成氧化物-氮化物-氧化物的结构;对所述晶圆片进行第一次侧墙蚀刻,在所述存储单元区的所述栅极和所述 外围器件区的所述栅极的侧壁上形成第一侧墙;对所述存储单元区的所述 栅极之间的硅衬底进行轻浅掺杂离子注入;对所述晶圆片进行第二次侧墙 沉积,所述第二次侧墙沉积的材料为氧化物;对所述晶圆片进行第二次侧 墙蚀刻,在所述存储单元区的所述栅极和所述外围器件区的所述栅极的所 述第一侧墙外围形成由氧化物组成的第二侧墙;对所述晶圆片进行酸洗,去除所述外围器件区上栅极顶部的氮化物层以及一部分所述第一侧墙中的 氮化物,去除所述存储单元区的所述第一侧墙中的一部分氮化物;蚀刻去 除所述存储单元区的所述栅极的所述第一侧墙上部的一部分氧化硅,以及 所述外围器件区的栅极上所述第一侧墙上部的一部分氧化物;对所述外围 器件区栅极两边的硅衬底进行源漏极离子注入;以及,在栅极的顶部和所 述栅极之间裸露的硅衬底上形成金属硅化物。通过本发明的技术方案,使得在技术节点变小的同时,降低了存储单元区的深宽比,有利于后续对层 间介质的填充,增大了所述外围器件区的侧墙厚度,保证了足够的击穿电 压,提高了产品均匀性,提高了或非型闪存器件的可靠性。

本发明一实施例提供一种或非型闪存器件,所述或非型闪存器件采用 本发明的所述或非型闪存器件的制造方法形成,所述或非型闪存器件包括 存储单元区和外围器件区,所述存储单元区和所述外围器件区设置于一硅 衬底上,所述存储单元区包括栅极,部分所述存储单元区的所述栅极之间 的硅衬底上设置有有源区,所述存储单元区的所述栅极的顶部和所述有源 区覆盖有一层金属硅化物,所述存储单元区的所述栅极的侧壁上设置一侧 墙;所述外围器件区包括栅极,所述外围器件区的所述栅极的两边分别设 置有源极和漏极,所述外围器件区的所述栅极的顶部和所述源极以及所述 漏极覆盖设置有一层金属硅化物,所述外围器件区的所述栅极的侧壁上设 置有侧墙。

下面参阅图6详细描述本实施例提供的或非型闪存器件:

所述存储单元区的所述栅极自下而上依次包括氧化物、浮栅层、栅间 介质层以及多晶硅层,所述存储单元区的侧墙03的高度低于所述存储单元 区的所述栅极41的高度,所述存储单元区的侧墙03的结构为氧化物-氮化 物-氧化物结构,且所述存储单元区的所述侧墙的底部氧化物将氮化物完全 包裹,与现有技术相比,参阅图1,图1为现有或非型闪存器件的存储单 元区的器件示意图,所述侧墙的高度与所述栅极21的高度是相同的,且所述侧墙的底部的氧化物未将氮化物完全包裹,本实施例的或非型闪存器件 的存储区单元的深宽比更低,有利于后续层间介质的填充,且所述存储单 元区的所述侧墙的底部氧化物将氮化物完全包裹,在酸洗工艺中,所述氮 化物不会由于酸洗而损失,提高了产品的均匀性,避免了潜在漏电和干扰 失效的风险。

所述外围器件区的所述栅极自下而上依次包括氧化物层以及多晶硅 层,与现有技术相比,参阅图2,图2是现有的或非型闪存器件的外围器 件区的器件示意图,所述侧墙02的宽度较本实施例的所述外围器件区的所 述侧墙04的宽度要窄,更宽的所述侧墙04使得所述金属硅化物47之间的 距离更远,使得所述外围器件区有更高的击穿电压,同时避免了热载流子 效应等威胁所述外围器件区可靠性的问题。

综上所述,本发明提供的或非型闪存器件,包括存储单元区和外围器 件区,所述存储单元区和所述外围器件区设置于一硅衬底上,所述存储单 元区包括栅极,所述存储单元区的部分所述栅极之间的硅衬底上设置有有 源区,所述存储单元区的所述栅极的顶部和所述有源区覆盖有一层金属硅 化物,所述存储单元区的所述栅极的侧壁上设置一侧墙;所述外围器件区 包括栅极,所述外围器件区的所述栅极的两边分别设置有源极和漏极,所述外围器件区的所述栅极的顶部和所述源极以及所述漏极覆盖设置有一层 金属硅化物,所述外围器件区的所述栅极的侧壁上设置有侧墙。本发明提 供的或非型闪存器件使得在技术节点变小的同时,降低了存储单元区的深 宽比,有利于后续对层间介质的填充,增大了所述外围器件区的侧墙厚度, 保证了足够的击穿电压,提高了产品均匀性,提高了或非型闪存器件的可 靠性。

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何 限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰, 均属于权利要求书的保护范围。

- 与非型闪存器件的擦除确认方法及其与非型闪存器件

- 或非型闪存器件及其制造方法