一种ARM芯片cache命中率的测试方法

文献发布时间:2024-01-17 01:28:27

技术领域

一种ARM芯片cache命中率的测试方法,属于通信及计算机领域。

背景技术

在ARM架构下,cache是一种高速缓存,用于临时存储数据和指令,缓存常常作为系统的数据缓冲,将频繁访问的数据放入缓存中,避免多次到数据库,或者文件系统,以提高内存访问速度。在缓存系统中的一个核心指标为命中率(hit rate),命中率等于读取请求返回存在的次数/总共的读取次数。其中,命中是指读取某一数据时,假若该数据存在,则是命中;非命中(miss)是指读取某一数据时,假若该数据不存在,则是非命中。缓存命中率的高低与用户的使用逻辑关系密切。当命中率低时,是不能提升系统的性能的,所以命中率的高低直接影响系统的响应时间和整体吞吐量。然而,由于cache容量有限,命中率的高低会直接影响系统的性能和效率。因此需要准确测试ARM芯片cache的命中率。

在现有技术中,ARM芯片cache命中率的测试通常有两种方法:模拟器模拟和实际部署测试。其中,模拟器模拟是通过模拟不同负载和运行环境下的性能指标来测试cache命中率,但由于是虚拟的测试环境,测试结果可能与实际情况不同。并且模拟器模拟还存在如下缺陷:测试结果不够准确:由于采用的是软件模拟器,不能完全模拟真实的硬件环境,因此测试结果可能与实际情况存在偏差。(2)测试成本高:为实现准确的测试结果,需要用到高性能的软件模拟器,这样往往需要消耗大量的计算资源。

而实际部署测试是通过在实际硬件上运行程序来测试cache命中率,但该方法需要大量的时间和资源,并且在实际应用中不便实现,同时实际部署测试还存在如下缺陷:(1)测试周期长:需要在实际环境中部署测试程序,需要花费大量的时间来收集和分析测试结果。(2)测试成本高:需要大量的硬件资源,如ARM芯片、开发板等,并且需要熟悉ARM芯片的架构和编程方法,才能进行测试。(3)不方便实现:需要对硬件进行改动和部署。

因此设计一种简单易行的ARM芯片cache命中率的测试方法,成为本领域亟待解决的问题。

发明内容

本发明要解决的技术问题是:克服现有技术的不足,提供一种采用了基于引用计数的Cache分析方法,通过记录Cache的命中次数和访问次数,可以准确测量Cache的访问时间和命中率,为优化ARM芯片的Cache提供基础数据的ARM芯片cache命中率的测试方法。

本发明解决其技术问题所采用的技术方案是:该ARM芯片cache命中率的测试方法,其特征在于:包括如下步骤:

步骤a,根据需要测试的测试程序的编程语言和目标平台,编写插桩代码;

步骤b,将步骤a中编译的插桩代码和测试程序进行合并,并进行编译和链接,生成带有插桩代码的二进制可执行文件;

步骤c,在目标平台上运行测试程序;

步骤d,分析测试结果,根据插桩代码记录的Cache的命中次数和访问次数,计算出cache当前测试的命中率,并与前次测试的命中率进行比较。

优选的,步骤c包括如下步骤:

步骤c-1,确定测试的硬件环境;

步骤c-2,搭建测试的软件环境;

步骤c-3,启动测试程序。

优选的,步骤c-3包括如下步骤:

步骤c-3-1,运行测试程序,运行测试程序,并确保测试程序正确地访问ARM芯片的cache;

步骤c-3-2,对cache的命中次数和访问次数进行记录和追踪;

步骤c-3-3,测试程序运行时间的记录:记录测试程序的运行时间。

优选的,在步骤a中,使用系统调用或者CPU周期计数器记录cache的访问次数和命中次数。

与现有技术相比,本发明所具有的有益效果是:

1、在本ARM芯片cache命中率的测试方法中,采用了基于引用计数的Cache分析方法,通过记录Cache的命中次数和访问次数,可以准确测量Cache的访问时间和命中率,为优化ARM芯片的Cache提供基础数据。

2、本ARM芯片cache命中率的测试方法,可以准确测试ARM芯片的Cache命中率和其他性能指标,避免了因参数误差等原因造成的测试偏差和结果不准确的情况。

3、通过引用计数的Cache分析方法,可以避免擦除Cache数据、清空Cache等影响测试结果的情况,得到更加准确和实际的测试数据。

4、本ARM芯片cache命中率的测试方法,简单易行、成本低廉,可以广泛应用于ARM芯片的性能测试和调优工作。

5、测试程序采用汇编语言编写,能够提高程序的执行效率和稳定性,确保测试结果的准确性和可靠性。

附图说明

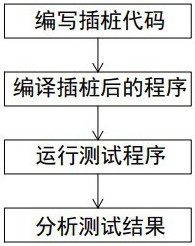

图1为ARM芯片cache命中率的测试方法流程图。

图2为ARM芯片cache命中率的测试方法运行测试程序流程图。

具体实施方式

图1~2是本发明的最佳实施例,下面结合附图1~2对本发明做进一步说明。

如图1所示,一种ARM芯片cache命中率的测试方法(以下简称测试方法),包括如下步骤:

步骤a,编译插桩代码;

根据需要测试的测试程序的编程语言和目标平台,编写插桩代码,通过插入测试代码实现对指定代码段的监控和统计。通过插桩代码记录cache的访问次数和命中次数,可以使用系统调用或者CPU周期计数器来实现。

测试程序采用汇编语言编写,能够确保测试程序的执行效率和稳定性,得到更准确的测试数据。

步骤b,编译插桩后的程序;

将步骤a中编译的插桩代码和测试程序进行合并,并进行编译和链接,生成带有插桩代码的二进制可执行文件。

步骤c,运行测试程序;

在目标平台上运行测试程序,并使其执行与缓存相关的操作,如数据访问、文件读写等。此时,通过插桩代码会自动进行统计,计算出cache的访问次数和命中次数。

步骤c包括如下步骤:

步骤c-1,确定测试的硬件环境,选择符合测试要求的ARM芯片和相关硬件设备,如开发板、调试器、JTAG。

步骤c-2,搭建测试的软件环境,选择或者搭建合适的操作系统和编程环境,根据测试需求和目标,对测试程序进行编写和调试。

步骤c-3,启动测试程序;

包括如下步骤:

步骤c-3-1,运行测试程序,通过正常的启动方式运行测试程序,并确保测试程序可以正确地访问ARM芯片的cache。

步骤c-3-2,数据的记录和追踪:使用脚本对cache的命中次数和访问次数进行记录和追踪,以便于后续的数据分析和统计。

步骤c-3-3,测试程序运行时间的记录:记录测试程序的运行时间,以便后续计算指标和分析性能。

步骤d,分析测试结果;

包括如下步骤:

步骤d-1,数据的计算和统计:根据插桩代码记录的数据,计算出cache当前测试的命中率,并与前次测试的命中率进行比较。

步骤d-2,数据的可视化展示:使用图表、统计图等方式将测试结果可视化展示,以便更直观地观察和比较数据。

在本测试方法中,利用计数的Cache分析方法,通过记录Cache的命中次数和访问次数,可以准确测量Cache的访问时间和命中率,为优化ARM芯片的Cache提供基础数据。在实现上,本发明采用了汇编语言编写测试程序,以确保程序执行的效率和稳定性,同时通过对测试程序的参数设置和运行,可以模拟多种业务场景和访问模式,尽可能地反映实际测试情况。

以上所述,仅是本发明的较佳实施例而已,并非是对本发明作其它形式的限制,任何熟悉本专业的技术人员可能利用上述揭示的技术内容加以变更或改型为等同变化的等效实施例。但是凡是未脱离本发明技术方案内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与改型,仍属于本发明技术方案的保护范围。

- 一种提升Cache命中率的方法、系统、设备及介质

- 一种提升Cache Tire缓存命中率的方法