半导体装置及其制造方法

文献发布时间:2023-06-19 09:41:38

技术领域

本发明的实施方式涉及一种半导体装置及其制造方法。

背景技术

以追求高积体化为目的而包含经积层化的存储单元的三维存储器等的半导体装置得到开发。随着上述积层化的进展,通过将某晶片的金属垫与另外的晶片的金属垫利用贴合工艺接合而制造出三维存储器。在如上述的半导体装置中,存在为了进一步提高积体度而减细布线、或为了缩短布线长而在较细的布线上形成插塞并与上层布线连接的情况。在这种情况下,会有难于进行插塞与其对应的布线的位置对准、或插塞与其它布线易于短路等的问题。相同的问题也会在三维存储器以外的半导体装置的布线上形成插塞时产生。

现有技术文献

专利文献

专利文献1:日本特开2010-129686号公报

专利文献2:日本特开平9-283617号公报

专利文献3:日本特开2018-41963号公报

发明内容

发明所要解决的问题

本发明的实施方式提供一种可在布线上适当地形成插塞的半导体装置及其制造方法。

解决问题的技术手段

根据一实施方式,半导体装置具备:第1绝缘膜、以及设置在所述第1绝缘膜内的多条布线。所述装置还具备:第2绝缘膜,设置在所述第1绝缘膜及所述多条布线上;以及导电体,设置在所述多条布线中的第1布线上,且具有在所述第2绝缘膜内相对于所述第1布线朝上方突出的形状。所述装置还具备介隔着所述导电体设置在所述第1布线上的插塞。所述装置还具备设置在所述插塞的上方且与所述插塞电连接的第1垫。所述装置还具备设置在所述第1垫上且与所述第1垫电连接的第2垫。

附图说明

图1是表示第1实施方式的半导体装置的构造的剖视图。

图2是表示第1实施方式的柱状部的构造的剖视图。

图3是表示第1实施方式的半导体装置的制造方法的剖视图。

图4是表示第1实施方式的阵列芯片的构造的剖视图。

图5是表示第1实施方式的阵列晶片的制造方法的剖视图(1/4)。

图6是表示第1实施方式的阵列晶片的制造方法的剖视图(2/4)。

图7是表示第1实施方式的阵列晶片的制造方法的剖视图(3/4)。

图8是表示第1实施方式的阵列晶片的制造方法的剖视图(4/4)。

图9是用于说明第2实施方式的半导体装置的构造的剖视图与平面图。

图10是用于说明第2实施方式的半导体装置的构造的剖视图与平面图。

图11是表示第2实施方式的半导体装置的构造的平面图。

图12是表示第2实施方式的半导体装置的构造的剖视图。

图13是示意性地表示第2实施方式的半导体装置的构造的平面图。

图14是表示第2实施方式的半导体装置的制造方法的平面图。

图15是表示第2实施方式的半导体装置的制造方法的平面图。

具体实施方式

以下,参照图式说明本发明的实施方式。在图1至图15中,对相同或类似的结构标注相同的符号,而省略重复的说明。

(第1实施方式)

图1是表示第1实施方式的半导体装置的构造的剖视图。图1的半导体装置是将阵列芯片1与电路芯片2贴合而成的三维存储器。

阵列芯片1具备:包含多个存储单元的存储单元阵列11、存储单元阵列11上的绝缘层12(例如氮化硅膜)、绝缘层12上的绝缘层13(例如氧化硅膜)、以及存储单元阵列11下的层间绝缘膜14。

电路芯片2介隔着绝缘层15设置在阵列芯片1下。电路芯片2具备层间绝缘膜16、以及层间绝缘膜16下的衬底17。衬底17例如是硅衬底等的半导体衬底。图1表示与衬底17的表面平行且相互垂直的X方向及Y方向、以及垂直于衬底17的表面的Z方向。在本说明书中,将+Z方向视为上方向,将-Z方向视为下方向,但-Z方向与重力方向可一致也可不一致。

阵列芯片1具备多条字线WL、源极线SL、以及选择栅极SG作为存储单元阵列11内的电极层。图1表示存储单元阵列11的阶梯构造部21。如图1所示,各字线WL通过接触插塞22与字布线层23电连接,源极线SL通过接触插塞24与源极布线层25电连接,选择栅极SG通过接触插塞26与选择栅极布线层27电连接。贯通字线WL、源极线SL、以及选择栅极SG的柱状部CL通过插塞28与位线BL电连接。

电路芯片2具备多个晶体管31。各晶体管31具备:介隔着栅极绝缘膜设置在衬底17上的栅极电极32、以及设置在衬底17内的未图示的源极扩散层及漏极扩散层。电路芯片2还具备:多个插塞33,设置在所述晶体管31的源极扩散层或漏极扩散层上;布线层34,设置在所述插塞33上且包含多条布线;及布线层35,设置在布线层34上且包含多条布线。设置在绝缘层15内的多个金属垫36是设置在布线层35上。阵列芯片1具备设置在所述金属垫36上且包含多条布线的布线层37。本实施方式的各字线WL及各位线BL分别与对应的布线层37电连接。

阵列芯片1还具备:通过未图示的介层插塞与布线层37电连接的垫41、设置在垫41上的外部连接电极42、以及设置在外部连接电极42上的外部连接垫43。外部连接垫43可通过焊料球、金属凸块、接合线等连接于安装衬底及其它装置。

图2是表示第1实施方式的柱状部CL的构造的剖视图。

如图2所示,存储单元阵列11具备在层间绝缘膜14上交替地积层的多条字线WL以及多个绝缘层51。各字线WL例如是W(钨)层。各绝缘层51例如是氧化硅膜。

柱状部CL具备:阻挡绝缘膜52、电荷蓄积层53、隧道绝缘膜54、通道半导体层55、以及磁芯绝缘膜56。电荷蓄积层53例如是氮化硅膜,在字线WL及绝缘层51的侧面介隔着阻挡绝缘膜52而形成。通道半导体层55例如是硅层,在电荷蓄积层53的侧面介隔着隧道绝缘膜54而形成。阻挡绝缘膜52、隧道绝缘膜54、以及磁芯绝缘膜56的一例为氧化硅膜或金属绝缘膜。

图3是表示第1实施方式的半导体装置的制造方法的剖视图。

图3表示包含多个阵列芯片1的阵列晶片W1、以及包含多个电路芯片2的电路晶片W2。图3还示出了设置在阵列晶片W1的下表面的第1绝缘层61及多个第1金属垫62、以及设置在电路晶片W2的上表面的第2绝缘层71及多个第2金属垫72。各第1金属垫62设置在布线层37的下表面,各第2金属垫72设置在布线层35的上表面。另外,阵列晶片W1在绝缘层13上具备衬底18。

另外,在图3中是于层间绝缘膜14的下表面形成有第1绝缘层61,但第1绝缘层61也可以包含于层间绝缘膜14而一体化。同样在图3中是在层间绝缘膜16的上表面形成有第2绝缘层71,但第2绝缘层71也可以包含于层间绝缘膜16而一体化。

首先,将阵列晶片W1与电路晶片W2通过机械压力而贴合。由此,第1绝缘层61与第2绝缘层71粘接而形成绝缘层15。接着,将阵列晶片W1及电路晶片W2在400℃下进行退火。由此,第1金属垫62与第2金属垫72接合而形成多个金属垫36。

其后,通过CMP(Chemical Mechanical Polishing,化学机械研磨)或湿式蚀刻去除衬底18,并将阵列晶片W1及电路晶片W2切断为多个芯片。如上述那样制造图1的半导体装置。另外,外部连接电极42与外部连接垫43例如在去除衬底18后形成在垫41上。

此外,在本实施方式中是将阵列晶片W1与电路晶片W2贴合,但也可以替代地将阵列晶片W1彼此贴合。参照图1~图3在前文所述的内容及参照图4~图15将于下文叙述的内容也可以应用于阵列晶片W1彼此的贴合。阵列晶片W1也被称为存储晶片,电路晶片W2也被称为CMOS晶片。

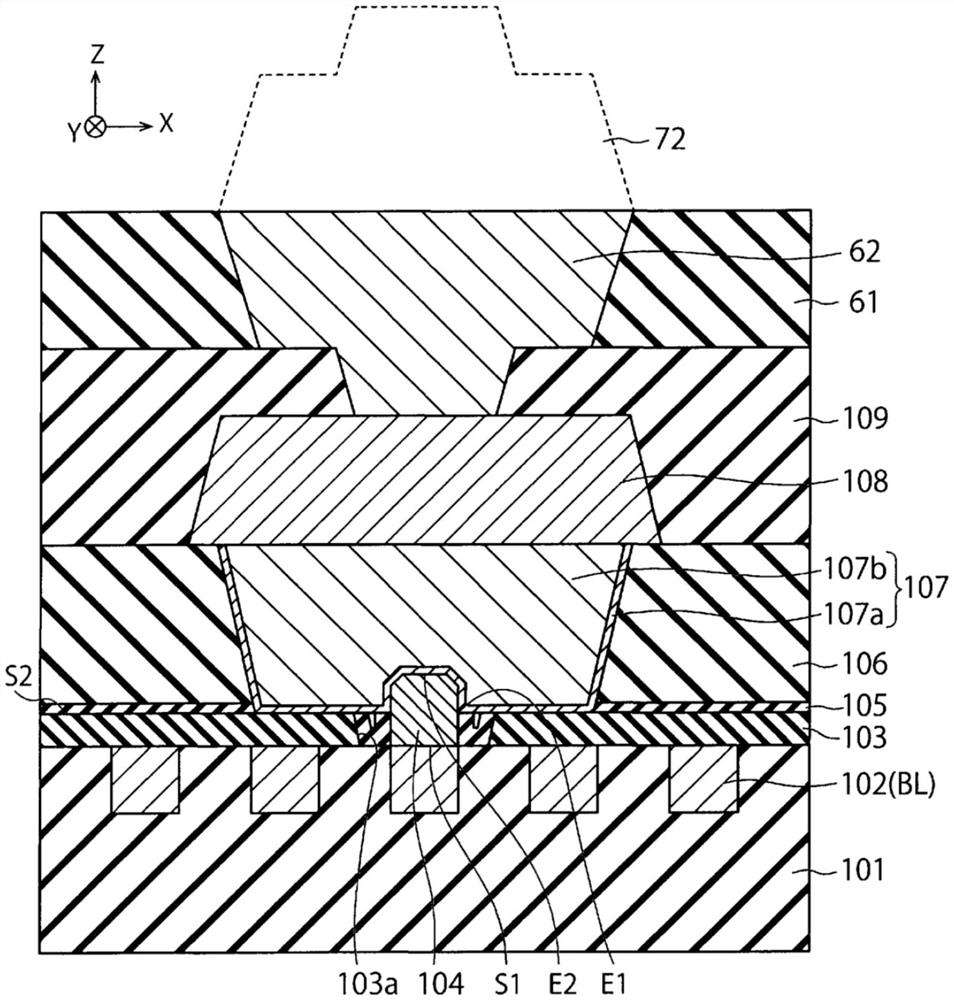

图4是表示第1实施方式的阵列芯片1的构造的剖视图。其中,应注意图4的上方向及下方向与图1的上方向及下方向相反。图4是表示将图1所示的阵列芯片1上下反转的状态。这在下述的图5~图15中也相同。

如图4所示,阵列芯片1具备:作为第1绝缘膜的一例的第1层间绝缘膜101、多条金属布线102、作为第2绝缘膜的一例的阻止绝缘膜103、作为导电体的一例的金属凸块104、间隔绝缘膜105、第2层间绝缘膜106、介层插塞107、金属布线108、以及第3层间绝缘膜109。图4更表示阵列芯片1内的第1绝缘层61及第1金属垫62、以及电路芯片2内的第2金属垫72。

第1层间绝缘膜101例如是SiO

阻止绝缘膜103例如是SiN膜(氮化硅膜),形成在第1层间绝缘膜101及金属布线102上。符号103a表示形成在所述金属布线102中的1条金属布线102上的开口部。以下将所述1条金属布线102称为「第1金属布线102」。符号S1表示第1金属布线102的上表面。符号S2表示阻止绝缘膜103的上表面。

金属凸块104是由例如Cu、CoWPB、CoWB、或Sn形成(Co表示钴、B表示硼、P表示磷、Sn表示锡),形成在阻止绝缘膜103的开口部103a内。具体来说,金属凸块104形成在上述第1金属布线102上,且具有相对于第1金属布线102朝上方突出的形状。金属凸块104的平面形状例如是圆形、正方形或接近所述形状的形状。本实施方式的金属凸块104是于第1金属布线102上通过镀覆而形成。符号E2表示金属凸块104的上端(最上部)。

间隔绝缘膜105例如是等离子SiN膜,形成在阻止绝缘膜103的上表面S2、以及在阻止绝缘膜103的开口部103a内形成在阻止绝缘膜103与金属凸块104之间。第2层间绝缘膜106例如是SiO

介层插塞107在第2层间绝缘膜106内形成在阻止绝缘膜103、金属凸块104、以及间隔绝缘膜105上,且在第1金属布线102上介隔着金属凸块104而形成。介层插塞107包含:势垒金属层107a,形成在阻止绝缘膜103、金属凸块104、以及间隔绝缘膜105的表面;以及插塞材层107b,在所述表面介隔着势垒金属层107a而形成。势垒金属层107a例如是含有Ti(钛)或Ta(钽)的导电层,插塞材107b例如为W(钨)层。介层插塞107的平面形状例如是与金属凸块104相同地为圆形、正方形、或与所述形状接近的形状,但与金属凸块104的下表面的面积相比,介层插塞107的上表面的面积设定为更宽广。符号E1表示金属凸块104与介层插塞107的接触面的下端(最下部)。

金属布线108形成在介层插塞107上。第3层间绝缘膜109以覆盖金属布线108的方式形成在第2层间绝缘膜106上。第1绝缘层61形成在第3层间绝缘膜109上。

第1金属垫62在第1绝缘层61内形成在金属布线108上,位于介层插塞107的上方,且通过金属布线108与介层插塞107电连接。在图4中为了方便理解而将本实施方式的第1金属垫62的上表面的面积与介层插塞107的上表面的面积描绘为相同程度,但实际上设定为介层插塞107的上表面的面积的2倍以上(例如10倍以上)。

第2金属垫72在上述第2绝缘层71内形成在第1金属垫62上,且与第1金属垫62电连接。本实施方式的第2金属垫72的下表面的面积与第1金属垫62的上表面的面积大致相同。

如以上所述,本实施方式的介层插塞107在第1金属布线102上介隔金属凸块104而形成。因此,将介层插塞107与其下层布线的接触面较第1金属布线102的上表面S1提高为更高。具体来说,金属凸块104与介层插塞107的接触面的下端E1设置在较第1金属布线102的上表面S1更高的位置。

由此,可将第1金属布线102用的介层插塞107与第1金属布线102以外的金属布线102之间的距离在上下方向上更宽地留出,而可抑制所述元件之间的短路及阻止绝缘膜103的经时劣化。根据本实施方式,即便在金属布线102较细、或金属布线102间的距离较窄时,通过在上下方向上更宽地留出所述距离,而可有效地抑制上述短路及经时劣化。另外,根据本实施方式,由于即便介层插塞107用的光刻术的位置对准精度较低,仍易于抑制上述短路,因此可降低光刻术的成本。

金属凸块104可收纳于开口部103a内,但较理想的是从开口部103a朝上方露出。因此,在本实施方式中,金属凸块104的上端E2设置在较阻止绝缘膜103的上表面S2更高的位置,金属凸块104与介层插塞107的接触面的下端E1设置在较金属凸块104的上端E2更低的位置。由此,可更宽裕地确保第1金属布线102用的介层插塞107与第1金属布线102以外的金属布线102的短路裕度。

本实施方式的金属布线102是位线BL,配置在上述柱状部CL的附近等。一般来说,在柱状部CL的附近,位线BL较细,且位线BL间的距离也较窄。然而,根据本实施方式,由于可在较细的金属布线102上也形成介层插塞107,因此可在柱状部CL的附近的金属布线102上形成介层插塞107,其结果为可缩短金属布线102的布线长。其理由在于,将金属布线102从柱状部CL延伸至较远的地点,而在该地点上无需形成介层插塞107。由此,可进一步提高半导体装置的积体度及降低金属布线102间的静电容量。在本实施方式中,通过进一步将第1金属垫62配置在介层插塞107的正上方(+Z方向),而可缩短第1金属垫62与介层插塞107间的布线长,及进一步提高半导体装置的积体度。

图5至图8是表示第1实施方式的阵列晶片W1的制造方法的剖视图。

首先,在第1层间绝缘膜101内形成多条金属布线102,在第1层间绝缘膜101与所述金属布线102上形成阻止绝缘膜103(图5(a))。阻止绝缘膜103的厚度例如为20~30nm。

接着,在阻止绝缘膜103上形成抗蚀膜111,并通过光刻术及蚀刻在抗蚀膜111上形成开口部111a(图5(b))。接着,通过蚀刻去除开口部111a内的阻止绝缘膜103,并在阻止绝缘膜103形成开口部103a(图5(c))。其后,去除抗蚀膜111。

接着,在露出于阻止绝缘膜103的开口部103a内的金属布线102上形成金属凸块104(图6(a))。本实施方式的金属凸块104在金属布线102上通过无电解镀覆而形成。其结果为,金属凸块104以具有相对于金属布线102朝上方突出的形状的方式成长。在图6(a)中,金属凸块104的上端E2位于较阻止绝缘膜103的上表面S2更高的位置。图6(a)所示的2个金属凸块104下的2条金属布线102相当于第1金属布线102。

由于本实施方式的金属凸块104通过镀覆而形成,因此即便当开口部103a与金属布线102稍许偏移地形成时,也可以在金属布线102上自对准地形成金属凸块104。各金属凸块104可以选择性地只形成在金属布线102的上表面,也可以形成在开口部103a内的第1层间绝缘膜101及金属布线102的整个上表面。

接着,在未图示的衬底18的整个面上形成间隔绝缘膜105(图6(b))。其结果为,间隔绝缘膜105形成在第1层间绝缘膜101、阻止绝缘膜103、金属凸块104的表面、以及开口部103a内的阻止绝缘膜103与金属凸块104的间隙。在形成间隔绝缘膜105之前不存在所述间隙或由其它层填埋时,也可以不形成间隔绝缘膜105。间隔绝缘膜105的厚度例如为2~3nm。

接着,在间隔绝缘膜105上形成第2层间绝缘膜106(图6(c))。接着,在第2层间绝缘膜106上依次形成基底层112及抗蚀膜113(图7(a))。基底层112的一例为有机膜、抗反射膜(例如SiO

接着,通过光刻术以及蚀刻在抗蚀膜113形成开口部113a(图7(b))。接着,通过蚀刻去除开口部113a内的基底层112,并在基底层112形成开口部112a(图7(b))。

接着,通过蚀刻去除开口部112a内的第2层间绝缘膜106,并在第2层间绝缘膜106形成开口部106a(图8(a))。另外,去除开口部106a内的间隔绝缘膜105(图8(a))。其结果为,金属凸块104露出于开口部106a内。

接着,在开口部106a内依次形成势垒金属层107a及插塞材层107b(图8(b))。其结果为,在金属布线102上介隔着金属凸块104而形成有介层插塞107。其后,去除基底层112,如果残存有抗蚀膜113则也将抗蚀膜113去除。

图8(b)表示右侧的介层插塞107产生位置偏移而形成的样态。即便产生这样的位置偏移,由于如上述那样介层插塞107与金属布线102之间距离较远,因此也可抑制所述元件之间的短路及阻止绝缘膜103的经时劣化。因此,由于在图7(b)的步骤中光刻术的位置对准精度为较低即可,因而可降低光刻术的成本。例如,在图7(b)的步骤中也可使用ArF光刻术或KrF光刻术。

其后,形成金属布线108、第3层间绝缘膜109、第1绝缘层61、以及第1金属垫62等,而制造出阵列芯片1。另外,实施图3所示的方法而制造出本实施方式的半导体装置。

如以上所述那样,在本实施方式中,在金属布线102上介隔着金属凸块104而形成介层插塞107。因此,根据本实施方式,可抑制介层插塞107与金属布线102的短路及阻止绝缘膜103的经时劣化等,而可在金属布线102上适当地形成介层插塞104。

另外,本实施方式的介层插塞107可由各种方法形成,例如可通过单镶嵌形成,也可通过双镶嵌形成。另外,介层插塞107也可与金属凸块104相同地通过镀覆而形成。另外,在本实施方式中,也可在图6(b)的步骤与图6(c)的步骤之间,通过CMP(CheminalMechanical Polishing,化学机械研磨)将间隔绝缘膜105及金属凸块104的表面进行研磨。此时,理想的是进行CMP直至阻止绝缘膜103的上表面露出。

(第2实施方式)

图9是用于说明第2实施方式的半导体装置的构造的剖视图及平面图。

图9(a)及图9(b)是分别表示图5(c)的步骤的剖视图及平面图。图9(c)是与图6(a)相同地表示形成在第1金属布线102上的金属凸块104的剖视图。

图10是用于说明第2实施方式的半导体装置的构造的剖视图及平面图。

图10(a)至图10(c)分别对应于图9(a)至图9(c)。其中,图9(c)的金属凸块104形成在较粗的第1金属布线102上,图10(c)的金属凸块104形成在较细的第1金属布线102上。

如上述那样,根据第1实施方式的方法,也可在较细的第1金属布线102上形成金属凸块104。然而,如果在较细的第1金属布线102上形成金属凸块104,则会产生金属凸块104的成长速度变慢等的缺点。因此,在本实施方式中,对能够受益第1实施方式的优点,且在较粗的第1金属布线102上形成金属凸块104的方法进行说明。

图11是表示第2实施方式的半导体装置的构造的平面图。

本实施方式的半导体装置具备:在X方向上延伸的多条布线LI、多个柱状部CL、以及多个插塞28。各插塞28包含接触插塞28a、以及设置在接触插塞插塞28a上的介层插塞28b。由1个柱状部CL、所述柱状部CL上的1个接触插塞28a、以及所述接触插塞插塞28a上的1个介层插塞28b构成1个柱状构造,本实施方式的半导体装置具备多个具有这种形状的柱状构造。

图11与图4相同,更表示包含金属布线102a~102d的多条金属布线102、设置在金属布线102c上的金属凸块104、以及设置在金属凸块104上的介层插塞107。所述金属布线102在Y方向上延伸,且设置在介层插塞28b上。

本实施方式的各金属布线102具备:具有第1宽度(W)的第1部分P1及第2部分P2、以及设置在第1部分P1与第2部分P2之间并具有较第1宽度宽的第2宽度(3W)的第3部分P3。在本实施方式中,为了配置金属凸块104而使用该第3部分P3。图11表示设置在金属布线102c的第3部分P3上的金属凸块104。本实施方式的第2宽度设定为第1宽度的3倍,但也可设定为其它值。

在本实施方式中,各金属布线102的大部分宽度为第1宽度,各金属布线102的一部分宽度为第2宽度。然而,由于将金属凸块104形成在该第2宽度的部分上,因此金属凸块104的成长速度变快。像这样,根据本实施方式,可通过较细的金属布线102而提高积体度,且加快金属凸块104的成长速度。

以下,以金属布线102c为例,说明各金属布线102的形状的细节。

在金属布线102c中,第1部分P1在Y方向上延伸,且在第3部分P3的右上角与第3部分P3连接。另外,第2部分P2在Y方向上延伸,且在第3部分P3的左下角与第3部分P3连接。以下,将右上角称为第1部位,将左下角称为第2部位。在金属布线102c中,第1部位P1的位置与第2部位P2的位置在X方向上相互偏移,具体来说偏移2W的X坐标程度。

金属布线102d在金属布线102c的+X方向上与金属布线102c相邻。金属布线102d的第3部分P3的位置相对于金属布线c的第3部分P3的位置朝-Y方向偏移。另一方面,金属布线102b在金属布线102c的-X方向上与金属布线102c相邻。金属布线102b的第3部分P3的位置相对于金属布线c的第3部分P3的位置朝+Y方向偏移。±Y方向为第1方向的示例,±X方向为第2方向的示例。

在这样的配置上,例如有在各金属布线102设置第3部分P3,并且将金属布线102所占区域缩窄的优点。此外,当在写入时等选择存储单元阵列11内的某柱状部CL时,需要选择1条位线BL及1条选择栅极SG而进行,且需要将与所述位线BL及选择栅极SG电连接的柱状部CL限定为1个。因此,在图11中第3部分P3的下方,不仅可设置包含柱状部CL、接触插塞28a、以及介层插塞28b的柱状构造,也可设置从柱状构造省略接触插塞28a及/或介层插塞28b的构造。所述构造内的柱状部CL成为无电性作用的虚设柱状部。或者,也可在图11的第3部分P3的下方,设置从柱状构造至少省略柱状部CL的构造。

图12是表示第2实施方式的半导体装置的构造的剖视图。

图12表示与图4相同的截面。其中,应注意金属凸块104下的第1金属布线102的宽度为3W。此图表示第1金属布线102的第3部分P3的截面。

图13是示意性地表示第2实施方式的半导体装置的构造的平面图。

图13表示上述的选择栅极SG。所述选择栅极SG在X方向上延伸,且在Y方向上彼此相邻。在图13中,各金属布线102(位线BL)的第3部分P3配置在任一选择栅极SG上。

图14及图15是表示第2实施方式的半导体装置的制造方法的平面图。下文中说明具备第1至第3部分P1~P3的金属布线102的形成方法。

首先,在上述第1层间绝缘膜101上形成在Y方向上延伸的多条第1芯材线121(图14(a))。各第1芯材线121具备具有第1宽度(W)的部分、以及具有第2宽度(3W)的部分。所述第1芯材线121例如利用光刻术及细化而形成。

接着,于所述第1芯材线121的侧面,形成在Y方向上延伸的多条第2芯材线122(图14(b))。各第2芯材线122具有下述形状,即:在第1芯材线121的第2宽度的部分附近具有弯曲部分。

接着,去除第1芯材线121(图15(a))。接着,通过镶嵌在第2芯材线122间的间隙而形成多条金属布线102(图15(b))。其结果为,各金属布线102形成具备第1至第3部分P1~P3的形状。在本实施方式中,将第2芯材线122用作第1层间绝缘膜101的一部分。

如以上所述那样,在本实施方式中,各金属布线102具备具有第1宽度的部分、以及具有较第1宽度更宽的第2宽度的部分,且金属凸块104形成在具有第2宽度的部分上。因此,根据本实施方式,能够享有第1实施方式的优点,且在较粗的金属布线102上形成金属凸块104。

以上说明了几个实施方式,但所述实施方式是仅作为例子而提出的,并非意欲限定发明的范围。本说明书中所说明的新颖的装置及方法也能以其它各种方式进行实施。另外,对于本说明书所说明的装置及方法的形态,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。后附的权利要求书以及与其均等的范围意图包含如发明的范围及主旨所包含的此种形态及变化例。

1:阵列芯片

2:电路芯片

11:存储单元阵列

12:绝缘层

13:绝缘层

14:层间绝缘膜

15:绝缘层

16:层间绝缘膜

17:衬底

18:衬底

21:阶梯构造部

22:接触插塞

23:字布线层

24:接触插塞

25:源极布线层

26:接触插塞

27:选择栅极布线层

28:插塞

28a:接触插塞

28b:介层插塞

31:晶体管

32:栅极电极

33:插塞

34:布线层

35:布线层

36:金属垫

37:布线层

41:垫

42:外部连接电极

43:外部连接垫

51:绝缘层

52:阻挡绝缘膜

53:电荷蓄积层

54:隧道绝缘膜

55:通道半导体层

56:磁芯绝缘膜

61:第1绝缘层

62:第1金属垫

71:第2绝缘层

72:第2金属垫

101:第1层间绝缘膜

102:金属布线

102a:金属布线

102b:金属布线

102c:金属布线

102d:金属布线

103:阻止绝缘膜

103a:开口部

104:金属凸块

105:间隔绝缘膜

106:第2层间绝缘膜

106a:开口部

107:介层插塞

107a:势垒金属层

107b:插塞材层

108:金属布线

109:第3层间绝缘膜

111:抗蚀膜

111a:开口部

112:基底层

112a:开口部

113:抗蚀膜

113a:开口部

121:第1芯材线

122:第2芯材线。

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置

- 半导体装置的制造方法、显示装置的制造方法、半导体装置、半导体元件的制造方法以及半导体元件