一种用于半桥隔离变换器的过流保护电路

文献发布时间:2023-06-19 19:37:02

技术领域

本发明属于电源管理集成电路技术领域,具体涉及一种用于半桥隔离变换器的过流保护电路。

背景技术

在当今社会,随着物联网技术的不断发展,在各种应用场景下涌现出了一大批新的电子设备,在多种多样的应用场景要求下,对各种电子设备中的电源管理系统的安全性,稳定性和可靠性提出了越来越高的要求。而在各种类型的电源管理产品中,隔离型变换器因为其具有电气隔离的特点,在安全性和可靠性上面天然有着巨大的优势,现已经成为了多种场合下的必选方案。在各种隔离变换器中,半桥变换器是一种常见的类型,在中等功率应用场景下各项指标都较为均衡,因此在当前是一种热门的拓扑。对半桥变换器进行控制的电源IC,如同当前市场上的主流电源IC一样,通常都会设置过流保护电路,以应对系统可能发生的过流行为。在通常的电源IC中,一旦检测到过流发生,就会立刻关断上管以停止对输出继续充电,并在随后的数个周期内每周期仅仅维持一个最小的上管开启时间,直到检测到过流现象消失才会恢复芯片正常工作。但对于半桥变换器拓扑而言,这样的做法可能会带来一些问题。在检测到过流关断上管之后,在下一个周期如果依照传统方案只维持最小开启时间的话,因为半桥变换器对主边变压器正负两个方向交替充电的特点,这样就会导致变压器主边在前后两个周期内的充电时间不一致,因为人们无法确定过流事件可能出现的时间节点,所以这两个充电时间有可能相差比较大,这就会导致变压器主边发生磁偏甚至出现磁饱和的现象。对于半桥变换器的控制IC来说,一般的过流保护电路无法解决这个隐患。

发明内容

针对上述关于半桥变换器过流保护设计的难题,本发明设计了一种专门用于解决半桥变换器在过流保护阶段可能出现磁饱和问题的电路。该电路在半桥变换器触发过流保护后,依然会立即关闭上管以避免过流的进一步加剧,但在下一个周期时,上管将不会像传统的过流保护机制那样仅仅开启一个最小时间,而是开启与上个周期相同的时间,这样就保证了变压器主边在过流期间的前后两个周期内在相反的方向依然充电相同的时间,有效地避免了变压器主边可能出现的磁饱和问题。之后如果过流现象依然持续,则保证之后偶数个周期内上管按照最小导通时间开启,既保证了过流保护的有效性,又保证主边变压器不出现磁饱和现象。

本发明的目的是针对常规的电源IC过流保护电路应用在半桥变换器上可能会出现的磁饱和问题。在传统的过流保护行为机制上增加了适用于半桥变换器特点的额外过流保护机制。使得半桥变换器出现过流现象时的保护问题得到了更好的解决。

本发明的技术方案为:

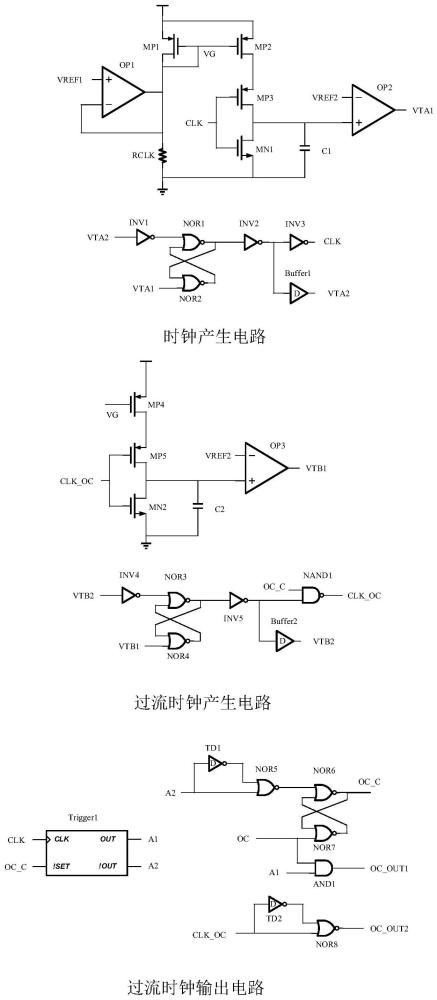

一种用于半桥隔离变换器的过流保护电路,包括时钟产生电路、过流时钟产生电路、过流信号输出电路;

所述时钟产生电路包括第一PMOS管MP1、第二PMOS管MP2、第三PMOS管MP3、第一NMOS管MN1、第一电容C1、频率决定电阻RCLK、第一运放OP1、第二运放OP2、第一反相器INV1、第二反相器INV2、第三反相器INV3、第一或非门NOR1、第二或非门NOR2、第一延迟缓冲器Buffer1;所述第一运放OP1的正端接第一基准电压VREF1,负端接输出端,输出通过接频率决定电阻RCLK的一端和第一PMOS管MP1、第二PMOS管MP2的栅极;第一PMOS管MP1的源极接电源;第二PMOS管的源极接电源,其漏极接第三PMOS管的源极;第三PMOS管的栅极接第一时钟信号,其漏极接第一NMOS管的漏极、第一电容C1的一端、第二运放OP2的正端;第一NMOS管MN1的栅极接第一时钟信号,第一NMOS管MN1的源极、第一电容C1的另一端、频率决定电阻RCLK的另一端接地;第二运放OP2的负端接第二基准电压,其输出端接第二或非门NOR2的一个输入端;第二或非门NOR2的另一个输入端接第一或非门NOR1的输出端;第一或非门NOR1的一个输入端接第二或非门NOR2的输出端,第一或非门的另一个输入端接第一反相器INV1的输出端;第一反相器INV1的输入端接第一延迟缓冲器Buffer1的输出端;第二反相器INV2的输入端接第一或非门NOR1的输出端,第二反相器INV2的输出端接第三反相器INV3的输入端和第一延迟缓冲器Buffer1的输入端;第三反相器INV3的输出端输出第一时钟信号;

所述过流时钟产生电路部分包括第四PMOS管MP4、第五PMOS管MP5、第二NMOS管MN2、第二电容C2、第三运放OP3、第四反相器INV4、第五反相器INV5、第三或非门NOR3、第四或非门NOR4、第一与非门NAND1、第二延迟缓冲器Buffer2;第四PMOS管MP4的源极接电源,其栅极接第一运放OP1的输出端;第五PMOS管MP5的源极接第四PMOS管MP4的漏极,第五PMOS管MP5的栅极接第二时钟信号,第五PMOS管的漏极接第二NMOS管的漏极、第二电容C2的一端、第三运放OP3的正端;第二NMOS管MN2的栅极接第二时钟信号,其源极和第二电容C2的另一端接地;第三运放OP3的负端接第二基准电压,其输出端接第四或非门NOR4的一个输入端;第四或非门NOR4的另一个输入端接第三或非门NOR3的输出端;第三或非门NOR3的一个输入端接第四或非门NOR4的输出端,第三或非门NOR3的另一个输入端接第四反相器INV4的输出端;第四反相器INV4的输入端接第二延迟缓冲器Buffer2的输出端;第五反相器INV5的输入端接第三或非门NOR3的输出端,第五反相器INV5的输出端接第二延迟缓冲器Buffer2的输入端和第一与非门NAND1的一个输入端,第一与非门NAND1的另一个输入端连接过流信号输出电路,第一与非门NAND1的输出端输出第二时钟信号;

所述过流信号输出电路包括第一触发器Trigger1、第一延迟反相器TD1、第二延迟反相器TD2、第五或非门NOR5、第六或非门NOR6、第七或非门NOR7、第八或非门NOR8、第一与门AND1;第一触发器Trigger1的时钟端接第一时钟信号,为正边沿触发,其复位信号接第二过流检测信号,低电平有效,第一触发器Trigger1的两个输出端OUT和!OUT分别输出第一触发信号和第二触发信号,在复位阶段分别为高电平和低电平;第一延迟反相器TD1的输入端和第五或非门NOR5的一个输入端接第二触发信号,第五或非门NOR5的输出端接第六或非门NOR6的一个输入端,第六或非门NOR6的另一个输入端接第七或非门NOR7的输出端,第六或非门NOR6的输出端输出第二过流检测信号;第七或非门NOR7的一个输入端接第六或非门NOR6的输出端,第七或非门NOR7的另一个输入端接第一过流检测信号;第一与门AND1的一个输入端接第一过流检测信号,第一与门AND1的另一个输入端接第一触发信号,第一与门的输出端输出第一过流信号;第二延迟反相器TD2的输入端和第八或非门NOR8的一个输入端接第二时钟信号,第二延迟反相器TD2的输出端接第八或非门NOR8的另一个输入端,第八或非门NOR8的输出端输出第二过流信号;所述第一过流检测信号为从而半桥隔离变换器中检测到的过流信号;所述第一过流信号和第二过流信号均用于控制半桥隔离变换器中上管的关断,并且均为高电平有效。

本发明的有益效果为,通过电阻编程控制时钟的周期,顺带控制了过流发生时对周期的记录,从而在发生过流的时刻能够保证下一个周期的上管开启时间能够对应上过流发生周期的上管开启时间。在对系统进行过流保护的同时使得变压器主边能够一直保持磁平衡。

附图说明

图1本发明提出的适用于半桥变换器的过流保护具体电路。

图2本发明提出的电路产生的时钟波形示意。

图3本发明提出的电路在应用时的具体波形效果。

具体实施方式

下面结合附图,对本发明技术方案进行详细描述:

本发明的技术方案包括:时钟产生电路部分,过流时钟产生电路部分,过流信号输出电路部分共三部分组成,具体电路结构如图1所示:

时钟产生电路部分包括,第一PMOS管MP1、第二PMOS管MP2、第三PMOS管MP3、第一NMOS管MN1、第一电容C1、频率决定电阻RCLK、第一运放OP1、第二运放OP2、第一反相器INV1、第二反相器INV2、第三反相器INV3、第一或非门NOR1、第二或非门NOR2、第一延迟缓冲器Buffer1。具体链接关系为:运放OP1连接为buffer形式,正端输入电位VREF1,输出接RCLK到地,输出上端接二极管连接的MP1,MP1的栅极为VG,VG与MP2栅极连接,作为电流镜。从电源到地依次连接MP2,MP3,MN1,MP3和MN1的栅极接CLK信号。MN1的漏端下挂C1到地,并接入OP2的正端,OP2的负端接VREF2,输出信号为VTA1,。在这里OP1和OP2均可用通用运放代替。数字部分NOR1和NOR2接成RS锁存器,VTA2信号接INV1后接入NOR1端的输入,VTA1信号接NOR2端的输入,NOR1的输出作为RS锁存器的输出,其后接INV2,INV2的输出并联出两条线,分别接INV3输出CLK信号和接Buffer1输出VTA2信号。

过流时钟产生电路部分包括,第四PMOS管MP4、第五PMOS管MP5、第二NMOS管MN2、第二电容C2、第三运放OP3、第四反相器INV4、第五反相器INV5、第三或非门NOR3、第四或非门NOR4、第一与非门NAND1、第二延迟缓冲器Buffer2。具体链接关系为:从电源到地依次连接MP4,MP5,MN2,MP4的栅极接VG电位,MP5和MN2的栅极接CLK_OC信号。MN2的漏端下挂C2到地,并接入OP3的正端,OP3的负端接VREF2,输出信号为VTB1,。在这里OP3可用通用运放代替。数字部分NOR3和NOR4接成RS锁存器,VTB2信号接INV4后接入NOR3端的输入,VTB1信号接NOR4端的输入,NOR3的输出作为RS锁存器的输出,其后接INV5,INV5的输出并联出两条线,分别接NAND1的一端并输出CLK_OC信号和接Buffer2输出VTB2信号。NAND1的另一个输入端接OC_C。

过流信号输出电路部分包括,第一触发器Trigger1、第一延迟反相器TD1、第二延迟反相器TD2、第五或非门NOR5、第六或非门NOR6、第七或非门NOR7、第八或非门NOR8、第一与门AND1。具体链接关系为:第一触发器Trigger1的时钟端接CLK信号,正边沿触发,复位信号接OC_C信号,低电平有效,两个输出OUT和!OUT分别接A1和A2信号,在复位阶段分别为高电平和低电平。NOR6和NOR7组成RS锁存器,A2信号经过TD1得到的信号与A2信号本身作为NOR5的输入,NOR5输出端接RS锁存器NOR6一侧的输入,NOR6的输出作为整个RS锁存器的输出输出OC_C信号,NOR7一侧的输入为OC信号。OC和A1信号输入到AND1,AND1输出OC_OUT1信号。CLK_OC信号经过TD2得到的信号与CLK_OC信号本身作为NOR8的输入,NOR8输出OC_OUT2信号。

在第一部分时钟产生电路,运放OP1进行钳位使得RCLK上流过特定的电流,这个电流可以通过控制RCLK的大小来进行调节。这个电流流经MP1再通过电流镜MP2,通过这个电流的大小控制给电容C1充电的速度,在给电容C1充电的时段,VTA1保持为低,直到C1上的电位增加到一定程度之后VTA1转为高。VTA1转为高电平之后触发CLK为高,同时也触发VTA2经过一小段时间之后为低,变低后的VTA2将再次触发RS锁存器使得CLK为低,这就形成了一个完整的时钟周期,其中CLK即为时钟信号,其低电平时间是电流电容C1的充电时间,较长;而高电平时间是Buffer1的延迟时间,这个时间较短。所得的具体时钟波形在图2中展示出来。

接着是第二部分的过流时钟产生电路部分,这部分主要适用于产生与先前产生的时钟周期相同延时的过流指示信号。在正常情况下,OC_C信号一直保持为低,这就使得CLK_OC信号一直保持为高,这部分电路不工作。而当过流发生时,OC_C保持为高,表示着过流状态的持续,CLK_OC为低,激活整个系统开始工作。这时该系统将经过与先前的时钟产生电路相同的工作过程,如果保证各个电路参数相同,则CLK_OC将经历一个先为低后为高的一段时钟周期,且这个时钟周期降与先前产生的CLK信号的周期相同,时钟周期结束标志是CLK_OC翻低,这个动作将会对下个周期上管的关断有作用。在第三部分讲述。

第三部分的电路负责将先前产生的信号转化为每个周期关断上管的标志信号。最原始的过流信号为OC,OC变高标志着在外部的系统中过流状况已经发生。这时OC_C翻高,表示过流状况的持续性,同时OC_OUT1立即翻高,送入更后续的逻辑电路中控制上管关断,以避免过流状况的进一步恶化,这表示着第一次因为过流关断上管。在这个时钟周期中,上管就已经关断了。而在下个时钟周期后,因为CLK有翻高的过程,将通过触发器使得A1翻低,将OC_OUT1锁住不再翻高。与此同时,第二部分电路中产生的CLK_OC的下降沿将触发OC_OUT2翻高,因为CLK_OC的下降沿时刻与第一次过流发生的时刻正好相差一个时钟周期,因此当OC_OUT2翻高时,第二个时钟周期内的上管开启时间也将会与第一个时钟周期内的上管开启时间相同,此时正好有OC_OUT2翻高,这就使得这一对周期的上管开启时间都是相同的。在下一个时钟周期到来后,CLK又有高电平脉冲,通过触发器使得A2翻低,A2翻低又产生了高电平脉冲对NOR6和NOR7形成的RS触发器起作用,将OC_C翻低,这样一对过流周期就结束了。等到下一个周期如果还是过流状态,因为一开始就检测到过流,那么下一对周期将会是一个上管仅仅维持最小开启时间的周期,直到电路恢复正常。过流保护的效果在图3中展示。

综上所述,使用这种新的过流保护电路可以在对电路进行正常的过流保护的同时保证两个周期内上管开启时间的一致性,保证主边变压器不会出现磁偏。非常适合用于半桥变换器的控制IC之中。