具有多孔传热元件的篡改响应组件

文献发布时间:2024-01-17 01:21:27

背景技术

许多活动需要安全的电子通信。为了便于安全电子通信,加密/解密系统可以在连接到通信网络的设备所包括的电子部件或电路板组件上实现。这种电子部件是针对恶意分子有吸引力的目标,因为它可能包含用于解密所截取的消息或用于编码欺诈性消息的代码或密钥。为了防止这种情况,电子部件可以安装在外壳中,然后将其包裹在安全传感器中并用聚氨酯树脂封装。在一个或多个实施例中,安全传感器可以是绝缘材料的网或片,其上制造有电路元件,例如紧密间隔的导线。如果传感器被撕裂,则电路元件被扰乱,并且撕裂可被感测以便生成警报信号。可以将警报信号传递到监视器电路,以便揭示对组件完整性的攻击,从而触发擦除被存储在电子部件内的加密/解密密钥。

发明内容

在本发明的一个或多个方面,本文提供了一种防篡改(tamper-proof)组件,其包括电路板、安装到电路板的外壳组件、以及压力传感器。电路板包括电子部件,并且外壳组件被安装到电路板以将电子部件包封在安全容积内。外壳组件包括导热外壳和多孔传热元件。导热外壳在导热外壳内包括密封内部隔室(compartment),并且导热外壳被安装到电路板。多孔传热元件位于导热外壳的密封内部隔室内,并且多孔传热元件的尺寸和位置被设计成便于将来自电子部件的热传导穿过导热外壳的密封内部隔室。压力传感器感测导热外壳的密封内部隔室内的压力以便于识别指示篡改事件的压力变化。

在本发明的另一方面,提供了一种篡改响应组件,其包括电路板、多个电子部件、第一外壳组件、第二外壳组件和压力传感器。电路板包括第一侧和第二侧,第一侧和第二侧是电路板的相对侧。多个电子部件包括耦接到电路板的第一侧的至少一个第一电子部件和耦接到电路板的第二侧的至少一个第二电子部件。第一外壳组件被安装到电路板的第一侧以将耦接到电路板的第一侧的至少一个第一电子部件包封在安全容积的第一腔室内。第一外壳组件包括导热外壳和多孔传热元件。导热外壳在导热外壳内具有密封内部隔室,并且导热外壳被安装到电路板的第一侧。多孔传热元件位于导热外壳的密封内部隔室内并且其尺寸和位置被设计成便于将来自至少一个第一电子部件的热传导穿过导热外壳的密封内部隔室。第二外壳组件被安装到电路板的第二侧以将耦接到电路板的第二侧的至少一个第二电子隔室包封在安全容积的第二腔室内。压力传感器感测第一外壳组件的导热外壳的密封内部隔室内的压力,以便于识别指示篡改事件的压力变化。

在本发明的又一方面,提供了一种制造篡改响应组件的方法。该方法包括:提供具有电子部件的电路板,以及将外壳组件安装到电路板以将电子部件包封在安全容积内。外壳组件包括导热外壳和多孔传热元件。导热外壳在导热外壳内包括密封内部隔室,并且导热外壳被安装到电路板。多孔传热元件位于导热外壳的密封内部隔室内并且其尺寸和位置被设计成便于将来自电子部件的热传导穿过导热外壳的密封内部隔室。该方法还包括提供压力传感器以感测导热外壳的密封内部隔室内的压力,以便于识别指示篡改事件的压力变化。

通过本文所述的技术实现了附加的特征和优点。本发明的其它实施例和方面在本文中详细描述,并且被认为是所要求保护的方面的一部分。

附图说明

现在将仅通过示例并参考以下附图来描述本发明的优选实施例:

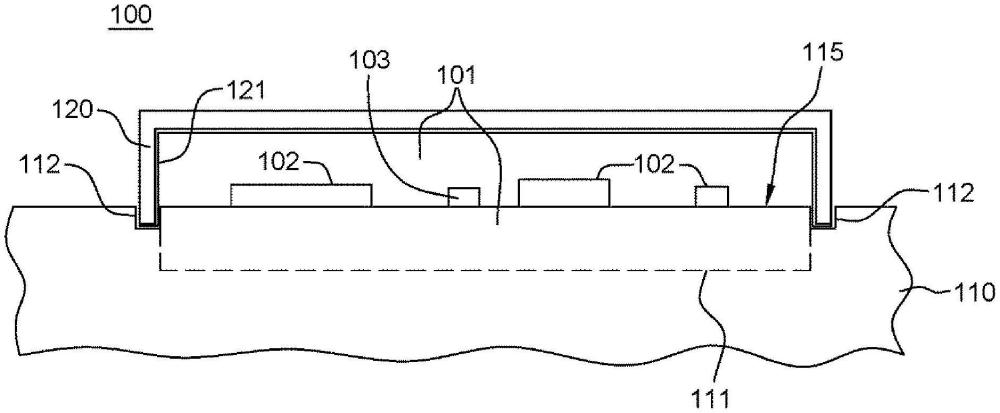

图1A是根据本发明的一个或多个方面的(部分地)包括外壳和具有嵌入式篡改检测电路的多层电路板的防篡改电子封装或篡改响应组件的一个实施例的截面正视图;

图1B是根据本发明的一个或多个方面的图1A的多层电路板的俯视平面图;

图2示出了根据本发明的一个或多个方面的篡改响应传感器的一个实施例,其中导线至少部分地形成至少一个篡改检测电路;

图3是根据本发明的一个或多个方面的图1A和1B的篡改响应组件的更详细实施例的局部截面正视图,该篡改响应组件(部分地)包括外壳和具有嵌入式篡改检测电路的多层电路板;

图4示出了根据本发明的一个或多个方面的制造具有嵌入式篡改检测电路的多层电路板的过程的一个实施例;

图5是根据本发明的一个或多个方面的篡改响应组件的一个实施例的等轴视图;

图6A是根据本发明的一个或多个方面的具有多孔传热元件的篡改响应组件(例如图5所示)的另一实施例的横截面正视图;

图6B是根据本发明的一个或多个方面的沿线6B截取的图6A的篡改响应组件的局部放大图;

图7A-7E示出了根据本发明的一个或多个方面的制造用于诸如图6A和6B所示的具有多孔传热元件的篡改响应组件的外壳组件的过程的一个实施例;

图8A和8B示出了根据本发明的一个或多个方面的制造用于在诸如图6A和6B所示的外壳组件中使用的多孔传热元件的过程的一个实施例;

图9是根据本发明的一个或多个方面的具有一个或多个多孔传热元件的篡改响应组件的又一实施例的截面正视图;

图10A和10B部分地示出了根据本发明的一个或多个方面的制造用于具有多孔传热元件的篡改响应组件的外壳组件的过程的一个实施例;以及

图11是根据本发明的一个或多个方面的具有多孔传热元件的篡改响应组件的另一实施例的局部截面图。

具体实施方式

下面参考附图中示出的非限制性示例更全面地解释本发明的各方面及其某些特征、优点和细节。省略了对公知材料、制造工具、处理技术等的描述,以免不必要地使本发明在细节上变得模糊。然而,应当理解,详细描述和特定示例虽然指示了本发明的各方面,但仅以示例的方式给出,而不是以限制的方式给出。对于本公开,在本发明的基本概念的范围内的各种替换、变型、添加和/或布置对于本领域技术人员将是显而易见的。还应注意,下面参考附图,为了便于理解,附图没有按比例绘制,其中在不同附图中使用的相同附图标记表示相同或相似的部件。而且,应注意,本文公开了许多发明方面和特征,并且除非另外不一致,否则每个公开的方面或特征可根据需要与任何其它公开的方面或特征组合,以用于例如篡改响应组件的特定应用。

图1A和1B示出了防篡改电子封装或篡改响应组件100的一个实施例,该防篡改电子封装或篡改响应组件100包括一个或多个电子部件,例如耦接到多层电路板110的电子器件(或元件)102和/或电路115。

共同参考图1A和1B,电路115位于多层电路板110上或嵌入在其中,该多层电路板110还具有嵌入的篡改响应传感器111,该传感器111便于部分地限定与多层电路板110相关联的安全容积101,该安全容积101(在一个或多个实施例中)延伸到多层电路板110中。具体地,在图1A和1B的实施例中,安全容积101可以部分地存在于多层电路板110内,并且部分地存在于多层电路板110上方。一个或多个电子器件102被安装到安全容积101内的多层电路板110,并且可以包括例如一个或多个加密模块和/或解密模块和/或相关联的部件,以在防篡改电子封装内受到保护。在一个或多个实现方式中,要被保护的一个或多个电子部件可以包括例如计算机系统的安全通信卡中的部件。

防篡改电子封装100还包括外壳120,例如基座型外壳,其在例如形成于多层电路板110的上表面内的连续凹槽(或沟槽)112内被安装到多层电路板110,并且例如经由设置在连续凹槽112内的结构粘合剂而被固定到多层电路板110。在一个或多个实施例中,外壳120可以由导热材料制成,并且作为散热器操作,以便于对安全容积内的一个或多个电子部件102进行冷却。安全网格或篡改响应传感器121可以与外壳120相关联,例如,围绕外壳120的内表面包裹(wrap),以便于与嵌入在多层电路板110内的篡改响应传感器111组合地限定安全容积101。在一个或多个其他实现方式中,可以使用例如诸如环氧树脂或其他粘合剂的接合材料将外壳120牢固地固定到多层电路板110的表面(没有连续的凹槽)。

简言之,在一个或多个示例中,篡改响应传感器121可以包括一个或多个篡改检测层,篡改检测层包括设置在结构层的一侧或两侧上的电路线或迹线,在一个或多个实现方式中,结构层可以是柔性绝缘层或膜。柔性层的一侧或两侧上的电路线可以具有线宽并且具有节距或线到线的间隔,使得在任何点处对层的刺穿导致对一个或多个电路线或迹线的损伤。在一个或多个实现方式中,电路线可以限定一个或多个导体,该一个或多个导体可以在网络中电连接到例如对线上的电阻进行监视的外壳监视器或检测器103。检测到由切割或损伤一个或多个线引起的电阻变化将导致自动擦除安全容积内的信息。篡改响应传感器的导线可以是任何期望的图案,诸如正弦图案,以使得更难以破坏篡改检测层而不被检测到。

对于电阻监视,可以采用各种材料来形成电路线。例如,电路线可以由金属或金属合金形成,例如铜或银,或者可以由本征导电聚合物、碳墨、或者例如由(美国)加利福尼亚州卡尔弗城的Omega Technologies公司提供的

如上所述,在一个或多个实现方式中,对外壳120的内表面进行加衬的或者甚至被直接印刷到形成在外壳120的内表面上方的一个或多个层上的篡改响应传感器的电路线可以被连接以限定一个或多个检测网络。

如果在外壳120的内表面上方使用柔性层,则柔性层可由结晶聚合物材料形成。例如,结晶聚合物可以包括聚偏氟乙烯(PVDF)或Kapton或者其它结晶聚合物材料。有利地,结晶聚合物可以被制造得更薄,同时仍然维持柔性衬底的结构完整性,这也允许增强的折叠以及折叠之后传感器的更高可靠性。

如图1B所示,可以在多层电路板110内提供一个或多个外部电路连接过孔113,用于电连接到安全容积101内的一个或多个电子部件。这些一个或多个外部电路连接过孔113可以电连接到被嵌入在多层电路板110内并且例如延伸到安全容积101中的(或下方的)安全基底区域中的一个或多个外部信号线或平面(未示出)。通过耦接到多层电路板110内的这种外部信号线或平面,可以提供到和来自安全容积101的电连接。

如上所述,安全容积101的尺寸可以被确定为容纳一个或多个要保护的电子部件,并且可以被构造为延伸到多层电路板110中。在一个或多个实现方式中,多层电路板110包括在板中限定的安全容积101内的电互连,以例如用于将嵌入式篡改响应传感器111的一个或多个篡改检测层电连接到相关联的监视器电路,该监视器电路与例如一个或多个子卡一起也布置在安全容积101内,所述子卡诸如存储器DIMM、PCIe卡、处理器卡等。

注意,图1A和1B中示出的封装实施例仅作为示例给出。可以采用外壳120或多层电路板110的其它配置,和/或可以使用耦接外壳120和多层电路板110的其它方法。例如,在一个或多个替代实现方式中,可以使用例如诸如环氧树脂或其他粘合剂的结构接合材料将外壳120牢固地固定到多层电路板110的上表面(而没有连续的凹槽)。

图2示出了篡改响应传感器200或安全传感器的篡改检测层205(或激光和穿刺响应层)的一个实施例的一部分。在图2中,篡改检测层205包括设置在诸如柔性层202的层的一个或两个相对侧上的电路线或迹线201,在一个或多个实施例中,该层可以是柔性绝缘层或膜。

图2示出了在例如柔性层202的一侧上的电路线201,其中膜的相对侧上的迹线例如具有相同的图案,但是(在一个或多个实施例中)偏移成位于电路线201之间的间隔203的正下方。如下所述,在柔性层的一侧上的电路线可以具有线宽W

如上所述,随着入侵技术的持续演化,反入侵技术需要继续改善以保持领先。在一个或多个实现方式中,图2的以上概述的篡改响应传感器200可覆盖外壳的内表面或对该内表面进行加衬,以在要保护的至少一个电子部件周围提供安全容积。此外,篡改响应传感器,或更具体地,传感器的篡改检测电路,可以嵌入到下面描述的多层电路板内。

还应注意,当使用电阻监视来实现时,可有利地采用各种材料来形成电路线。例如,电路线可以由印刷到柔性层202的堆叠中的一个或多个柔性层202的一个或两个相对侧上的导电油墨(诸如含碳的导电油墨)形成。替代地,可使用金属或金属合金来形成电路线,例如铜、银、本征导电聚合物、碳墨或者例如由(美国)加利福尼亚州卡尔弗城的OmegaTechnologies公司提供的

通过进一步的示例,图3示出了防篡改电子封装100的更详细实施例的局部截面正视图,并且具体地,示出了外壳120固定到其上的多层电路板110的局部截面正视图。在该配置中,嵌入式篡改响应传感器包括多个篡改检测层,该多个篡改检测层包括例如至少一个篡改检测垫(或基底)层300和至少一个篡改检测框架301。在所描绘的示例中,仅通过示例的方式示出了两个篡改检测垫层300和两个篡改检测框架301。最下面的篡改检测垫层300可以是完全在多层电路板110内和/或上方限定的安全容积下方延伸的连续感测或检测层。如果需要,安全容积101下方的一个或两个篡改检测垫层300可以被分成多个电路区。在每个篡改检测垫层内,或者更具体地,在每个篡改检测垫层的每个电路区内,可以以任何期望的配置提供多个电路或导电迹线。此外,篡改检测层内的导电迹线可以被实现为例如电阻层。

如图所示,在一个实施例中,一个或多个外部信号线或平面305可进入两个篡改检测垫层300之间的安全容积101,然后通过按照任何期望位置和图案布置的一个或多个导电过孔向上电连接到安全容积101。在所示的配置中,一个或多个篡改检测框架301至少设置在由容纳外壳120的基底的连续凹槽112限定的区域内部。与外壳120相关联的篡改响应传感器121、篡改检测框架301和篡改检测垫层300一起限定安全容积101,该安全容积101可部分地延伸到多层电路板110中。在部分地在多层电路板110内限定安全容积101的情况下,外部信号线305可以被牢固地电连接到例如安装到安全容积101内的多层电路板110的一个或多个电子部件或电连接到多层电路板110的一个或多个电子部件。此外,安全容积101可以例如经由适当的监视器电路来容纳多个篡改检测层300、301的导电迹线的电互连。

通过将篡改检测垫层300(以及如果需要,篡改检测框架301)向外延伸超过外壳120的外围,可以提供附加的安全性。以这种方式,由于攻击将需要清除例如篡改检测垫层300、外壳120以及嵌入式篡改检测电路的篡改检测框架301,因此在外壳120和多层电路板110之间的界面处,攻击的线可能变得更加困难。

图1A-2的多层电路板110的多种变化是可能的。例如,在一个实施例中,嵌入式篡改检测电路可包括诸如以上所描述的一个或多个篡改检测垫层300和一个或多个篡改检测框架301、以及三板结构,该三板结构包括夹在上接地平面与下接地面之间的一个或多个外部信号线或外部信号层。在此配置中,可便于到安全容积和来自安全容积的信号的高速传递,且明确地说,可便于到驻留在安全容积内的一个或多个电子部件和来自驻留在安全容积内的一个或多个电子部件的信号的高速传递。

还应注意,一旦限定了安全容积,则根据实现方式,可以根据需要使多层电路板110的层之间的安全容积内的导电过孔对准或偏移。导电过孔的对准可以有助于例如提供最短的连接路径,而使层之间的导电过孔偏移可以通过使穿过或围绕多个篡改检测层中的一个或多个篡改检测层对安全容积的攻击更困难来进一步增强防篡改电子封装的安全性。

在电子电路或电子封装的多层电路板内形成的嵌入式篡改检测电路的篡改检测层可包括在迹线端点处的例如相应的输入和输出接触或过孔的组之间形成的多个导电迹线或线。可采用任何图案和任何数量的导电迹线或电路来限定篡改检测层或篡改检测层内的篡改检测电路区。例如4、6、8等的导电迹线可以在到那些导电迹线的相应的输入和输出接触的组之间在给定的篡改检测层或电路区域内平行地(或以其它方式)形成。

在一个或多个实现方式中,多层电路板可以是例如通过构建板的多个层而形成的多层布线板或印刷电路板或卡。图4示出了用于在这样的多层电路板内形成篡改检测层并对其进行图案化的一个实施例。

如图4所示,在一个或多个实现方式中,诸如本文所公开的篡改检测垫层或篡改检测框架等的篡改检测层可通过提供材料堆叠来形成,该材料堆叠至少部分地包括诸如预浸(或预浸渍)材料层的结构层401、用于限定期望的迹线图案的迹线材料层402、以及要被图案化以限定导电接触或过孔的上覆导电材料层403,其中该导电接触或过孔电连接到迹线材料层402内(例如,在迹线端点处)形成的迹线图案。在一个或多个实现方式中,迹线材料层402可包括镍磷(NiP),而上覆导电层403可包括铜。注意,这些材料仅通过示例的方式来标识,并且在构建(build-up)400内可以使用其它迹线和/或导电材料。

在构建400上方提供第一光致抗蚀剂404,并用一个或多个开口405对第一光致抗蚀剂404进行图案化,通过该开口可以蚀刻上覆导电层403。取决于所采用的材料和所使用的蚀刻工艺,可期望第二蚀刻工艺来去除迹线材料层402的部分以限定本发明的篡改检测层的导电迹线。然后,可以去除第一光致抗蚀剂404,并且在导电层403特征上方提供第二光致抗蚀剂404’以保留例如输入和输出接触。然后蚀刻导电层403的暴露部分,并且可以去除第二光致抗蚀剂404’,其中例如用粘合剂(或预浸料)406填充该层中的任何开口,并且提供下一构建层,如图所示。注意,在该实现方式中,蚀刻掉大部分的上覆导电层403,而仅在期望的位置保留导电接触或过孔,例如,在通过图案化迹线材料层402而在层内形成的迹线的端点处保留。注意,可以采用各种材料中的任何材料来形成篡改检测层内的导线或迹线。镍磷(NiP)作为材料是特别有利的,因为它能抵抗通过软钎焊(solder)或者使用导电粘合剂来结合到其上的接触,使得在试图穿透到电子电路的受保护的安全容积中期间,更难从一个电路或迹线桥接到下一个电路或迹线。可以采用的其它材料包括由(美国)加利福尼亚州卡尔弗城的Omega Technologies公司提供的

篡改检测层内的迹线或电路以及具体地嵌入式篡改检测电路的篡改检测电路区连同监视外壳的篡改检测器可以电连接,以检测或比较例如在防篡改电子封装的安全容积101(图1A)内提供的电路。检测或监视器电路可包括位于安全容积101(图1A)内部(例如位于由篡改检测框架301(图3)和篡改检测垫层300(图3)所限定的安全容积内)的常规印刷布线路板电互连和各种桥接器或比较电路。

注意,有利地,不同篡改检测层上的不同篡改检测电路区可电互连到例如相同的检测电路中。因此,大量互连配置中的任何配置都是可能的。例如,如果两个篡改检测垫层中的每一个包含30个篡改检测电路区,并且两个篡改检测框架中的每一个包含4个篡改检测电路区,则例如,所得到的68个篡改检测电路区可以在安全容积内以任何配置被连接,以在针对电阻或篡改的变化而被监视的安全容积内创建期望布置的电路网络。注意,在这方面,篡改响应传感器的电源或电池可以位于安全容积的内部或外部,其中传感器被配置成如果电源或电池被篡改则断开(trip)并破坏任何受保护或关键的数据。

作为进一步的示例,图5示出了防篡改电子封装的一个实施例的等距视图,其中外壳500(例如图1A的外壳120,或者下面结合图6A-11描述的外壳)被示出为被密封到多层电路板110以限定围绕一个或多个电子部件的安全容积。在所示的实施例中,外壳500由导热材料形成,并且包括主表面501和具有侧壁角503的侧壁502。外壳500的内表面将包括分别对应于主表面501和侧壁502的内主表面和内侧壁表面,其中在一个实施例中,内主表面和内侧壁表面被诸如以上结合图1A-2描述的实施例中的一个或多个篡改响应传感器覆盖。如在该实施例中所描述的,用于篡改响应传感器的电源505或电池可以位于安全容积的外部,其中篡改检测器被配置为如果电源或电池被篡改则断开并破坏任何受保护的或关键的数据。外壳500可以粘附到多层电路板110,如本文所述,该多层电路板110可以包括其自身的篡改保护。

随着计算系统中加密和解密的使用增加,诸如本文所述的篡改响应组件内的电力使用预期继续增加。结果,篡改响应组件内的散热成为问题。对于如图1A-2所示的设计,在产生热的电子部件和外部导热外壳之间存在具有潜在高热阻抗的多个层。鉴于这种约束,本文公开了新颖的篡改响应组件和制造方法,其提供增强的防篡改保护和从安全容积内的电子部件到例如散热器的增强的热传递,散热器诸如外壳的外表面上的多个空气冷却鳍。

当考虑防篡改封装时,电子封装需要实现限定的防篡改要求,例如在作为美国政府计算机安全标准的国家标准与技术研究院(NIST)出版物FIPS 140-2中提出的用于认证密码模块的那些要求。NIST FIPS 140-2限定了四个安全级别,称为级别1到级别4,其中安全级别1提供最低的安全级别,而安全级别4提供最高的安全级别。在安全级别4,提供物理安全机制以建立围绕密码模块的完整保护包络(envelope),目的是检测物理访问的任何未授权尝试并对其作出响应。从任何方向穿透密码模块外壳都具有非常高的被检测到的概率,导致所有纯文本关键安全参数(CSP)的立即归零。

为了解决不断改善的防入侵技术的需求,以及提供更高性能的加密/解密功能,需要增强用于一个或多个电子部件或组件的安全级别4防篡改、显篡改(tamper-evident)封装。

下面参照图6A-11公开的是各种防篡改组件和制造方法,其提供例如安全级别4安全容积并且提供在安全容积内生成的热通过外壳向外的增强传递,该安全容积用于容纳一个或多个电子部件,例如一个或多个加密和/或解密模块以及例如要保护的通信卡或其它电子部件的相关联元件。

作为示例,图6A和6B示出了根据本文公开的一个或多个方面的篡改响应组件600的一个实施例。共同参考图6A和6B,篡改响应组件600包括多层电路板610以及耦接到电路板的主表面(例如电路板的上表面)的一个或多个电子部件602。在一个或多个实现方式中,多层电路板610和一个或多个电子部件602类似于以上结合图1A-5描述的多层电路板110和一个或多个电子部件102。例如,在一个实施例中,多层电路板610包括与以上结合图1A-4描述的嵌入式篡改响应传感器111类似的嵌入式篡改响应传感器611。在一个或多个实现方式中,电子部件602包括要被保护的一个或更多个专用集成电路。如图所示,在一个或多个实施例中,可以从多层电路板610提供外围部件互连(PCI)接片613或总线,以连接到多层电路板的内部部件和/或电路。

在一个实施例中,篡改响应组件600包括安装到电路板610的外壳组件,该外壳组件诸如在形成于多层电路板610的上表面内的连续凹槽(或沟槽)612内并且例如经由设置在连续凹槽612内的结构粘合剂625固定到多层电路板610。在一个或多个实施例中,外壳组件包括由导热材料制成的外壳620,例如金属材料,该外壳620作为散热器操作以便于冷却由外壳组件和电路板限定的安全容积601内的电子部件602。在一个或多个实施例中,多个空气冷却鳍或销624从外壳620向外延伸以便于从外壳620散热。

在所示的实施例中,使用压力感测,并且具体地,使用对压力变化或压力差变化的检测来实现篡改检测。这种压力感测方法代替了与图1A-2的外壳的内表面相关联的安全网格或篡改响应传感器。例如,在一个或多个实施例中,外壳620包括位于外壳620的内壁621和外壁622之间的密封的内部隔室或空间623。

在一个实施例中,密封内部隔室623被限定或形成为内壁621和外壁622之间的间隙。如下所述,在一个实施例中,导热外壳620可以由基底导热元件和上部导热元件制成,它们例如通过软钎焊或硬钎焊(braze)632密封在一起,从而形成内壁621和外壁622。在替代的制造方法中,3D打印可以用于形成例如外壳620的一个或多个结构。

还提供了多个压力传感器640、641。在所示的实施例中,压力传感器640被定位成感测外壳620的密封隔室623内的压力,并且压力传感器641被定位成感测安全容积601内的压力,其中监视器电路或模块603也被设置在多层电路板610内或上。压力传感器640、641提供由监视器电路监视的所感测压力数据以识别指示篡改事件的压力变化或压力差变化。例如,当例如试图通过钻穿外壳620来破坏安全容积601时,密封内部隔室623内的压力发生变化。注意,可以以各种方式检测压力变化。例如,在不同时间间隔来自传感器640的传感器数据之间的压力差可以指示篡改事件。替代地,可使用压力传感器640与压力传感器641之间的所感测的压力差来识别指示篡改事件的压力变化。在一个或多个实施例中,密封内部隔室623内的压力将被设定为不同于安全容积601内的压力,如下面进一步解释的。注意,尽管示出为单个压力传感器640,但是如果需要,多个压力传感器可以被设置在密封内部隔室623内和/或安全容积601内。

在一个或多个实现方式中,外壳组件还包括位于密封内部隔室623内的一个或多个多孔传热元件630,每个多个传热元件630相对于相应电子部件来设计尺寸和定位,以便于将来自安全容积601内的相应电子部件602的热传导穿过导热外壳620的密封内部隔室623。热界面材料(TIM)635用于便于从相应电子部件602到内壁621的热传递,并且因此便于穿过多孔传热元件630到外壁622的热传递,以便穿过导热鳍624耗散。如下文进一步讨论的,在一个实施例中,多孔传热元件630包括夹在上部和下部箔801、802(图8A和8B)之间的多孔材料800(图8A),并且在外壳620的密封内部隔室623内,例如在形成于内壁621和外壁622内的相应凹部内,多孔传热元件630粘附到内壁621和外壁622,如图所示。在一个实施例中,多孔传热元件630使用软钎焊或硬钎焊接合633粘附至到内壁和外壁。

有利地,多孔传热元件630是透气的,并且设计有足够的孔隙率,使得试图钻穿外壳620进入多孔传热元件630中导致密封内部隔室623内的压力变化,该压力变化由压力传感器640检测。以这种方式,多孔传热元件维持外壳组件的防篡改功能,同时仍然提供从相应热生成电子部件穿过外壳的密封内部隔室传递的热的高导热性。注意,诸如图6A和6B中所示的篡改响应组件有利地提供了从安全容积601内的热生成电子部件向外通过外壳620的更少的部件层,并因此提供了更少的传热界面。还应注意,在图6A和6B的实现方式中,多孔传热元件630相对于待冷却的相应电子部件而被设计和定位。例如,在一个实现方式中,多孔传热元件覆盖并具有与待冷却的相应电子部件的占用面积基本相同或比其稍大(例如,大25%)的占用面积待冷却的相应电子部件的占用面积。这允许密封内部隔室的大部分保持为空气或气体填充的空间。

图7A-7E示出了制造如图6A和6B所示的外壳组件的过程的一个实施例。如图7A所示,例如通过使用冲压(punch)机或开槽操作来预形成基底导热元件700,以具有形成安全容积的一部分的内部空间701。在一个具体实施例中,通道的内部空间或深度(d)可以例如在4-5mm的范围内。

如图7B所示,基底导热元件可经历进一步的操作,例如进一步的冲压或开槽操作,以形成位置和尺寸被设计成覆盖待冷却的相应电子部件的凹部702和一旦组装就将形成导热外壳的密封内部隔室的一部分的通道或间隙703。此外,施加软钎焊膏和/或硬钎焊膏633、632,软钎焊膏或硬钎焊膏633位于凹部702内以容纳相应的多孔传热元件,并且软钎焊膏或硬钎焊膏632设置成便于将基底导热元件连接到上部导热元件,其中,一旦上部导热元件被连接就形成外壁622的一部分,如图7C和7D所示。注意,如图7C所示,上部导热元件还经历诸如冲压或开槽的操作,以形成从外壁622向外延伸的导热鳍634、以及尺寸和位置被设置成部分地接收相应的多孔传热元件630的一个或多个凹部704。

参照图8A和8B,示出了多孔传热元件630的一个实施例。在该实施例中,多孔传热元件630包括多孔材料800以及上金属箔801和下金属箔802。在一个实现方式中,多孔材料800是烧结金属结构,例如烧结铜块或衬垫,并且上金属箔和下金属箔是上铜箔和下铜箔。可通过烧结金属颗粒形成的多孔材料800包括空隙以便透气。此外,在一个或多个实现方式中,多孔材料800具有与限定密封内部隔室的外壳的内壁与外壁之间的间隙近似相同的厚度。例如,在一个实施例中,在密封内部隔室由内壁和外壁之间的大约2mm的间隙限定的情况下,多孔材料800具有大约2-4mm的厚度。此外,在一个实现方式中,上金属箔和下金属箔801、802可各自具有1mm或更小的厚度。在一个具体的实现方式中,例如烧结金属块的多孔材料具有大约3mm的厚度,并且金属箔具有例如小于1mm的厚度,例如每个大约.5mm。

在一个或多个实施例中,多孔材料是具有开孔的烧结金属结构,其是空气和液体可渗透的。在制造期间,颗粒尺寸和孔尺寸是可控制的,例如,小于50μm尺寸。在一个或多个实施例中,多孔材料具有30%-80%范围内的孔隙率,例如50%的孔隙率。多孔传热元件的热导率可在制造期间通过控制烧结块中金属颗粒的颗粒尺寸和密度来调节。

在一个实现方式中,多孔传热元件630可通过烧结上金属箔和下金属箔801、802之间的多孔材料来制造,如图8B所示。在一个或多个其它实施例中,上金属箔和下金属箔可接合到例如烧结金属块的多孔材料800。有利地,提供上金属箔和下金属箔以防止软钎焊或硬钎焊材料在导热外壳内被接合就位时渗入多孔材料中。这有利地防止了在用于将多孔传热元件630固定到外壳的内壁和外壁的软钎焊或硬钎焊过程期间多孔材料的堵塞。

注意,在一个或多个实现方式中,限定外壳的内壁和外壁的基部导热元件和上部导热元件中的凹部702、704的尺寸被设计为具有基本上容纳软钎焊和/或硬钎焊片或膏以及多孔传热元件的相应金属箔的深度,使得内壁和外壁之间的空间或间隙主要或仅包含多孔材料,这增强了压力传感器检测指示通过多孔传热元件的篡改事件的压力变化的能力。

回到图7D,可以使用软钎焊或硬钎焊工艺来形成外壳,包括在外壳620的内壁621和外壁622之间形成密封内部隔室623。

如图7E所示,外壳组件还可被制造成包括位于密封内部隔室623内的压力传感器640,一个或多个布线711从外壳向外延伸以将压力传感器连接到监视器电路,如图6A所示。在一个实施例中,布线711穿过包括压力密封件710的开口。如图所示,在一个或多个实现方式中,还提供端口720以在将外壳安装到多层电路板之前对内部密封隔室623进行加压或减压。例如,在一个实施例中,内部密封隔室623可被加压至高于大气压的压力,或者在另一实施例中,可被减压至例如低于大气压的压力,或甚至接近真空。一旦加压或减压,端口720就被填充材料721压力密封。

图9-11示出了根据本发明的一个或多个方面的篡改响应组件的进一步的实施例。

在图9的实施例中,示出了篡改响应组件900,其类似于图6A-8的篡改响应组件600,除了在多层电路板610的第二主表面或第二侧上设置第二外壳组件。如图所示,第二外壳组件包括具有内壁921和外壁922的第二外壳920,在内壁921和外壁922之间限定了密封内部隔室923。当第二外壳被安装到多层电路板610的第二侧(例如,在多层电路板的第二侧中的相应沟槽内)时,限定了安全容积的第二腔室901以保护被安装到多层电路板610的第二侧的一个或多个电子部件902。如图所示,在一个或多个实施例中,与篡改响应传感器611类似的篡改响应传感器911在容纳外壳920的沟槽附近被嵌入在多层电路板610内与多层电路板的第二侧相邻。如同外壳620那样,外壳920可以使用例如诸如环氧树脂或其它粘合剂925之类的接合材料被牢固地固定到多层电路板610。注意,在该实施例中,嵌入式篡改响应传感器611、911仅需要占据多层电路板610的在沟槽附近的一部分,例如所示的。第一和第二外壳620、920一起在电路板的相对侧上限定安全容积601、901,并且嵌入式篡改响应传感器防止沿着外壳到板界面的篡改。

在一个或多个实现方式中,以与上述制造导热外壳620类似的方式,安装到多层电路板的第二侧的第二外壳组件也由基部导热元件和上部导热元件形成。如图所示,软钎焊或硬钎焊接合932连接基部导热元件和上部导热元件,其限定外壳的内壁921和外壁922以及内壁与外壁之间的密封内部隔室923。在一个或多个实施例中,外壳900由金属材料形成,以便于从外壳920和多层电路板610的第二侧之间的相应安全容积内散热。注意,实际上,通过将外壳620安装到多层电路板的第一侧并将外壳920安装到多层电路板的第二侧,可以获得单个安全容积。可以在多层电路板内设置一个或多个通孔1000(如图10B所示),使得在多层电路板的第一侧上方的安全容积腔室内的压力和在多层电路板的第二侧上方的安全容积腔室内的压力相等。在一个实施例中,压力传感器940设置在外壳920的密封内部隔室923内,并且压力传感器941设置在安全容积的第二腔室901内,其中布线将压力传感器连接回到与多层电路板610相关联的监视器电路903和/或与多层电路板610耦接的部件,以监视(与监视器电路603一起)安全容积的第一腔室601和第二腔室901与密封内部隔室623、923中的一个或多个之间的压力变化差。

在一个或多个实施例中,钻穿外壳620、920中的一个的任何尝试导致由一个或多个压力传感器检测到的压力变化,该压力变化由监视器电路使用以触发警报,并擦除篡改响应组件内的任何机密的加密和/或解密数据。例如,钻穿外壳620可导致密封内部隔室623内的压力改变,并且由监视器电路来检测,该监视器电路监视与密封内部隔室623和安全容积的第一腔室相关联的压力传感器之间的压力差(见图6A和6B)。钻穿外壳920可以类似地导致密封内部隔室923内的压力相对于安全容积的第二腔室901而改变,这可以由监视器电路检测。

图10A和10B建立在图7A-7E的制造过程上,其中图10A进一步示出了使用与以上结合图7A-7E所述的那些类似的制造过程形成的第二外壳。在该实施例中,如上结合图9所述,外壳920被制造为安装到多层电路板的第二侧。如图所示,第二外壳920包括压力传感器940,其具有从压力传感器延伸穿过内壁中包括压力密封件1010的相应开口的布线1011。此外,填充端口1020被设置在内壁921中,以允许在外壳920的内壁921和外壁922之间的密封内部隔室923的加压或减压。一旦加压或减压,端口密封件1021被施加以压力密封填充端口1020。注意,代替向密封内部隔室623、923施加高压(例如,高于1ATM压力),可以在篡改响应组件中使用低压(例如,低于1ATM压力)或真空,以便于本文描述的压力感测篡改检测保护。有利地,通过在密封内部隔室内提供较低的压力,在不同的操作温度下隔室压力的变化将较低。

图11是根据本发明的一个或多个方面的另一篡改响应组件的局部截面正视图。如图所示,该实施例中的篡改响应组件包括从安装到多层电路板610的第一侧的电子部件602和从安装到多层电路板610的第二侧的电子部件902的相应传热路径。在上面结合图6A-9描述了从电子部件602向上通过多孔传热元件630到达多个导热鳍624的传热路径。另外,在该构造中,热界面材料1135将电子部件902耦接到第二外壳组件的内壁921,并且相应多孔传热元件1130的尺寸和位置被设计成覆盖在传热路径中的电子部件902上,以提供穿过在第二外壳的内壁921和外壁922之间限定的第二外壳的密封内部隔室的增强的导热性。多孔传热元件1130与上文结合图6A-10B的实施例所述的多孔传热元件630相同或相似。

本领域技术人员将注意到,本文提供了篡改响应组件的压力感测实现方式,其中一个或多个多孔传热元件位于导热外壳的密封内部隔室内。多孔传热元件的尺寸和位置被设计成便于将来自相应电子部件的热传导穿过导热外壳的密封内部隔室,有利地允许通过监视压力以检测指示篡改事件的变化来实现防篡改保护,即使在篡改事件涉及钻穿多孔传热元件的情况下也是如此。在一个或多个实现方式中,多孔传热元件包括多孔材料,例如烧结金属,其具有在30%-80%范围内的孔隙率,例如,大约50%(在一个实施例中)。在一个具体实施例中,多孔材料是烧结铜结构,其包括上金属箔和下金属箔,以在将多孔传热元件粘附到外壳的内壁和外壁时阻止软钎焊料或硬钎焊料渗入多孔材料中。在一个或多个实现方式中,多孔传热元件相对于相应热生成电子部件被设定尺寸和定位,使得外壳内的密封内部隔室的仅一部分包含多孔传热元件。有利地,多孔传热元件具有软钎焊或硬钎焊界面,该软钎焊或硬钎焊界面为外壳的安全容积内的一个或多个散热部件提供高K界面。实际上,多孔传热元件的热性能可根据孔径和所得的平均空隙率、晶界电阻等而变化。烧结金属结构的设计可以适于通过根据需要使用较厚的实心金属部分作为上金属箔和下金属箔来减轻对烧结金属结构的降低的传导性的热影响。在一个或多个实施例中,中间部分包括多孔材料,所述多孔材料暴露于密封内部隔室或与密封内部隔室流体连通。

本文所用的术语仅是为了描述特定实施例的目的,而不是要限制本发明。如本文所用,单数形式“一”、“一个”和“该”旨在也包括复数形式,除非上下文另有明确指示。还应理解,术语“包括(comprise)”(以及任何形式的包括,例如“包括(comprises)”和“包括(comprising)”)、“具有”(以及任何形式的具有,例如“has”和“having”)、“包含(include)”(以及任何形式的包含,例如“includes”和“including”)和“含有”(以及任何形式的含有,例如“contains”和“containing”)是开放式的连接动词。因此,“包括”、“具有”、“包含”或“含有”一个或多个步骤或元件的方法或装置拥有那些一个或多个步骤或元件,但不限于仅拥有那些一个或多个步骤或元件。同样,“包括”、“具有”、“包含”或“含有”一个或多个特征的方法的步骤或装置的元件拥有那些一个或多个特征,但不限于仅拥有那些一个或多个特征。此外,以某种方式配置的装置或结构至少以该方式配置,但是也可以以未列出的方式配置。

如果存在,下面的权利要求中的所有装置或步骤加功能元件的对应结构、材料、动作和等同物旨在包括用于与具体要求保护的其它要求保护的元件来组合地执行功能的任何结构、材料或动作。已经出于说明和描述的目的给出了本发明的描述,但是该描述不是穷举的或者将本发明限制为所公开的形式。在不背离本发明范围的情况下,许多修改和变化对于本领域普通技术人员来说是显而易见的。选择和描述实施例是为了最好地解释本发明的一个或多个方面的原理和实际应用,并且使本领域的其他普通技术人员能够理解本发明的一个或多个方面,以用于具有适合于所设想的特定用途的各种修改的各种实施例。