带外延层的半导体器件及其制作方法

文献发布时间:2023-06-19 13:49:36

技术领域

本发明涉及半导体集成电路制造领域,特别涉及一种带外延层的半导体器件及其制作方法。

背景技术

在目前激烈的市场竞争中,客户想要尽可能使用较小的设计规则来提高产品的竞争力,这就对于使用传统的杂质掺杂隔离技术的工艺提出了更高的要求,例如隔离规则的缩小将限制外延厚度,而外延厚度的减少将会直接影响产品器件的耐压。在实际的工艺开发过程中,即使将隔离扩散以及外延厚度做到最好的平衡可能依旧无法满足客户对于产品耐压的期望值。且由于外延工艺的整体厚度一致性不佳,导致单片晶圆内的不同区域的耐压值差距较大,无法保证客户产品性能的一致性。

发明内容

本发明要解决的技术问题是为了克服现有的制造工艺无法满足产品器件的耐压期望值、外延工艺的整体厚度一致性不佳导致晶圆内器件耐压值一致性差的缺陷,提供一种带外延层的半导体器件及其制作方法。

本发明是通过下述技术方案来解决上述技术问题:

本发明提供一种带外延层的半导体器件的制作方法,在N型外延工艺之前,对P型衬底进行N-离子(N型负离子)注入,以阻挡延缓所述P型衬底中的P型杂质在所述N型外延工艺过程中的反向扩散。

较佳地,所述对P型衬底进行N-离子注入之后、N型外延工艺之前,还包括埋层推进步骤。

较佳地,所述N-离子为砷离子。

较佳地,所述砷离子的剂量范围为1E12~3E13。

较佳地,所述砷离子注入的能量范围为40Kev(千电子伏特)~160Kev。

较佳地,所述砷离子注入的能量为120Kev。

较佳地,所述半导体器件为双极型器件。

本发明还提供一种带外延层的半导体器件,所述半导体器件使用前述的带外延层的半导体器件的制作方法制造生成。

在符合本领域常识的基础上,上述各优选条件,可任意组合,即得本发明各较佳实例。

本发明的积极进步效果在于:本发明在已选用掺杂浓度较淡的P型衬底的情况下,通过在N型外延工艺之前对P型衬底进行砷离子注入,起到阻挡减缓衬底P型杂质向外延层扩散,补偿外延层N型杂质分布深度的作用;从而实现了在不改变外延工艺大环境的条件下,实际增加了N型外延的有效厚度,提高了半导体器件的纵向耐压值。同时可以有效提高外延层整体厚度的一致性,提高晶圆内器件的耐压值的一致性。

附图说明

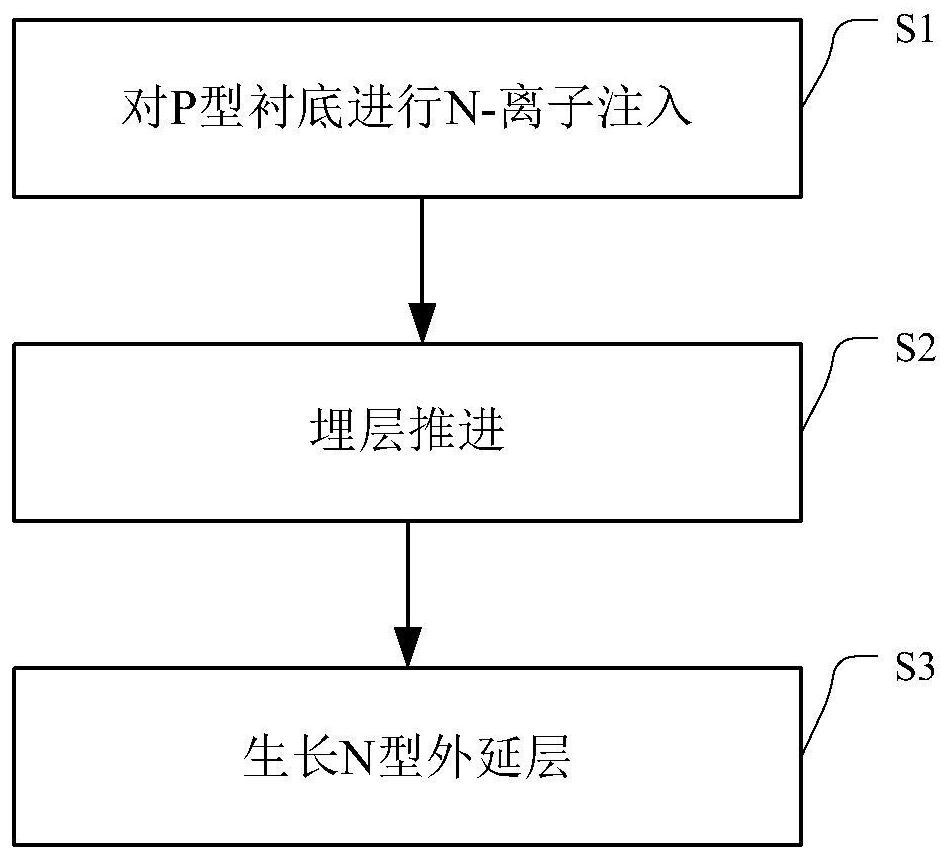

图1为本发明实施例1的带外延层的半导体器件的制作方法的工艺流程图。

图2为本发明实施例1的带外延层的半导体器件的制作方法的外延试验片杂质分布对比曲线图。

图3为本发明实施例1的带外延层的半导体器件的制作方法的晶圆片上器件的纵向耐压值分布图。

具体实施方式

下面通过实施例的方式进一步说明本发明,但并不因此将本发明限制在所述的实施例范围之中。

实施例1

本实施例提供一种带外延层的半导体器件的制作方法,如图1所示,所述制作方法包括如下步骤:

S1、对P型衬底进行N-离子注入。

本实施例中,在N型外延工艺之前,对P型衬底采用满片普注的工艺方法进行N-离子注入,以阻挡延缓P型衬底中的P型杂质在N型外延工艺过程中的反向扩散。其中N-离子为砷离子。

其中,砷离子的剂量范围为1E12~3E13,注入的能量范围为40Kev~160Kev。本实施例中砷离子注入的能量采用120Kev,经测试验证效果最佳。

S2、埋层推进。

由于增加砷离子注入将会对衬底表面带来额外的晶格损伤,而衬底表面的晶格排列将会直接影响到整个外延层的生长质量。将新引入的砷离子注入工艺步骤安排在外延前相关埋层的炉管杂质推进前,这样炉管的高温能够很大程度上修复离子注入造成的晶格损伤,使外延层的生长过程中尽可能少得引入缺陷,保证产品质量。

S3、生长N型外延层。

通过埋层推进步骤的高温修复P型衬底中砷离子注入的晶格损伤后,在P型衬底上生长N型外延层,从而可以继续进行剩余的工艺步骤,因为这些工艺步骤和现有的实现方式一致,所以在此不再赘述。

本实施例中的半导体器件为双极型器件。需要说明的是,本实施例的带外延层的半导体器件的制作方法也适用于其它有外延的、且受外延层下衬底杂质反扩影响的工艺。

以下通过具体的试验过程详细分析本实施例的带外延层的半导体器件的制作方法的原理。

在现有的工艺过程中,通过对于外延层杂质分布SRP(Spreading ResistanceProfiling扩展电阻测试)的分析,显示实际N型杂质分布深度(外延有效厚度)要远小于外延菜单设计理论值,可以判定外延工艺中的高温过程以及后续的高温炉管工艺使P型衬底的杂质向N型外延层扩散,导致外延层的实际有效N型杂质分布深度被削减。受限于外延工艺气源以及工艺设备,无法进一步优化外延工艺菜单,同时由于外延后的高温热过程对现有器件的其它电参数有不可预知的影响,在已选用掺杂浓度较淡的P型衬底的情况下,在不改变外延工艺大环境的条件下,在外延工艺前进行N-注入,可以起到阻挡减缓衬底P型杂质向外延层扩散,补偿外延层N型杂质分布深度的作用。基于砷在硅中的固溶度较高,扩散系数较小的特点,选择砷离子作为N-注入掺杂元素可以尽可能减少对于衬底的影响,同时也减少了对于其他器件参数的影响。

首先在试验片上安排不同砷离子注入剂量SRP实验(即离线外延层扩展电阻测试),进行杂质分布曲线对比分析。如图2所示,生长相同厚度(9.5微米)外延层,砷离子注入剂量不同的试验片的杂质分布图中,浅灰色线代表未进行砷离子注入的外延试验片,深色带菱形线代表进行7.7E12剂量砷离子注入的外延试验片,深色带方形线代表进行3E13剂量砷离子注入的外延试验片,三条曲线的载流子浓度最低处为该试验片的N/P反型界面分界点,可以看出进行砷离子注入的试验片的N/P反型界面深度分别为7.16微米和8.17微米,相较于未进行砷离子注入的试验片的N/P反型界面深度6.8微米更深,且注入剂量越高,试验片的N/P反型界面越深,这代表进行砷离子注入能够有效阻挡衬底内的P型杂质从衬底向外延层反向扩散的运动,使有效的N型外延区域更厚,理论上可以增加器件的纵向耐压值,从而证实在N型外延工艺前对P型衬底进行砷离子注入可以增加器件的纵向耐压值。

然后在正式生产片上进行外延工艺前砷离子注入试验,通过多次注入剂量尝试对比PCM(Process Control and Monitor工艺电参数监控测试)结果,从而确定最适合的砷离子注入剂量。如图3所示,横轴为实验晶圆的批次编号,一组24片晶圆,纵轴为BVCEO(基极开路、集电极-发射极反向击穿电压),即器件击穿电压,左部是没有采取砷离子注入工艺的晶圆击穿电压分布,右部是采用了砷离子注入工艺的晶圆击穿电压分布。从图3可以看出,左部的晶圆击穿电压大多在30多伏到60多伏之间,每个晶圆的击穿电压都相差10多伏~20多伏的区间,显示没有采取砷离子注入工艺的晶圆的击穿电压较低且一致性差;右部的晶圆击穿电压均在60伏左右,且每个晶圆的击穿电压波动范围均在10伏以内,显示采取了砷离子注入工艺的晶圆的击穿电压整体较高且一致性好。所以在外延工艺前对P型衬底进行砷离子注入能够极大的提高器件的纵向耐压值且能提高晶圆片中器件耐压值的一致性,同时器件的其他PCM参数不受影响。通过大量的试验,得出对应于各种工艺条件下的砷离子注入剂量和注入能量。

本实施例在已选用掺杂浓度较淡的P型衬底的情况下,通过在N型外延工艺之前对P型衬底进行砷离子注入,起到阻挡减缓衬底P型杂质向外延层扩散,补偿外延层N型杂质分布深度的作用;从而在不改变外延工艺大环境的条件下,实际增加了N型外延的有效厚度,提高了半导体器件的纵向耐压值。同时注入P型衬底中的砷离子阻挡减缓了衬底中P型杂质向外延层扩散,可以有效提高外延层整体厚度的一致性,提高晶圆内器件的耐压值的一致性。

实施例2

本实施例提供一种带外延层的半导体器件,该半导体器件使用实施例1所述的带外延层的半导体器件的制作方法制造生成。

该半导体器件由于在N型外延工艺之前进行了P型衬底砷离子注入,在外延工艺过程中可以阻挡减缓P型杂质向外延层的扩散,能够增加N型外延的有效厚度,器件的纵向耐压值有显著提升。

虽然以上描述了本发明的具体实施方式,但是本领域的技术人员应当理解,这仅是举例说明,本发明的保护范围是由所附权利要求书限定的。本领域的技术人员在不背离本发明的原理和实质的前提下,可以对这些实施方式做出多种变更或修改,但这些变更和修改均落入本发明的保护范围。

- 带外延层的半导体器件及其制作方法

- 一种半导体器件及其氮化镓外延层制作方法