一种适用于SAR ADC的动态锁存电路

文献发布时间:2023-06-19 19:37:02

技术领域

本发明属于模拟集成电路技术领域,提出一种基于动态电路的锁存逻辑,由于动态逻辑晶体管数量少且速度快,因此其适合作为逐次逼近型模数转换器的逻辑电路使用。

背景技术

人类生活的现实世界,人们日常所接触到的信号,如声音等,都是模拟信号,因此数字信号设备必须能够与模拟世界相互交流,这些能够使得数字世界和模拟世界之间相互交流的器件被称为数据转换器。模数转换器(ADC)作为沟通模拟世界和数字世界的重要器件,在许多电子设备中广泛使用。逐次逼近型(Successive Approximation Register,SAR)ADC因为其结构上简单,并且高度数字化,与现在不断进步的CMOS工艺节点十分契合,使得它在低功耗应用方面有着比较明显的优势,并且随着工艺的进步其性能也越发出色,因此SAR ADC成为近些年模数转换器领域内的研究热点。作为逐次逼近算法的核心,逐次逼近寄存器逻辑电路影响了整个系统的运行速度与稳定性。

SAR ADC由于使用逐次逼近型算法,每一次比较出结果之后都需要一个锁存逻辑将对应的码字存下来,若是使用同步时钟进行锁存,则在SAR ADC中这个时钟频率将会远大于采样时钟频率,特别是在高速SAR ADC的应用中,无论是通过片外注入还是片内产生如此高频时钟都是十分困难的。

由于逐次逼近型算法,每一位结果在锁存之后还需要反馈到电容阵列,传统的SAR逻辑电路采用D触发器对每一位结果进行锁存,由于传统的D触发器锁存信号需要经过的逻辑门层数较多,这样导致较大的逻辑延迟,这在高速SAR ADC中将会限制ADC的转换速度。

发明内容

针对上述问题,本发明提出一种异步动态锁存逻辑,异步SAR逻辑时钟由片内异步产生,不需要额外的输入时钟或片上生成时钟,解决了上述需要高频同步时钟的问题。使用五管动态锁存逻辑代替传统的D触发器锁存逻辑,动态逻辑由于使用的MOS管数量少、速度快,大大减少SAR逻辑电路延迟、面积开销和功耗。通过更可靠的逻辑设计,防止异步使能信号传递过快导致锁存码字出错。

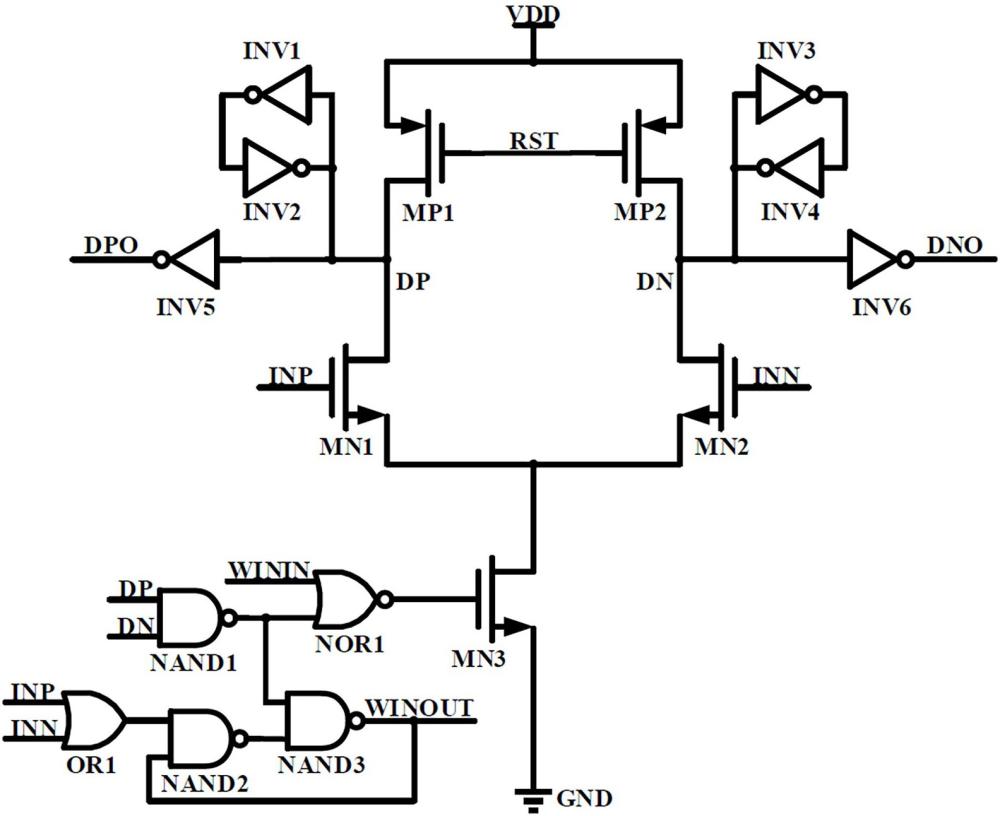

本发明所述异步动态锁存逻辑单元如图2所示,包括以下几个部分:五管动态锁存逻辑电路,电位保持电路,异步窗信号接收与传递电路。五管动态锁存逻辑电路用于锁存比较器输出的结果码字INP与INN,INP与INN同一时刻最多仅有一个为高电位,当SAR ADC处于采样阶段时复位信号RST处于有效电位低电位以使锁存节点DP与DN复位到高电位。电位保持电路由一组首尾相连的反相器构成,反相器由最小尺寸PMOS管和NMOS管组成,电位保持电路用于当复位信号RST为高电位并且比较器未输出结果或者五管动态锁存电路尾管未导通时保持浮空节点DP和DN电位,防止DP和DN节点的电位因漏电或者串扰而出现错误。异步窗信号接收与传递电路用于接收窗使能信号以使当前动态锁存模块有效,并在正确锁存比较器的输出结果后,在比较器复位时将窗使能信号传递给下一个动态锁存模块,从而防止比较器输出还未复位而下一个动态锁存单元已经有效这种情况发生。

与现有技术相比,本发明有如下好处:采用五管动态锁存电路代替D触发器锁存电路,五管锁存电路相比于D触发器电路使用的MOS管数量更少,信号经过的逻辑门层数也更少,因此延迟更低、速度更快并且面积开销和功耗也更低,在高速SAR ADC的应用中十分具有优势;采用异步窗信号作为动态锁存模块的使能信号,与传统采用同步时钟的方式相比,解决了需要片外输入或者片上生成一个高频时钟的困难,同时,异步时钟可以自适应调整每一位码字的时钟间隔,降低每一个周期的量化时间,提高SAR ADC的量化速度;此外,设计了可靠的窗使能信号传递逻辑,避免了比较器未复位而下一个动态锁存模块已经有效这种情况发生,防止发生窗信号传递过快导致的串码问题。

附图说明

图1为逐次逼近型模数转换器的整体结构示意图。

图2为本专利提出的动态锁存电路模块。

具体实施方式

下面结合附图,对本发明的具体实施方式做进一步详细描述。

图2为本发明的动态锁存电路模块,输入信号有比较器的结果信号INP和INN、动态锁存单元复位信号RST以及窗使能信号WININ,输出信号有锁存结果信号DPO和DNO以及传递给下一个动态锁存单元的窗使能信号WINOUT。

当SAR ADC处于采样阶段时,复位信号为有效电位低电位,所有的动态锁存单元进行复位将锁存节点DP和DN置于高电位,同时下拉第一个动态锁存单元的输入窗使能信号为低电位以开启第一个锁存单元。采样完成后比较器开始正常工作,SAR ADC进入到量化阶段,复位信号上拉到高电位,此时锁存节点DP和DN处于浮空状态,为了防止锁存节点因为漏电或串扰导致结果出错,由反相器INV1和反相器INV2(反相器INV3和反相器INV4)组成的电位保持电路与节点DP(DN)相连,这样保证了锁存节点在未进行锁存操作时电位的正确性。

当比较器输出结果到处于有效状态的动态锁存单元时,由于比较器的输出结果INP和INN有且仅有一个为高电位,所以锁存节点DP和DN中仅有一个将被下拉至低电位,与非门NAND1的输出上拉到高电位,五管动态锁存电路的尾管由开启状态变为关闭状态。或门OR1和与非门NAND2、NAND3一起组成可靠的窗信号传递逻辑,即使与非门NAND1的输出已经变为高电位,输出窗使能信号WINOUT也不会立刻变为低电位,必须在比较器的输出INP和INN都复位到低电位时,信号WINOUT才会变为低电位传递到下一个动态锁存单元使下一个锁存单元有效,这样保证了窗使能信号的可靠性。