伽马电压转换电路、显示装置和伽马电压转换方法

文献发布时间:2023-06-19 18:30:43

技术领域

本公开涉及显示技术领域,特别涉及一种伽马电压转换电路、显示装置和伽马电压转换方法。

背景技术

有机发光二极管(Organic Light-Emitting Device,简称OLED)显示基板,是一种与传统的液晶显示(Liquid Crystal Display,简称LCD)不同的显示基板,具备主动发光、温度特性好、功耗小、响应快、可弯曲、超轻薄和成本低等优点,其已成为新一代显示装置的重要发展发现之一,此外,有源矩阵有机发光二极体(AMOLED)显示基板也开始在小尺寸领域崭露头角。而在相应的显示系统中,需要将相应伽马电压转换成模拟灰阶电压才能进行显示,此时需要用到相应得到伽马电压转换电路,现阶段,传统的转换电路存在较大噪声并且响应速度较慢,以及,在进行伽马电压转换时存在灰阶显示亮度抖动,显示基板均一性差等问题。

发明内容

本公开旨在至少解决现有技术中存在的技术问题之一,提出了一种伽马电压转换电路、显示装置和伽马电压转换方法。

为实现上述目的,第一方面,本公开实施例提供了一种伽马电压转换电路,其包括:

第一分压电路,具有多个第一输入端和多个第一分压输出端;一个所述第一输入端被配置为接收一个第一伽马通道输入的第一伽马电压信号,所述第一分压电路被配置为根据所述第一伽马电压信号生成多路第一模拟电压信号,一个所述第一分压输出端被配置为输出一路所述第一模拟电压信号;

格雷码控制电路,用于根据待显示的灰阶值生成对应的格雷码控制信号并输出;

第一编码电路,用于根据所述格雷码控制信号以及所述多路第一模拟电压信号中的一者生成多路第二模拟电压信号并输出;

第一输出控制电路,用于根据所述多路第二模拟电压信号生成模拟灰阶电压信号并输出。

在一些实施例中,所述第一分压电路包括多个串接的电阻,任意两个串接的电阻之间的连接节点为串联节点,一个所述串接节点对应一个所述第一分压输出端。

在一些实施例中,所述格雷码控制信号包括第一格雷码信号和第二格雷码信号,其中,所述第一格雷码信号和所述第二格雷码信号的每一位均相反;

所述第一编码电路,具体用于根据所述第一格雷码信号和所述第二格雷码信号以及所述多路第一模拟电压信号中的一者,生成所述多路第二模拟电压信号并输出。

在一些实施例中,所述第一编码电路包括多个开关子电路和多个输出子电路;

每个所述开关子电路均包括多条支路,每条支路具有一个第二输入端和多个第三输入端,一个所述第二输入端被配置为接收一个所述第一分压输出端输出的一路所述第一模拟电压信号,一个所述第三输入端被配置为接收所述格雷码控制信号的一个第一预设位;每条支路被配置为根据所述格雷码控制信号的多个所述第一预设位控制自身的通断状态,并在处于导通状态时根据接收到的所述第一模拟电压信号第一模拟电压信号生成待输出电压信号;

每个所述输出子电路具有多个第四输入端和多个第五输入端,一个所述第四输入端被配置为接收一个所述开关子电路输出的所述待输出电压信号,一个所述第五输入端被配置为接收所述格雷码控制信号的一个第二预设位;每个所述输出子电路被配置为根据所述格雷码控制信号的多个所述第二预设位控制自身与一个所述开关子电路接通,并根据接收到的所述待输出电压信号生成所述第二模拟电压信号并输出。

在一些实施例中,所述第一模拟电压信号以及所述第一分压输出端与灰阶值一一对应,所述第二模拟灰阶电压与灰阶值一一对应,共有2m级灰阶值,m为正整数;

所述多个开关子电路包括多个第一开关子电路和多个第二开关子电路,每个所述第一开关子电路包括2n条支路,每个所述第二开关子电路包括2n条支路,n为正整数;

按照对应的灰阶值从小到大的顺序排序,每n个相邻的所述第一分压输出端为一组;其中,针对对应的灰阶值小于或等于预设的第一阈值的N组所述第一分压输出端,每两组相邻的所述第一分压输出端与一个所述第一开关子电路内的各第二输入端相连接,N为正整数;针对对应的所述灰阶值大于或等于预设的第二阈值的M组所述第一分压输出端,相邻的每两组所述第一分压输出端与一个所述第二开关子电路的各第二输入端相连接,所述第二阈值大于所述第一阈值,M为正整数。

在一些实施例中,所述多个开关子电路还包括第三开关子电路和多个第四开关子电路,所述第三开关子电路包括k条支路,每个所述第四开关子电路包括n条支路,其中,k=(2m-N*n-M*n)/n,k为正整数;

针对对应的灰阶值大于所述第一阈值且小于所述第二阈值的多组所述第一分压输出端,其中,每组所述第一分压输出端对应的灰阶值包括其中最小的第一灰阶值和n-1个第二灰阶值,每n个相邻的所述第一灰阶值对应的所述第一分压输出端依次交替与所述第三开关子电路的n个所述第二输入端以及一个所述第四开关子电路的各所述第二输入端相连接。

在一些实施例中,m=8,n=4,对应的灰阶值按照从小到大的顺序排序包括第0级至第255级,所述格雷码控制信号按照从低位到高位的顺序包括第0位至第7位;所述第一阈值等于第31级灰阶值;所述第二阈值等于第224级灰阶值。

在一些实施例中,所述第一开关子电路和所述第二开关子电路对应的所述第一预设位均包括第0位至第4位,所述第三开关子电路对应的所述第一预设位包括第2位至第7位,所述第四开关子电路对应的所述第一预设位包括第3位至第7位。

在一些实施例中,所述第一编码电路具有多个开关晶体管,开关晶体管包括:第一晶体管至第八晶体管,其控制极分别用于接收相反的第0位至相反的第7位;第九晶体管至第十六晶体管,其控制极分别用于接收第0位至第7位;

一个所述第一开关子电路和一个所述第二开关子电路均包括第一支路至第八支路,其中,第一支路包括依次连接的第一晶体管、第二晶体管、第三晶体管、第十二晶体管和第十三晶体管,其被配置为接收第5+8i级灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第二支路包括依次连接的第九晶体管、第二晶体管、第三晶体管、第十二晶体管和第十三晶体管,其被配置为接收第4+8i级灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第三支路包括依次连接的第一晶体管、第十晶体管、第三晶体管、第十二晶体管和第十三晶体管,其被配置为接收第6+8i级灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第四支路包括依次连接的第九晶体管、第十晶体管、第三晶体管、第十二晶体管和第十三晶体管,其被配置为接收第7+8i级灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第五支路包括依次连接的第一晶体管、第十晶体管、第十一晶体管、第十二晶体管和第十三晶体管,其被配置为接收第1+8i级灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第六支路包括依次连接的第九晶体管、第十晶体管、第十一晶体管、第十二晶体管和第十三晶体管,其被配置为接收第0+8i级灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第七支路包括依次连接的第一晶体管、第二晶体管、第十一晶体管、第十二晶体管和第十三晶体管,其被配置为接收第2+8i级灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第八支路包括依次连接的第九晶体管、第二晶体管、第十一晶体管、第十二晶体管和第十三晶体管,其被配置为接收第3+8i级灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;

其中,对于所述第一开关子电路,i的取值为0、1、2、3中的任意一者,对于所述第二开关子电路,i的取值为28、29、30、31中的任意一者。

在一些实施例中,第一支路至第八支路复用第十二晶体管和第十三晶体管,第一支路至第四支路复用第三晶体管,第五支路至第八支路复用第十一晶体管,第一支路和第二支路复用一个第二晶体管,第三支路和第四支路复用一个第十晶体管,第五支路和第六支路复用另一个第十晶体管,第七支路和第八支路复用另一个第二晶体管。

在一些实施例中,一个所述第四开关子电路包括第九支路至第十二支路,其中,第九支路包括依次连接的第四晶体管、第十三晶体管、第六晶体管、第十五晶体管和第十六晶体管,其被配置为接收第60+32j级的第一灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第十支路包括依次连接的第十二晶体管、第十三晶体管、第六晶体管、第十五晶体管和第十六晶体管,其被配置为接收第52+32j级的第一灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第十一支路包括依次连接的第四晶体管、第五晶体管、第六晶体管、第十五晶体管和第十六晶体管,其被配置为接收第44+32j级的第一灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第十二支路包括依次连接的第十二晶体管、第五晶体管、第六晶体管、第十五晶体管和第十六晶体管,其被配置为接收36+32j级的第一灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;其中,j的取值为0、1、2、3、4、5中的任意一者;

所述第三开关子电路包括多个基本单元,一个所述基本单元包括第十三支路至第十六支路,其中,第十三支路包括依次连接的第三晶体管、第十三晶体管、第六晶体管、第十五晶体管和第十六晶体管,其被配置为接收第56+32j级的第一灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第十四支路包括依次连接的第十一晶体管、第十二晶体管、第十三晶体管、第六晶体管、第十五晶体管和第十六晶体管,其被配置为接收第48+32j级的第一灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第十五支路包括依次连接的第三晶体管、第五晶体管、第六晶体管、第十五晶体管和第十六晶体管,其被配置为接收第40+32j级的第一灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;第十六支路包括依次连接的第十一晶体管、第十二晶体管、第五晶体管、第六晶体管、第十五晶体管和第十六晶体管,其被配置为接收32+32j级的第一灰阶值对应的所述第一分压输出端输出的所述第一模拟电压信号;对于一个所述基本单元,第十四支路的第十一晶体管和第十五支路的第五晶体管之间还连接有一个第四晶体管;对于相邻设置的两个所述基本单元,其中一个所述基本单元的第十六支路的第十一晶体管和另一个所述基本单元的第十三支路的第十三晶体管之间还连接有一个第四晶体管。

在一些实施例中,第九支路至第十二支路复用第六晶体管、第十五晶体管和第十六晶体管,第九支路和第十支路复用第十三晶体管,第十一支路和第十二支路复用第五晶体管;

对于一个所述基本单元,第十三支路至第十六支路复用第六晶体管、第十五晶体管和第十六晶体管,第十三支路和第十四支路复用第十三晶体管,第十五支路和第十六支路复用第五晶体管。

在一些实施例中,所述多个输出子电路包括第一输出子电路、第二输出子电路和第三输出子电路,每个所述输出子电路均具备四个所述第四输入端,分别被配置为接收对应的所述多个第一开关子电路、所述多个第二开关子电路、所述第三开关子电路和所述多个第四开关子电路输出的所述待输出电压信号;

所述第一输出子电路和所述第二输出子电路均被配置为根据所述待输出电压信号输出一路所述第二模拟电压信号,所述第三输出子电路被配置为根据所述待输出电压输出两路相同的所述第二模拟电压信号。

在一些实施例中,所述第一输出子电路被配置为,根据所述格雷码控制信号的第5位、第6位和第7位控制自身与一个所述第一开关子电路或一个所述第二开关子电路接通,或者根据所述格雷码控制信号的第2位和第3位控制自身与所述第三开关子电路或一个所述第四开关子电路接通;

所述第二输出子电路被配置为,根据所述格雷码控制信号的第5位、第6位和第7位控制自身与一个所述第一开关子电路或一个所述第二开关子电路接通,或者根据所述格雷码控制信号的第0位和第1位控制自身与所述第三开关子电路或一个所述第四开关子电路接通;

所述第三输出子电路被配置为,根据所述格雷码控制信号的第5位、第6位和第7位控制自身与一个所述第一开关子电路或一个所述第二开关子电路接通,或者根据所述格雷码控制信号的第1位控制自身与所述第三开关子电路或一个所述第四开关子电路接通。

在一些实施例中,每个所述输出子电路具有多个开关晶体管,开关晶体管包括:第一晶体管至第八晶体管,其控制极分别用于接收相反的第0位至相反的第7位;第九晶体管至第十六晶体管,其控制极分别用于接收第0位至第7位;

所述第一输出子电路通过第三晶体管和第十二晶体管与所述多个第四开关子电路的输出端相连接,并且通过第四晶体管和第十一晶体管与所述多个第四开关子电路的输出端相连接;所述第一输出子电路通过第十一晶体管和第十二晶体管与所述第三开关子电路相连接,并且通过第四晶体管和第三晶体管与所述第三开关子电路相连接;所述第一输出子电路通过第十四晶体管、第十五晶体管和第十六晶体管与所述多个第一开关子电路的输出端相连接;所述第一输出子电路通过第十四晶体管、第十五晶体管和第八晶体管与所述多个第二开关子电路的输出端相连接;

所述第二输出子电路通过第二晶体管和第九晶体管与所述多个第四开关子电路的输出端相连接,并且通过第一晶体管和第十晶体管与所述多个第四开关子电路的输出端相连接;所述第二输出子电路通过第九晶体管和第十晶体管与所述第三开关子电路相连接,并且通过第一晶体管和第二晶体管与所述第三开关子电路相连接;所述第二输出子电路通过第十四晶体管、第十五晶体管和第十六晶体管与所述多个第一开关子电路的输出端相连接;所述第二输出子电路通过第十四晶体管、第十五晶体管和第八晶体管与所述多个第二开关子电路的输出端相连接;

所述第三输出子电路通过第二晶体管与所述多个第四开关子电路的输出端相连接;所述第三输出子电路通过第十晶体管与所述第三开关子电路相连接;所述第三输出子电路通过第十四晶体管、第十五晶体管和第十六晶体管与所述多个第一开关子电路的输出端相连接;所述第三输出子电路通过第十四晶体管、第十五晶体管和第八晶体管与所述多个第二开关子电路的输出端相连接。

在一些实施例中,所述第一输出控制电路包括运算放大器,所述第一输出控制电路的输入端被配置为接收所述多个输出子电路输出的四路所述第二模拟电压信号,所述运算放大器被配置为根据四路所述第二模拟电压信号进行加权求和,生成所述模拟灰阶电压信号。

在一些实施例中,所述伽马电压转换电路还包括:

第二分压电路,具有多个第六输入端和多个第二分压输出端,一个所述第六输入端被配置为接收一个第二伽马通道输入的第二伽马电压信号,所述第二分压电路被配置为根据所述第二伽马电压信号生成多路第三模拟电压信号,一个所述第二分压输出端被配置输出一路所述第三模拟电压信号;

第二编码电路,用于根据所述格雷码控制信号以及所述多路第三模拟电压信号中的一者生成多路第四模拟电压信号并输出;

第二输出控制电路,用于根据所述多路第四模拟电压信号生成模拟灰阶电压信号并输出。

在一些实施例中,还包括:

所述第一编码电路和所述第二编码电路均包括多个开关晶体管,所述第一编码电路中的开关晶体管采用P型晶体管和N型晶体管中的一者,所述第二编码电路中的开关晶体管采用P型晶体管和N型晶体管中的另一者,所述第一编码电路中的开关晶体管对应的控制极信号与所述第二编码电路中的开关晶体管对应的控制极信号各位均相反。

第二方面,本公开实施例提供了一种显示装置,其包括:伽马电压转换电路

所述伽马电压转换电路采用如上述实施例中任一所述的伽马电压转换电路。

第三方面,本公开实施例提供了一种伽马电压转换方法,应用于如上述实施例中任一所述的伽马电压转换电路,所述方法包括:

根据第一伽马通道输入的第一伽马电压信号生成多路第一模拟电压信号;

根据待显示的灰阶值生成对应的格雷码控制信号;

根据所述格雷码控制信号以及所述多路第一模拟电压信号中的一者生成多路第二模拟电压信号;

根据所述多路第二模拟电压信号生成模拟灰阶电压信号并输出。

在一些实施例中,所述根据所述格雷码控制信号以及所述多路第一模拟电压信号中的一者生成多路第二模拟电压信号,包括:

根据所述格雷码控制信号的多个第一预设位控制自身的一个开关子电路的一条支路的通断状态,并根据处于导通状态的支路接收到的所述第一模拟电压信号生成待输出电压信号;

根据所述格雷码控制信号的多个第二预设位控制自身的输出子电路与该开关子电路接通,并根据所述待输出电压信号生成所述第二模拟电压信号并输出。

在一些实施例中,所述根据所述多路第二模拟电压信号生成模拟灰阶电压信号并输出,包括:

根据所述多路第二模拟电压信号进行加权求和,生成所述模拟灰阶电压信号。

在一些实施例中,所述方法还包括:

根据第二伽马通道输入的第二伽马电压信号生成多路第三模拟电压信号;

根据所述格雷码控制信号以及所述多路第三模拟电压信号中的一者生成多路第四模拟电压信号;

根据所述多路第四模拟电压信号生成模拟灰阶电压信号并输出。

附图说明

附图用来提供对本公开的进一步理解,并且构成说明书的一部分,与本公开的实施例一起用于解释本公开,并不构成对本公开的限制。通过参考附图对详细示例实施例进行描述,以上和其他特征和优点对本领域技术人员将变得更加显而易见,在附图中:

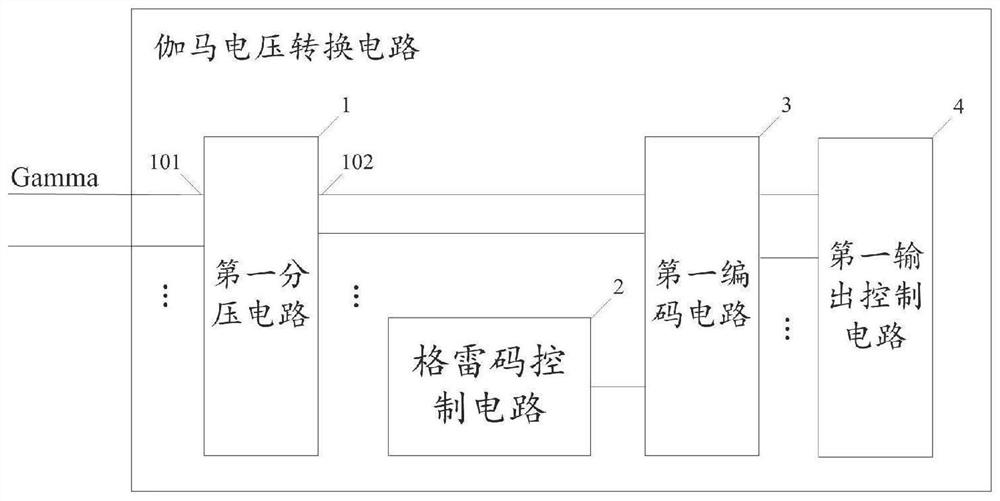

图1为本公开实施例提供的一种伽马电压转换电路的结构示意图;

图2为本公开实施例提供的一种第一编码电路的结构示意图;

图3为本公开实施例提供的另一种第一编码电路的示意图;

图4a为本公开提供的一种第一开关子电路或第二开关子电路的结构示意图;

图4b为本公开提供的一种第四开关子电路的结构示意图;

图4c为本公开提供的一种第三开关子电路的多个基本单元的结构示意图;

图5为本公开实施例提供的一种输出子电路的示意图;

图6a为本公开实施例提供的一种第一输出子电路的结构示意图;

图6b为本公开实施例提供的一种第二输出子电路的结构示意图;

图6c为本公开实施例提供的一种第三输出子电路的结构示意图;

图7为本公开实施例提供的另一种伽马电压转换电路的结构示意图;

图8为本公开实施例提供的一种伽马电压转换方法的流程图;

图9为本公开实施例中步骤S3的一种具体实施方法流程图。

具体实施方式

为使本领域的技术人员更好地理解本公开的技术方案,下面结合附图对本公开提供的伽马电压转换电路、显示装置和伽马电压转换方法进行详细描述。

在下文中将参考附图更充分地描述示例实施例,但是所述示例实施例可以以不同形式来体现且不应当被解释为限于本文阐述的实施例。反之,提供这些实施例的目的在于使本公开透彻和完整,并将使本领域技术人员充分理解本公开的范围。

本文所使用的术语仅用于描述特定实施例,且不意欲限制本公开。如本文所使用的,单数形式“一个”和“该”也意欲包括复数形式,除非上下文另外清楚指出。还将理解的是,当本说明书中使用术语“包括”和/或“由……制成”时,指定存在所述特征、整体、步骤、操作、元件和/或组件,但不排除存在或添加一个或多个其他特征、整体、步骤、操作、元件、组件和/或其群组。

将理解的是,虽然本文可以使用术语第一、第二等来描述各种元件,但这些元件不应当受限于这些术语。这些术语仅用于区分一个元件和另一元件。因此,在不背离本公开的指教的情况下,下文讨论的第一元件、第一组件或第一模块可称为第二元件、第二组件或第二模块。

除非另外限定,否则本文所用的所有术语(包括技术和科学术语)的含义与本领域普通技术人员通常理解的含义相同。还将理解,诸如那些在常用字典中限定的那些术语应当被解释为具有与其在相关技术以及本公开的背景下的含义一致的含义,且将不解释为具有理想化或过度形式上的含义,除非本文明确如此限定。

图1为本公开实施例提供的一种伽马电压转换电路的结构示意图。如图1所示,该伽马电压转换电路包括:第一分压电路1、格雷码控制电路2、第一编码电路3和第一输出控制电路4。

其中,第一分压电路1具有多个第一输入端101和多个第一分压输出端102;一个第一输入端101被配置为接收一个第一伽马(Gamma)通道输入的第一伽马电压信号,第一分压电路1被配置为根据第一伽马电压信号生成多路第一模拟电压信号,一个第一分压输出端102被配置为输出一路第一模拟电压信号。

格雷码控制电路2用于根据待显示的灰阶值生成对应的格雷码(Gray)控制信号并输出。

第一编码电路3用于根据格雷码控制信号以及多路第一模拟电压信号中的一者生成多路第二模拟电压信号并输出。

第一输出控制电路4用于根据多路第二模拟电压信号生成模拟灰阶电压信号并输出。

在一些实施例中,第一分压电路1包括多个串接的电阻,任意两个串接的电阻之间的连接节点为串联节点,一个串接节点对应一个第一分压输出端;在一些实施例中,第一分压电路1又称为电阻串。

在一些实施例中,格雷码控制信号包括第一格雷码信号和第二格雷码信号,其中,第一格雷码信号和第二格雷码信号的每一位(bit)均相反。第一编码电路3具体用于根据根据第一格雷码信号和第二格雷码信号以及多路第一模拟电压信号中的一者,生成多路第二模拟电压信号并输出。

在一些实施例中,可基于如下方式进行二进制码与格雷码的相互转换:二进制码到格雷码的转换包括,保留二进制码的最高位,将二进制码的最高位和次高位的异或结果作为格雷码的次高位,以此类推,后续将二进制码的前一位与当前位的异或结果作为格雷码的当前位,可得到二进制码对应的格雷码;格雷码到二进制的转换包括,将0与格雷码的最高位作为二进制码的最高位,将二进制码的最高位和格雷码的次高位的异或结果作为二进制码的次高位,以此类推,后续将二进制码的前一位与格雷码的当前位的异或结果作为二进制码的当前位,可得到格雷码对应的二进制码。

对应于现行的基于二进制码进行伽马电压转换的方案,其在逐灰阶进行切换时会造成显示亮度抖动、亮度不均一及电源波动等问题,这多是因为基于二进制码进行逐灰阶转换时,可能存在多位同时翻转的情况,例如,从第127级灰阶到第128级灰阶时,其对应的二进制码即从01111111到10000000,8个位会同时进行翻转,会产生较大的毛刺和噪声;同时,因为走线长短及负载大小各不相同,8个位各自控制的开关不能同时动作,可能会在翻转时形成中间态,如01111111至00011111再到10000000,中间态00011111即第31级灰阶是不希望出现的,其会造成切换过程中短暂接通第31级灰阶对应的电压,导致输出电压波动,不能快速准确地输出需要的灰阶,即第128级灰阶对应的电压,影响响应速度以及达到稳态的时间;并且,由于每行的充电时间较短,进而容易造成远端充电不足、亮度低,导致面板及装置均一性差;多位同时进行切换,还会造成数字电路及模拟电路的瞬间抽载较大,导致电源波动。而在使用格雷码时,从第127级灰阶到第128级灰阶,其对应的格雷码从01001000到11000000,仅有第7位和第3位发生变化,再例如从第199级灰阶到第200级灰阶,其对应的格雷码从10100100到10101100,仅有第3位发生变化,且在格雷码的应用中只有一位发生变化的情况占大多数。由此利用格雷码参与转换大大减少了转换过程中的不定态,避免了逐灰阶切换过程中由于多位不同时切换造成的输出电压波动,使输出更加快速精确的达到目标电压,提高了响应速度。

本公开实施例中采用基于格雷码的编码电路等进行伽马电压转换,格雷码对应的相邻灰阶切换过程至多带来两位的变化,避免了多位切换以及该过程中的不定态、中间态,提高了响应速度,减少了电路的毛刺和噪声,逐灰阶切换时灰阶显示亮度变化会更加顺畅,从而解决了逐灰阶切换所造成的显示抖动及电源波动等问题,进一步地,由于输出更精确地达到目标电位,使得面板的远端和近端电压一致,从而亮度一致,面板的均一性更优。

图2为本公开实施例提供的一种第一编码电路的结构示意图。具体地,该结构为基于图1所示的伽马电压转换电路的一种具体化可选实施方案。如图2所示,第一编码电路包括多个开关子电路301和多个输出子电路302。

其中,每个开关子电路301均包括多条支路,每条支路具有一个第二输入端3011和多个第三输入端3012,一个第二输入端3011被配置为接收一个第一分压输出端输出的一路第一模拟电压信号,一个第三输入端3012被配置为接收格雷码控制信号的一个第一预设位;每条支路被配置为根据格雷码控制信号的多个第一预设位控制自身的通断状态,并在处于导通状态时根据接收到的第一模拟电压信号生成待输出电压信号。

其中,每个输出子电路302具有多个第四输入端3021和多个第五输入端3022,一个第四输入端3021被配置为接收一个开关子电路301输出的待输出电压信号,一个第五输入端3022被配置为接收格雷码控制信号的一个第二预设位;每个输出子电路302被配置为根据格雷码控制信号的多个第二预设位控制自身与一个开关子电路301接通,并根据接收到的待输出电压信号生成第二模拟电压信号并输出。需要说明的是,在本公开各实施例中,将连接在一个第二输入端和开关子电路的输出端之间的电路作为开关子电路中的一条支路。

图3为本公开实施例提供的另一种第一编码电路的示意图。具体地,该结构为基于图2所示的第一编码电路的一种具体化可选实施方案;其中,第一模拟电压信号以及第一分压输出端与灰阶值一一对应,第二模拟灰阶电压信号与灰阶值一一对应,共有2

其中,如图3所示,多个开关子电路包括多个第一开关子电路501和多个第二开关子电路502,每个第一开关子电路501包括2n条支路,每个第二开关子电路502包括2n条支路,n为正整数;按照对应的灰阶值从小到大的顺序排序,每n个相邻的第一分压输出端为一组;其中,针对对应的灰阶值小于或等于预设的第一阈值的N组第一分压输出端,每两组相邻的第一分压输出端与一个第一开关子电路501内的各第二输入端3011相连接,N为正整数;针对对应的灰阶值大于或等于预设的第二阈值的M组第一分压输出端,相邻的每两组第一分压输出端与一个第二开关子电路502的各第二输入端3011相连接,第二阈值大于第一阈值,M为正整数。其中,如图所示,第一开关子电路501对应输出D端,第二开关子电路502对应输出E端。

在一些实施例中,m=8,n=4,对应的灰阶值按照从小到大的顺序排序包括第0级至第255级,格雷码控制信号按照从低位到高位的顺序包括第0位至第7位;第一阈值等于第31级灰阶值;第二阈值等于第224级灰阶值。

具体地,由于第一分压电路的输出是非线性的,尤其输出对应低灰阶(例如本实施例中的第0级至第31级)和高灰阶(例如本实施例中的第224级至第255级)时非线性度较大,故低灰阶和高灰阶部分需要逐灰阶输出。

在一些实施例中,第一编码电路具有多个开关晶体管,开关晶体管包括:第一晶体管601至第八晶体管608,其控制极分别用于接收相反的第0位至相反的第7位,图中,以Sn<0>表示相反的第0位,其他标识可依此类推;第九晶体管609至第十六晶体管616,其控制极分别用于接收第0位至第7位,图中,以S<0>表示第0位,其他标识可依此类推。

图4a为本公开提供的一种第一开关子电路或第二开关子电路的结构示意图。如图4a所示,其对应m=8,n=4的情况,示例性地示出了一种第一开关子电路501以及第二开关子电路502的结构;需要说明的是,该取值不会限制本实施例及后续实施例中的技术方案,仅作为示例性地描述,m和n的取值可为其他值时同样可适用于本申请的技术方案。

其中,第一开关子电路501和第二开关子电路502对应的第一预设位均包括第0位至第4位。

其中,共有4个第一开关子电路501、4个第二开关子电路502,一个第一开关子电路501和一个第二开关子电路502均包括第一支路至第八支路,其中,第一支路包括依次连接的第一晶体管601、第二晶体管602、第三晶体管603、第十二晶体管612和第十三晶体管613,其被配置为接收第5+8i级灰阶值对应的第一分压输出端输出的第一模拟电压信号,图中,以INH<5+8i>表示该支路被配置接收的对象,其他标识可依此类推;第二支路包括依次连接的第九晶体管609、第二晶体管602、第三晶体管603、第十二晶体管612和第十三晶体管613,其被配置为接收第4+8i级灰阶值对应的第一分压输出端输出的第一模拟电压信号;第三支路包括依次连接的第一晶体管601、第十晶体管610、第三晶体管603、第十二晶体管612和第十三晶体管613,其被配置为接收第6+8i级灰阶值对应的第一分压输出端输出的第一模拟电压信号;第四支路包括依次连接的第九晶体管609、第十晶体管610、第三晶体管603、第十二晶体管612和第十三晶体管613,其被配置为接收第7+8i级灰阶值对应的第一分压输出端输出的第一模拟电压信号;第五支路包括依次连接的第一晶体管601、第十晶体管610、第十一晶体管611、第十二晶体管612和第十三晶体管613,其被配置为接收第1+8i级灰阶值对应的第一分压输出端输出的第一模拟电压信号;第六支路包括依次连接的第九晶体管609、第十晶体管610、第十一晶体管611、第十二晶体管612和第十三晶体管613,其被配置为接收第0+8i级灰阶值对应的第一分压输出端输出的第一模拟电压信号;第七支路包括依次连接的第一晶体管601、第二晶体管602、第十一晶体管611、第十二晶体管612和第十三晶体管613,其被配置为接收第2+8i级灰阶值对应的第一分压输出端输出的第一模拟电压信号;第八支路包括依次连接的第九晶体管609、第二晶体管602、第十一晶体管611、第十二晶体管612和第十三晶体管613,其被配置为接收第3+8i级灰阶值对应的第一分压输出端输出的第一模拟电压信号。

其中,对于第一开关子电路501,i的取值为0、1、2、3中的任意一者,对于第二开关子电路502,i的取值为28、29、30、31中的任意一者,如图4a所示,第一开关子电路501对应输出D端,第二开关子电路502对应输出E端。

在一些实施例中,如图4a所示,第一支路至第八支路复用第十二晶体管612和第十三晶体管613,第一支路至第四支路复用第三晶体管603,第五支路至第八支路复用第十一晶体管611,第一支路和第二支路复用一个第二晶体管602,第三支路和第四支路复用一个第十晶体管610,第五支路和第六支路复用另一个第十晶体管610,第七支路和第八支路复用另一个第二晶体管602。

在一些实施例中,如图3所示,多个开关子电路还包括第三开关子电路503和多个第四开关子电路504,第三开关子电路503包括k条支路,每个第四开关子电路504包括n条支路,其中,k=(2m-N*n-M*n)/n,k为正整数。

针对对应的灰阶值大于第一阈值且小于第二阈值的多组第一分压输出端,其中,每组第一分压输出端对应的灰阶值包括其中最小的第一灰阶值和n-1个第二灰阶值,每四个相邻的第一灰阶值对应的第一分压输出端依次交替与第三开关子电路503的n个第二输入端3011以及一个第四开关子电路504的各第二输入端3011相连接。其中,如图所示,第一开关子电路501对应输出B端,第二开关子电路502对应输出A端。

具体地,由于第一分压电路的输出是非线性的,尤其输出对应低灰阶和高灰阶时非线性度较大,故低灰阶和高灰阶部分需要基于第一开关子电路501和第二开关子电路502做逐灰阶输出,而位于中间部分的灰阶,则可基于减小占用面积的原则,利用下述的第三开关子电路和第四开关子电路进行输出。

图4b为本公开提供的一种第四开关子电路的结构示意图。如图4b所示,其对应m=8,n=4的情况,示例性地示出了一种第四开关子电路504的结构。其中,第四开关子电路504对应的第一预设位包括第3位至第7位。

其中,共有6个第四开关子电路504,一个第四开关子电路504包括第九支路至第十二支路,其中,第九支路包括依次连接的第四晶体管604、第十三晶体管613、第六晶体管606、第十五晶体管615和第十六晶体管616,其被配置为接收第60+32j级的第一灰阶值对应的第一分压输出端102输出的第一模拟电压信号;第十支路包括依次连接的第十二晶体管612、第十三晶体管613、第六晶体管606、第十五晶体管615和第十六晶体管616,其被配置为接收第52+32j级的第一灰阶值对应的第一分压输出端102输出的第一模拟电压信号;第十一支路包括依次连接的第四晶体管604、第五晶体管605、第六晶体管606、第十五晶体管615和第十六晶体管616,其被配置为接收第44+32j级的第一灰阶值对应的第一分压输出端102输出的第一模拟电压信号;第十二支路包括依次连接的第十二晶体管612、第五晶体管605、第六晶体管606、第十五晶体管615和第十六晶体管616,其被配置为接收36+32j级的第一灰阶值对应的第一分压输出端102输出的第一模拟电压信号;其中,j的取值为0、1、2、3、4、5中的任意一者。

在一些实施例中,如图4b所示,第九支路至第十二支路复用第六晶体管606、第十五晶体管615和第十六晶体管616,第九支路和第十支路复用第十三晶体管613,第十一支路和第十二支路复用第五晶体管605。

图4c为本公开提供的一种第三开关子电路的多个基本单元的结构示意图。如图4c所示,其对应m=8,n=4的情况,示例性地示出了一种第三开关子电路503的结构。其中,第三开关子电路503对应的第一预设位包括第2位至第7位。

具体地,第三开关子电路503共包括6个基本单元,图中示例性地示出了其中的两个,其中,一个基本单元包括第十三支路至第十六支路,其中,第十三支路包括依次连接的第三晶体管603、第十三晶体管613、第六晶体管606、第十五晶体管615和第十六晶体管616,其被配置为接收第56+32j级的第一灰阶值对应的第一分压输出端102输出的第一模拟电压信号;第十四支路包括依次连接的第十一晶体管611、第十二晶体管612、第十三晶体管613、第六晶体管606、第十五晶体管615和第十六晶体管616,其被配置为接收第48+32j级的第一灰阶值对应的第一分压输出端100输出的第一模拟电压信号;第十五支路包括依次连接的第三晶体管603、第五晶体管605、第六晶体管606、第十五晶体管615和第十六晶体管616,其被配置为接收第40+32j级的第一灰阶值对应的第一分压输出端102输出的第一模拟电压信号;第十六支路包括依次连接的第十一晶体管611、第十二晶体管612、第五晶体管605、第六晶体管606、第十五晶体管615和第十六晶体管616,其被配置为接收32+32j级的第一灰阶值对应的第一分压输出端102输出的第一模拟电压信号;对于一个基本单元,第十四支路的第十一晶体管611和第十五支路的第五晶体管605之间还连接有一个第四晶体管604;对于相邻设置的两个基本单元,其中一个基本单元的第十六支路的第十一晶体管611和另一个基本单元的第十三支路的第十三晶体管613之间还连接有一个第四晶体管604。

在一些实施例中,如图4c所示,对于一个基本单元,第十三支路至第十六支路复用第六晶体管606、第十五晶体管615和第十六晶体管616,第十三支路和第十四支路复用第十三晶体管613,第十五支路和第十六支路复用第五晶体管605。

图5为本公开实施例提供的一种输出子电路的示意图。具体地,该结构为基于图3所示的第一编码电路的一种具体化可选实施方案;如图5所示,多个输出子电路包括第一输出子电路701、第二输出子电路702和第三输出子电路703,每个输出子电路302均具备四个第四输入端3021,分别被配置为接收对应的多个第一开关子电路、多个第二开关子电路、第三开关子电路和多个第四开关子电路输出的待输出电压信号,即与各开关子电路的输出A、B、D、E端相连接。

第一输出子电路701和第二输出子电路702均被配置为根据待输出电压信号输出一路第二模拟电压信号,第三输出子电路703被配置为根据待输出电压输出两路相同的第二模拟电压信号。

在一些实施例中,每个输出子电路具有多个开关晶体管,开关晶体管包括:第一晶体管601至第八晶体管608,其控制极分别用于接收相反的第0位至相反的第7位;第九晶体管609至第十六晶体管616,其控制极分别用于接收第0位至第7位。

图6a为本公开实施例提供的一种第一输出子电路的结构示意图。其与上述的图4a至图4c中的各开关子电路对应连接,其中,第一输出子电路701被配置为,根据格雷码控制信号的第5位、第6位和第7位控制自身与一个第一开关子电路或一个第二开关子电路接通,或者根据格雷码控制信号的第2位和第3位控制自身与第三开关子电路或一个第四开关子电路接通,即根据格雷码控制信号的第5位、第6位和第7位与输出D或E端接通,或者根据格雷码控制信号的第2位和第3位与输出A或B端接通。

如图6a所示,第一输出子电路701通过第三晶体管603和第十二晶体管612与多个第四开关子电路的输出端相连接,并且通过第四晶体管604和第十一晶体管611与多个第四开关子电路的输出端相连接;第一输出子电路通过第十一晶体管611和第十二晶体管+612与第三开关子电路相连接,并且通过第四晶体管604和第三晶体管603与第三开关子电路相连接;第一输出子电路通过第十四晶体管614、第十五晶体管615和第十六晶体管616与多个第一开关子电路的输出端相连接;第一输出子电路通过第十四晶体管614、第十五晶体管615和第八晶体管608与多个第二开关子电路的输出端相连接。

图6b为本公开实施例提供的一种第二输出子电路的结构示意图。其中,第二输出子电路702被配置为,根据格雷码控制信号的第5位、第6位和第7位控制自身与一个第一开关子电路或一个第二开关子电路接通,或者根据格雷码控制信号的第0位和第1位控制自身与第三开关子电路或一个第四开关子电路接通。

如图6b所示,第二输出子电路702通过第二晶体管602和第九晶体管609与多个第四开关子电路的输出端相连接,并且通过第一晶体管601和第十晶体管610与多个第四开关子电路的输出端相连接;第二输出子电路通过第九晶体管609和第十晶体管610与第三开关子电路相连接,并且通过第一晶体管601和第二晶体管602与第三开关子电路相连接;第二输出子电路702通过第十四晶体管614、第十五晶体管615和第十六晶体管616与多个第一开关子电路的输出端相连接;第二输出子电路702通过第十四晶体管614、第十五晶体管615和第八晶体管608与多个第二开关子电路的输出端相连接。

图6c为本公开实施例提供的一种第三输出子电路的结构示意图。其中,。第三输出子电路703被配置为,根据格雷码控制信号的第5位、第6位和第7位控制自身与一个第一开关子电路或一个第二开关子电路接通,或者根据格雷码控制信号的第1位控制自身与第三开关子电路或一个第四开关子电路接通。

如图6c所示,第三输出子电路703通过第二晶体管602与多个第四开关子电路的输出端相连接;第三输出子电路通过第十晶体管610与第三开关子电路相连接;第三输出子电路通过第十四晶体管614、第十五晶体管615和第十六晶体管616与多个第一开关子电路的输出端相连接;第三输出子电路通过第十四晶体管614、第十五晶体管615和第八晶体管608与多个第二开关子电路的输出端相连接。

在一些实施例中,第一输出控制电路包括运算放大器,第一输出控制电路的输入端被配置为接收多个输出子电路输出的四路第二模拟电压信号,运算放大器被配置为根据四路第二模拟电压信号进行加权求和,生成模拟灰阶电压信号。

具体地,下面结合实际应用示例性地对上述伽马电压转换电路进行详细描述。以使能一组第一分压输出端为例,该组对应的灰阶值包括第一灰阶值和三个第二灰阶值,第一灰阶值为第48级灰阶值,第二灰阶值包括第49级、第50级和第51级灰阶值。在伽马电压转换电路输出的模拟灰阶电压信号对应第48级灰阶值时,对应的格雷码为00100000,第一输出电路输出第48级灰阶值对应的模拟电压,第二输出电路输出第48级灰阶值对应的模拟电压,第三输出电路输出两路第48级灰阶值对应的模拟电压,由此第一输出控制电路生成第48级灰阶值对应的模拟灰阶电压信号并输出;在伽马电压转换电路输出的模拟灰阶电压对应第49级灰阶值时,其对应的格雷码为00100001,第一输出电路输出第48级灰阶值对应的模拟电压,第二输出电路输出第52级灰阶值对应的模拟电压,第三输出电路输出两路第48级灰阶值对应的模拟电压,由此第一输出控制电路根据该四路模拟电压生成第49级灰阶值对应的模拟灰阶电压信号并输出;在伽马电压转换电路输出的模拟灰阶电压对应第51级灰阶值时,其对应的格雷码为00100010,第一输出电路输出第48级灰阶值对应的模拟电压,第二输出电路输出第52级灰阶值对应的模拟电压,第三输出电路输出两路第52级灰阶值对应的模拟电压,由此第一输出控制电路根据该四路模拟电压生成第51级灰阶值对应的模拟灰阶电压信号并输出;在伽马电压转换电路输出的模拟灰阶电压对应第50级灰阶值时,其对应的格雷码为00100011,第一输出电路输出第48级灰阶值对应的模拟电压,第二输出电路输出第48级灰阶值对应的模拟电压,第三输出电路输出两路第52级灰阶值对应的模拟电压,由此第一输出控制电路根据该四路模拟电压生成第50级灰阶值对应的模拟灰阶电压信号并输出。

本公开实施例提供了一种伽马电压转换电路,其可用于采用基于格雷码的编码电路等进行伽马电压转换,提高了响应速度,减少了电路的毛刺和噪声,逐灰阶切换时灰阶显示亮度变化会更加顺畅,从而解决了逐灰阶切换所造成的显示抖动及电源波动等问题,进一步地,由于输出更精确地达到目标电位,使得面板的远端和近端电压一致,从而亮度一致,面板的均一性更优;在此基础上,本公开实施例提供了一种分段编码式的第一编码电路,针对低灰阶和高灰阶,如上述的第0级至第31级灰阶、第224级至第255级灰阶,采用逐灰阶编码输出的方式,利用第一开关子电路和第二开关子电路编码输出,针对中间部分的灰阶,利用第三开关子电路和第四开关子电路编码输出,其输出的模拟电压各组第一分压输出端对应的第一灰阶值,并利用第一输出控制电路基于多路模拟电压生成模拟灰阶电压,实现保证该伽马电压转换电路输出的灰阶精度的同时,其占用面积缩小一半。

具体地,以8位数模转换为例,传统开关树结构数模转换电路实现8位的数模转换需要使用29即512个开关晶体管;而本公开基于6位数模转换以及2位内插运算放大器实现8位数模转换,基于上述的开关晶体管复用结构只需要设置297个开关晶体管,可使占用面积节省一半。

图7为本公开实施例提供的另一种伽马电压转换电路的结构示意图。具体地,该结构为基于图1所示的伽马电压转换电路的一种具体化可选实施方案。

如图7所示,该电路还包括:

第二分压电路10,具有多个第六输入端103和多个第二分压输出端104,一个第六输入端103被配置为接收一个第二伽马通道输入的第二伽马电压信号,第二分压电路被配置为根据第二伽马电压信号生成多路第三模拟电压信号,一个第二分压输出端104被配置输出一路第三模拟电压信号。

第二编码电路30,用于根据格雷码控制信号以及多路第三模拟电压信号中的一者生成多路第四模拟信号电压并输出。

第二输出控制电路40,用于根据多路第四模拟电压信号生成模拟灰阶电压信号并输出。

在一些实施例中,在该电路中,第一编码电路3和第二编码电路30均包括多个开关晶体管,第一编码电路3的开关晶体管采用P型晶体管和N型晶体管中的一者,第二编码电路30的开关晶体管采用P型晶体管和N型晶体管中的另一者,第一编码电路3的开关晶体管对应的控制极信号与第二编码电路30的开关晶体管对应的控制极信号各位均相反。具体地,由于信号采用全正半压的形式,以P型晶体管和N型晶体管分别传输高压和低压。

在一些实施例中,第一编码电路3和第二编码电路30与同一格雷码控制电路2连接,或者第一编码电路3和第二编码电路30各自对应的格雷码控制电路2独立设置。

本公开实施例还提供了一种显示装置,其包括:如上述实施例中任一的伽马电压转换电路。

图8为本公开实施例提供的一种伽马电压转换方法的流程图。具体地,该方法应用于如上述实施例中任一的伽马电压转换电路,如图8所示,该方法包括:

步骤S1、根据第一伽马通道输入的第一伽马电压信号生成多路第一模拟电压信号。

步骤S2、根据待显示的灰阶值生成对应的格雷码控制信号。

步骤S3、根据格雷码控制信号以及多路第一模拟电压信号中的一者生成多路第二模拟电压信号。

步骤S4、根据多路第二模拟电压信号生成模拟灰阶电压信号并输出。

在一些实施例中,步骤S4,根据多路第二模拟电压信号生成模拟灰阶电压信号并输出的步骤,包括:根据多路模拟电压进行加权求和,生成模拟灰阶电压。

在一些实施例中,该方法还包括:根据第二伽马通道输入的第二伽马电压信号生成多路第三模拟电压信号;根据格雷码控制信号以及多路第三模拟电压信号中的一者生成多路第四模拟电压信号;根据多路第四模拟电压信号生成模拟灰阶电压信号并输出。

图9为本公开实施例中步骤S3的一种具体实施方法流程图。具体地,如图9所示,步骤S3,根据第一模拟电压信号及其对应的格雷码控制信号生成多路模拟电压的步骤,包括:

步骤S301、根据格雷码控制信号的多个第一预设位控制自身的一个开关子电路的一条支路的通断状态,并根据处于导通状态的支路接收到的第一模拟电压信号生成待输出电压信号。

步骤S302、根据格雷码控制信号的多个第二预设位控制自身的输出子电路与该开关子电路接通,并根据待输出电压信号生成第二模拟电压信号并输出。

本公开实施例提供了一种伽马电压转换方法,应用于相应的伽马电压转换电路,该方法可用于基于格雷码进行伽马电压转换,格雷码对应的相邻灰阶切换过程至多带来两位的变化,避免了多位切换以及该过程中的不定态、中间态,提高了响应速度,减少了电路的毛刺和噪声,逐灰阶切换时灰阶显示亮度变化会更加顺畅,从而解决了逐灰阶切换所造成的显示抖动及电源波动等问题,进一步地,由于输出更精确地达到目标电位,使得面板的远端和近端电压一致,从而亮度一致,面板的均一性更优。

本领域普通技术人员可以理解,上文中所公开方法中的全部或某些步骤、装置中的功能模块/单元可以被实施为软件、固件、硬件及其适当的组合。在硬件实施方式中,在以上描述中提及的功能模块/单元之间的划分不一定对应于物理组件的划分;例如,一个物理组件可以具有多个功能,或者一个功能或步骤可以由若干物理组件合作执行。某些物理组件或所有物理组件可以被实施为由处理器,如中央处理器、数字信号处理器或微处理器执行的软件,或者被实施为硬件,或者被实施为集成电路,如专用集成电路。这样的软件可以分布在计算机可读介质上,计算机可读介质可以包括计算机存储介质(或非暂时性介质)和通信介质(或暂时性介质)。如本领域普通技术人员公知的,术语计算机存储介质包括在用于存储信息(诸如计算机可读指令、数据结构、程序模块或其他数据)的任何方法或技术中实施的易失性和非易失性、可移除和不可移除介质。计算机存储介质包括但不限于RAM、ROM、EEPROM、闪存或其他存储器技术、CD-ROM、数字多功能盘(DVD)或其他光盘存储、磁盒、磁带、磁盘存储或其他磁存储装置、或者可以用于存储期望的信息并且可以被计算机访问的任何其他的介质。此外,本领域普通技术人员公知的是,通信介质通常包含计算机可读指令、数据结构、程序模块或者诸如载波或其他传输机制之类的调制数据信号中的其他数据,并且可包括任何信息递送介质。

本文已经公开了示例实施例,并且虽然采用了具体术语,但它们仅用于并仅应当被解释为一般说明性含义,并且不用于限制的目的。在一些实例中,对本领域技术人员显而易见的是,除非另外明确指出,否则可单独使用与特定实施例相结合描述的特征、特性和/或元素,或可与其他实施例相结合描述的特征、特性和/或元件组合使用。因此,本领域技术人员将理解,在不脱离由所附的权利要求阐明的本公开的范围的情况下,可进行各种形式和细节上的改变。