一种USB2.0/3.0接口测试装置及其测试方法

文献发布时间:2023-06-19 11:32:36

技术领域

本申请涉及电路测试技术领域,尤其涉及一种USB2.0/3.0接口测试装置及其测试方法。

背景技术

在工业生产中为了确保主机板USB接口功能(USB2.0/3.0)正常,在投入使用前都需要进行详细的测试。目前市场上存在的USB测试仪、USB2.0测试仪以及3.0测试仪等相关测试仪器体积大,利用率低,而且不能同时测量USB2.0以及USB3.0接口。另外,待测主机板(服务器)会有两个设备(USB2.0以及3.0)挂在系统USB总线上,即主机板存在X86架构和ARM架构。

针对上述中的相关技术,发明人认为存在有测试仪利用率低的缺陷。

发明内容

为了缩小测试仪的体积,并提高测试仪的利用率,本申请提供一种USB2.0/3.0接口测试装置及其测试方法。

第一方面,本申请提供一种USB2.0/3.0接口测试装置,采用如下的技术方案:

一种USB2.0/3.0接口测试装置,包括USB测试接口,与待测主机板电连接,用于接收经待测主机板传出的USB2.0接口信号或USB3.0接口信号;切换模块,用于自动识别USB2.0接口信号,并基于USB2.0接口信号切换成USB2.0链路,以使USB2.0接口被正常检测;控制模块,用于接收USB2.0接口信号与USB3.0接口信号,并对USB2.0接口信号或USB3.0接口信号进行性能测试;存储模块,用于与被测试主机板的数据存储;供电模块,用于对控制模块供电。

通过采用上述技术方案,当接收到USB3.0接口信号时,由控制模块实现对USB3.0接口的测量,当接收到USB2.0接口信号时,通过切换模块,自动切换USB2.0链路,以使USB2.0接口信号接入控制模块,进而使得控制模块对USB2.0接口进行性能测试。通过此方式,便能达到测量USB2.0或者USB3.0接口,从而能有效提高测量效率。

优选的,所述切换模块包括USART电路,所述USART电路用于自动识别ARM架构来切换USB2.0链路以实现USB2.0接口的性能测试。

通过采用上述技术方案,一般情况下,ARM架构对应USB2.0接口,因而当当USART电路检测到USB2.0接口信号时,便能自动切换USB2.0链路,以便于USB2.0接口信号接入控制模块,从而便于控制模块的测量。

优选的,所述控制模块耦接有提示模块,所述提示模块用于提示USB2.0接口信号或USB3.0接口信号是否正常。

通过采用上述技术方案,设置的提示模块,能够便于测试人员及时了解到测试状态,从而能及时针对异常情况进行处理,以提高测试效率。

优选的,所述提示模块包括第一指示灯与第二指示灯,所述第一指示灯在USB2.0接口信号或USB3.0接口信号异常时工作,所述第二指示灯在USB2.0接口信号或USB3.0接口信号正常时工作。

通过采用上述技术方案,第一指示灯与第二指示灯的相互配合,能够及时了解到USB2.0接口与USB3.0接口是否发生异常,进而能及时排出故障,从而能有效提高检测效率。

优选的,所述存储模块为EEPROM存储电路。

通过采用上述技术方案,EEPROM (Electrically Erasable Programmable Read-Only Memory),电可擦可编程只读存储器是一种掉电后数据不丢失的存储芯片。 EEPROM可以在电脑上或专用设备上擦除已有信息,重新编程。它能在字节水平上进行删除和重写而不是整个芯片擦写,这样闪存更新速度较快。

第二方面,本申请提供一种USB2.0/3.0接口测试方法,采用如下的技术方案:

一种USB2.0/3.0接口测试方法,包括:

获取接口信号;

判断接口信号为USB2.0接口信号或USB3.0接口信号;

当接口信号为正常的USB3.0接口信号时,输出USB3.0接口测试信号;

反之,则输出USB3.0异常信号;

当接口信号为USB2.0接口信号时,自动切换USB2.0链路,再输出USB2.0接口测试信号;

反之,则输出USB2.0异常信号。

通过采用上述技术方案,当检测到USB3.0接口信号时,输出USB3.0接口测试信号,以使检测装置对USB3.0接口进行测试;当检测到USB2.0接口信号时,自动切换USB2.0链路,以供USB2.0接口信号直接接入控制模块,进一步便于控制模块输出USB2.0接口测试信号,以使检测对USB2.0接口进行测试。

优选的,所述USB3.0异常信号包括:

获取USB3.0接口信号并预设USB3.0接口信号基准值;

判断USB3.0接口信号与USB3.0接口信号基准值是否相符;

当USB3.0接口信号与USB3.0接口信号基准值不相符时,输出USB3.0异常信号;

反之,不动作。

通过采用上述技术方案,针对异常情况进行提示的方式,能够方便测试人员及时排除故障,从而有效提高测试效率。

优选的,所述USB2.0异常信号包括:

获取USB2.0接口信号并预设USB2.0接口信号基准值;

判断USB2.0接口信号与USB2.0接口信号基准值是否相符;

当USB2.0接口信号与USB2.0接口信号基准值不相符时,输出USB2.0异常信号;

反之,不动作。

通过采用上述技术方案,针对异常情况进行提示的方式,能够方便测试人员及时排除故障,从而有效提高测试效率。

综上所述,本申请包括以下至少一种有益技术效果:

1.整体相比较于一般测试仪器,本申请的测试装置体积更小,能有效降低成本;

2.相较于一般测试仪器只能单独测试USB2.0接口或者USB3.0接口的方式,本申请能兼容测试USB2.0接口或者USB3.0接口,从而有效提高测试效率以及适用性。

附图说明

图1是本申请实施例中USB2.0/3.0接口测试装置的俯视图;

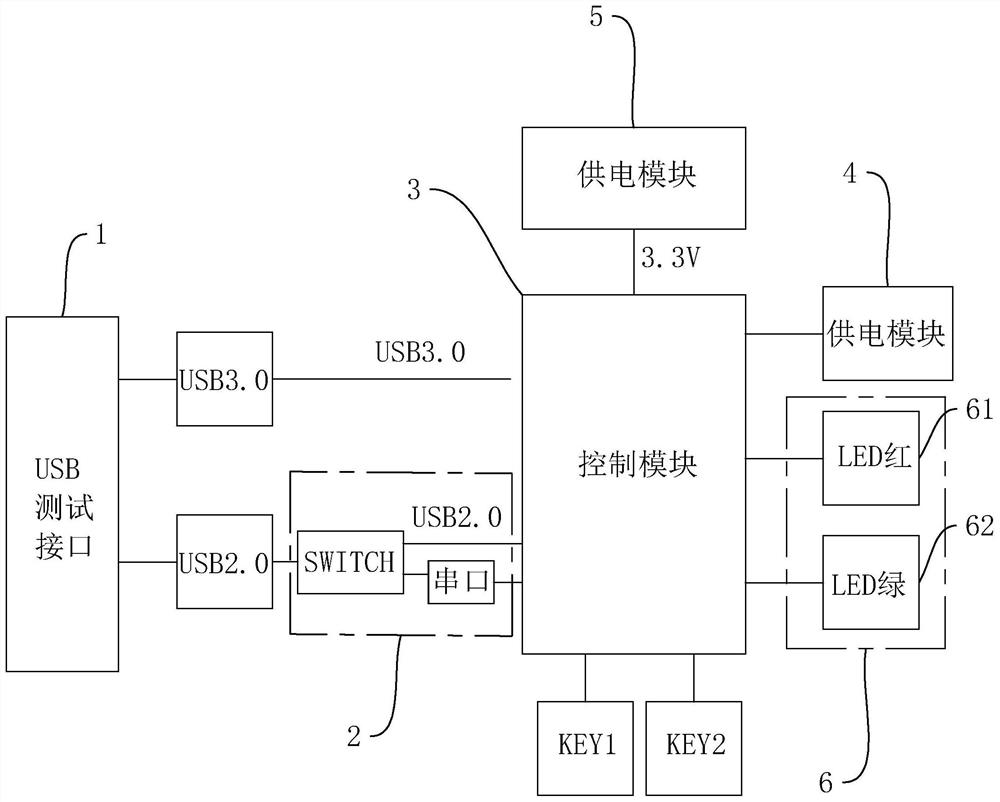

图2是本申请实施例中USB2.0/3.0接口测试装置的功能模块示意图;

图3是本申请实施例中USB2.0/3.0接口测试方法的流程示意图;

图4是本申请实施例中USB3.0异常信号的流程示意图;

图5是本申请实施例中USB2.0异常信号的流程示意图。

附图标记:1、USB测试接口;2、切换模块;3、控制模块;4、存储模块;5、供电模块;6、提示模块;61、第一指示灯;62、第二指示灯。

具体实施方式

以下结合附图1-5对本申请作进一步详细说明。

本申请实施例公开一种USB2.0/3.0接口测试装置,参照图1,用于检测USB2.0/3.0接口的性能,USB2.0/3.0接口测试装置整体呈薄片状。

参照图2,USB2.0/3.0接口测试装置包括USB测试接口1与控制模块3。其中,USB测试接口1通过USB3.0数据线与待测试主机板的USB3.0接口相连接,同时,也可以通过USB3.0数据线分别连接待测试主机板的USB2.0接口以及USB测试接口1。当USB3.0数据线连接USB测试接口1与待测试主机板的USB3.0接口时,USB测试接口1接收到USB3.0接口信号,同理,当USB3.0数据线连接USB测试接口1与待测试主机板的USB2.0接口时,USB测试接口1接收到USB2.0接口信号。

控制模块3与USB测试接口1电连接,用于接收USB2.0接口信号与USB3.0接口信号,并对USB2.0接口信号或USB3.0接口信号进行性能测试,在本实施例中,控制模块3包括型号为CH569W的单片机。当控制模块3接收到USB3.0接口信号时,控制模块3直接对USB3.0接口进行性能测试。具体测试方式如下:控制模块3会被待测主机板识别成设备(USB device),然后待测主机板会与控制模块3之间根据USB协议通讯。

具体测试USB 3.0接口时性能时,此时的控制模块3(被识别成USB device)挂在待测主机板的USB 3.0总线上,当控制模块3识别到USB 3.0接口信号时,与USB 3.0接口实现通讯,此时,便能对USB 3.0接口进行相关参数的性能测试。参数的性能测试包括枚举设备名称,即判断当前接口是USB3.0接口还是USB2.0接口,还包括对当前接口速度进行测试,实际情况下,USB2.0接口的速度为480Mbps,USB 3.0接口的速度为5Gbps。

当USB3.0数据线连接在USB测试接口1与待测试主机板的USB2.0接口之间时,为了使检测装置及时识别到USB2.0接口信号,以间接使控制模块3对USB2.0接口进行性能测试,在控制装置上耦接有切换模块2,切换模块2为USART电路,USART电路具体包括型号为PL2303的接口转换器。该器件(PL2303)作为 USB/RS232 双向转换器,一方面从主机接收USB 数据并将其转换为 RS232 信息流格式发送给外设;另一方面从 RS232 外设接收数据转换为 USB 数据格式传送回主机。这些工作全部由器件自动完成。

在本实施例中,USART电路能自动识别ARM架构与X86架构,当识别到ARM架构后,自动切换成USB2.0链路,此时,USB2.0接口信号通过USB2.0链路连接于控制模块3,针对此,便能使控制模块3对USB2.0接口的性能测试。另外,用户可以通过bootload更新App对USB测试接口1进行参数设定,参数设定包括控制模块3的版本号,厂家名称,以及对于USART电路的特定频率等。同时,当控制模块3与PC端(例如电脑)实现交互数据时,即可通过电脑读取到交互次数以及数据内容。

实际情况下,待测试的主机板(服务器)存在X86架构和ARM架构,服务器为ARM架构时,用USB链路会有问题,这个目前没有办法分析出来(因为ARM架构的服务器现在很少)。然而,当在测试装置内嵌入USART电路时,USART电路在自动识别ARM架构后,便能通过USART电路构建USB2.0链路,以使控制模块3经USB2.0链路识别到USB2.0接口信号。

在控制模块3上耦接有存储模块4,存储模块4为EEPROM存储电路,EEPROM存储电路用于与被测试主机板的数据存储,同时还能用来测试USB通讯是否正常,即,当控制模块3与USB2.0接口或者USB3.0接口按照预先设定的速度(480Mbps或5Gbps)进行交互时,则证明此时的通讯没有问题。另外,在控制模块3上耦接有供电模块5,供电模块5为3.3V供电电压,供电模块5用于对控制模块3供电。

在控制模块3上耦接有提示模块6,提示模块6用于提示USB2.0接口信号或USB3.0接口信号是否正常,提示模块6包括第一指示灯61与第二指示灯62,第一指示灯61在USB2.0接口信号或USB3.0接口信号异常时工作,第二指示灯62在USB2.0接口信号与USB3.0接口信号正常时工作,在本实施例中,第一指示灯61为红灯,第二指示灯62为绿灯。当控制模块3没有检测到USB2.0接口信号或USB3.0接口信号时,则USB2.0接口或者USB3.0接口有问题,红灯亮,当控制模块3有检测到USB2.0接口信号或USB3.0接口信号时,USB2.0接口或者USB3.0接口没有问题,绿灯亮。

实施原理为:当USB测试接口1通过USB3.0数据线与待测试主机板的USB3.0接口相连接时,控制模块3检测到USB3.0接口信号,此时,控制模块3对USB3.0接口进行性能检测。

当USB3.0数据线连接在USB测试接口1与待测试主机板的USB2.0接口之间时,USART电路识别到ARM架构,识别后,自动切换成USB2.0链路,以使USB2.0接口信号接入控制模块3,进而使得控制模块3对USB2.0接口进行性能检测。

本申请实施例还公开一种USB2.0/3.0接口测试方法。参照图3,测试方法包括:

获取接口信号;

判断接口信号为USB2.0接口信号或USB3.0接口信号;

当接口信号为正常的USB3.0接口信号时,输出USB3.0接口测试信号;

反之,则输出USB3.0异常信号;

当接口信号为USB2.0接口信号时,自动切换USB2.0链路,再输出USB2.0接口测试信号;

反之,则输出USB2.0异常信号。

其中,参照图4,USB3.0异常信号包括:

获取USB3.0接口信号并预设USB3.0接口信号基准值;

判断USB3.0接口信号与USB3.0接口信号基准值是否相符;

当USB3.0接口信号与USB3.0接口信号基准值不相符时,输出USB3.0异常信号;

反之,不动作。

其中,参照图5,USB2.0异常信号包括:

获取USB2.0接口信号并预设USB2.0接口信号基准值;

判断USB2.0接口信号与USB2.0接口信号基准值是否相符;

当USB2.0接口信号与USB2.0接口信号基准值不相符时,输出USB2.0异常信号;

反之,不动作。

在本实施例中,USB2.0接口信号基准值设定为USB2.0接口的速度,即为480Mbps,USB3.0接口信号基准值设定为USB3.0接口的速度,即为5Gbps。

本申请实施例一种USB2.0/3.0接口测试方法的实施原理为:当接收到USB3.0接口信号且与预设基准值相符时,输出USB3.0接口测试信号,使控制模块对USB3.0接口进行测试,当接收到USB2.0接口信号且与预设基准值相符时,自动切换USB2.0链路,使得USB2.0接口信号经USB2.0链路与控制模块相连,进而使得使控制模块对USB2.0接口进行测试。

本具体实施方式的实施例均为本申请的较佳实施例,并非依此限制本申请的保护范围,故:凡依本申请的结构、形状、原理所做的等效变化,均应涵盖于本申请的保护范围之内。

- 一种USB2.0/3.0接口测试装置及其测试方法

- 一种非标准PCIE3.0接口测试装置