一种基于Latch的异步逐次逼近转换逻辑结构

文献发布时间:2023-06-19 11:35:49

技术领域

本发明提出一种异步逐次逼近转换逻辑结构设计,属于模拟集成电路技术领域,由于其时钟为异步产生,因此不需要片外或片内产生一个高频时钟驱动逐次逼近算法的运行,适合作为逐次逼近型模数转换器的逻辑产生电路使用。

技术背景

模数转换器(Analog to Digital Converter,ADC)作为连接模拟域信号与数字域信号之间的桥梁,极大程度的影响着整个系统的性能。其中逐次逼近型模数转换器(Successive Approximation Register Analog to Digital Converter,SAR ADC)利用二进制算法实现模拟信号到数字信号的转换,具有芯片面积小、静态功耗低和数据输出不存在延迟等特点,因而受到了广泛的应用。作为逐次逼近算法的核心,逐次逼近寄存器逻辑影响了整个系统的运行速度与稳定性。

由于SAR ADC使用的是逐次逼近算法,若是采用传统的同步时钟逻辑,则驱动片内电容翻转的时钟将远大于其采样时钟(取决于SAR ADC位数),而对于高速的运用场景,无论是通过片外注入还是片内产生如此高频时钟都是十分困难的。因此,片内自驱动的异步SAR逻辑时钟产生电路被设计出来解决这个问题。由于其时钟均为片内异步产生,不但天然的解决了上述问题,其自适应的时钟间隔也可以进一步降低每个采样周期所需量化时间,因此得到了广泛的使用。

随着精度的增加,ADC的数字逻辑也会因此成倍的增加,导致系统的功耗抬升。与此同时,在数模混合系统中,数字逻辑大量翻转所产生的噪声将通过片内寄生耦合到模拟电路上。同时由于封装bonding wire的寄生电感效应,数字模块的噪声也会被耦合到电源线上,影响整个系统的精度,这对于高精度ADC是极为不利的。

发明内容

一种异步逐次逼近转换逻辑。通过使用Latch结构代替D触发器结构,减小了逻辑电路面积与功耗。同时通过更可靠的逻辑设计,增强了锁存系统与时钟产生电路的稳定性,避免了传统动态逻辑对寄生的敏感性。

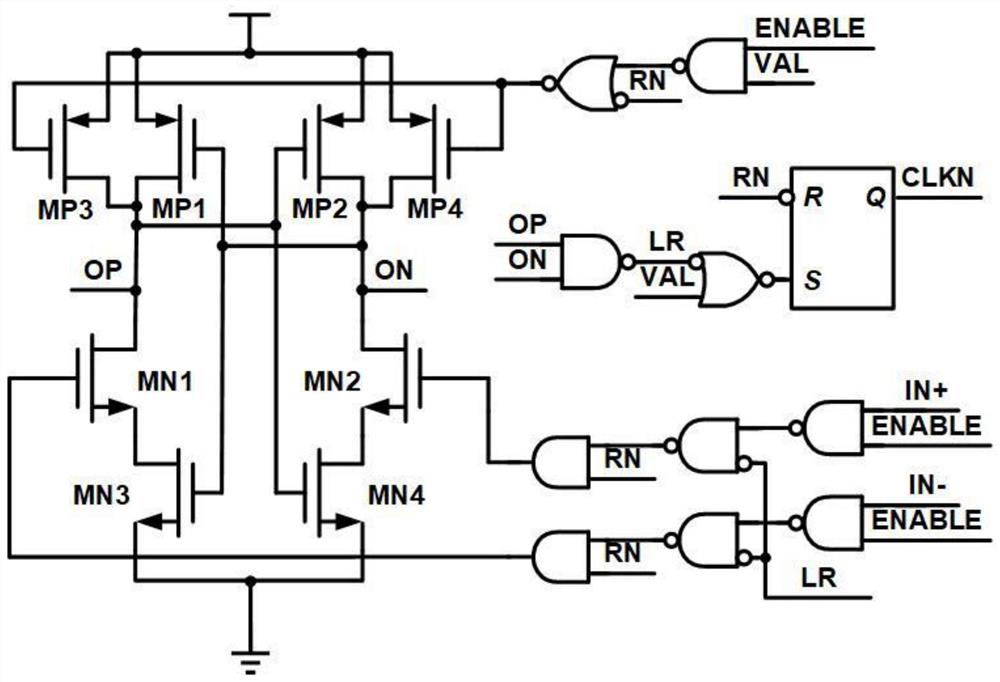

如图1为传统D触发器逐次逼近转换逻辑。需要注意的是图中只包含了异步时钟产生模块,实际使用中每一位还需要一个D触发器对比较器的输出码字进行锁存,因此D触发器的数目还需要翻倍,进一步增加系统的功耗与面积。如图2为本设计中的异步逐次逼近转换逻辑,其使用Latch结构进行锁存,并使用简单的逻辑控制电路产生时钟信号,大大减小了电路开销。

所述模块包括一个Latch结构,一个复位控制产生电路,一个输入先择电路和一个时钟产生电路。其中:Latch结构用于锁存当前位的比较器输出码字;复位控制产生电路用于产生复位信号将Latch上一次的锁存信息抹除并置为1;输入选择电路的作用是保证Latch的输入为对应位数的比较器输出,并在锁存发生之前与锁存结束后将比较器的输出与Latch的输入隔离开来,实现在复位时避免输入管与复位管的竞争,并在锁存结束后保持正反馈通路增强锁存信息的稳定性;时钟产生电路则用于产生下一级锁存的控制时钟。

附图说明

图1为传统D触发器逐次逼近转换逻辑结构示意图。

图2为本设计中的异步逐次逼近转换逻辑结构示意图。

具体实施方式

下面结合附图和具体实施例,对本设计进行详细的描述。

本设计中所提出的异步逐次逼近转换逻辑结构适用于高精度逐次逼近型模数转换器中,如图2所示为本设计中电路结构示意图,电路主要受RN、ENABLE和VAL信号控制。其中:RN信号为逐次逼近转换的复位信号,电压低为有效;ENABLE为上一级锁存模块的输出时钟;VAL为比较器的输出有效信号,电压高为有效。IN+、IN-则接入比较器输出。CLKN为输出的下一级控制时钟。对于一个N位SAR ADC,只需要使用N个图2中的模块就可以完成整个逐次逼近逻辑。

当RN复位信号有效时,逐次逼近转换逻辑结构进行复位,MP3、MP4的栅极电压被拉低,ON、OP被复位至高电平,同时MN1与MN2被关断,避免了输入管与复位管之间的竞争和电源与地之间的短接瞬间大电流。此时ENABLE、LR均被置0。

复位完成后,RN置1,SAR ADC量化开始。在上一级时钟(ENABLE)输出有效之前,复位管MP3、MP4一直被导通,同时输入管MN1、MN2的栅极被LR信号拉低,Latch一直处于复位状态,避免错误锁存。当时上一级时钟(ENABLE)有效时,IN+、IN-被选通到输入管MN1、MN2的栅极,复位管MP3、MP4等待至比较器输出有效(VAL)信号置1后关断,锁存被触发。在锁存结束后,LR(Latch Ready)被使能,将输入管MN1、MN2的栅极置1,维持Latch的正反馈环路,保证锁存结果的稳定性。与此同时,LR信号也会控制比较器复位,待比较器复位成功后,VAL信号无效,才将RS触发器置1,产生下一级时钟,防止下一级锁存错误的码字。

本领域的普通技术人员应当理解,可以对本发明做出修改和变型组合,但在不脱离本方案的精神的范围内,均应涵盖在本发明的权利保护范围之内。

- 一种基于Latch的异步逐次逼近转换逻辑结构

- 异步逐次逼近模数转换器及转换方法