一种高精度逐次逼近性模数转换器的后台校准方法及系统

文献发布时间:2023-06-19 11:35:49

技术领域

本发明属于模拟集成电路设计领域,特别涉及一种高精度逐次逼近性模数转换器的后台校准方法及系统。

背景技术

造成逐次逼近性模数转换器性能误差的主要因素包括比较器失调、噪声影响、电容寄生和电容失配等因素。由于制造工艺的偏差,电容通常会出现随机失配。当逐次逼近性模数转换器的电容阵列出现电容失配时,会对逐次逼近性模数转换器的整体线性度产生影响。对逐次逼近性模数转换器的电容阵列进行校准是提高逐次逼近性模数转换器线性度的重要技术。校准可以分为数字校准和模拟校准,而数字校准又包含前台校准和后台校准。模拟校准是指使用设计模拟电路来配合检测和补偿主DAC阵列的失配,数字校准是指分析数字码从而计算电容失配并进行修正。前台校准是指模数转换器在正常工作之前,先进行校准,采用校准值进行模拟量到数字码的转换;而后台校准是指模数转换器工作之中同时进行校准。

对于模拟校准和数字前台校准虽然可以校准失配电容,但这两种方法受限于两个方面,第一,这两种校准方法都无法再电路工作时进行校准,只能先进行校准而后进行工作,无法做到校准与电路工作同时进行;第二,这两种校准方法依赖于附加DAC阵列的精度或自身DAC阵列低位电容的精度,而当阵列达不到要求时校准效果无法得到保障。

发明内容

本发明的目的在于提供一种高精度逐次逼近性模数转换器的后台校准方法及系统,以解决上述问题。

为实现上述目的,本发明采用以下技术方案:

一种高精度逐次逼近性模数转换器的数字后台校准方法,包括以下步骤:

步骤1,逐次逼近型模数转换器具有冗余位的电容阵列,对逐次逼近型模数转换器输入电压进行采样;

步骤2,SAR逻辑控制:控制电容切换,对采样得到的电压完成正负干扰下的电压量化;

步骤3,通过量化结果对码值进行校准得到权重迭代结果;

步骤4,根据校准后的权重值输出校准后码值。

进一步的,步骤1中,其电容阵列应有n个电容的电容阵列,其中n大于12,校准前电容阵列权重寄存器复位为二进制权重,此逐次逼近型模数转换器比较器输出比较结果为D

进一步的,步骤2中,SAR逻辑控制控制冗余电容开关,先将P端冗余电容的上极板接Vref,而后控制DAC电容阵列的电容切换,完成量化,复位电容连接方式;再将N端冗余电容上极板接Vref,SAR逻辑控制控制DAC电容的切换,再次进行量化,将两次量化结果输入到校准模块。

进一步的,步骤3中,校准模块通过LMS迭代得到相应的权重迭代结果,其具体的迭代公式如下所示:

Weight

d

其中u位迭代步长,iter_lms(i)为迭代权重值所施加的误差权重,D2和D1为输出的正干扰码值和负干扰码值,d为输入干扰对应的线性误差,ν为其迭代步长。

进一步的,电容值大的造成的误差更大,并且呈现二进制关系,在迭代时,添加误差权重来加速收敛;当电容权重带来的非线性误差减小到在连续10000次的迭代中保持在5*10

进一步的,步骤4中,码值计算模块得到比较器结果与权重迭代结果计算得到对应码值输出结果,其计算方法为:

Dout为输出数字码,D

进一步的,Dev的值计算:

dev(1)=D(21)

dev(i)=dev(i-1)+D(i+20)+D(i+19)-1

其中D为比较器的输出结果,将所得结果带入码值输出计算公式得到码值输出。

进一步的,在步骤3中的迭代中,无需将所有的电容权重位进行迭代,可通过电容的失配率来计算需要校准的最低位电容,低于校准最低位电容由于其失配不会对输出权重造成影响,因此无需校准,只需将校准最低位电容到最高位电容的权重进行校准:根据电容工艺匹配性给出的失配曲线,结合电容的面积可计算出不同电容的失配率,计算出需要校准的最低位电容,其具体计算方法为:

其中C

进一步的,一种高精度逐次逼近性模数转换器的后台校准系统,包括采样模块、逻辑控制模块、校准模块和码值计算模块;

采样模块用于对逐次逼近型模数转换器输入电压进行采样;

逻辑控制模块用于控制电容切换,对采样得到的电压完成正负干扰下的电压量化;

校准模块用于通过量化结果对码值进行校准得到权重迭代结果;

码值计算模块用于根据校准后的权重值输出校准后码值。

与现有技术相比,本发明有以下技术效果:

本发明针对逐次逼近型模数转换器的电容阵列电容失配的问题进行研究,给出了一种数字后台校准的改进算法,该算法通过LMS迭代实现对电容权重的校准,并根据采用的码值计算公式确定最后所需要校准的位数以实现对权重值的校准,从而提升逐次逼近型模数转换器的精度。

本发明基于LMS算法的数字后台校准技术,这种技术能够根据比较器的输出结果找出误差,然后对失配的电容阵列进行校准以达到性能的有效改善;

本发明码值计算方法可以是得高精度逐次逼近模数转换器具有性能的有效提升。

本发明改善了高精度逐次逼近模数转换器需要外部添加干扰源或者需要额外的模拟电路进行干扰源添加,而采用这种方法的干扰源添加可以使用电路中的dummy电容,有效的利用了DAC阵列,简化了扰动添加的复杂性。

附图说明

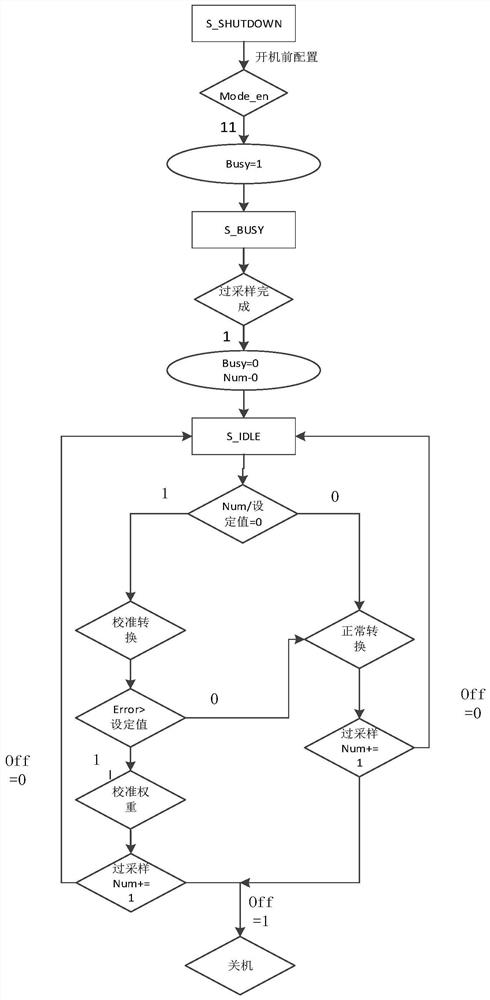

图1是本发明中模数转换器工作流程图

图2是本发明中模数转换器电容阵列示意图

图3是本发明中校准前INL和DNL结果图

图4是本发明中校准后INL和DNL结果图

图5是本发明中校准前ENOB仿真结果图

图6是本发明中校准后ENOB仿真结果图

图7是本发明中校准期间ENOB变化仿真结果图。

具体实施方式

以下结合附图对本发明进一步说明。

请参阅图1至图7,本发明主要针对逐次逼近型模数转换器的电容阵列电容失配的问题进行研究,给出了一种数字后台校准的改进算法,该算法通过LMS迭代实现对电容权重的校准,并根据采用的码值计算公式确定最后所需要校准的位数以实现对权重值的校准,从而提升逐次逼近型模数转换器的精度。

本发明提出的是一种适于高精度逐次逼近性模数转换器的数字后台校准方法,所述逐次逼近型模数转换器需要带冗余位的电容阵列,其电容阵列应有n个电容的电容阵列,其中n应该大于12,校准前电容阵列权重寄存器复位为二进制权重,此逐次逼近型模数转换器比较器输出比较结果为Dn-1,Dn-2,…,D0,其对应量化结果为Dout。其特征在于,所述数字自校准方法包括步骤1:采样(M001)对输入电压的采样;步骤2:SAR逻辑控制(M002)控制电容切换完成正负干扰下的电压量化;步骤3:校准模块(M003)通过量化结果对码值进行校准;步骤4:输出码值计算(M004)根据校准后的权重值输出校准后码值。

步骤1:采样模块(M001)采样输入电压。

步骤2:SAR逻辑控制(M002)控制冗余电容开关,先将P端冗余电容的上极板接Vref,而后控制DAC电容阵列的电容切换,完成量化,复位电容连接方式。而后将N端冗余电容上极板接Vref,M002控制DAC电容的切换,再次进行量化,将两次量化结果输入到校准模块(M003)。

步骤3:校准模块(M003)通过LMS迭代得到相应的权重迭代结果,其具体的迭代公式如下所示:

Weight

d

其中u位迭代步长,iter_lms(i)为迭代权重值所施加的误差权重,即电容值大的造成的误差更大,并且呈现二进制关系,因此在迭代时,需要添加误差权重来加速收敛,D2和D1为输出的正干扰码值和负干扰码值,最后当电容权重带来的非线性误差减小到可接受的值时,权重值迭代结束。d为输入干扰对应的线性误差,ν为其迭代步长。

步骤4:码值计算模块(M004)得到比较器结果与权重迭代结果计算得到对应码值输出结果,其计算方法为(以某17位SARADC为例,具有28位电容的DAC阵列):

Dout为输出数字码,D

dev(1)=D(21)

dev(i)=dev(i-1)+D(i+20)+D(i+19)-1

其中D为比较器的输出结果,将所得结果带入码值输出计算公式即可得到码值输出。

此外,待校准的最低位电容应由电容的适配性造成的误差是否对结果造成影响决定。根据电容工艺匹配性给出的失配曲线,结合电容的面积可计算出不同电容的失配率,从而可以计算出可以对输出码值产生量化误差的最低位失配的电容,以此电容作为待校准最低为电容。由于不同的电容其失配率与面积有关,通常面积越大失配越大,本校准方法需要根据电容工艺的需要选取合适的电容来作为第一位待校准电容。根据电容工艺匹配性给出的失配曲线,结合电容的面积可计算出不同电容的失配率,从而可以计算出需要校准的最低位电容,其所电容失配产生的误差应该可以在输出码值中得到体现,其具体计算方法为:

其中C

实施例:

以某17位SAR ADC具有28个电容组成的电容阵列为例,介绍该校准方法。所有电容下极板接Vref,将Vip端的冗余电容接Vref,Vin端的冗余电容接gnd。

采样输入电压,并进行量化比较,将比较器的28位输出保存至D1。

将Vip端的冗余电容接gnd,Vin端的冗余电容接Vref。

进行量化,将比较器28位输出结果保存至D2。

将两次量化结果输入到后台校准单元根据上述迭代计算公式对所有需要校准的电容权重进行一次迭代,同时将迭代结果输出至码值计算单元。

将比较器结果D1输入至码值计算单元利用校准中的计算公式计算得到输出码值。

重复步骤0017-步骤0022,计算误差结果,若误差减小到范围内,则不在循环,进行步骤H,否则持续循环。

所有电容下极板接Vref,将所有的的冗余电容接gnd。

采样输入电压,并进行量化比较,将比较器的28位输出保存至D。

将比较器结果D输入至码值计算单元利用校准完成的计算公式与最新的权重迭代值计算得到输出码值。

重复步骤0024到0026,并相隔固定时间监测ADC误差值,若误差大于设定值,则重新开始校准,进行步骤G,若小于设定值,则进行步骤K,直到ADC关机。

- 一种高精度逐次逼近性模数转换器的后台校准方法及系统

- 一种适用于逐次逼近模数转换器的后台电容失配校准方法