一种射频器件的功率承载力的测量方法

文献发布时间:2023-06-19 11:35:49

技术领域

本发明涉及半导体集成电路测试领域,尤其涉及一种射频器件的功率承载力的测量方法。

背景技术

随着半导体技术的发展,SOI技术已经广泛应用于射频,尤其射频开关占据了一定的市场份额,且具有与其他模块集成化的优点,将获得进一步的增长预期。在SOI结构的设计开发阶段,需要使用MPW(Multi Project Wafer,多项目晶圆)来验证射频开关的功率处理能力(通常通过测试射频开关的功率承载力)。其中,MPW是指在同一块晶圆上制作出多款芯片,MPW包含有多个独立的产品(芯片),其目的是为了提高设计效率,降低制作成本。

为了验证射频开关的非线性特性,需要验证射频器件的串联支路、并联支路和ESD(Electro-Static discharge,静电释放)支路等结构的功率处理能力。由于不同的支路结构需要通过不同的测试条件和测试方法来进行测量,使得现有技术需要通过多次测量来实现对每种支路进行测量,也就是说,在MPW上经过多次(例如三次)测试来分别测量串联支路的功率处理能力、并联支路的功率处理能力以及ESD支路的功率处理能力,这就使得测试时间较长,测试效率低下,拉长了设计开发时间。

另外,由于相同的支路(例如串联支路)所包含的多个设计的芯片在多项目晶圆上的分布是不规则的,其可能聚集在同一区域,也可能与其他支路(例如并联支路和ESD支路)混成一片,这就使得在测试前需要针对不同的支路结构建立不同的测试档案(例如是串联支路的测试档案、并联支路的测试档案、ESD支路的测试档案),该档案包括相同支路的各芯片的位置坐标、测试条件和测试方法等。由于一个多项目晶圆上存在大量的芯片,这就使得建立档案的过程是一个复杂的过程,从而需要耗费大量的精力和时间进行测试准备。

发明内容

本发明提供了一种射频器件的功率承载力的测量方法,可以提高测试效率,缩短测试准备时间。

为解决上述技术问题,本发明提供一种射频器件的功率承载力的测量方法,包括以下步骤:

步骤S1:提供多项目晶圆,所述多项目晶圆包括至少两种类型的待测芯片;

步骤S2:建立测试档案,所述测试档案包括至少两种类型的待测芯片的测试条件和测试方法;以及

步骤S3:从所述测试档案中调取当前所述待测芯片所属类型的测试条件和测试方法,并对测量当前的所述待测芯片的功率承载力,同时检测下一个待测芯片的类型,以测量所有待测芯片的功率承载力。

可选的,步骤S3包括:

确认首个待测芯片的类型,并从所述测试档案中调取首个所述待测芯片所属类型的测试条件和测试方法,并测量首个所述待测芯片的功率承载力,同时检测第二个待测芯片的类型;以及

从第二个待测芯片开始,每个正在测试的待测芯片作为当前待测芯片,从所述测试档案中调取当前的所述待测芯片所属类型的测试条件和测试方法,并测量当前的所述待测芯片的功率承载力,同时检测下一个待测芯片的类型,以测量所有待测芯片的功率承载力。

进一步的,在步骤S3中,按照顺序对所述多项目晶圆上的每个待测芯片进行测试。

进一步的,按照每行从左向右的顺序,每行从右向左的顺序,每列从上向下的顺序,每列从下向上的顺序,或者,蛇形的顺序对所述多项目晶圆上的每个待测芯片进行测试。

进一步的,通过使用第一组探针来测量当前所述待测芯片的功率承载力;同时,使用第二组探针检测下一个待测芯片的所述类型。

进一步的,按照每行从左向右的顺序对所述多项目晶圆上的每个待测芯片进行测试。

进一步的,通过使用射频器件专用的若干个探针来测量当前所述待测芯片的功率承载力;同时,使用若干个普通直流探针检测下一个待测芯片的电特性来确定其所述类型。

可选的,所述多项目晶圆包括多个待测芯片,且每个待测芯片均包括串联支路、并联支路和ESD支路。

进一步的,所述多项目晶圆包括三种类型的待测芯片,其分别为串联支路具有不同设计的待测芯片、并联支路具有不同设计的待测芯片和ESD支路具有不同设计的待测芯片。

进一步的,其特征在于,每种类型均具有多个的待测芯片。

与现有技术相比,本发明具有以下有益效果:

本发明提供一种射频器件的功率承载力的测量方法,包括以下步骤:步骤S1:提供多项目晶圆,所述多项目晶圆包括至少两种类型的待测芯片;步骤S2:建立测试档案,所述测试档案包括至少两种类型的待测芯片的测试条件和测试方法;以及步骤S3:从所述测试档案中调取当前所述待测芯片所属类型的测试条件和测试方法,并对测量当前的所述待测芯片的功率承载力,同时检测下一个待测芯片的类型,以测量所有待测芯片的功率承载力。本发明通过建立一个包括至少两种类型的待测芯片的测试条件和测试方法,该档案包括了至少两种类型的待测芯片的测试条件和测试方法,但是其并不包括针对不同类型来区分并整理出待测芯片的位置坐标,这就大大减少了前期测试准备时间,缩短了测试准备时间,还通过一次测试完成了不同类型的待测芯片的测试,缩短了测试时间,缩短了设计开发时间,加快了新产品的面世的脚步。

进一步的,按照每行从左向右的顺序对所述多项目晶圆上的每个待测芯片进行测试;通过使用射频器件专用的若干个探针来测量当前所述待测芯片的功率承载力,同时,使用若干个普通直流探针检测下一个待测芯片的电特性来确定其所述类型(权6和权7),降低测试成本,从而降低了设计开发的经费。

附图说明

图1为MPW中一个区块的三种设计类型的分布示意图;

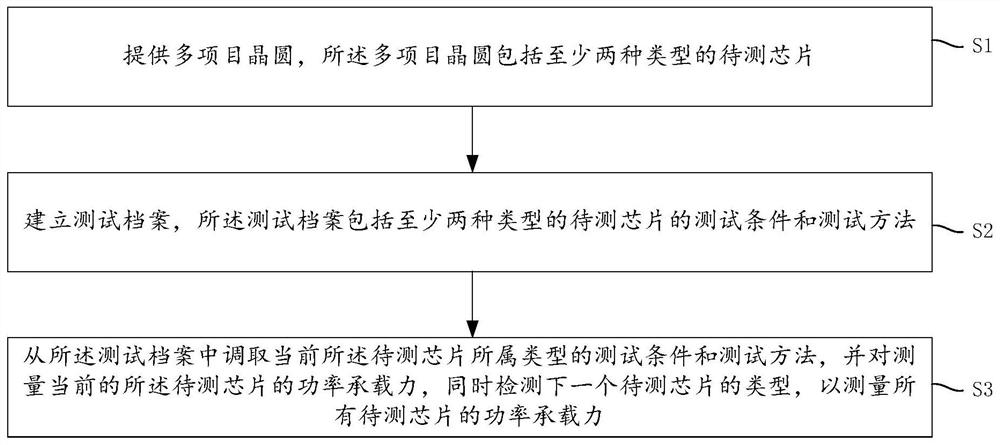

图2为本发明一实施例的一种射频器件的功率承载力的测量方法的流程示意图;

图3为本发明一实施例的射频器件的功率承载力的测量方法的测试顺序示意图。

具体实施方式

如图1所示,在MPW的一个区块中包括三个子区域,其分别为区域A、B、C,每个子区域均包含多个待测芯片,每个待测芯片可以均包括串联支路、并联支路和ESD支路。具体的,在区域A中具有多个不同设计的串联支路,在区域B中具有多个不同设计的并联支路,在区域C中具有多个不同设计的ESD支路。由图1可知,在MPW上不同类型(不同设计的串联支路、不同设计的并联支路和不同设计的ESD支路)的待测芯片的分布并不规则,使得在前期测试准备时,对每种类型的测试都需要进行相应的芯片位置坐标的确认,整个测试准备工作较为繁冗,其影响了设计开发的时间。而且每种类型的测试均需要专门的步骤来进行(即每种类型均需要对MPW进行一次测试),使得测试时间很长,同样影响了设计开发的时间,测试效率低下。

基于上述研究,本发明提供一种射频器件的功率承载力的测量方法,包括以下步骤:步骤S1:提供多项目晶圆,所述多项目晶圆包括至少两种类型的待测芯片;步骤S2:建立测试档案,所述测试档案包括至少两种类型的待测芯片的测试条件和测试方法;以及步骤S3:从所述测试档案中调取当前所述待测芯片所属类型的测试条件和测试方法,并对测量当前的所述待测芯片的功率承载力,同时检测下一个待测芯片的类型,以测量所有待测芯片的功率承载力。本发明通过建立一个包括至少两种类型的待测芯片的测试条件和测试方法,该档案包括了至少两种类型的待测芯片的测试条件和测试方法,但是其并不包括针对不同类型来区分并整理出待测芯片的位置坐标,这就大大减少了前期测试准备时间,缩短了测试准备时间,还通过一次测试完成了不同类型的待测芯片的测试,缩短了测试时间,缩短了设计开发时间,加快了新产品的面世的脚步。

进一步的,按照每行从左向右的顺序对所述多项目晶圆上的每个待测芯片进行测试;通过使用射频器件专用的若干个探针来测量当前所述待测芯片的功率承载力,同时,使用若干个普通直流探针检测下一个待测芯片的电特性来确定其所述类型(权6和权7),降低测试成本,从而降低了设计开发的经费。

以下将对本发明的一种射频器件的功率承载力的测量方法作进一步的详细描述。下面将参照附图对本发明进行更详细的描述,其中表示了本发明的优选实施例,应该理解本领域技术人员可以修改在此描述的本发明而仍然实现本发明的有利效果。因此,下列描述应当被理解为对于本领域技术人员的广泛知道,而并不作为对本发明的限制。

为了清楚,不描述实际实施例的全部特征。在下列描述中,不详细描述公知的功能和结构,因为它们会使本发明由于不必要的细节而混乱。应当认为在任何实际实施例的开发中,必须做出大量实施细节以实现开发者的特定目标,例如按照有关系统或有关商业的限制,由一个实施例改变为另一个实施例。另外,应当认为这种开发工作可能是复杂和耗费时间的,但是对于本领域技术人员来说仅仅是常规工作。

为使本发明的目的、特征更明显易懂,下面结合附图对本发明的具体实施方式作进一步的说明。需说明的是,附图均采用非常简化的形式且均使用非精准的比率,仅用以方便、明晰地辅助说明本发明实施例的目的。

图2为本实施例的一种射频器件的功率承载力的测量方法的流程示意图。如图2所示,本实施例提供了一种射频器件的功率承载力的测量方法,所述方法包括以下步骤:

步骤S1:提供多项目晶圆,所述多项目晶圆包括至少两种类型的待测芯片;

步骤S2:建立测试档案,所述测试档案包括至少两种类型的待测芯片的测试条件和测试方法;以及

步骤S3:从所述测试档案中调取当前所述待测芯片所属类型的测试条件和测试方法,并对测量当前的所述待测芯片的功率承载力,同时检测下一个待测芯片的类型,以测量所有待测芯片的功率承载力。

以下结合图2和图3对本实施例的一种射频器件的功率承载力的测量方法进行详细描述。

首先执行步骤S1,提供多项目晶圆,所述多项目晶圆包括至少两种类型的待测芯片。

在本实施例中,所述多项目晶圆包括多个待测芯片,且每个待测芯片可以均包括串联支路、并联支路和ESD支路。所述多项目晶圆包括三种类型的待测芯片,其分别为串联支路具有不同设计的待测芯片、并联支路具有不同设计的待测芯片和ESD支路具有不同设计的待测芯片,每种类型均具有多个的待测芯片,且每种类型的各待测芯片的分布不规则,可能是按照区块分布,也可能在其中一个类型的集中区块中夹杂着其他一种或几种类型的若干个待测芯片。

若采用现有技术中对各类型均建立测试档案,将会是一个很大的工程,为此,接着执行步骤S2,建立测试档案,所述测试档案包括至少两种类型的待测芯片的测试条件和测试方法。

在步骤中,建立一个包括至少两种类型的待测芯片的测试条件和测试方法,该档案包括了至少两种类型的待测芯片的测试条件和测试方法,但是其并不包括针对不同类型来区分并整理出待测芯片的位置坐标,这就大大减少了前期测试准备时间,缩短了测试准备时间,从而缩短了设计开发时间,加快了新产品的面世的脚步。

接着执行步骤S3,从所述测试档案中调取当前所述待测芯片所属类型的测试条件和测试方法,并对测量当前的所述待测芯片的功率承载力,同时检测下一个待测芯片的类型,以测量所有待测芯片的功率承载力。

本步骤包括以下步骤:

首先执行步骤S31,确认首个待测芯片的类型,并从所述测试档案中调取首个所述待测芯片所属类型的测试条件和测试方法,并测量首个所述待测芯片的功率承载力,同时检测第二个待测芯片的类型。本步骤在对当前功率承载力测试的时候,可以同时对下一个待测芯片的类型进行检测,使得在当前测试结束之后,可以直接调取下一个待测芯片所属类型的测试条件和测试方法,并对其进行测量。本步骤具体包括:首先,在测试之初,测试人员先确认出首个待测芯片的类型,以确认出该待测芯片的具体类型,即该首个待测芯片需要测试的是串联支路、并联支路还是ESD支路的功率承载力。接着,从所述测试档案中调取首个所述待测芯片所属类型的测试条件和测试方法,并测量首个所述待测芯片的功率承载力;与此同时,检测第二个待测芯片的类型。

接着执行步骤S32,从所述测试档案中调取当前的所述待测芯片所属类型的测试条件和测试方法,并测量当前的所述待测芯片的功率承载力,同时检测下一个待测芯片的类型,以测量所有待测芯片的功率承载力。

本步骤具体包括:首先,从第二个待测芯片开始,每个正在测试的待测芯片作为当前待测芯片,从所述测试档案中调取当前的所述待测芯片所属类型的测试条件和测试方法,并测量当前的所述待测芯片的功率承载力,同时检测下一个待测芯片的类型。在本步骤中,在首个待测芯片测试的同时确定了第二个待测芯片的类型,使得除首个待测芯片以外,其他所有的待测芯片均可以通过在其测试开始之前预先知道其类型,使得当前待测芯片的测试开始时间是在上一个待测芯片测试结束后直接开始进行。接着,将每个待测芯片的测试结果在其测试结束之后输出。最后,采用上述步骤将多项目晶圆中的每个待测芯片进行测试,从而完成了每个类型的功率承载力的测试。整个过程测试时间短,测试效率高。

在本实施例中,可以按照一定的顺序对每个待测芯片进行测试,例如从多项目晶圆1的第一行的多个待测芯片从左向右依次测量,接着对第二行的多个待测芯片至最后一行的多个待测芯片均从左向右依次测量(如图3所示);还可以从多项目晶圆的第一列的多个待测芯片从上向下依次测量,接着对第二列的多个待测芯片至最后一列的多个待测芯片均从上向下依次测量;还可以从多项目晶圆的第一行的多个待测芯片从左向右依次测量,并以蛇形方式从第二行的多个待测芯片从右向左依次测量,且奇数行的多个待测芯片与第一行的多个待测芯片的测量顺序相同,偶数行的多个待测芯片与第二行的多个待测芯片的测量顺序相同,即整个测试过程成蛇形;还可以采用其他的方式,例如从每一行的从右向左依次测量,从每一列的从下向上依次测量等等。

上述测量方法可以对所述多项目晶圆上的每个待测芯片依次进行测试,使得一个多项目晶圆仅需要一次测试就可以完成至少两种类型的待测芯片的测试,其缩短了进一步测试时间,提高了测试效率,进一步缩短了设计开发时间。

由于芯片内部的分布,采用从多项目晶圆的第一行的多个待测芯片从左向右依次测量,接着对第二行的多个待测芯片至最后一行的多个待测芯片均从左向右依次测量,其可以通过使用第一组探针(即射频专用的若干个探针)来测量当前所述待测芯片的功率承载力;同时,使用第二组探针(即若干个普通直流探针)检测下一个待测芯片的电特性来确定其所述类型;其他的测试顺序则需要两组射频专用的若干个探针来进行测试当前所述待测芯片的功率承载力,以及检测下一个待测芯片的电特性来确定其所述类型。

本实施例采用从多项目晶圆的第一行的多个待测芯片从左向右依次测量,接着对第二行的多个待测芯片至最后一行的多个待测芯片均从左向右依次测量,使得其仅需要一组射频专用的若干个探针,可以降低测试成本,从而降低了设计开发的经费。

综上所述,本发明提供一种射频器件的功率承载力的测量方法,包括以下步骤:步骤S1:提供多项目晶圆,所述多项目晶圆包括至少两种类型的待测芯片;步骤S2:建立测试档案,所述测试档案包括至少两种类型的待测芯片的测试条件和测试方法;以及步骤S3:从所述测试档案中调取当前所述待测芯片所属类型的测试条件和测试方法,并对测量当前的所述待测芯片的功率承载力,同时检测下一个待测芯片的类型,以测量所有待测芯片的功率承载力。本发明通过建立一个包括至少两种类型的待测芯片的测试条件和测试方法,该档案包括了至少两种类型的待测芯片的测试条件和测试方法,但是其并不包括针对不同类型来区分并整理出待测芯片的位置坐标,这就大大减少了前期测试准备时间,缩短了测试准备时间,还通过一次测试完成了不同类型的待测芯片的测试,缩短了测试时间,缩短了设计开发时间,加快了新产品的面世的脚步。

进一步的,按照每行从左向右的顺序对所述多项目晶圆上的每个待测芯片进行测试;通过使用射频器件专用的若干个探针来测量当前所述待测芯片的功率承载力,同时,使用若干个普通直流探针检测下一个待测芯片的电特性来确定其所述类型(权6和权7),降低测试成本,从而降低了设计开发的经费。

此外,需要说明的是,除非特别说明或者指出,否则说明书中的术语“第一”、“第二”等的描述仅仅用于区分说明书中的各个组件、元素、步骤等,而不是用于表示各个组件、元素、步骤之间的逻辑关系或者顺序关系等。

可以理解的是,虽然本发明已以较佳实施例披露如上,然而上述实施例并非用以限定本发明。对于任何熟悉本领域的技术人员而言,在不脱离本发明技术方案范围情况下,都可利用上述揭示的技术内容对本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

- 一种射频器件的功率承载力的测量方法

- 一种大功率射频器件的封装结构和封装方法