具校正功能连续近似缓存器模拟至数字转换器及校正方法

文献发布时间:2023-06-19 11:52:33

技术领域

本公开涉及一种模拟数字转换器的校正方法,且特别是有关于一种连续近似缓存器模拟至数字转换器的校正方法及其电路。

背景技术

模拟数字转换器性能的表现可能影响仪器测量的精准度,故在此应用将会要求模拟数字转换器的线性度。晶圆代工厂提供每个制程下所有装置的不匹配参数,在连续近似模拟数字转换器(Successive Approximation Register Analog-to-Digital Converter,SAR ADC)里,电容数字式模拟转换器(Capacitor Digital to Analog Converter,CDAC)影响着整体的线性度。如何在不过度放大电容数字模拟转换器的单位电容的情形下,仍可达到一定的线性度,是本技术领域所欲解决的课题之一。

发明内容

根据本公开一种实施方式,提供一种连续近似缓存器模拟至数字转换器的校正方法。所述连续近似缓存器模拟至数字转换器包括至少一电容式数字至模拟转换器以及控制器,所述至少一电容式数字至模拟转换器包括对应于Nd位的Nd个电容,其中Nd为正整数。所述连续近似缓存器模拟至数字转换器的电容校正方法包括:将第z位至第(Nd-1)位的所述电容耦接第一参考电压,根据第(z-1)位至第0位的所述电容的运作产生第一数字码,其中z为小于Nd的整数;将第(i+1)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将第i位的所述电容耦接第二参考电压,根据第(i-1)位至所述第0位的所述电容的运作产生第二数字码,其中i为小于Nd的整数,且z小于i;根据所述第一数字码与所述第二数字码产生所述第i位的所述电容的电容权重;以及根据所述第i位的所述电容的所述电容权重校正所述连续近似缓存器模拟至数字转换器。

依据一实施方式,本公开提供一种连续近似缓存器模拟至数字转换器的校正方法,其中连续近似缓存器模拟至数字转换器包括至少一电容式数字至模拟转换器以及控制器。至少一电容式数字至模拟转换器包括对应于Nd位的Nd个电容,其中Nd为正整数。连续近似缓存器模拟至数字转换器的电容校正方法包括:将第i位至第(Nd-1)位的电容耦接第一参考电压,根据第(i-1)位至第0位的电容的运作产生第一数字码,其中i为小于Nd的整数;将第(i+1)位至第(Nd-1)位的电容耦接所述第一参考电压,将第i位的电容耦接第二参考电压,根据第(i-1)位至第0位的电容的运作产生第二数字码;根据第一数字码与第二数字码产生第i位的电容的电容权重;以及根据第i位的电容的电容权重校正连续近似缓存器模拟至数字转换器。

依据另一实施方式,本公开提供一种具有校正功能的连续近似缓存器模拟至数字转换器,其包括:至少一电容式数字至模拟转换器,受控于多个控制信号以分别控制至少一电容式数字至模拟转换器的Nd个切换电容的切换运作,其中Nd为正整数;比较器,耦接至少一电容式数字至模拟转换器,用以将至少一电容式数字至模拟转换器的输出与比较电压进行比较;以及控制器,耦接比较器以及至少一电容式数字至模拟转换器,用以根据比较器的输出产生控制信号及数字输出信号。控制器在校正模式时,藉由比较器的(Nd+1)次运作的结果获得至少一电容式数字至模拟转换器的第i位的电容权重,其中i为小于Nd的整数。

根据本公开另一实施方式,提供一种具有校正功能的连续近似缓存器模拟至数字转换器,包括:至少一Nd位电容式数字至模拟转换器,具有Nd位的电容,其中Nd为正整数;控制器,耦接所述至少一个电容式数字至模拟转换器。所述控制器用以执行以下电容校正程序:将第z位至第(Nd-1)位的所述电容耦接第一参考电压,根据第(z-1)位至第0位的所述电容的运作产生第一数字码,其中z为小于Nd的整数;将第(i+1)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第i位的所述电容耦接第二参考电压,根据所述第(i-1)位至所述第0位的所述电容的运作产生第二数字码,其中i为小于Nd的整数,且z小于i;根据所述第一数字码与所述第二数字码产生所述第i位的所述电容的电容权重;以及根据所述第i位的所述电容的所述电容权重校正所述连续近似缓存器模拟至数字转换器。

依据另一实施方式,本公开一种具有校正功能的连续近似缓存器模拟至数字转换器,包括:至少一Nd位电容式数字至模拟转换器,具有Nd位的电容;控制器,耦接比较器的输出以及至少一个电容式数字至模拟转换器。控制器进行以下电容校正程序:将第i位至第(Nd-1)位的电容耦接第一参考电压,根据第(i-1)位至第0位的电容的运作产生第一数字码,其中i为小于Nd的整数;将第(i+1)位至第(Nd-1)位的电容耦接所述第一参考电压,将第i位的电容耦接第二参考电压,根据第(i-1)位至第0位的电容的运作产生第二数字码;根据第一数字码与第二数字码产生第i位的电容的电容权重;以及根据第i位的电容的电容权重校正连续近似缓存器模拟至数字转换器。

基于上述,本公开结合窗口切换的优点,无需在信号路径上增加其他电路,而影响校正的比较器偏移以及闪烁噪声的信息。此外,本公开也可改善因校正而累积的电容权重偏差,来进一步提升电容式数字至模拟转换器的积分非线性度。

附图说明

包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

图1是依照本公开一实施例所绘示的连续近似缓存器模拟至数字转换器的电路方块示意图。

图2是依照本公开一实施例所绘示的单端输入式连续近似缓存器模拟至数字转换器的切换机制示意图。

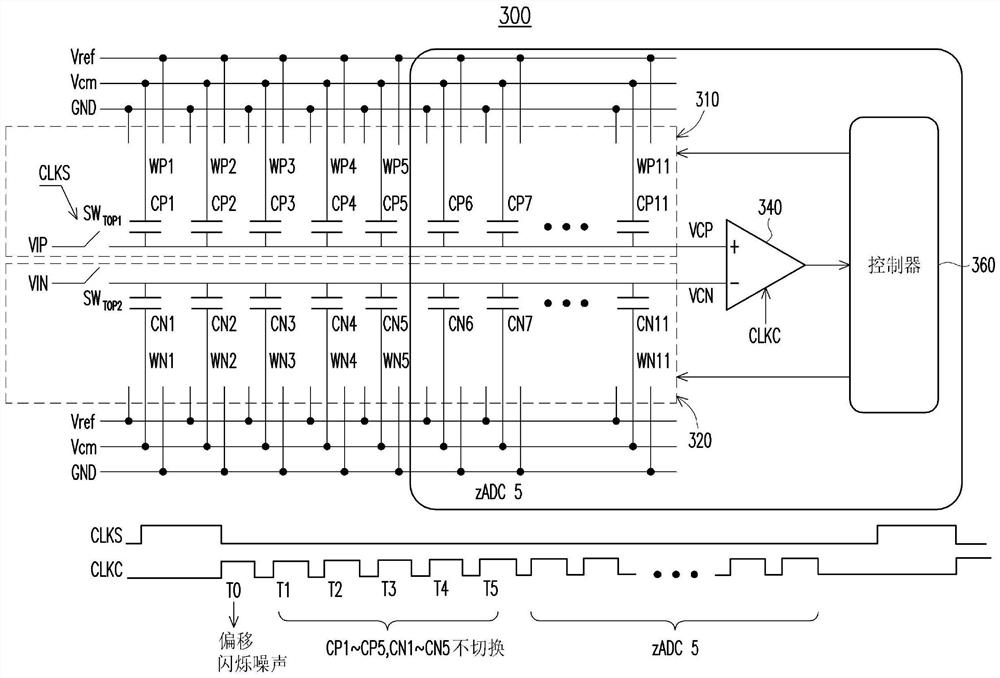

图3是依照本公开另一实施例所绘示的连续近似缓存器模拟至数字转换器的电路方块示意图。

图4是依照本公开另一实施例所绘示的差动输入式连续近似缓存器模拟至数字转换器的切换机制示意图。

图5为本公开一实施例的校正的时序示意图。

图6为本公开一实施例的闪烁噪声与比较器的偏移的校正示意图。

图7为本公开一实施例的电容校正的示意图。

图8为本公开一实施例的电容校正的示意图。

图9A绘示本公开一实施例的电路方块变化例的示意图。

图9B绘示本公开一实施例的电路方块变化例的示意图。

图10A与10B绘示本公开一实施例的时钟信号缩减示意图。

图11绘示本公开的连续近似缓存器模拟至数字转换器的校正方法的流程示意图。

图12是根据本发明一实施例的连续近似缓存器模拟至数字转换器的校正方法的流程示意图。

图13是根据本发明一实施例的连续近似缓存器模拟至数字转换器的校正方法的流程示意图。

附图标号说明

100、200:连续近似缓存器模拟至数字转换器

120、220:第一电容式数字至模拟转换器

121、281:取样开关

140、240:比较器

160、260:控制器

280:第二电容式数字至模拟转换器

300:连续近似缓存器模拟至数字转换器

310:第一电容式数字至模拟转换器

320:第二电容式数字至模拟转换器

340:比较器

345:时钟缩减电路

360:控制器

380:编码器

400:校正处理器

CP1~CP11、CN1~CN11:电容

WP1~WP11、WN1~WN11、SW

Vcm:第一参考电压(共模电压)

Vref:第二参考电压

GND:第三参考电压

CQ:比较结果输入端

CQ1:第一比较结果

CQ2_1~CQ2_10、CQ2_k:第二比较结果

D:输入端

GND:接地电压

RDY:备妥信号

RST:重置信号

SCP1~SCP10、SCN1~SCN10:切换电容组

SDO:数字输出信号

SP1~SP10:第一控制信号

SN1~SN10:第二控制信号

VDD:电源电压

VIP:第一模拟输入信号

VIN:第二模拟输入信号

VP0:第一电压

VP1~VPk:第二电压

VN0:第三电压

VN1~VNk:第四电压

Vr:比较参考电压

Vref:参考电压

WIN1~WINk:窗口区域

CLKS:取样时钟信号

CLKC:比较时钟信号

RCLKC:缩减比较时钟

具体实施方式

本发明一实施例提出一种基于窗口切换架构连续近似模拟数字转换器(简称:SARADC)的校正技术,可有效缩小因制程限制且必须到达较高线性度表现的数字模拟转换器(DAC)的装置尺寸,亦可进一步达到因切换模拟数字转换器消耗的动态功率。本技术结合了窗口切换的优点,无须在信号路径上增加其他电路来得到会影响校正的比较器偏移以及闪烁噪声的信息,也可改善因校正而累积的权重偏差,来进一步提升模拟数字转换器的积分非线性度(Integral Non Linearity,INL)。

模拟至数字转换操作

图1是依照本公开一实施例所绘示的连续近似缓存器模拟至数字转换器100的电路方块示意图。连续近似缓存器模拟至数字转换器(Successive Approximation RegisterAnalog-to-Digital Converter,SAR ADC)100,用以转换第一模拟输入信号VIP为数字输出信号SDO,其中数字输出信号SDO具有从最高有效位(Most Significant Bit,MSB)计算至最低有效位(Least Significant Bit,LSB)的N个位,其中N为正整数,以下以N=10来说明。

SAR ADC 100可包括第一电容式数字至模拟转换器(Capacitor Digital toAnalog Converter,CDAC)120、比较器140以及控制器160。第一电容式数字至模拟转换器120可包括取样开关121以及切换电容组SCP1~SCP10,其分别受控于第一控制信号SP1~SP10。第一电容式数字至模拟转换器120可于一时间点通过取样开关121接收并取样第一模拟输入信号VIP以产生第一电压VP0。取样开关121可例如是通过一取样时钟信号CLKS所控制的靴带式开关(Bootstrapped Switch)。第一电容式数字至模拟转换器120受控于多个第一控制信号SP1~SP10以分别控制切换电容组SCP1~SCP10的切换运作。详细来说,切换电容组SCPi可包括电容CPi及开关WPi,其中i为1至L的整数(在此例中,L=10)。电容CP1~CP10的第一端耦接至比较器140的非反相输入端,而电容CP1~CP10的第二端则分别通过对应的开关WP1~WP10被切换于参考电压Vref与接地电压GND之间。开关WP1~WP10分别由第一控制信号SP1~SP10所控制。电容CP1~电容CP8的电容值分别为电容CP2~电容CP9的电容值的两倍,而电容CP9的电容值等于电容CP10的电容值。在实施例中,耦接可以是直接连接或是间接连接,间接连接例如是通过另一装置连接,例如若是说明装置A耦接装置B,可以是装置A与装置B直接连接,也可以是装置A与装置B之间通过装置C相接,例如装置A直接连接到装置C后,装置C再直接连接到装置B。

比较器140接收来自第一电容式数字至模拟转换器120的第一电压VP0,且受控于比较时钟信号CLKC,以将第一电压VP0与比较参考电压Vr进行比较,产生第一比较结果CQ1,其中比较参考电压Vr可例如是参考电压Vref。控制器160耦接比较器140以及第一电容式数字至模拟转换器120。特别是,控制器160可根据第一比较结果CQ1产生第一控制信号SP1~SP10以分别控制切换电容组SCP1~SCP10的切换运作。

更进一步来说,控制器160具有二进制窗口(binary window)功能。控制器160可根据比较器140的输出(亦即第一比较结果VP0)来决定切换电容组SCP1~SCP10中的至少一者的切换运作,以将第一电容式数字至模拟转换器120的输出逼近上述的二进制窗口,其中上述的二进制窗口为M位的窗口,且M为小于或等于N的正整数。详细来说,于连续近似缓存器模拟至数字转换器100的M次迭代(iteration)运作的第k次迭代运作中(k小于或等于M),控制器160可将切换电容组SCP1~SCP10中的第k个切换电容组SCPk进行切换(例如自第一状态切换为第二状态),致使第一电容式数字至模拟转换器120产生对应的第二电压VPk。接着,比较器140可将第k次迭代运作的第二电压VPk与比较参考电压Vr进行比较以产生对应的第二比较结果CQ2_k。控制器160可根据第一比较结果CQ1与第二比较结果CQ2_k定义(或决定)窗口区域WINk。并且,控制器160可根据第一比较结果CQ1与第二比较结果CQ2_k来决定是否将第k个切换电容组SCPk切换回第一状态,或者维持于第二状态。

于第k次迭代运作中,若第一比较结果CQ1表示第一电压VP0大于比较参考电压Vr,且第二比较结果CQ2_k表示第二电压VPk亦大于比较参考电压Vr,则控制器160将第k个切换电容组维持在第二状态(即切换后的状态)。或者是,于第k次迭代运作中,若第一比较结果CQ1表示该第一电压VP0小于比较参考电压Vr,且第二比较结果CQ2_k表示第二电压VPk亦小于比较参考电压Vr,则控制器160将第k个切换电容组维持在第二状态(即切换后的状态)。

相对地,于第k次迭代运作中,若第一比较结果CQ1与第二比较结果CQ2_k表示第一电压VP0及第二电压VPk的其中之一大于比较参考电压Vr,且第一电压VP0及第二电压VPk的其中另一小于比较参考电压Vr,则控制器160将第k个切换电容组切换回第一状态(即切换前的状态)。

图2是依照本公开一实施例所绘示的单端输入式连续近似缓存器模拟至数字转换器执行二进制窗口功能时的切换机制示意图,其中横轴表示时间,纵轴表示第一电容式数字至模拟转换器120的输出电压,以下将以M等于4来说明。基于二进制窗口为4位的窗口,故而于图2的第一次迭代运作(即k=1)至第四次迭代运作(即k=4)中,分别示出由虚线所包围出来的四块窗口区域,即WIN1~WIN4。

首先,于取样保持(sample-and-hold)运作(即k=0)中,第一电容式数字至模拟转换器120通过取样开关121接收并取样第一模拟输入信号VIP以产生第一电压VP0。在一实施例中,在此的第一模拟输入信号VIP的振幅(Amplitude)例如是等于参考电压Vref,且第一模拟输入信号VIP的共模电压(Common Mode Voltage)例如是等于参考电压Vref。比较器140可判断第一电压VP0是否大于比较参考电压Vr,从而产生第一比较结果CQ1。接着,于第一次迭代运作(即k=1),控制器160可根据第一比较结果CQ1产生第一控制信号SP1以控制切换电容组SCP1的切换运作。以下先针对第一电压VP0大于比较参考电压Vr的情况进行说明。

于取样保持运作(即k=0)中,如果第一电压VP0大于比较参考电压Vr,则比较器140可输出例如是逻辑1的第一比较结果CQ1。因此,于第一次迭代运作(即k=1)中,控制器160将切换电容组SCP1中的开关WP1进行切换以将第一电压VP0下拉,致使第一电容式数字至模拟转换器120产生对应的第二电压VP1,其中VP1=VP0-(Vref/2

接着,于第二次迭代运作(即k=2)中,控制器160将对切换电容组SCP2中的开关WP2进行切换以将第二电压VP1下拉,致使第一电容式数字至模拟转换器120产生对应的第二电压VP2,其中VP2=VP1-(Vr/2

至于连续近似缓存器模拟至数字转换器100于第三次迭代运作(即k=3)及第四次迭代运作(即k=4)的运作,则可根据上述第一次迭代运作(即k=1)及第二次迭代运作(即k=2)的说明而类推得知,故在此不再赘述。

以下针对第一电压VP0小于比较参考电压Vr的情况进行说明。于取样保持运作(即k=0)中,如果第一电压VP0小于比较参考电压Vr,则比较器140可输出例如是逻辑0的第一比较结果CQ1。因此,于第一次迭代运作(即k=1)中,控制器160将对切换电容组SCP1中的开关WP1进行切换以将第一电压VP0上拉,致使第一电容式数字至模拟转换器120产生对应的第二电压VP1,其中VP1=VP0+(Vr/2

接着,于第二次迭代运作(即k=2)中,控制器160将对切换电容组SCP2中的开关WP2进行切换以将第二电压VP1上拉,致使第一电容式数字至模拟转换器120产生对应的第二电压VP2,其中VP2=VP1+(Vr/2

至于连续近似缓存器模拟至数字转换器100于第三次迭代运作(即k=3)及第四次迭代运作(即k=4)的运作,则可根据上述第一次迭代运作(即k=1)及第二次迭代运作(即k=2)的说明而类推得知。

图3是依照本公开另一实施例所绘示的连续近似缓存器模拟至数字转换器200的电路方块示意图。连续近似缓存器模拟至数字转换器200为差动输入式模拟至数字转换器。连续近似缓存器模拟至数字转换器200用以转换差动对信号(包括第一模拟输入信号VIP及第二模拟输入信号VIN)为数字输出信号SDO。

SAR ADC 200可包括第一电容式数字至模拟转换器220、第二电容式数字至模拟转换器280、比较器240以及控制器260。第一电容式数字至模拟转换器220、比较器240以及控制器260的架构分别类似于图1的第一电容式数字至模拟转换器120、比较器140以及控制器160,故可参酌上述图1的相关说明而类推,在此不再赘述。

第二电容式数字至模拟转换器280可包括取样开关281以及切换电容组SCN1~SCN10。第二电容式数字至模拟转换器280可于一时间点通过取样开关281接收并取样第二模拟输入信号VIN以产生第三电压VN0。取样开关281可例如是通过一取样时钟信号CLKS所控制的靴带式开关。第二电容式数字至模拟转换器280受控于多个第二控制信号SN1~SN10以分别控制切换电容组SCN1~SCN10的切换运作。详细来说,切换电容组SCNi可包括电容CNi及开关WNi,其中i为1至10的整数。电容CN1~CN10的第一端耦接至比较器240的反相输入端,而电容CN1~CN10的第二端则分别通过开关WN1~WN10被切换于参考电压Vref与接地电压GND之间。开关WN1~WN10分别由第二控制信号SN1~SN10所控制。电容CN1~电容CN8的电容值分别为电容CN2~电容CN9的电容值的两倍,而电容CN9的电容值等于电容CN10的电容值。

运作上,比较器240接收来自第一电容式数字至模拟转换器220的第一电压VP0以及来自第二电容式数字至模拟转换器280的第三电压VN0。比较器240可受控于比较时钟信号CLKC以将第一电压VP0与第三电压VN0的差值与零值交越点进行比较以产生第一比较结果CQ1。特别是,控制器260可根据第一比较结果CQ1产生第一控制信号SP1~SP10及第二控制信号SN1~SN10,以分别控制切换电容组SCP1~SCP10及SCN1~SCN10的切换运作。

进一步来说,控制器260具有二进制窗口功能。控制器260可根据比较器240的输出(亦即第一比较结果CQ1)来决定切换电容组SCP1~SCP10中的至少一者及切换电容组SCN1~SCN10中的至少一者的切换运作,以将第一电容式数字至模拟转换器220的输出及第二电容式数字至模拟转换器280的输出逼近上述的二进制窗口,其中上述的二进制窗口为M位的窗口,且M为小于或等于N的正整数。详细来说,在连续近似缓存器模拟至数字转换器200的M次迭代运作的第k次迭代运作中(k小于或等于M),控制器260可将切换电容组SCP1~SCP10中的第k个切换电容组SCPk进行切换(例如自第一状态切换为第二状态),使第一电容式数字至模拟转换器220产生对应的第二电压VPk。此外,控制器260可将切换电容组SCN1~SCN10中的第k个切换电容组SCNk进行切换(例如自第一状态切换为第二状态),使第二电容式数字至模拟转换器280产生对应的第四电压VNk。接着,比较器240可将第k次迭代运作的第二电压VPk与第四电压VNk的差值与零值交越点(zero crossing point,例如0伏特)进行比较以产生对应的第二比较结果CQ2_k。控制器260可根据第一比较结果CQ1及第二比较结果CQ2_k定义(或决定)窗口区域WINk。还有,控制器260可根据第一比较结果CQ1及第二比较结果CQ2_k来决定是否将第一电容式数字至模拟转换器220的第k个切换电容组及第二电容式数字至模拟转换器280的第k个切换电容组切换回第一状态(即切换前的状态),或维持于第二状态。

下面一并参照图3及图4,图4是依照本公开一实施例所绘示的差动输入式连续近似缓存器模拟至数字转换器执行二进制窗口功能时的切换机制示意图,其中横轴表示时间,纵轴表示第一电容式数字至模拟转换器220的输出电压与第二电容式数字至模拟转换器280的输出电压的电压差(亦即比较器240的差动输入电压)。为了方便说明,以下将以M等于4(即上述的二进制窗口为4位的窗口)为例子进行说明,而M为其他正整数的实施例则可依以下说明类推。基于二进制窗口为4位的窗口,故在图4的第一次迭代运作(即k=1)至第四次迭代运作(即k=4)中,分别示出由虚线所包围出来的四块窗口区域WIN1~WIN4。

首先,于取样保持运作(即k=0)中,第一电容式数字至模拟转换器220通过取样时钟信号CLKS,控制取样开关221接收并取样第一模拟输入信号VIP以产生第一电压VP0,且第二电容式数字至模拟转换器280通过取样时钟信号CLKS,控制取样开关281接收并取样第二模拟输入信号VIN以产生第三电压VN0。在一实施例中,第一模拟输入信号VIP与第二模拟输入信号VIN的振幅(Amplitude)例如皆等于参考电压Vref,且第一模拟输入信号VIP与第二模拟输入信号VIN的共模电压(Common Mode Voltage)例如是皆相等,而第一模拟输入信号VIP与第二模拟输入信号VIN彼此的相位差例如是180度。比较器240受控于比较时钟信号CLKC,可据以判断第一电压VP0与第三电压VN0的差值是否大于零值交越点,从而产生第一比较结果CQ1。接着,于第一次迭代运作(即k=1),控制器260可根据第一比较结果CQ1产生第一控制信号SP1及第二控制信号SN1,以控制切换电容组SCP1及SCN1的切换运作。以下将先针对第一电压VP0与第三电压VN0的差值大于零值交越点(即VP0-VN0>0)进行说明。

在取样保持运作(即k=0)中,如果第一电压VP0与第三电压VN0的差值大于零值交越点,则比较器240可输出例如是逻辑1的第一比较结果CQ1。因此,在第一次迭代运作(即k=1)中,控制器260将切换电容组SCP1中的开关WP1进行切换以将第一电压VP0下拉,使第一电容式数字至模拟转换器220产生对应的第二电压VP1,其中VP1=VP0-(Vref/2)。同时,控制器260将切换电容组SCN1中的开关WN1进行切换以将第三电压VN0上拉,使第二电容式数字至模拟转换器280产生对应的第四电压VN1,其中VN1=VN0+(Vref/2)。接着,比较器240可将第一次迭代运作(即k=1)的第二电压VP1与第四电压VN1进行比较,以判断第二电压VP1与第四电压VN1的差值是否大于零值交越点。如果第二电压VP1与第四电压VN1的差值大于零值交越点,则比较器240将输出例如是逻辑1的第二比较结果CQ2_1。可以理解的是,如果第二电压VP1与第四电压VN1的差值大于零值交越点,表示第一电压VP0与第三电压VN0的差值大于Vref而位于窗口区域WIN1之外,故控制器260将切换电容组SCP1中的开关WP1以及切换电容组SCN1中的开关WN1维持在切换后的状态,此时第二电压VP1与第四电压VN1的差值即为VP1-VN1=[VP0-(Vref/2)]-[VN0+(Vref/2)]=(VP0-VN0)-Vref。相对地,如果第二电压VP1与第四电压VN1的差值小于零值交越点,则比较器240将输出例如是逻辑0的第二比较结果CQ2_1。可以理解的是,如果第二电压VP1与第四电压VN1的差值小于零值交越点,表示第一电压VP0与第三电压VN0的差值小于Vref而位于窗口区域WIN1之内,故控制器260将切换电容组SCP1中的开关WP1以及切换电容组SCN1中的开关WN1回复至切换前的状态,此时第二电压VP1与第四电压VN1的差值即为VP1-VN1=VP0-VN0。

接着,于第二次迭代运作(即k=2)中,控制器260将切换电容组SCP2中的开关WP2进行切换以将第二电压VP1下拉,致使第一电容式数字至模拟转换器220产生对应的第二电压VP2,其中VP2=VP1-(Vref/4)。同时,控制器260将切换电容组SCN2中的开关WN2进行切换以将第四电压VN1上拉,致使第二电容式数字至模拟转换器280产生对应的第四电压VN2,其中VN2=VN1+(Vref/4)。接着,比较器240可将第二次迭代运作(即k=2)的第二电压VP2与第四电压VN2进行比较,以判断第二电压VP2与第四电压VN2的差值是否大于零值交越点。如果第二电压VP2与第四电压VN2的差值大于零值交越点,则比较器240将输出例如是逻辑1的第二比较结果CQ2_2。可以理解的是,如果第二电压VP2与第四电压VN2的差值大于零值交越点,表示第二电压VP1与第四电压VN1的差值大于0.5Vref而位于窗口区域WIN2之外,故控制器260将切换电容组SCP2中的开关WP2以及切换电容组SCN2中的开关WN2维持在切换后的状态,此时VP2-VN2=[VP1-(Vref/4)]-[VN1+(Vref/4)]=(VP1-VN1)-0.5Vref。相对地,如果第二电压VP2与第四电压VN2的差值小于零值交越点,则比较器240将输出例如是逻辑0的第二比较结果CQ2_2。可以理解的是,如果第二电压VP2与第四电压VN2的差值小于零值交越点,表示第二电压VP1与第四电压VN1的差值小于0.5Vref而位于窗口区域WIN2之内,故控制器260将切换电容组SCP2中的开关WP2以及切换电容组SCN2中的开关WN2回复至切换前的状态,此时VP2-VN2=(VP1-VN1)。

至于第一电容式数字至模拟转换器220与第二电容式数字至模拟转换器280分别于第三次迭代运作(即k=3)及第四次迭代运作(即k=4)的切换运作,则可根据上述第一次迭代运作(即k=1)及第二次迭代运作(即k=2)的说明而类推得知,故在此不再赘述。可以理解的是,在第一电压VP0与第三电压VN0的差值大于零值交越点的情况下,控制器将根据第一比较结果CQ1与第二比较结果CQ2_k来控制第一电容式数字至模拟转换器220与第二电容式数字至模拟转换器280的切换运作。另一方面,在第一电压VP0与第三电压VN0的差值小于零值交越点,控制器260将根据第一比较结果CQ1与第二比较结果CQ2_k来控制第一电容式数字至模拟转换器220与第二电容式数字至模拟转换器280的切换运作,其详细运作可参照上述说明而类推得知,故不再赘述。

校正方法

在一实施例中,模拟至数字转换器在操作模式进行在模拟至数字转换正常操作,在校正模式进行校正;在一实施例中,在操作模式前,可先行进入校正模式;在一实施例中,可在操作模式进行一段时间后进入校正模式;在一实施例中,可每进行一段时间的操作模式后(周期性地)进入校正模式。接着将说明本公开实施例的电容校正的方法,在此做为解说范例的是上面图3所说明的电路架构。在这个例子的架构中,为了着眼在电容校正的部分,将电路图再略作简化。在此范例中,以具有11个电容为范例,其中电容CP1~CP5、CN1~CN5待校正的电容,而电容CP6~CP11、CN6~CN11为准确的电容;在实施时,各电容可各为一个电容群,例如,电容CP1、CN1可以各由8个较小的电容所组成,电容CP2、CN2可以各由4个较小的电容所组成,本发明不加以限制。电容CP6~CP11、CN6~CP11在制作时,可以通过要求制程参数达到所要求的准确度。在一实施例中,在未增加额外电路下,以准确的电容做为参考,校正较为不准的电容。在本实施例以准确的电容CP6-CP11、CN6~CN11来校正较为不准确的电容CP1-CP5、CN1~CN5。

图5为本公开一实施例的校正的时序示意图。在本公开实施例中,校正过程是可以执行多次,并可以藉由多次校正所得的闪烁(flicker)噪声与比较器的偏移(offset)以及电容C1~C5的平均值,使获得的校正值更为精准。如图5所示,在每一个校正循环的校正顺序为先校正闪烁噪声与比较器的偏移(即图中的O&F,两者统称噪声),再校正电容CP5~CP1、CN5~CN1。在一实施例中,亦即在取样时钟CLKS第一个周期进行闪烁噪声与比较器的偏移的校正,在取样时钟CLKS第二个周期至第六周期分别进行电容CP5~CP1和CN5~CN1的校正。在取样时钟CLKS第一个周期获得比较器的偏移(offset)与闪烁(flicker)噪声的信息Do[x],接着于每个取样时钟CLKS,依序进行电容CP5~CP1、CN5~CN1的校正,而分别获得校正信息Do[x+1]~Do[x+5],其中Do[x]为模拟数字转换器输出的二进制数字码,其中,x代表每个校正周期,x为正整数,而y代表一个校正程序的重复次数,其为自然数。同理,上述校正程序一直重复进行,例如在取样时钟CLKS的第七至第十二周期可以获得比较器的偏移与闪烁(flicker)噪声以及电容CP5~CP1和CN5~CN1的校正信息Do[x+6]~Do[x+11]。以此类推,此整体校正程序将会持续数个周期来进行平均。

接着配合电路结构来说明校正的方法,其中将以闪烁噪声与比较器的偏移、电容CP5、CN5与电容CP1、CN1的校正来进行说明,电容CP4、CN5至CP2、CN2的校正方法与电容CP5、C1和电容CN5、CN1的校正方法相似。

接着以图6至图8说明本公开范例的电容校正方法。图6为本公开一实施例的闪烁噪声与比较器340的偏移的校正示意图。

如图6所示,连续近似缓存器模拟至数字转换器300可包括第一电容式数字至模拟转换器310、第二电容式数字至模拟转换器320、比较器340以及控制器360。第一电容式数字至模拟转换器310、第二电容式数字至模拟转换器320的输出VCP和VCN分别连接到比较器340的两个输入端。电容CP1、CN1对应MSB,依序而下为电容CP2与CN2、电容CP3与CN4......,但本发明不以此为限。比较器340输出的比较结果再传送到控制器360。在一实施例中,控制器360进行图1~图4所说明的模拟数字转换的控制,以及/或是进行电容校正以及闪烁噪声与比较器360的偏移的量化等控制。

首先进行闪烁噪声与比较器340的偏移的校正。如图6所示,当取样时钟(samplingclock)CLKS为高电位时,此时将电容器CP1~CP11与CN1~CN11的第一端(或称顶板)的开关SW

在取样时钟CLKS转为低电位时,控制器360将开关SWTOP1、SWTOP2断开,使电容CP1~CP11与电容CN1~CN11的第一端与第一输入电压VIP、第二输入电压VIP断开,电容CP1~CP5与电容CN1~CN5(即,需进行校正的电容)的所有第二端分别藉由开关WP1~WP5与开关WN1~WN5而维持在第一参考电压Vcm。当取样时钟CLKS由高电位转为低电位后,进入校正程序,在比较时钟(comparator clock)CLKC的T0周期,开始偏移和闪烁噪声的校正。在一实施例中,在比较时钟CLKC的T1-T5周期,电容CP1~CP5的开关WP1~WP5与电容CN1~CN5的开关WN1~WN5不会进行切换动作。经过比较时钟CLKC的5个周期(T1-T5)后,由第一电容式数字至模拟转换器310的准确电容CP6-CP11和第二电容式数字至模拟转换器320的准确电容CN6-CN11(图6所示的zADC 5)进行SAR ADC 300的数字至模拟转换的操作。在进行SAR ADC300的数字至模拟转换的操作时,电容CP6~CP11与电容CN6~CN11的第二端不需再接到第一参考电压Vcm,可依SAR ADC 300的操作接到第二参考电压Vref或第三参考电压GND。在一实施例中,zADC为由准确的电容及/或已校正的电容所组成的对应的模拟至数字转换器。通过zADC 5每个位的结果,决定相对应的电容切换,即进行SAR ADC 300的二进制搜寻法。若该位下,比较器340的结果为1,则代表该位的VCP侧的电容藉由第二端的开关从Vcm切换到GND、VCN侧的电容藉由第二端的开关从第一参考电压Vcm切换到第二参考电压Vref。反之,若在该位下,比较器340的结果为0,则代表该位VCP侧的电容藉由第二端的开关从第一参考电压Vcm切换到第二参考电压Vref,VCN侧的电容藉由第二端的开关从第一参考电压Vcm切换到第三参考电压GND。如此,切换完后,进行下个位的比较,直到所有位转换完成。zADC 5所得到的二进制七个数字位输出为闪烁噪声与比较器340的偏移的信息。在本实施例中,以所有的准确电容量测闪烁噪声与比较器340的偏移的信息,但本发明并不以此为限,在一实施例中,可以部份的准确电容量测闪烁噪声与比较器340的偏移的信息,例如包括LSB的较低位的数个电容的对应ADC量测闪烁噪声与比较器340的偏移的信息,具体而言,例如可以CP7~CP11、CN7~CN11量测,量测方式与上述类似,例如当取样时钟CLKS由高电位转为低电位后,进入校正程序,在比较时钟CLKC的T0周期,开始偏移和闪烁噪声的校正。在比较时钟CLKC的T1-T5周期,电容CP1~CP6的开关WP1~WP6与电容CN1~CN6的开关WN1~WN6不会进行切换动作。经过比较时钟CLKC的6个周期(T1-T6,T6未绘示,T6为T5的下一周期)后,由第一电容式数字至模拟转换器310的准确电容CP7-CP11和第二电容式数字至模拟转换器320的准确电容CN7-CN11进行SAR ADC 300的数字至模拟转换的操作。在进行SAR ADC 300的数字至模拟转换的操作时,电容CP7~CP11与电容CN7~CN11的第二端不需再接到第一参考电压Vcm,可依SAR ADC 300的操作接到第二参考电压Vref或第三参考电压GND。所得到的二进制六个数字位输出为闪烁噪声与比较器340的偏移的信息。本实施例中的高电位及低电位仅为例示,在另一实施例中,也可在取样时钟CLKS为低电位时进行电容重置,在取样时钟CLKS为高电位时进行校正,本公开不对此做限制。

当将闪烁噪声与比较器340的偏移量化后,进行第一电容式数字至模拟转换器310与第二电容式数字至模拟转换器320的电容CP1~CP5与电容CN1~CN5的校正程序。在一实施例中,电容校正从待校电容中的最小位开始,于本实施例中,由电容CP5与电容CN5开始,亦即位排序最接近准确的电容CP6-CP11与电容CN6~CN11。

图7为本公开一实施例的电容校正的示意图。以下以实施例说明电容CP5、CN5的校正。如图7所示,取样时钟CLKS为高电位时,第一电容式数字至模拟转换器310的电容CP1~CP11的第一端均经由开关SW

在取样时钟CLKS转为低电位后,在比较时钟CLKC的T0~T4周期,对应的第一电容式数字至模拟转换器310和第二电容式数字至模拟转换器320的电容CP1-CP4与电容CN1~CN4的第二端均分别经由开关WP1~WP4与开关WN1~WN4维持在第一参考电压Vcm,而与第一电容式数字至模拟转换器310和第二电容式数字至模拟转换器320分别对应的SW

接着,在比较时钟CLKC的T5周期,开始进行电容CP5、CN5的校正。此时,第一电容式数字至模拟转换器310的电容CP5的第二端通过开关WP5连接到第二参考电压Vref(参考电压),而第二电容式数字至模拟转换器320的电容CN5的第二端通过开关WN5接到第三参考电压GND(接地电压)。接着,在比较时钟CLKC的T5周期后,进行电容CP6~CP11与CN6~CN11对应的zADC 5的模拟至数字转换的操作。

如前所述,第一电容式数字至模拟转换器310的电容CP6-CP11与第二电容式数字至模拟转换器320的电容CN6-CN11可以通过要求制程参数来准确制作,所以由CP6-CP11与CN6~CN11对应的zADC 5进行模拟至数字转换可得到准确的结果,以校正电容CP5、CN5。

在一实施例中,由zADC 5进行模拟至数字转换得到的结果包含闪烁噪声与比较器340的偏移,在一实施例中,由zADC 5进行模拟至数字转换得到的结果减去闪烁噪声与比较器340的偏移(例如前述所得的闪烁噪声与比较器340的偏移),以得到电容CP5及/或电容CN5的电容权重W

图8为本公开一实施例的电容校正的示意图。以下以实施例说明电容CP1、CN1的校正。如图8所示,取样时钟CLKS为高电位时,第一电容式数字至模拟转换器310的电容CP1~CP11的第一端均经由开关SW

在取样时钟CLKS转为低电位后,与第一电容式数字至模拟转换器310和第二电容式数字至模拟转换器320分别对应的SW

如前所述,第一电容式数字至模拟转换器310的电容CP6~CP11与第二电容式数字至模拟转换器320的电容CN6~CN11为准确的电容,且电容CP2~CP5、CN2~CN5也进行过校正,后续由zADC1的电容CP2-CP11、CN2~CN11进行一般连续近似模拟数字转换动作时,可以对电容CP1、CN1进行校正。以此得到的电容CP1、CN1的权重包含闪烁噪声与比较器340的偏移,故可减去闪烁噪声与比较器340的偏移,以得到电容CP1、CN1的电容权重W

以与上述类似的方法,可以对第一电容式数字至模拟转换器310的电容CP2-CP4与第二电容式数字至模拟转换器320的电容CN2-CN4进行电容权重的校正。以校正电容CP4、CN4为例,在取样时钟CLKS为高电位时,重置电容CP1~CP11、CN1~CN11,在取样时钟CLKS为低电位且比较时钟CLKC的T0~T3周期间,断开SW

在一实施例中,SAR ADC 300在校正模式的校正程序的时序与操作模式的时序相同或相似,因此不需增设或改变电路,即可以达到电容的校正以及闪烁噪声与比较器340的偏移的量测。

在一实施例中,在获得各电容的电容权重后,可以电容权重修正第一电容式数字至模拟转换器310及/或第二电容式数字至模拟转换器320所输出的数字码,以得到准确的数字码。在一实施例中,由于电容不准确,可能使第一电容式数字至模拟转换器310及/或第二电容式数字至模拟转换器320所输出的数字码与正确的数字码有偏差,在获得各电容的电容权重后,可使用冗余电路(未绘示)修正偏差,以获得正确的数字码,在一实施例中,可量化闪烁噪声和比较器340的偏移。

以下以另一实施例说明电容CP1~CP5及电容CN1~CN5的电容权重W

图9A绘示本公开一实施例的电路方块变化例的示意图。如图9A所示,连续近似缓存器模拟至数字转换器300可以更包括:编码器380,其耦接到控制器360,用以接收控制器360的输出;以及校正处理器400,耦接至编码器380。在校正模式下以校正电容CP5、CN5为例,SAR ADC 300输出二进制制数字结果至编码器380,编码器380将二进制制数字结果编码后产生十进制制的编码结果,再将该编码结果传送到校正处理器400。校正处理器400可利用循环对进行y次的校正程序进行平均。在一实施例中,可由校正处理器400执行式(1)的运算。在一实施例中,可以平均后的电容权重W

图9B绘示本公开一实施例的电路方块变化例的示意图。如图9B所示,连续近似缓存器模拟至数字转换器300可以还包括时钟缩减电路345,可用以产生缩减比较时钟RCLKC。在一实施例中,时钟缩减电路345可缩减比较时钟CLKC,以产生缩减比较时钟RCLKC。在一实施例中,可使用缩减比较时钟RCLKC进一步地减少校正时间。

在上述实施例中,在量测噪声后,从最靠近LSB的待校电容开始校正,直到最靠近MSB的待校电容为止。例如电容CP1~CP5、CN1~CN5的校正是从电容CP5、CN5开始,依序校正到电容CP1、CN1。依此顺序,第一个校正的电容CP5、CN5是最靠近LSB的待校电容,作为校正基础的电容CP6~CP11、CN6~CN11均为准确的电容。校正电容CP5、CN5后,再以电容CP5~CP11、CN5~CN11校正下一个最靠近LSB的待校电容CP4、CN4。以此类推,每次皆校正最靠近LSB的待校电容,用来校正待校电容的电容包括先前校正过的电容以及准确的电容来进行。

但是,本公开并不限定于此。在另一实施例中,在量测噪声后,从最靠近MSB的待校电容开始校正,直到最靠近LSB的待校电容为止。但是,从MSB侧往LSB侧进行校正的说明如下。

首先使用电容CP2-CP11、CN2~CN11(例如图8中的zADC 1)进行电容CP1、CN1的校正。此时,zADC 1中的电容CP6-CP11、CN6~CN11是准确的,但是电容CP2-CP5、CN2~CN5尚未经过校正。因此,当以上述方式获得电容CP1、CN1的权重W

接着,再从如图9A或9B所示的校正处理器400,以电容CP5、CN5的电容权重W

在一实施例中,若连续近似缓存器模拟至数字转换器的准确电容为第0至第a位,则在一实施例中,校正顺序可以是以第i位从i=a+1位起,重复地往上递增,产生各电容的电容权重,直到产生第(Nd-1)位的电容权重为止。在一实施例中,校正顺序可以是以第i位从i=Nd-1位起,重复地往下递减,产生各电容的电容权重,直到产生第a+1位的电容权重为止。

在一实施例中,校正时序使用连续近似缓存器模拟至数字转换器在操作模式下时的时钟顺序,故可以不增设或改变电路的硬件结构,便可以达到电容的校正以及闪烁噪声与比较器340的偏移的量测。在另一实施例中,可以进一步减少校正时间,例如,如图7所示,当进行电容CP5、CN5的校正时,使用原本操作模式的时序,在比较时钟CLKC的T0~T4周期间,电容不进行切换,因此,可缩减T0~T4周期,以减少校正时间。

图10A与10B绘示本公开一实施例的时钟信号缩减示意图。如图10A的上半图所示,在操作模式时,T0周期为取样保持运作的周期,T1~T5周期为电容CP1~CP5、CN1~CN5的对应模拟至数字转换周期。在校正模式时,进行闪烁噪声与比较器340的偏移的量测后,周期T1~T5期间电容CP1~CP5、CN1~CN5并未切换,直到比较时钟CLKC的下一个周期后再进行zADC 5的模拟至数字转换。在一实施例中,如图10A的下半图所示,在校正模式省略T1~T5周期;亦即,周期T0的下一周期,即进行zADC 5的运作,其时序如缩减比较时钟RCLKC的波形所示。

在一实施例中,如图10B的上半图所示,在操作模式时,T0周期为取样保持运作的周期,T1~T5周期为电容CP1~CP5、CN1~CN5的对应模拟至数字转换周期;在校正模式时,进行闪烁噪声与比较器340的偏移的量测后,周期T1~T4期间电容CP1~CP4、CN1~CP4并未切换,直到周期T5时切换电容CP5、CN5第二端的电压,接着进行zADC 5的模拟至数字转换。在一实施例中,如图10B的下半图所示,在校正模式省略T0~T4周期;也就是说,在取样时钟CLKS转为低电位后,比较时钟CLKC的第一个周期可以是周期T5,直接进入电容CP5、CN5的校正程序,其时序如缩减比较时钟RCLKC的波形所示。在此实施例中,可以不需等待周期T0~T4,以使校正时间更快。同理,在进行电容CP4、CN4校正时,可省略周期T0~T3的等待周期。在进行电容CP3、CN3校正时,可省略周期T0~T2的等待周期。在进行电容CP2、CN2校正时,可省略周期T0~T1的等待周期。在进行电容CP1、CN1校正时,可省略周期T0的等待周期。如此,整体的校正时间可以更为缩短。

在一实施例中,电容式数字至模拟转换器具有Nd位,Nd为正整数,当校正第i位的电容时,缩减比较时钟RCLKC省略了操作模式时序(比较时钟CLKC)中第Nd-1位电容至第(i+1)位的等待周期,其中i为小于Nd的整数。在一实施例中,如图9B所示,可以在连续近似缓存器模拟至数字转换器300中增加时钟缩减电路345,用以进行时钟缩减,亦即对操作模式的比较时钟CLKC缩减成缩减比较时钟RCLKC,省略等待周期。

此外,在上述校正程序中,对待校电容进行校正时,第一电容式数字至模拟转换器310的待校电容的第二端电压被切换而连接到第二参考电压Vref,而第二电容式数字至模拟转换器320的待校电容的第二端被切换而连接到第三参考电压GND,但本公开并不限定于此。例如,第一电容式数字至模拟转换器310的待校电容的第二端电压被切换而连接到第三参考电压GND,而第二电容式数字至模拟转换器320的待校电容的第二端被切换而连接到第二参考电压Vref。在另一实施例中,第一电容式数字至模拟转换器310的待校电容的第二端电压可以连接到第二参考电压Vref或第三参考电压GND,亦即可以切换到不同的参考电压,在另一实施例中,也可以切换到其他电压。同理,第二电容式数字至模拟转换器320的待校电容的第二端电压可以连接到第二参考电压Vref或第三参考电压GND,亦即可以切换到不同的参考电压,在另一实施例中,也可以切换到其他电压。在另一实施例中,第二参考电压可以是Vref或GND的其中一个电压,第三参考电压可以是Vref或GND的其中另外一个电压,例如第二参考电压可以是GND,第三参考电压可以是Vref。

在上述实施例中,以差动电路(differential circuit)(例如图3所示的电路)说明电容校正的程序,但是单端电路(single ended circuit)(例如图1所示的电路)也可以适用本公开的电容校正方法。亦即,比较器340的输入端只连接一个电容式数字至模拟转换器也可以适用本公开的电容校正方法。单端电路架构下的电容校正方法与差动电路的校正方法相同或相似,在此省略其说明。

图11绘示本公开的连续近似缓存器模拟至数字转换器的校正方法的流程示意图。在一实施例中,连续近似缓存器模拟至数字转换器包含至少一个Nd位电容式数字至模拟转换器,电容式数字至模拟转换器的电容有对应第0位至第Nd-1位,其中第0位的电容至第i-1位的电容例如是上述的准确的电容(例如电容CP11~CP6、CN11~CN6),而第i位电容至第Nd-1位电容例如是待校电容(例如上述的电容CP5~CP1、CN5~CN1),i为小于Nd的整数。在一实施例中,Nd位电容式数字至模拟转换器所转换的数字码经SAR ADC的转换后可得到Nd+1个位的数字码,例如SAR ADC可不需电容运作,而比较VIP与VIN的差异,以获得多1个位的数字码。如图11所示,在步骤S100,将第i位至第(Nd-1)位的电容耦接第一参考电压,根据第(i-1)位至第0位的电容的运作产生第一数字码,其中i为小于Nd的整数。在一实施例中,步骤S100可以获得噪声,该噪声可以包括闪烁噪声以及比较器的偏移。

在一实施例中,将第Nd-1位至第0位的电容的第一端连接到输入电压(例如VIP,VIN),电容的第二端连接第一参考电压(例如Vcm);将所述第Nd-1个位至所述第0位的电容的第一端断开所述输入电压;以及利用所述第(i-1)个位至所述第0位的电容所对应的连续近似缓存器模拟至数字转换器产生第一数字码,以量测所述噪声。

接着,执行步骤S102。在步骤S102,将第(i+1)位至第(Nd-1)位的电容耦接第一参考电压,将第i位的电容耦接第二参考电压,根据第(i-1)位至第0位的电容的运作产生第二数字码。在一实施例中,步骤S102基于第(i-1)个位至第0位电容的运作,校正第i个位的电容,并由所述比较器产生第二数字码,将述第二数字码与所述第一数字码相减以产生所述第i个位电容的权重。

在一实施例中,将第i个位电容耦接至第二参考电压或第三参考电压,第(Nd-1)个位至第(i+1)个位电容耦接至所述第一参考电压,利用第(i-1)个位至第0位电容所对应的连续近似缓存器模拟至数字转换器产生第二数字码,并由所述第二数字码与所述第一数字码产生所述第i个位电容的权重。

在一实施例中,将第(Nd-1)个位至所述第0个位的电容(如CP1~CP11、CN1~CN11)的第一端连接到输入电压(如VIP、VIN),电容的第二端连接所述第一参考电压(如Vcm);将第Nd-1个位至所述第0位的电容的第一端断开所述输入电压;将第i个位的电容的第二端耦接至第二参考电压(如Vref)或第三参考电压(如GND);以及利用第(i-1)个位至第0位的电容所对应的连续近似缓存器模拟至数字转换器产生第二数字码,并由所述第二数字码与所述第一数字码产生第i个位电容的所述电容权重。

在步骤S106,判断i是否已经等于Nd-1,亦即上述动作是否已经进行到第Nd-1个位。如果尚未进行到第Nd-1个位,亦即判断结果为否,则进行步骤S108。步骤S108递增i,即i=i+1,再继续执行步骤S102,直至i=Nd-1为止。另外,当在步骤S106,判断i是否已经等于Nd-1,亦即到第(Nd-1)个位电容的电容权重都已经产生,并且将连续近似缓存器模拟至数字转换器校正完毕。在一实施例中,可以在步骤S102和S106间加一步骤,根据第一数字码与第二数字码产生第i位的所述电容的电容权重;在一实施例中,也可在步骤S106判断i=Nd-1后,根据各次执行步骤S102获得的各个第二数字码产生各个位的电容的电容权重。获得各位或所有位的电容权重后,可依据获得的电容权重修正对应的连续近似缓存器模拟至数字转换器。

图12是根据本发明一实施例的连续近似缓存器模拟至数字转换器的校正方法的流程示意图。在此实施例中,不须将所有准确的电容皆用来获得闪烁噪声以及比较器的偏移。连续近似缓存器模拟至数字转换器包括至少一电容式数字至模拟转换器以及控制器,至少一电容式数字至模拟转换器包括对应于Nd位的Nd个电容,Nd为正整数。如图12所示。在步骤S1202中,将第z位至第(Nd-1)位的电容耦接第一参考电压,根据第(z-1)位至第0位的电容的运作产生第一数字码,其中z为小于Nd的整数。在一实施例中,例如第0~5位的电容式数字至模拟转换器具有准确的电容,Nd例如为11,z例如为5,将第5位至第10位的电容耦接第一参考电压,根据第4位至第0位的电容的运作产生第一数字码,第一数字码包括闪烁噪声以及比较器的偏移。在步骤S1204中,将第(i+1)位至第(Nd-1)位的电容耦接第一参考电压,将第i位的电容耦接第二参考电压,根据第(i-1)位至第0位的电容的运作产生第二数字码,其中i为小于Nd的整数,且z小于i。在此实施例中,i例如为6,将第7位至第10位的电容耦接第一参考电压,将第6位的电容耦接第二参考电压,根据第5位至第0位的电容的运作产生第二数字码。在步骤S1206中,根据第一数字码与第二数字码产生第i位的电容的电容权重。在此实施例中,根据利用第4位至第0位的电容的运作产生的第一数字码与利用第5位至第0位的电容产生的第二数字码产生第6位的电容的电容权重,在步骤S1208中,根据第i位的电容的电容权重校正连续近似缓存器模拟至数字转换器。

图13是根据本发明一实施例的连续近似缓存器模拟至数字转换器的校正方法的流程示意图。连续近似缓存器模拟至数字转换器包括至少一电容式数字至模拟转换器以及控制器,至少一电容式数字至模拟转换器包括对应于Nd位的Nd个电容,Nd为正整数。如图13所示。在步骤S1302中,将第i位至第(Nd-1)位的电容耦接第一参考电压,根据第(i-1)位至第0位的电容的运作产生第一数字码,其中i为小于Nd的整数。在一实施例中,Nd例如为11,i例如为6,将第6位至第10位的电容耦接第一参考电压,根据第5位至第0位的电容的运作产生第一数字码,第一数字码包括闪烁噪声以及比较器的偏移。在步骤S1304中,将第(i+1)位至第(Nd-1)位的电容耦接第一参考电压,将第i位的电容耦接第二参考电压,根据第(i-1)位至第0位的电容的运作产生第二数字码。在此实施例中,i例如为6,将第7位至第10位的电容耦接第一参考电压,将第6位的电容耦接第二参考电压,根据第5位至第0位的电容的运作产生第二数字码。在步骤S1306中,根据第一数字码与第二数字码产生第i位的电容的电容权重。在此实施例中,根据利用第5位至第0位的电容的运作产生的第一数字码与利用第5位至第0位的电容产生的第二数字码产生第6位的电容的电容权重,在步骤S1308中,根据第i位的电容的电容权重校正连续近似缓存器模拟至数字转换器。

由上述说明可以得知,本公开实施例的电容校正方法可以不需增加额外的电路架构,可以原本的连续近似缓存器模拟至数字转换器的操作架构下进行。例如将驱动连续近似缓存器模拟至数字转换器的进行模拟至数字转换的比较时钟CLKC做为校正时钟,在比较时钟CLKC的T1~T5周期间,在操作模式中可以用来驱动电容CP1~CP5、CN1~CN5进行模拟至数字转换,在校正模式中,可以将被校正的电容连接到第二参考电压Vref或第三参考电压GND,而其他尚未被校正的电容则连接到第一参考电压Vcm。因此,在一实施例中,可改变控制器360内的控制序列(control sequence)以适用于操作模式及校正模式,而不需大幅改变整体的电路架构,亦不需增大电容的面积,整体电路的尺寸也就不会变大。

综上所述,基于上述本公开的说明,若是需校正电容数量为NumC,校正所需时间可所减为(NumC+1)周期,较传统校正所需2NumC周期,速度提升约2倍。校正流程若连续重复多次,亦可用来消除电路所产生的白噪声,使得校正更为准确。本公开一实施例可不需在信号路径上增加电路,即可得到闪烁噪声与比较器偏移的信息。

此外,本公开一实施例可改善因校正而累积的电容权重偏差,来进一步提升电容式数字至模拟转换器的积分非线性度。

根据本公开一种实施方式,提供一种连续近似缓存器模拟至数字转换器的校正方法。所述连续近似缓存器模拟至数字转换器包括至少一电容式数字至模拟转换器以及控制器,所述至少一电容式数字至模拟转换器包括对应于Nd位的Nd个电容,其中Nd为正整数。所述连续近似缓存器模拟至数字转换器的电容校正方法包括:将第z位至第(Nd-1)位的所述电容耦接第一参考电压,根据第(z-1)位至第0位的所述电容的运作产生第一数字码,其中z为小于Nd的整数;将第(i+1)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第i位的所述电容耦接第二参考电压,根据所述第(i-1)位至所述第0位的所述电容的运作产生第二数字码,其中i为小于Nd的整数,且z小于i;根据所述第一数字码与所述第二数字码产生所述第i位的所述电容的电容权重;以及根据所述第i位的所述电容的所述电容权重校正所述连续近似缓存器模拟至数字转换器。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,其中将所述第z位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,根据所述第(z-1)位至所述第0位的所述电容的运作产生所述第一数字码包括:将所述第(Nd-1)位至所述第0位的所述电容的第一端耦接输入电压,所述第(Nd-1)位至所述第0位的所述电容的第二端耦接所述第一参考电压;将所述第(Nd-1)位至所述第0位的所述电容的所述第一端断开所述输入电压;以及利用所述第(z-1)位至所述第0位的电容所对应的所述连续近似缓存器模拟至数字转换器产生所述第一数字码。

根据本公开一种实施方式,提供一种连续近似缓存器模拟至数字转换器的校正方法,其中所述连续近似缓存器模拟至数字转换器包括至少一电容式数字至模拟转换器以及控制器,所述至少一电容式数字至模拟转换器包括对应于Nd位的Nd个电容,其中Nd为正整数。所述连续近似缓存器模拟至数字转换器的电容校正方法包括:将第i位至第(Nd-1)位的所述电容耦接第一参考电压,根据第(i-1)位至第0位的所述电容的运作产生第一数字码,其中i为小于Nd的整数;将第(i+1)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第i位的所述电容耦接第二参考电压,根据所述第(i-1)位至所述第0位的所述电容的运作产生第二数字码;根据所述第一数字码与所述第二数字码产生所述第i位的所述电容的电容权重;以及根据所述第i位的所述电容的所述电容权重校正所述连续近似缓存器模拟至数字转换器。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,还包括多次执行所述电容校正方法,以获得所述第i位所述电容权重的平均值。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,其中将所述第i位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,根据所述第(i-1)位至所述第0位的所述电容的运作产生所述第一数字码包括:将所述第(Nd-1)位至所述第0位的所述电容的第一端耦接输入电压,所述第(Nd-1)位至所述第0位的所述电容的第二端耦接所述第一参考电压;将所述第(Nd-1)位至所述第0位的所述电容的所述第一端断开所述输入电压;以及利用所述第(i-1)位至所述第0位的电容所对应的所述连续近似缓存器模拟至数字转换器产生所述第一数字码。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,其中将所述第(i+1)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第i位的所述电容耦接所述第二参考电压,根据所述第(i-1)位至所述第0位的所述电容的运作产生所述第二数字码包括:将所述第(i+1)位至所述第(Nd-1)位的所述电容的第二端耦接所述第一参考电压,将所述第i位的电容的第二端耦接至所述第二参考电压;以及利用所述第(i-1)位至所述第0位的所述电容所对应的所述连续近似缓存器模拟至数字转换器产生所述第二数字码。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,其中所述至少一电容式数字至模拟转换器包括第一电容式数字至模拟转换器与第二电容式数字至模拟转换器,其中将所述第i位的电容的所述第二端耦接所述第二参考电压包括:所述第一电容式数字至模拟转换器的所述第i位的所述电容的第二端耦接所述第二参考电压;以及所述第二电容式数字至模拟转换器的所述第i位的所述电容的第二端耦接第三参考电压。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,其中所述连续近似缓存器模拟至数字转换器还包括比较器,所述输入电压由所述比较器的输入共模电压决定。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,还包括:产生所述第二数字码后,将第(i+2)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第(i+1)位的所述电容耦接所述第二参考电压,根据所述第i位至所述第0位的所述电容的运作产生第三数字码;以及根据所述第一数字码与所述第三数字码产生所述第i+1位的所述电容的电容权重。在一实施例中,将i重复往上递增,以产生各电容的电容权重,到产生第(Nd-1)位的电容权重为止。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,还包括:产生所述第二数字码后,将所述第i位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第(i-1)位的所述电容耦接所述第二参考电压,根据第(i-2)位至所述第0位的所述电容的运作产生第三数字码;以及根据所述第一数字码与所述第三数字码产生所述第i-1位的所述电容的电容权重。在一实施例中,将i重复往下递减,产生各电容的电容权重,直到产生第(a+1)位的电容权重为止。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,还包括:根据第(j-1)位至第i位的所述电容的电容权重获得第j位的所述电容的电容权重,其中Nd>j>i。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,其中所述电容校正方法的校正时序与所述连续近似缓存器模拟至数字转换器的操作模式时序相同。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,其中该所述电容校正方法在校正第i位的电容时,所述电容校正方法的校正时序省略操作模式时序中第(Nd-1)位电容至第(i+1)位的等待周期。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,其中所述连续近似缓存器模拟至数字转换器还包括比较器,所述第一数字码包括闪烁噪声以及所述比较器的偏移的信息。

在上述连续近似缓存器模拟至数字转换器的电容校正方法,其中根据所述第一数字码与所述第二数字码产生所述第i位的所述电容的电容权重包括将所述第一数字码与所述第二数字码相减以产生所述第i位的所述电容的电容权重。

根据本公开另一实施方式,提供一种具有校正功能的连续近似缓存器模拟至数字转换器,包括:至少一电容式数字至模拟转换器,受控于多个控制信号以分别控制所述至少一电容式数字至模拟转换器的Nd个切换电容的切换运作,其中Nd为正整数;比较器,耦接所述至少一电容式数字至模拟转换器,用以将所述至少一电容式数字至模拟转换器的输出与比较电压进行比较;以及控制器,耦接所述比较器以及所述至少一电容式数字至模拟转换器,用以根据所述比较器的输出产生所述控制信号及数字输出信号。所述控制器在校正模式时,藉由所述比较器的(Nd+1)次运作的结果获得所述至少一电容式数字至模拟转换器的第i位的电容权重,其中i为小于Nd的整数。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,其中所述控制器在操作模式时,根据所述比较器的所述输出而将所述至少一电容式数字至模拟转换器的所述输出逼近Nd位的窗口,藉由所述比较器的(Nd+1)次比较运算的结果来完成将所述至少一电容式数字至模拟转换器的所述输出逼近所述Nd位的窗口的一运作。

根据本公开另一实施方式,提供一种具有校正功能的连续近似缓存器模拟至数字转换器,包括:至少一Nd位电容式数字至模拟转换器,具有Nd位的电容,其中Nd为正整数;控制器,耦接所述至少一个电容式数字至模拟转换器。所述控制器用以执行以下电容校正程序:将第z位至第(Nd-1)位的所述电容耦接第一参考电压,根据第(z-1)位至第0位的所述电容的运作产生第一数字码,其中z为小于Nd的整数;将第(i+1)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第i位的所述电容耦接第二参考电压,根据所述第(i-1)位至所述第0位的所述电容的运作产生第二数字码,其中i为小于Nd的整数,且z小于i;根据所述第一数字码与所述第二数字码产生所述第i位的所述电容的电容权重;以及根据所述第i位的所述电容的所述电容权重校正所述连续近似缓存器模拟至数字转换器。

根据本公开另一实施方式,提供一种具有校正功能的连续近似缓存器模拟至数字转换器,包括:至少一Nd位电容式数字至模拟转换器,具有Nd位的电容,其中Nd为正整数;控制器,耦接所述至少一个电容式数字至模拟转换器。所述控制器用以执行以下电容校正程序:将第i位至第(Nd-1)位的所述电容耦接第一参考电压,根据第(i-1)位至第0位的所述电容的运作产生第一数字码,其中i为小于Nd的整数;将第(i+1)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第i位的所述电容耦接第二参考电压,根据所述第(i-1)位至所述第0位的所述电容的运作产生第二数字码;根据所述第一数字码与所述第二数字码产生所述第i位的所述电容的电容权重;以及根据所述第i位的所述电容的所述电容权重校正所述连续近似缓存器模拟至数字转换器。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,其中所述控制器更多次执行所述校正程序,以获得所述第i位所述电容权重的平均值。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,所述控制器在执行将所述第i位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,根据所述第(i-1)位至所述第0位的所述电容的运作产生所述第一数字码包括:将所述第(Nd-1)位至所述第0位的所述电容的第一端耦接输入电压,所述第(Nd-1)位至所述第0位的所述电容的第二端耦接所述第一参考电压;将所述第(Nd-1)位至所述第0位的所述电容的所述第一端断开所述输入电压;以及利用所述第(i-1)位至所述第0位的电容所对应的所述连续近似缓存器模拟至数字转换器产生所述第一数字码。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,其中所述控制器在执行将所述第(i+1)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第i位的所述电容耦接所述第二参考电压,根据所述第(i-1)位至所述第0位的所述电容的运作产生所述第二数字码包括:将所述第(i+1)位至所述第(Nd-1)位的所述电容的第二端耦接所述第一参考电压,将所述第i位的电容的第二端耦接至所述第二参考电压;以及利用所述第(i-1)位至所述第0位的所述电容所对应的所述连续近似缓存器模拟至数字转换器产生所述第二数字码。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,其中所述至少一电容式数字至模拟转换器包括第一电容式数字至模拟转换器与第二电容式数字至模拟转换器,其中所述控制器在执行将所述第i位的电容的所述第二端耦接所述第二参考电压包括:所述第一电容式数字至模拟转换器的所述第i位的所述电容的第二端耦接所述第二参考电压;以及所述第二电容式数字至模拟转换器的所述第i位的所述电容的第二端耦接第三参考电压。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,其中所述连续近似缓存器模拟至数字转换器还包括比较器,所述输入电压由所述比较器的输入共模电压决定。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,所述控制器更用以执行:产生所述第二数字码后,将第(i+2)位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第(i+1)位的所述电容耦接所述第二参考电压,根据所述第i位至所述第0位的所述电容的运作产生第三数字码;以及根据所述第一数字码与所述第三数字码产生所述第i+1位的所述电容的电容权重。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,所述控制器还执行:产生所述第二数字码后,将所述第i位至所述第(Nd-1)位的所述电容耦接所述第一参考电压,将所述第(i-1)位的所述电容耦接所述第二参考电压,根据第(i-2)位至所述第0位的所述电容的运作产生第三数字码;以及根据所述第一数字码与所述第三数字码产生所述第i-1位的所述电容的电容权重。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,所述控制器还用以执行:根据第(j-1)位至第i位的所述电容的电容权重获得第j位的所述电容的电容权重,其中Nd>j>i。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,其中所述控制器的所述电容校正程序的校正时序与所述连续近似缓存器模拟至数字转换器的操作模式时序相同。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,还包括:时钟缩减电路,耦接在所述控制器与所述比较器之间,用以在校正第i位的电容时,将所述电容校正程序的校正时序省略操作模式时序中第(Nd-1)位电容至第(i+1)位的等待周期。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,所述连续近似缓存器模拟至数字转换器还包括比较器,所述第一数字码包括闪烁噪声以及所述比较器的偏移的信息。

在上述具有校正功能的连续近似缓存器模拟至数字转换器,其中所述控制器将所述第一数字码与所述第二数字码相减以产生所述第i位的所述电容的电容权重。

虽然本公开已以实施例公开如上,然其并非用以限定本公开,任何所属技术领域中具有通常知识者,在不脱离本公开的精神和范围内,当可作些许的更动与润饰,故本公开的保护范围当视后附的权利要求书所界定者为准。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 具校正功能连续近似缓存器模拟至数字转换器及校正方法

- 连续逼近式模拟数字转换器的校正电路与校正方法