存储器装置的制造方法

文献发布时间:2023-06-19 11:54:11

技术领域

本申请有关于一种半导体装置的制造方法,且特别是有关于一种存储器装置的制造方法。

背景技术

随着市场的快速成长,提高存储器装置的积集度以及缩小关键尺寸已成为一种趋势。在此趋势下,存储器装置常遭遇字元线漏电(word line leakage)、位元线短路(bitline short)以及高温数据保持(high-temperature data retention,HTDR)不佳等问题。此外,位元线之间的介电层上的金属或金属氧化物颗粒残留也容易导致位元线短路的问题。因此,能够进一步提升存储器装置的效能的工艺,仍为目前业界致力研究的课题之一。

发明内容

根据本申请一些实施例,提供一种存储器装置的制造方法,包含以下步骤:提供衬底(substrate),衬底包括存储单元区(memory cell region)与周边区;于存储单元区上形成多个第一栅极结构;于周边区上形成至少一第二栅极结构;于衬底上形成衬层,衬层覆盖多个第一栅极结构以及至少一第二栅极结构,且衬层形成于多个第一栅极结构之间的多个沟槽的底部;于衬层上形成间隔层(spacer layer);于间隔层上形成停止层(stoppinglayer);于停止层上形成第一牺牲层(sacrificial layer),第一牺牲层覆盖多个第一栅极结构以及至少一第二栅极结构,且形成于多个沟槽的底部;移除第一牺牲层的一部分,以暴露出位于多个第一栅极结构以及至少一第二栅极结构上的停止层,以及位于多个沟槽的底部的停止层;移除位于多个沟槽的底部的停止层,以暴露出间隔层;移除剩余的第一牺牲层;于衬底上形成第二牺牲层,第二牺牲层覆盖多个第一栅极结构、衬层、间隔层以及停止层,且填入多个沟槽;以及移除第二牺牲层,且移除位于多个沟槽的底部的间隔层以及衬层,以暴露出衬底。

附图说明

为让本申请的特征、或优点能更明显易懂,下文特举出较佳实施例,并配合所附图式,作详细说明如下。

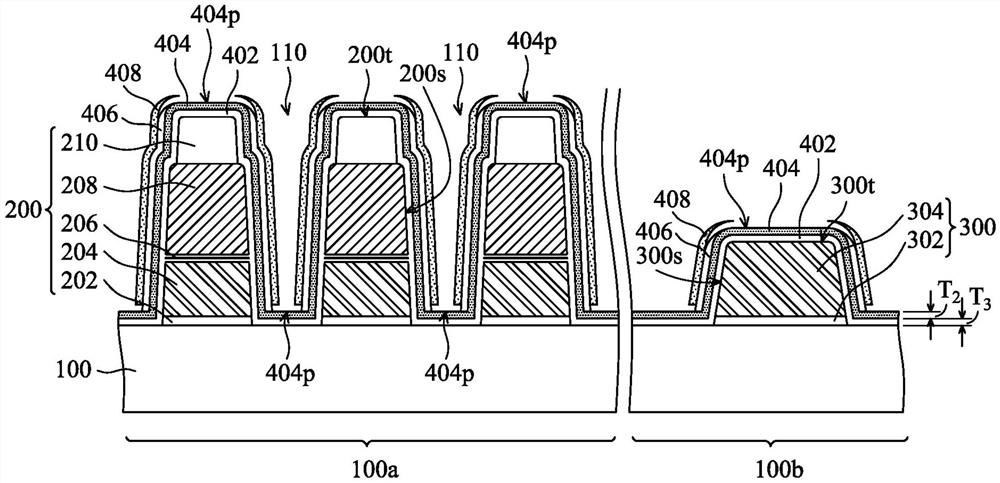

图1A至图1L显示根据本申请一些实施例中,存储器装置在其制造方法中各阶段的结构示意图。

[符号说明]

10 存储器装置;

100 衬底;

100a 存储单元区;

100b 周边区;

100p 部分顶表面;

110 沟槽;

130 接触件;

200 第一栅极结构;

200s 侧壁;

200t 顶表面;

202 穿隧介电层;

204 导体层;

206 闸间介电层;

208 导体层;

210 栅极掩膜层;

300 第二栅极结构;

300s 侧壁;

300t 顶表面;

302 栅极介电层;

304 导体层;

402 衬层;

404 间隔层;

404p 部分顶表面;

406 停止层;

406p 部分顶表面;

408 第一牺牲层;

410 第二牺牲层;

412 第一介电层;

414 掩膜层;

416 第二介电层;

418 导电材料;

KN 肩部;

T

T

T

具体实施方式

请参照图1A,首先,提供衬底100,衬底100可包含存储单元区100a与周边区100b。

接着,于衬底100的存储单元区100a上形成多个第一栅极结构200,以及于周边区100b上形成至少一第二栅极结构300。在一些实施例中,第一栅极结构200之间定义出多个沟槽110。

如图1A所示,在一些实施例中,第一栅极结构200及第二栅极结构300可为具有多个层别的堆叠结构。具体而言,根据一些实施例,第一栅极结构200可包含依序堆叠于衬底100上的穿隧介电层202、导体层204、闸间介电层206以及导体层208。

在一些实施例中,导体层204可作为浮置栅极(floating gate)。在一些实施例中,导体层208可作为控制栅极(control gate)。

在一些实施例中,穿隧介电层202的材料可包含氧化硅。在一些实施例中,导体层204的材料可包含掺杂的多晶硅、非掺杂的多晶硅、或前述的组合。在一些实施例中,闸间介电层206的材料可包含氧化层/氮化层/氧化层(oxide/nitride/oxide,ONO)所构成的复合层,例如由氧化硅/氮化硅/氧化硅所构成的复合层。导体层208的材料可包含掺杂的多晶硅、非掺杂的多晶硅、或前述的组合。

此外,在一些实施例中,第一栅极结构200可进一步包含栅极掩膜层210,栅极掩膜层210可设置于导体层208上。在一些实施例中,栅极掩膜层210的材料可包含氧化硅、氮化硅、氮氧化硅、或前述的组合。

另一方面,根据一些实施例,第二栅极结构300可包含依序堆叠于衬底100上的栅极介电层302以及导体层304。在一些实施例中,导体层304可作为逻辑元件的栅极。在一些实施例中,导体层304的材料可包含掺杂的多晶硅。

接着,如图1A所示,于衬底100上形成衬层402,衬层402可覆盖第一栅极结构200以及第二栅极结构300,且衬层402可形成于第一栅极结构200之间的沟槽110的底部。详细而言,在一些实施例中,衬层402可顺应性地(conformally)形成于衬底100、第一栅极结构200以及第二栅极结构300上。再者,衬层402可覆盖第一栅极结构200的侧壁200s及顶表面200t,并与侧壁200s及顶表面200t接触。衬层402可覆盖第二栅极结构300的侧壁300s及顶表面300t,并与侧壁300s及顶表面300t接触。

在一实施例中,可于形成第一栅极结构200及第二栅极结构300的步骤之后以及于形成衬层402的步骤之前,实行至少一离子植入工艺,以于存储单元区100a的衬底100中形成多个浅掺杂区(未绘示),并于周边区100b的衬底100中形成多个浅掺杂区(未绘示)。

在一些实施例中,衬层402的材料可包含氧化硅。此外,在一些实施例中,衬层402的材料例如可为高温氧化物(high-temperature oxide,HTO)。

接着,于衬层402上形成间隔层404,间隔层404可覆盖衬层402、第一栅极结构200以及第二栅极结构300,且间隔层404亦可形成于第一栅极结构200之间的沟槽110的底部。详细而言,在一些实施例中,间隔层404可顺应性地(conformally)形成于衬层402上,并与衬层402接触。再者,间隔层404可覆盖第一栅极结构200的侧壁200s及顶表面200t以及第二栅极结构300的侧壁300s及顶表面300t。

在一些实施例中,间隔层404的材料可包含氮化硅、氮氧化硅、或前述的组合。

接着,于间隔层404上形成停止层406,停止层406可覆盖间隔层404、衬层402、第一栅极结构200以及第二栅极结构300,且停止层406亦可形成于第一栅极结构200之间的沟槽110的底部。详细而言,在一些实施例中,停止层406可顺应性地(conformally)形成于间隔层404上,并与间隔层404接触。再者,停止层406可覆盖第一栅极结构200的侧壁200s及顶表面200t以及第二栅极结构300的侧壁300s及顶表面300t。

在一些实施例中,停止层406的材料可包含氧化硅。

此外,停止层406可具有厚度T

接着,请参照图1B,于停止层406上形成第一牺牲层408,第一牺牲层408可覆盖第一栅极结构200以及第二栅极结构300,且第一牺牲层408可形成于沟槽110的底部。再者,第一牺牲层408可覆盖前述停止层406、间隔层404以及衬层402。详细而言,在一些实施例中,第一牺牲层408可顺应性地形成于停止层406上。再者,第一牺牲层408可覆盖第一栅极结构200的侧壁200s及顶表面200t以及第二栅极结构300的侧壁300s及顶表面300t。

在一些实施例中,第一牺牲层408的材料可包含多晶硅。

接着,请参照图1C,移除第一牺牲层408的一部分,以暴露出位于第一栅极结构200以及第二栅极结构300上的停止层406,以及位于沟槽110的底部的停止层406。如图1C所示,在一些实施例中,在移除一部分的第一牺牲层408之后,暴露出位于第一栅极结构200以及第二栅极结构300上方的停止层406的部分顶表面406p,并且,暴露出位于沟槽110的底部的停止层406的部分顶表面406p。

换言之,于此步骤中,覆盖第一栅极结构200的顶表面200t以及第二栅极结构300的顶表面300t的第一牺牲层408大致上被移除。另一方面,覆盖第一栅极结构200的侧壁200s以及第二栅极结构300的侧壁300s的第一牺牲层408大致上并未被移除,第一栅极结构200及第二栅极结构300的两侧仍具有第一牺牲层408。

接着,请参照图1D,移除位于沟槽110的底部的停止层406,以暴露出位于停止层406下方的间隔层404。详细而言,在一些实施例中,在移除图1C中经暴露的一部份的停止层406之后,暴露出位于第一栅极结构200以及第二栅极结构300上方的间隔层404的部分顶表面404p,并且,暴露出位于沟槽110的底部的间隔层404的部分顶表面404p。

应注意的是,前述移除位于沟槽110的底部的停止层406的步骤选择性地移除停止层406而未移除间隔层404。在一些实施例中,移除第一牺牲层408的一部分的步骤通过湿蚀刻法工艺实行。

此外,请参照图1E,移除剩余的第一牺牲层408,详细而言,可移除覆盖第一栅极结构200的侧壁200s以及第二栅极结构300的侧壁300s的第一牺牲层408。如图1E所示,于此步骤之后,沟槽110的底部大致上剩下间隔层404以及位于间隔层404下方的衬层402。

根据一些实施例,移除位于沟槽110的底部的停止层406的步骤(如图1D所示)与移除剩余的第一牺牲层408的步骤(如图1E所示)可同时进行。详细而言,在一些实施例中,移除位于沟槽110的底部的停止层406的步骤与移除剩余的第一牺牲层408的步骤通过同一湿蚀刻法工艺实行。

接着,请参照图1F,于衬底100上形成第二牺牲层410,第二牺牲层410覆盖第一栅极结构200、衬层402、间隔层404以及停止层406,且填入沟槽110。如图1F所示,在一些实施例中,第二牺牲层410亦可覆盖位于周边区100b的第二栅极结构300。

在一些实施例中,第二牺牲层410的材料可包含多晶硅。

接着,请参照图1G,在一些实施例中,于衬底100上形成第二牺牲层410的步骤之后,可进一步对第二牺牲层410进行回刻蚀工艺,将位于周边区100b的第二牺牲层410移除。

此外,根据一些实施例,于衬底100的周边区100b上形成第一介电层412,且第一介电层412覆盖第二栅极结构300。在一些实施例中,可进一步对第一介电层412进行平坦化工艺,使第一介电层412具有平坦的表面,接着,对第二牺牲层410进行平坦化工艺,使第二牺牲层410具有平坦的表面。

在一些实施例中,第一介电层412的材料可包含阶梯覆盖能力较好的旋涂玻璃(SOG)、硼磷硅玻璃(BPSG)、磷硅玻璃(PSG)、氧化硅、其它合适的介电材料、或前述的组合。

接着,可于经平坦化的第二牺牲层410以及第一介电层412上形成掩膜层414。在一些实施例中,掩膜层414可包含氮化硅、氧化硅、非晶碳材、其它合适的掩膜材料、或前述的组合。

接着,请参照图1H,在一些实施例中,可通过图案化工艺将掩膜层414图案化。图案化的掩膜层414可定义出后续形成的多个开口120的位置。具体而言,可通过图案化的掩膜层414作为掩膜移除部分的第二牺牲层410,以于第一栅极结构200上形成贯穿第二牺牲层410的开口120,且开口120可暴露出间隔层404的部分顶表面404p。

再者,在一些实施例中,可通过干法刻蚀工艺移除部分的第二牺牲层410,以形成开口120。

接着,请参照图1I,在一些实施例中,于开口120中形成第二介电层416。第二介电层416可用于定义存储单元区100a中后续将形成的接触件的位置。如图1I所示,第二介电层416大致上可设置于第一栅极结构200的正上方。在一些实施例中,第二介电层416与间隔层404接触。

在一些实施例中,第二介电层416的材料可包含氧化硅、氮化硅、氮氧化硅、其它合适的介电材料、或前述的组合。

此外,在一些实施例中,于开口120中形成第二介电层416之后,可通过湿式剥除工艺、干法刻蚀工艺、或前述的组合移除图案化的掩膜层414。

接着,请参照图1J及图1K,移除第二牺牲层410,且移除位于沟槽110的底部的间隔层404以及衬层402,以暴露出衬底100的部分顶表面100p。

根据一些实施例,移除剩余的第二牺牲层410的步骤(如图1J所示)与移除位于沟槽110的底部的间隔层404以及衬层402的步骤(如图1K所示)可同时进行。然而,根据另一些实施例,移除剩余的第二牺牲层410的步骤与移除位于沟槽110的底部的间隔层404以及衬层402的步骤亦可分开进行。

在一些实施例中,可通过干法刻蚀工艺、湿式剥除工艺移除剩余的第二牺牲层410以及位于沟槽110的底部的间隔层404以及衬层402。

值得注意的是,由于沟槽110的底部仅剩下间隔层404与衬层402,因此,于此步骤中,用于移除间隔层404以及衬层402的刻蚀工艺所需实行的刻蚀量减少,藉此可避免一次性的大量刻蚀,降低刻蚀工艺损害第一栅极结构200的风险。

具体而言,根据一些实施例,由于厚度相对较厚的停止层406已于先前的步骤中移除(如图1D所示),于此步骤中,仅需对厚度较薄的间隔层404与衬层402进行刻蚀工艺,如此一来,可减少刻蚀工艺对第一栅极结构200的侧壁200s上的衬层402、间隔层404及停止层406的消耗及薄化,维持第一栅极结构200的肩部KN上的衬层402、间隔层404及停止层406的厚度,避免第一栅极结构200的导体层208(或肩部KN)外露而造成短路或漏电流。

在一些实施例中,前述第一栅极结构200的肩部KN大致上可对应于导体层208的顶角部。

接着,请参照图1L,于第一栅极结构200之间的沟槽110中填充导电材料418,以形成多个接触件130,于此,大致完成存储器装置10的阶段制作。在一些实施例中,所述接触件130可为自对准接触件(self-align contact)。在一些实施例中,导电材料418可完全地填充于沟槽110中,并且形成于第二介电层416之间。

在一些实施例中,导电材料418可包含钨(W)、铜(Cu)、铝(Al)、金(Au)、银(Ag)、钛(Ti)、钼(Mo)、镍(Ni)、钨合金、铜合金、铝合金、金合金、银合金、钛合金、钼合金、镍合金、其它合适的导电材料、或前述的组合。

综上所述,所述存储器装置的制造方法可保护栅极结构的侧壁结构,减少沟槽底部的刻蚀工艺对栅极结构的侧壁结构造成损耗,避免栅极结构的肩部外露,进而可改善字元线漏电、位元线漏电或短路等问题。

- 存储器阵列、存储器阵列的制造方法、存储器阵列片材、存储器阵列片材的制造方法及无线通信装置

- 强电介质膜的形成方法、强电介质存储器、强电介质存储器的制造方法、半导体装置及半导体装置制造方法