集成电路结构

文献发布时间:2023-06-19 12:19:35

技术领域

本发明的实施例是有关于集成电路结构和集成电路设计系统。

背景技术

一般来说,电子设计自动化(electronic design automation,EDA)工具帮助半导体设计者取用所期望电路的纯粹的行为描述(behavioral description),并运作以形成准备制造的电路的最终布局。此过程经常取用电路的行为描述,并将其转化为功能性描述(functional description),然后将其分解成数千个布尔函数,并使用标准胞元库映射到相应的胞元行中。一旦被映射,便实行综合(synthesis)以将结构设计转化为物理布局,构建时钟树以将结构性元素同步化,且设计在布局之后被优化。

为避免来自各自不同的胞元库的胞元之间的未对准(misalignment),通常使用来自标准胞元库的胞元,所述胞元所具有的胞元高度等于胞元行的高度(下文中称为“行高度”)。因此,通常在相对早期的设计阶段处针对将哪一“单个(single)”胞元高度用于设计从而也固定对应的行高度作出决定。然而,通过仅使用单个胞元高度,必须在电路性能、电路功率及制造工艺之间进行一些折衷。例如,可通过沿着胞元行并排设置多个胞元来形成以性能为取向的电路(performance-orientated circuit),所述多个胞元中的每一者具有较高数目的有源区(例如,鳍);并且可通过沿着胞元行并排设置多个胞元来形成以功率/面积为取向的电路(power/area-orientated circuit),所述多个胞元中的每一者具有较低数目的有源区。

因此,为设计需要消耗低功率及占用小面积而不牺牲其性能的电路(例如,以平衡为取向的电路(balance-orientated circuit)),通常进行各种设计折衷。例如,具有较低数目的鳍的第一多个胞元交替地设置在具有较高数目的有源区的第二多个胞元之间。此种布局在所述第二多个胞元中的有源区(通常被称为“断裂鳍(broken fin)”,或者更一般地称为“断裂有源区(broken active region)”)中的一者或多者的延伸部上造成不连续性,此可能不利地降低电路的性能(由于由断裂鳍造成的松弛应变/应力)。因此,使用胞元设计电路的常规技术并不完全令人满意。

发明内容

本发明的实施例的一种集成电路结构包括:第一多个胞元行,在第一方向上延伸;以及第二多个胞元行,在第一方向上延伸。第一多个胞元行中的每一者具有第一行高度且包括设置在其中的多个第一胞元。第二多个胞元行中的每一者具有与第一行高度不同的第二行高度且包括设置在其中的多个第二胞元。所述多个第一胞元包括第一多个有源区,第一多个有源区中的每一者在第一方向上连续地延伸跨越所述多个第一胞元。所述多个第二胞元包括第二多个有源区,第二多个有源区中的每一者在第一方向上连续地延伸跨越所述多个第二胞元。第一多个有源区及第二多个有源区中的至少一个有源区具有沿着第一方向变化的宽度。

本发明的实施例的一种集成电路结构包括:第一多个胞元行,在第一方向上延伸;以及第二多个胞元行,在第一方向上延伸。第一多个胞元行中的每一者具有第一行高度且包括设置在其中的多个第一胞元。第二多个胞元行中的每一者具有与第一行高度不同的第二行高度且包括设置在其中的多个第二胞元。所述多个第一胞元中的每一者包括多个有源区,所述多个有源区中的每一者沿着第一方向以固定宽度延伸。所述多个第二胞元中的每一者包括多个有源区,所述多个有源区中的每一者沿着第一方向以固定宽度延伸。在第一多个胞元行及第二多个胞元行中的至少一个胞元行中,有源区数量沿着第一方向变化。

本发明的实施例的一种集成电路设计系统包括:非暂时性存储介质,被用指令集进行编码;以及硬件处理器,与非暂时性存储介质通信耦合,且被配置成执行所述指令集,所述指令集被配置成使硬件处理器:提供包括多个第一胞元的第一库,所述多个第一胞元各自具有第一胞元高度且包括沿着第一方向连续地延伸的多个有源区;提供包括多个第二胞元的第二库,所述多个第二胞元各自具有第二胞元高度且包括沿着第一方向连续地延伸的多个有源区,其中第二胞元高度与第一胞元高度不同;从第一库检索所述多个第一胞元的第一子集及从第二库检索所述多个第二胞元的第二子集;以及将沿着第一方向延伸的所述多个第一胞元的第一子集放置在第一多个胞元行中,且将沿着第一方向延伸的所述多个第二胞元的第二子集放置在第二多个胞元行中。在第一多个胞元行及第二多个胞元行中的至少一个胞元行中,有源区数量沿着第一方向变化。

附图说明

结合附图阅读以下详细说明,会最好地理解本发明的各个方面。应注意,各种特征未必按比例绘制。事实上,为论述清晰起见,可任意增大或减小各种特征的尺寸。

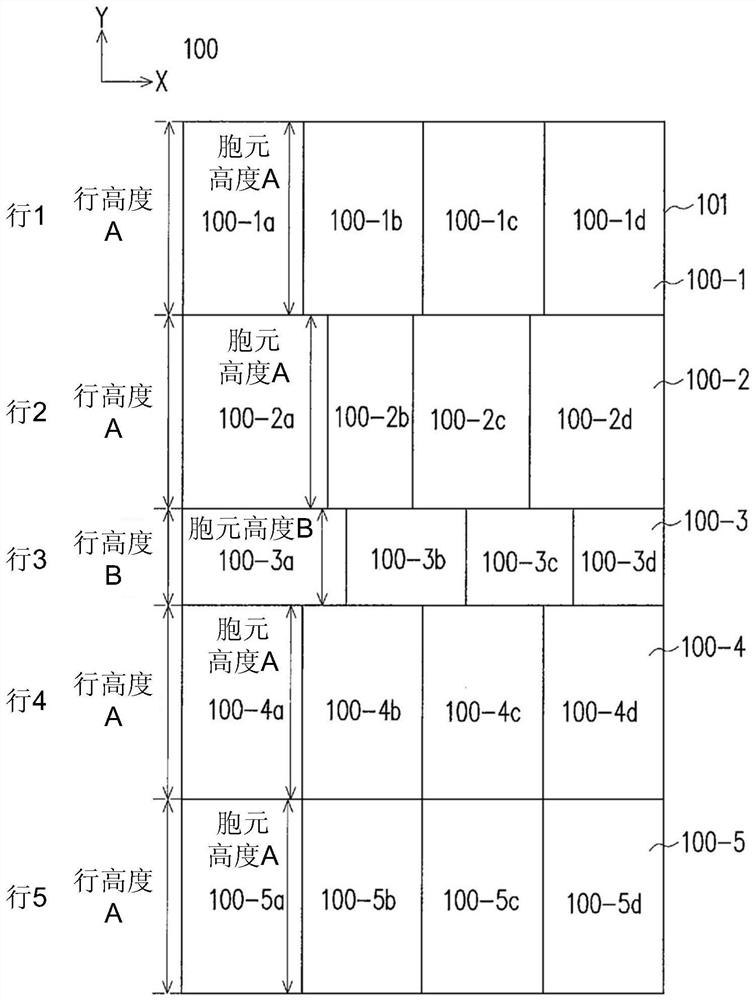

图1A、图1B及图1C分别示出根据本发明一些实施例的由本发明的系统及方法设计的示例性集成电路的示意图。

图2A示出根据本发明一些实施例的示例性集成电路在一个或多个第一布局层级处的对应布局设计的俯视图。

图2B示出根据本发明一些实施例的集成电路在所述一个或多个第一布局层级上方的第二布局层级处的对应布局设计的俯视图。

图2C、图2D、图2E及图2F各自示出根据本发明一些实施例的集成电路的一些胞元的对应剖视图的部分。

图2G示出根据本发明一些实施例的示例性集成电路在一个或多个第一布局层级处的另一对应布局设计的俯视图。

图3示出根据本发明一些实施例的示例性信息处置系统(information handlingsystem,IHS)的方块图。

图4示出根据本发明一些实施例的由IHS实行以产生包括混合行高度的集成电路的物理布局的示例性方法的流程图。

图5示出根据本发明一些实施例的各种混合行设计情景的不同应用。

图6示出根据本发明一些实施例的用于设计包括混合行高度的集成电路的示例性过程。

图7示出根据本发明一些实施例的平面板(planar)或纳米片材(nano-sheet)中的胞元在一个或多个布局层级处的对应布局设计的俯视图。

图8示出根据本发明一些实施例的鳍型场效晶体管(fin field-effecttransistor,FinFET)或纳米走线(nano-wire)中的胞元在一个或多个布局层级处的对应布局设计的俯视图。

图9示出根据本发明一些实施例的平面板或纳米片材中的胞元结构的俯视图。

图10示出根据本发明一些实施例的FinFET或纳米走线中的胞元结构的俯视图。

图11示出根据本发明一些实施例的由高性能(high performance,HP)胞元及低功率(lower power,LP)胞元构成的胞元系列(cell family)。

图12示出根据本发明一些实施例的具有各种HP对LP行比率(row ratio)的布局设计。

图13示出根据本发明一些实施例的由合并式HP-LP胞元构成的胞元系列。

图14示出根据本发明一些实施例的具有1/1的HP/LP行比率的示例性集成电路的对应布局设计的俯视图。

图15示出根据本发明一些实施例的具有2/1的HP/LP行比率的示例性集成电路的对应布局设计的俯视图。

图16示出根据本发明一些实施例的具有1/2的HP/LP行比率的示例性集成电路的对应布局设计的俯视图。

图17示出根据本发明一些实施例的平面板或纳米片材中的胞元的对应布局设计的俯视图,所述对应布局设计具有灵活有源区宽度及灵活有源区转变。

图18示出根据本发明一些实施例的FinFET或纳米走线中的胞元的对应布局设计的俯视图,所述对应布局设计具有灵活鳍数目及灵活有源区转变。

图19示出根据本发明一些实施例的用于产生用于制作的集成电路的物理布局的示例性方法的流程图。

具体实施方式

本公开阐述用于实施主题的不同特征的各种示例性实施例。下面阐述组件及布置的具体实例以简化本公开。当然,这些仅为实例而非旨在进行限制。例如,在以下说明中,在第二特征之上或第二特征上形成第一特征可包括其中第一特征与第二特征被形成为直接接触的实施例,且也可包括其中第一特征与第二特征之间可形成附加特征从而使得第一特征与第二特征可不直接接触的实施例。另外,本公开在各种实例中可重复使用参考编号和/或字母。此种重复使用是出于简单及清晰的目的,且自身并不表示所论述的各种实施例和/或配置之间的关系。

此外,为易于说明,本文中可能使用例如“在……下方(beneath)”、“在……下面(below)”、“下部的(lower)”、“在……上方(above)”、“上部的(upper)”等空间相对性用语来阐述图中所示一个元件或特征与另一(其他)元件或特征的关系。所述空间相对性用语旨在除图中所绘示的取向外还囊括器件在使用或操作中的不同取向。装置可具有其他取向(旋转90度或其他取向),且本文中所使用的空间相对性描述语可同样相应地进行解释。

本公开提供使用多个胞元行或行来设计电路的系统及方法的各种实施例,所述多个胞元行或行中的每一者包括沿着第一方向并排设置的一个或多个胞元,且各自具有沿着第一方向延伸的相同数目的有源区(例如,鳍)。更具体来说,设置在每一行内的相应有源区各自连续地延伸跨越所述一个或多个胞元。此外,根据一些实施例,此种多个行可沿着与第一方向实质上正交的第二方向设置,且可具有至少两个各自不同的行高度。换句话说,设置在具有不同行高度的相应行内的胞元具有不同数目的有源区。因此,其中的每一者可用于各自不同的应用(例如,以性能为取向的应用、以功率/面积为取向的应用、以平衡为取向的应用等)的各种电路可使用所公开的系统及方法来设计,而不具有现有技术通常遇到的断裂鳍问题,如上所述。

常规的单个数字设计区块(single digital design block)可具有三种情景:(1)高性能(HP)应用,具有高胞元、高速、高功率及大面积;(2)低功率(LP)应用,具有短胞元、低功率、小面积及低速度;以及(3)平衡应用,具有高胞元、中等速度、低功率及大面积。本公开提供系统及方法的各种实施例,以示出通过混合HP胞元与LP胞元以获得较小的面积来优化平衡应用的高效方式。这些实施例可应用于平面板、鳍型场效晶体管(FinFET)、或者例如栅极全包围式(gate-all-around,GAA)纳米片材或纳米走线等下一代器件。在所公开的混合行结构中,HP对LP行比率对于不同的应用而言可为灵活的。根据行比率,对于平面板或纳米片材中的HP胞元及LP胞元二者,可在放置功能性胞元之后以灵活有源区宽度和/或灵活片材宽度放置一些填充胞元。对于FinFET或纳米走线,HP胞元及LP胞元可根据行比率以灵活鳍数目和/或灵活走线数目放置。在一些实施例中,不同行上的有源区可利用从一个胞元到另一个胞元的灵活有源区转变进行合并。

图1A、图1B、图1C分别示出根据一些实施例的由本发明的系统及方法设计的示例性集成电路100、140及180的示意图。然而,并非需要所有所示出的组件,且本发明的一些实施例可包括未在图1A到图1C中示出的附加组件。在不背离本文中所述本发明的范围的情况下,可对组件的布置及类型进行变化。可包括附加的、不同的或更少的组件。

首先参照图1A,集成电路100包括相对于网格101布置(例如,布局)在相应的“胞元行”或“行”中的胞元组100-1、100-2、100-3、100-4及100-5。此外,在一些实施例中,每一胞元组包括沿着相应的行并排设置的一个或多个(标准)胞元。例如,胞元组100-1包括布置在网格101的行1中的胞元100-1a、100-1b、100-1c及100-1d;胞元组100-2包括布置在网格101的行2中的胞元100-2a、100-2b、100-2c及100-2d;胞元组100-3包括布置在网格101的行3中的胞元100-3a、100-3b、100-3c及100-3d;胞元组100-4包括布置在网格101的行4中的胞元100-4a、100-4b、100-4c及100-4d;并且胞元组100-5包括布置在网格101的行5中的胞元100-5a、100-5b、100-5c及100-5d。

在一些实施例中,集成电路100的行可呈现至少两个各自不同的“行高度”。如所示,行1、2、4及5可共享实质上相似的行高度,下文中称为“行高度A”;且行3可具有行高度,下文中称为“行高度B”,其中行高度A大于行高度B。在一些实施例中,此种行高度对应于放置在其中的胞元的胞元高度,此将被论述如下。

在一些实施例中,胞元组100-1、100-2、100-3、100-4及100-5的胞元是从具有不同胞元高度的相应标准胞元库检索。更具体来说,胞元组100-1、100-2、100-4及100-5的胞元可从包括多个胞元的第一标准胞元库(下文中称为“胞元库A”)检索,所述多个胞元中的每一者共享第一胞元高度(下文中称为“胞元高度A”);并且胞元组100-3的胞元可从包括多个胞元的第二标准胞元库(下文中称为“胞元库B”)检索,所述多个胞元中的每一者共享第二胞元高度(下文中称为“胞元高度B”)。换句话说,胞元100-1a到100-1d、100-2a到100-2d、100-4a到100-4d及100-5a到100-5d是胞元库A的子集,且胞元100-3a到100-3d是胞元库B的子集。胞元库A中的胞元100-1a到100-1d、100-2a到100-2d、100-4a到100-4d及100-5a到100-5d中的每一者及胞元库B中的胞元100-3a到100-3d与特定逻辑功能和/或特性(例如,定时特性)相关联。因此,应注意,尽管胞元100-1a到100-1d、100-2a到100-2d、100-4a到100-4d及100-5a到100-5d是从胞元库A检索,然而所述胞元并非全部共享相同的胞元宽度,对于此情形,胞元库B的胞元100-3a到100-3d是相似的。在一些实施例中,通过如所示般布置胞元组100-1到100-5,集成电路100可呈现例如以速度为取向的电路、以平衡为取向的电路或以功率/面积为取向的电路等特定特性,此将在下文进一步详细论述。

如上所述,每一行的行高度对应于放置在其中的胞元的胞元高度。在一些实施例中,每一行的行高度实质上接近放置在其中的胞元的胞元高度。此外,胞元组100-1到100-5的胞元中的每一者的胞元高度可对应于在第一方向(例如,X方向)上连续地延布且沿着第二方向(例如,Y方向)设置的一定数目的有源区。在一些实施例中,此种有源区可为一个或多个三维场效晶体管(例如,FinFET、栅极全包围式(GAA)晶体管)的鳍形区,或者一个或多个平面金属氧化物半导体场效晶体管(metal-oxide-semiconductor field-effect-transistor,MOSFET)的氧化物界定(oxide-definition,OD)区,其中有源区可用作相应晶体管的源极特征或漏极特征。例如,胞元100-1a到100-1d、100-2a到100-2d、100-4a到100-4d及100-5a到100-5d的胞元高度A可对应于沿着Y方向设置的较高数目的有源区;并且胞元100-3a到100-3d的胞元高度B可对应于沿着Y方向的较低数目的有源区,此将在下文参照图2A进一步详细示出及论述。

参照图1B,集成电路140包括相对于网格141布置(例如,布局)在相应的“行”中的胞元组140-1、140-2、140-3、140-4、140-5、140-6、140-7及140-8。例如,胞元组140-1包括布置在网格141的行1中的胞元140-1a、140-1b、140-1c及140-1d;胞元组140-2包括布置在网格141的行2中的胞元140-1a、140-2b、140-2c及140-2d;胞元组140-3包括布置在网格141的行3中的胞元140-3a及140-3b;胞元组140-4包括布置在网格141的行4中的胞元140-4a、140-4b及140-4c;胞元组140-5包括布置在网格141的行5中的胞元140-5a、140-5b、140-5c及140-5d;胞元组140-6包括布置在网格141的行6中的胞元140-6a、140-6b及140-6c;胞元组140-7包括布置在网格141的行7中的胞元140-7a及140-7b;并且胞元140-8包括布置在网格141的行8中的胞元140-8a、140-8b、140-8c、140-8d及140-8e。在一些实施例中,胞元组140-1、140-2、140-4、140-5、140-7及140-8的胞元可从上述标准胞元库B检索(例如,与集成电路100的胞元100-3a到100-3d相同);并且胞元组140-3及140-6的胞元可从上述标准胞元库A检索(例如,与集成电路100的胞元100-1a到100-1d相同)。在一些实施例中,集成电路140的行1、2、4、5、7及8可各自具有与行高度B实质上相似的行高度;并且集成电路140的行3及6可各自具有与行高度A实质上相似的行高度。因此,胞元140-1a到140-1d、140-2a到140-2d、140-4a到140-4c、140-5a到140-5d、140-7a到140-7b及140-8a到140-8e可各自具有与胞元高度B实质上相同的胞元高度;并且胞元140-3a到140-3b及140-6a到140-6c可各自具有与胞元高度A实质上相同的胞元高度。

然后参照图1C,集成电路180包括相对于网格181布置(例如,布局)在相应的“行”中的胞元组180-1、180-2、180-3、180-4、180-5及180-6。例如,胞元组180-1包括布置在网格181的行1中的胞元180-1a及180-1b;胞元组180-2包括布置在网格181的行2中的胞元180-2a、180-2b、180-2c及180-2d;胞元组180-3包括布置在网格181的行3中的胞元180-3a、180-3b及180-3c;胞元组180-4包括布置在网格181的行4中的胞元180-4a、180-4b及180-4c;胞元组180-5包括布置在网格181的行5中的胞元180-5a、180-5b、180-5c及180-5d;并且胞元组180-6包括布置在网格181的行6中的胞元180-6a、180-6b、180-6c、180-6d及180-6e。在一些实施例中,胞元组180-1、180-3及180-5的胞元可从上述标准胞元库A检索;并且胞元组180-2、180-4及180-6的胞元可从上述标准胞元库B检索。在一些实施例中,集成电路180的行1、3及5可各自具有与行高度A实质上相似的行高度;并且集成电路180的行2、4及6可各自具有与行高度B实质上相似的行高度。因此,胞元180-1a到180-1b、180-3a到180-3c及180-5a到180-5d可各自具有与胞元高度A实质上相同的胞元高度;并且胞元180-2a到180-2d、180-4a到180-4c及180-6a到180-6e可各自具有与胞元高度B实质上相同的胞元高度。

如以上所论述,胞元高度A对应于沿着Y方向设置的较高数目的有源区,且胞元高度B对应于沿着Y方向设置的较低数目的有源区。此外,在一些实施例中,与具有较低数目的有源区的胞元相比,具有较高数目的有源区的胞元可呈现较高的性能(例如,较快的速度),而具有较低数目的有源区的胞元可占用较小的面积,与具有较高数目的有源区的胞元相比,其通常也呈现较低的功耗。

因此,集成电路100(其所包括的具有胞元高度A的胞元多于具有胞元高度B的胞元)可在集成电路100到180(即,以速度为取向的电路)中呈现相对较高的性能;集成电路140(其所包括的具有胞元高度B的胞元多于具有胞元高度A的胞元)可在集成电路100到180(即,以功率/面积为取向的电路)中呈现相对较低的功耗;并且集成电路180(其包括相等数目的具有胞元高度A及B的胞元)可呈现比集成电路140相对更高的性能及比集成电路100相对更低的功耗(即,以平衡为取向的电路)。与形成以平衡为取向的电路(其通常在一个或多个相应的有源区中具有延伸不连续性)的现有技术相比,例如通过所公开的系统及方法形成的集成电路180可呈现平衡特性,而不会在相应的有源区中形成延伸不连续性。

更具体来说,视所设计的集成电路的特性而定,根据本发明的一些实施例,可相应地确定行比率,行比率定义具有胞元高度A的胞元的数目对具有胞元高度B的胞元的数目的比率。使用以上提供的集成电路来举例说明,当使用所公开的系统及方法设计旨在具有高性能的集成电路100时,可确定为4的较高行比率(因为具有胞元高度A及B的胞元的数目分别为4及1);当使用所公开的系统及方法设计旨在具有较低功耗的集成电路140时,可确定为1/3的较低行比率(因为具有胞元高度A及B的胞元的数目分别为2及6);并且当使用所公开的系统及方法设计旨在具有平衡特性的集成电路180时,可确定为1的中间行比率(因为具有胞元高度A及B的胞元的数目分别为3及3)。集成电路100到180被提供作为例示性实例。因此,应理解,所公开的系统及方法可用于设计具有例如(举例来说)1/2、2/3、3/2、1/4、3、4等任何其他行比率(在将分数约分到相应的最简项之后)的集成电路,同时仍然在本发明的范围内。

根据本发明的一些实施例,通过所公开的系统及方法设计的集成电路包括多个行,且所述多个行中的每一者包括共享相同的胞元高度的一个或多个并排设置的胞元。此外,此种相同的高度对应于跨越这些并排设置的胞元的相同数目的有源区,所述有源区在与所述多个行沿其进行布置的另一方向实质上正交的方向上延布。因此,并排设置的胞元的有源区可沿着所述行连续地延伸跨越相应的胞元。如以上所论述,通过跨越集成电路的多个并排胞元连续地延伸有源区,可增加有源区内的压缩应变,此可有利地改善集成电路的性能(例如,较高的驱动电流),同时使得集成电路能够通过布置具有各自不同的行高度(胞元高度)的两个或更多个行而被设计成具有任何所期望的特性。使用集成电路180作为代表性实例,此种连续地延伸的有源区将在下文进一步详细例示及论述。

另外,遵循所公开的系统及方法的混合行设计的集成电路可在非定时关键路径(non-timing critical path)上实现较小的面积、较低的功耗,同时保持鳍速度。在一个实例中,与传统的高速度设计相比,所公开的集成电路具有相同的最高速度,但将功率降低到70%,将面积降低到87%,且对鳍应力具有强的抵抗力而不造成鳍断裂。在另一个实例中,与传统的低功率设计相比,所公开的集成电路具有相同的功率、相似的面积,但将最高速度从70%增加到100%(增加约43%),且对鳍应力具有强的抵抗力而不造成鳍断裂。在又一个实例中,与传统的高速度及部分低功率设计相比,所公开的集成电路具有相同的功率,但将最高速度从90%增加到100%(增加约11%),将面积减少到87%,且对鳍应力具有相对强的抵抗力而不造成鳍断裂。

图2A示出根据一些实施例的集成电路180在一个或多个第一布局层级处的对应布局设计的俯视图,且图2B示出根据一些实施例的集成电路180在所述一个或多个第一布局层级上方的第二布局层级处的对应布局设计的俯视图。在一些其他实施例中,第二布局层级可低于或相同于所述一个或多个第一布局层级。出于清晰目的,图2C及图2D示出分别沿着线A-A及B-B截取的集成电路180的胞元180-1a及180-1b的对应剖视图的部分。

如图2A中所示,沿着网格181的行1,胞元180-1a及180-1b分别包括沿着X方向连续地延伸跨越胞元180-1a到180-1b的四个有源区212-1、212-2、212-3及212-4;沿着网格181的行2,胞元180-2a、180-2b、180-2c及180-2d分别包括沿着X方向连续地延伸跨越胞元180-2a到180-2d的两个有源区222-1及222-2;沿着网格181的行3,胞元180-3a、180-3b及180-3c分别包括沿着X方向连续地延伸跨越胞元180-3a到180-3c的四个有源区232-1、232-2、232-3及232-4;沿着网格181的行4,胞元180-4a、180-4b及180-4c分别包括沿着X方向连续地延伸跨越胞元180-4a到180-4c的两个有源区242-1及242-2;沿着网格180的行5,胞元180-5a、180-5b、180-5c及180-5d分别包括沿着X方向连续地延伸跨越胞元180-5a到180-5d的四个有源区252-1、252-2、252-3及252-4;并且沿着网格181的行6,胞元180-6a、180-6b、180-6c、180-6d及180-6e分别包括沿着X方向连续地延伸跨越胞元180-6a到180-6e的两个有源区262-1及262-2。

如上所述,集成电路180的胞元的有源区用作相应晶体管的源极特征或漏极特征,且集成电路180的每一胞元被配置成实行特定逻辑功能。因此,应理解,集成电路180的每一胞元可包括植入有n型掺杂剂的第一区、植入有p型掺杂剂的第二区及相应的多个栅极图案。在一些实施例中,相应有源区的一个子集形成在第一区之上以形成p型MOSFET,且相应有源区的另一个子集形成在第二区之上以形成n型MOSFET。此外,根据一些实施例,相应的所述多个栅极图案可在与有源区沿其进行延伸的方向实质上正交的方向上延布,以形成p型MOSFET及n型MOSFET的相应栅极。因此,集成电路180的胞元可呈现不同的栅极图案布局,以实行相应的特定逻辑功能。

例如,仍然参照图2A,胞元180-1a包括植入有n型掺杂剂的第一区214及植入有p型掺杂剂的第二区216以及栅极图案218-1、218-2及218-3,第一区214与第二区216是通过线215来划分,栅极图案218-1、218-2及218-3彼此间隔开相应的距离且各自在Y方向上延布。在一些实施例中,有源区212-1到212-4可各自设置在第一区214或第二区216之上,且栅极图案218-1到218-3可各自设置在相应的有源区212-1到212-4之上,此将参照图2C及图2D示出。相似地,相邻胞元180-1b也包括第一区214及第二区216以及栅极图案218-4、218-5、218-6及218-7,有源区212-1到212-4设置在第一区214及第二区216之上,栅极图案218-4、218-5、218-6及218-7彼此间隔开相应的距离且各自在Y方向上延布。

在一些实施例中,沿着其他行设置的集成电路180的胞元的有源区也设置在相应的第一植入区及第二植入区之上,且一个或多个相应的栅极图案也在Y方向上延布,因此沿着其他行设置的集成电路180的胞元的相应配置简要阐述如下。

沿着行2,胞元180-2a到180-2d包括植入有n型掺杂剂的第一区224及植入有p型掺杂剂的第二区226,第一区224与第二区226通过线225来划分,其中有源区222-1设置在第一区224之上,且有源区222-2设置在第二区226之上。胞元180-2a还包括栅极图案228-1、228-2及228-3,栅极图案228-1、228-2及228-3彼此间隔开相应的距离且各自在Y方向上延布;胞元180-2b还包括栅极图案228-4及228-5,栅极图案228-4与228-5彼此间隔开相应的距离且各自在Y方向上延布;胞元180-2c还包括栅极图案228-6、228-7、228-8及228-9,栅极图案228-6、228-7、228-8及228-9彼此间隔开相应的距离且各自在Y方向上延布;并且胞元180-2d还包括栅极图案228-10、228-11及228-12,栅极图案228-10、228-11及228-12彼此间隔开相应的距离且各自在Y方向上延布。

沿着行3,胞元180-3a到180-3c包括植入有n型掺杂剂的第一区234及植入有p型掺杂剂的第二区236,第一区234与第二区236通过线235来划分,其中有源区232-1及232-2设置在第一区234之上,且有源区232-3及232-4设置在第二区236之上。胞元180-3a还包括栅极图案238-1、238-2及238-3,栅极图案238-1、238-2及238-3彼此间隔开相应的距离且各自在Y方向上延布;胞元180-3b还包括栅极图案238-4、238-5及238-6,栅极图案238-4、238-5及238-6彼此间隔开相应的距离且各自在Y方向上延布;并且胞元180-3c还包括栅极图案238-7、238-8及238-9,栅极图案238-7、238-8及238-9彼此间隔开相应的距离且各自在Y方向上延布。

沿着行4,胞元180-4a到180-4c包括植入有n型掺杂剂的第一区244及植入有p型掺杂剂的第二区246,第一区244与第二区246通过线245来划分,其中有源区242-1设置在第一区244之上,且有源区242-2设置在第二区246之上。胞元180-4a还包括栅极图案248-1、248-2及248-3,栅极图案248-1、248-2及248-3彼此间隔开相应的距离且各自在Y方向上延布;胞元180-4b还包括栅极图案248-4、248-5及248-6,栅极图案248-4、248-5及248-6彼此间隔开相应的距离且各自在Y方向上延布;并且胞元180-4c还包括栅极图案248-7、248-8、248-9及248-10,栅极图案248-7、248-8、248-9及248-10彼此间隔开相应的距离且各自在Y方向上延布。

沿着行5,胞元180-5a到180-5d包括植入有n型掺杂剂的第一区254及植入有p型掺杂剂的第二区256,第一区254与第二区256通过线255来划分,其中有源区252-1及252-2设置在第一区254之上,且有源区252-3及252-4设置在第二区256之上。胞元180-5a还包括栅极图案258-1、258-2及258-3,栅极图案258-1、258-2及258-3彼此间隔开相应的距离且各自在Y方向上延布;胞元180-5b还包括栅极图案258-4及258-5,栅极图案258-4与258-5彼此间隔开相应的距离且各自在Y方向上延布;胞元180-5c还包括栅极图案258-6、258-7及258-8,栅极图案258-6、258-7及258-8彼此间隔开相应的距离且各自在Y方向上延布;并且胞元180-5d还包括栅极图案258-9、258-10及258-11,栅极图案258-9、258-10及258-11彼此间隔开相应的距离且各自在Y方向上延布。

沿着行6,胞元180-6a到180-6e包括植入有n型掺杂剂的第一区264及植入有p型掺杂剂的第二区266,第一区264与第二区266通过线265来划分,其中有源区262-1设置在第一区264之上,且有源区262-2设置在第二区266之上。胞元180-6a还包括栅极图案268-1及268-2,栅极图案268-1与268-2彼此间隔开相应的距离且各自在Y方向上延布;胞元180-6b还包括栅极图案268-3及268-4,栅极图案268-3与268-4彼此间隔开相应的距离且各自在Y方向上延布;胞元180-6c还包括栅极图案268-5及268-6,栅极图案268-5与268-6彼此间隔开相应的距离且各自在Y方向上延布;胞元180-6d还包括栅极图案268-7及268-8,栅极图案268-7与268-8彼此间隔开相应的距离且各自在Y方向上延布;并且胞元180-6e还包括栅极图案268-9及268-10,栅极图案268-9与268-10彼此间隔开且各自在Y方向上延布。

在一些实施例中,集成电路180的每一胞元的第一植入区及第二植入区、有源区及栅极图案可在一个或多个第一布局层级上形成在衬底之上,此将在图2C及图2D所示剖视图中示出。如上所述,图2B示出集成电路180在所述一个或多个第一布局层级上方的第二布局层级处的布局设计的俯视图。

根据本发明的一些实施例,在第二布局层级处,每一胞元包括在Y方向上(即,与有源区平行)延布且位于相应的栅极图案之上的多个导体图案。在一些实施例中,包括所述多个导体图案的此种第二布局层级直接设置在包括栅极图案的所述一个或多个第一布局层级上方(即,其间没有设置中间布局层级),第二布局层级在本文中被称为“M1层级(第一金属层级/层)”。此外,M1层级中的所述多个导体图案各自通过至少一个通路结构(未示出)电耦合到以上论述的p型MOSFET及n型MOSFET中的一者或多者,从而使得p型MOSFET及n型MOSFET中的每一者能够被供电,或者电连接到其他MOSFET或器件。

如图2B中所示,M1层级包括在Y方向上延布的多个导体图案,例如(举例来说)电源轨条270-1、270-2、270-3、270-4、270-5、270-6及270-7,以及M1内连线272-1、272-2、272-3、272-4、272-5、272-6、272-7、272-8、272-9、272-10、272-11、272-12、272-13、272-14、272-15、272-16及272-17。在一些实施例中,当从M1层级的顶部观察时,沿着每一行的胞元设置在各自被配置成载送电源信号(例如,VDD、接地等)的两个相邻电源轨条之间。此外,在这两个相邻电源轨条之间,M1内连线的相应子集彼此平行地在胞元之上延布。

例如,行1处的胞元组180-1的胞元设置在电源轨条270-1与270-2之间,M1内连线272-1到272-4在所述胞元上延布;行2处的胞元组180-2的胞元设置在电源轨条270-2与270-3之间,M1内连线272-5到272-6在所述胞元上延布;行3处的胞元组180-3的胞元设置在电源轨条270-3与270-4之间,M1内连线272-7到272-10在所述胞元上延布;行4处的胞元组180-4的胞元设置在电源轨条270-4与270-5之间,M1内连线272-11到272-12在所述胞元上延布;行5处的胞元组180-5的胞元设置在电源轨条270-5与270-6之间,M1内连线272-13到272-16在所述胞元上延布;并且行6处的胞元组180-6的胞元设置在电源轨条270-6与270-7之间,M1内连线272-17到272-18在所述胞元上延布。

在一些实施例中,在胞元之上延布的M1内连线的数目可对应于所述胞元中所包括的有源区的数目。更具体来说,对于具有较大行高度(即,其中的胞元各自具有较高数目的有源区)的行,可包括更多的M1内连线,而对于具有较短行高度(即,其中的胞元各自具有较低数目的有源区)的行,可包括更少的M1内连线。例如,在设置在行1处的具有4个有源区(例如,212-1到212-4)的胞元之上延布的M1内连线的数目可多于在设置在行2处的具有2个有源区(例如,222-1及222-2)的胞元之上延布的M1内连线的数目。在图2B的所示实施例中,设置在行1处的M1内连线的数目是4(等于行1处的胞元的有源区的数目),且设置在行2处的M1内连线的数目是2(等于行2处的胞元的有源区的数目)。然而,应理解,M1内连线的数目不限于等于上面延布有M1内连线的有源区的数目。

此外,在一些实施例中,M1内连线272-1到272-17中的每一者可沿着X方向共享实质上共形的宽度273,且可与相邻的M1内连线或电源轨条分隔开实质上相似的距离275。此种对M1内连线形成的设计约束可有利地降低设计复杂性。例如,M1内连线272-2沿着X方向具有共形的宽度273,且分别与M1内连线272-1及272-3分隔开距离275。

参照图2C及图2D,根据一些实施例,示出胞元180-1a及180-1b在第一一个或多个布局层级处分别沿线A-A及B-B截取的剖视图。如图2C及图2D中分别所示,植入有n型掺杂剂的第一区214(本文中称为“n阱214”)设置在衬底280之上;且植入有p型掺杂剂的第二区216(本文中称为“p阱216”)设置在衬底280之上。在一些实施例中,衬底280包含Si、Ge、SiGe、InAs、InGaAs、InAlAs、InP等;n阱214包含Si、Ge、SiGe、InAs、InGaAs、InAlAs、InP等;并且p阱216包含Si、Ge、SiGe、InAs、InGaAs、InAlAs、InP等。在一些实施例中,当衬底280包含Si时,n阱214也可包含Si,但掺杂有例如P、As等n型掺杂剂,且P阱216也可包含Si,但掺杂有例如B、Ga等P型掺杂剂。

在一些实施例中,n阱214还可包括被以提高的掺杂浓度植入p型掺杂剂的第一组区280-1、280-2、280-3、280-4及280-5;并且p阱216还可包括被以提高的掺杂浓度植入n型掺杂剂的第二组区282-1、282-2、282-3、282-4及282-5。此种第一组植入区280-1到280-5及第二组植入区282-1到282-5可用作相应的MOSFET的源极或漏极,第一组植入区280-1到280-5及第二组植入区282-1到282-5中的每一者在X方向上设置在两个相邻栅极图案之间。例如,在图2C中,设置在栅极图案218-1与218-2之间的区280-1可用作以栅极图案218-1或218-2作为其栅极的p型MOSFET的源极或漏极;并且在图2D中,设置在栅极图案218-2与218-3之间的区282-2可用作以栅极图案218-2或218-3作为其栅极的n型MOSFET的源极或漏极。

在图2C及图2D的所示实施例中,尽管相邻胞元180-1a与180-1b的相应的“侧”栅极图案218-3与218-4被合并在一起以形成单个栅极图案,然而此种侧栅极图案可通过源极/漏极彼此分隔开,同时仍然在本发明的范围内。在如图2E及图2F中所示的其他实施例中,相邻胞元180-1a与180-1b不共享侧栅极图案,而是在侧栅极图案218-3与218-4之间的浅沟槽隔离(shallow trench isolation,STI)290、292的中间具有胞元边界。

根据一些实施例,包括第一组植入区280-1到280-5的n阱214可形成连续地延伸的有源区212-1的部分,如图2C中所示;并且包括第二组植入区282-1到282-5的p阱216可形成连续地延伸的有源区212-3的部分,如图2D中所示。

图2G示出根据本发明一些实施例的示例性集成电路180在一个或多个第一布局层级处的另一对应布局设计的俯视图。在此实施例中,如图2G中所示,栅极图案218-1到218-7中的每一者形成穿过集成电路180的不同行的直线。即,在栅极图案218-1到218-7中的每一者中,不同行中的多晶硅栅极在Y方向上沿着相同的线彼此对准。但是不同行中的多晶硅栅极可在两个相邻行之间的边界处分隔或隔离。即,栅极图案218-1到218-7构成的每条线可在两个相邻行之间的边界处具有断点。

现在参照图3,根据本发明的一些实施例,提供信息处置系统(IHS)300的方块图。IHS 300可为用于实施本文中所论述的任何或所有过程的计算机平台,以设计具有混合行高度的集成电路(例如,集成电路100、140及180)。IHS 300可包括处理单元310,例如桌上型计算机、工作站、膝上型计算机或为特定应用定制的专用单元。IHS 300可配备有显示器314及一个或多个输入/输出(input/output,I/O)组件312,例如鼠标、键盘或打印机。处理单元310可包括连接到总线330的中央处理器(central processing unit,CPU)320、存储器322、海量存储器件324、视频适配器326及I/O接口328。

总线330可为包括存储器总线或存储器控制器、外围总线或视频总线在内的任何类型的几种总线架构中的一种或多种。CPU 320可包括任何类型的电子数据处理器,且存储器322可包括任何类型的系统存储器,例如静态随机存取存储器(static random accessmemory,SRAM)、动态随机存取存储器(dynamic random access memory,DRAM)或只读存储器(read-only memory,ROM)。

海量存储器件324可包括任何类型的存储器件,所述存储器件被配置成存储数据、程序及其他信息以及使得数据、程序及其他信息可经由总线330存取。海量存储器件324可包括例如硬盘驱动器、磁盘驱动器、光盘驱动器等中的一种或多种。

视频适配器326及I/O接口328提供将外部输入及输出器件耦合到处理单元310的接口。如图3中所示,输入及输出器件的实例包括耦合到视频适配器326的显示器314以及耦合到I/O接口328的I/O组件312,例如鼠标、键盘、打印机等。其他器件可耦合到处理单元310,且可使用附加的或更少的接口卡。例如,串行接口卡(未示出)可用于为打印机提供串行接口。处理单元310还可包括网络接口340,网络接口340可为到局域网(local areanetwork,LAN)或广域网(wide area network,WAN)316的有线链路和/或无线链路。

应注意,IHS 300可包括其他组件/器件。例如,IHS 300可包括电源、电缆、母板、可拆卸存储介质、壳体(case)等。尽管未示出,然而这些其他组件/器件被视为IHS 300的部分。

在本发明的一些实施例中,电子设计自动化(EDA)是由CPU 320执行以分析用户文件来获得集成电路(例如,以上论述的集成电路100、140及180)的布局的程序码。此外,在执行EDA期间,EDA可分析布局的功能性组件,如所属领域中已知。程序码可由CPU 320经由总线330从存储器322、海量存储器件324等存取,或者通过网络接口340远程存取。

图4示出根据本发明一些实施例的由IHS 300实行以产生包括混合行高度的集成电路的物理布局的示例性方法400的流程图。在一些实施例中,此种方法400可统称为EDA。在各种实施例中,方法400的操作由图3中所示的相应组件来实行。出于论述目的,将结合图3阐述方法400的以下实施例。方法400的所示实施例仅为实例。因此,应理解,可对各种操作中的任一者进行省略、重新排序和/或添加,同时仍然在本发明的范围内。

方法400以提供操作“行为/功能性设计402”、“设计约束404”及“混合行高度406”开始。在一些实施例中,行为/功能性设计402基于施加到集成电路的整体设计的输入的各种信号或激励来指定集成电路(例如,以上论述的集成电路100、140和/或180)的所期望行为或功能,且可以例如硬件描述语言(hardware description language,HDL)等合适的语言书写。可例如在EDA正在执行的同时由创建文件的用户通过I/O接口328(图3)将行为/功能性设计402上传到处理单元310中。作为另外一种选择,可将行为/功能性设计402上传和/或保存在存储器322或海量存储器件324上,或者可通过网络接口340从远程用户(图3)上传行为/功能性设计402。在这些情形中,在执行EDA期间,CPU 320将存取行为/功能性设计402。

此外,用户还提供设计约束404,以便约束行为/功能性设计402的物理布局的整体设计。在一些实施例中,设计约束404可例如通过I/O接口328输入、通过网络接口340下载等。设计约束404可指定定时、工艺参数及行为/功能性设计402一旦物理地形成为集成电路就必须遵守的其他合适的约束。

此外,用户还可提供混合行高度406,以便使得行为/功能性设计402的物理布局能够被布置成多个行,所述多个行具有至少两个各自不同的行高度。在一些实施例中,混合行高度406可例如通过I/O接口328输入、通过网络接口340下载等。混合行高度406可指定行比率(即,如上所述的具有各自不同的行高度的行的数目的比率)、相对于物理布局的网格具有各自不同的行高度的行的相应位置、和/或行为/功能性设计402一旦物理地形成为集成电路就必须遵守的其他合适的约束。

在提供行为/功能性设计402、设计约束404及混合行高度406之后,方法400继续进行到操作“综合408”,以创建功能等效逻辑门层级电路描述(logic gate-level circuitdescription),例如网表。综合408通过在满足由设计约束404及混合行高度406指定的约束的同时将行为/功能性设计402所期望的行为和/或功能匹配到来自胞元库集合409的(标准)胞元来形成功能等效逻辑门层级电路描述。

在一些实施例中,胞元库集合409可包括具有各自不同的胞元高度的多个胞元库,例如(举例来说)胞元库411、胞元库413等。在一些实施例中,胞元库411及413可分别对应于上述胞元库A及胞元库B。所述多个胞元库中的每一者包含一系列预先设计的胞元,预先设计的胞元中的每一者具有共同的胞元高度且可在小规模上实行特定逻辑功能。例如,胞元库A411的胞元可共享胞元高度A,且胞元库B 413的胞元可共享胞元高度B。胞元存储在胞元库(例如,胞元库A 411、胞元库B 413等)中作为信息,所述信息包括内部电路元件、到这些电路元件的各种连接、包括胞元高度、掺杂剂类型、掺杂浓度、阱等的预先设计的物理布局图案。另外,所存储的胞元还可包括胞元的形状、外部连接的端子位置、延迟特性、功耗等。

一旦综合408使用胞元库集合409(例如,胞元库A 411、胞元库B 413等)的胞元从行为/功能性设计402、设计约束404及混合行高度406产生功能等效逻辑门层级电路描述,方法400便继续进行到第一判断操作414,以检查设计要求是否匹配。在一些实施例中,在第一判断操作414中,可通过使用例如强调集成电路的仿真程序(Simulation Program withIntegrated Circuit Emphasis,SPICE)等电路仿真器实行一个或多个仿真来检查各种要求,例如(举例来说)胞元库A 411中的可用胞元对胞元库B 413中的可用胞元的比率、功能等效逻辑门层级电路描述的定时品质(timing quality)、功能等效逻辑门层级电路描述的功率品质等。如果满足第一判断操作414中的所有设计要求,则方法400继续进行到操作“放置及布线418”,此将在下文进一步详细论述。另一方面,如果并未满足第一判断操作414中的所有设计要求,则方法400继续进行到操作“查找根本原因416”,此也将在下文进一步详细论述。

实行放置及布线418以产生整体结构的实际物理设计。放置及布线418通过从胞元库集合409选取所选择胞元并将其放置到相应的行中来形成物理设计。在一些实施例中,第一组此种行具有与设置在第一组行内的大多数胞元的高度实质上相似的第一行高度,使得电源轨条、植入物及阱可在胞元之间对准;并且第二组此种行具有与第一行高度不同的第二行高度,第二行高度与设置在第二组行内的大多数胞元的高度实质上相似,使得电源轨条、植入物及阱可在胞元之间对准。每一胞元在胞元行内的放置以及每一胞元行相对于其他胞元行的放置可由成本函数(cost function)来指导,以便最小化所得集成电路的走线长度及面积要求。此种放置可由放置及布线418自动完成,或者可作为另外一种选择部分地通过手动过程来实行,由此用户可手动地将一个或多个胞元插入到一行中。

一旦放置及布线418完成产生整体结构的实际物理设计,方法400便继续进行到第二判断操作420,以检查设计要求是否匹配。在一些实施例中,在第二判断操作420中,可通过使用例如强调集成电路的仿真程序(SPICE)等电路仿真器实行一个或多个仿真来检查各种要求,例如(举例来说)在放置及布线418之后胞元库A411中的可用胞元对胞元库B 413中的可用胞元的比率、整体结构的实际物理设计的定时品质、整体结构的实际物理设计的功率品质、是否存在局部拥塞问题等。如果满足第二判断操作420中的所有设计要求,则方法400继续进行到操作“制造工具422”,此将在下文进一步详细论述。另一方面,如果并未满足第二判断操作420中的所有设计要求,则方法400继续进行到查找根本原因416,此将被论述如下。

根据一些实施例,实行查找根本原因416以查找导致在第一判断操作414或第二判断操作420中未能满足设计要求的原因。各种原因可能导致未能满足设计要求。基于原因是哪个或哪些,方法400可进行到相应的操作以重新实行此操作。例如,当原因是由于用于产生功能等效逻辑门层级电路描述的胞元的不良功率、性能、面积(power,performance,area,PPA)特性和/或胞元库集合409中缺少可用胞元时,方法400可进行到重新评估胞元库集合409的胞元的品质/数量的操作;当原因是由于行的不正确布置时,方法400可返回到混合行高度406,以重新评估其中指定的约束;当原因是由于综合功能等效逻辑门层级电路描述的不可行性时,方法400可返回到设计约束404以重新评估其中指定的约束;并且当原因是由于产生实际物理设计的不可行性时,方法400可返回到放置及布线418以重新放置和/或重新布线。

重新参照第二判断操作420,一旦已通过放置及布线418成功地产生物理设计,同时满足所有设计要求,方法400便继续进行到操作“制造工具422”以产生例如可在物理地制造物理设计中使用的光刻掩模。物理设计可通过此LAN/WAN 316发送到制造工具422。

图5示出根据本发明一些实施例的各种混合行设计情景的不同应用。图5示出五种示例性IC应用,所述五种示例性IC应用中的每一者对应于不同类型的混合行设计。混合行设计512、522、532、542、552在行-A(Row-A)与行-B(Row-B)之间具有不同的混合行比率,其中行-A代表包括来自胞元库A的胞元的行的数量,且行-B代表包括来自胞元库B的胞元的行的数量。在此实例中,来自胞元库A的每一胞元的胞元高度大于来自胞元库B的每一胞元的胞元高度。

例如,实现最高速度所期望的“速度最佳的”电路510可通过具有为3:1的混合行比率的混合行设计512来实现,为3:1的混合行比率意味着在混合行设计512中,行-A(包括来自胞元库A的胞元的行的数量)与行-B(包括来自胞元库B的胞元的行的数量)之间的比率是3:1。此是因为胞元高度越大的胞元越多,则可有助于提高速度。

在另一个实例中,实现最小面积及最低功耗所期望的“功率/面积最佳的”电路550可通过具有为1:3的混合行比率的混合行设计552来实现,为1:3的混合行比率意味着在混合行设计552中,行-A(包括来自胞元库A的胞元的行的数量)与行-B(包括来自胞元库B的胞元的行的数量)之间的比率是1:3。此是因为胞元高度越小的胞元越多,则可有助于节省电路面积及降低功耗。

在另一个实例中,“平衡的”电路530可通过具有为1:1的混合行比率的混合行设计532来实现,为1:1的混合行比率意味着在混合行设计532中,行-A(包括来自胞元库A的胞元的行的数量)与行-B(包括来自胞元库B的胞元的行的数量)之间的比率是1:1。“平衡的”电路530将保持不过高或过低的速度性能与面积/功率性能之间的平衡,其中面积不过大或过小且功耗不过高或过低。

在又一个实例中,实现高但不是最高的速度所期望的“以速度为取向的”电路520可通过具有为2:1的混合行比率的混合行设计522来实现,为2:1的混合行比率意味着在混合行设计522中,行-A(包括来自胞元库A的胞元的行的数量)与行-B(包括来自胞元库B的胞元的行的数量)之间的比率是2:1。

在又一个实例中,实现高但不是最高的功率/面积性能所期望的“以功率/面积为取向的”电路540可通过具有为1:2的混合行比率的混合行设计542来实现,为1:2的混合行比率意味着在混合行设计542中,行-A(包括来自胞元库A的胞元的行的数量)与行-B(包括来自胞元库B的胞元的行的数量)之间的比率是1:2。

图6示出根据本发明一些实施例的用于设计包括混合行高度的集成电路的示例性过程。在操作610处,设计至少两组库:库A及库B。不同库中的胞元具有不同的胞元高度和/或不同数目的金属线。例如,库A胞元具有较高的胞元高度及五条金属线,而库B胞元具有较低的胞元高度及三条金属线。在操作620处,选择平衡设计情景来保持所述两个库的胞元之间的混合行比率为1:1。在操作630处,基于为1:1的平衡混合行比率,用库A及库B的指定放置约束来初始化混合行布局规划(mixed row floorplan)。

图7示出根据本发明一些实施例的平面板或纳米片材中的胞元在一个或多个布局层级处的对应布局设计700的俯视图。如图7中所示,布局设计700包括布置在相同的行中的两个相邻胞元710、720。沿着此行,胞元710及720分别包括沿着X方向连续地延伸跨越胞元710及720的四个有源区702、704、706、708。布局设计700可用于包括胞元710、720的平面板,或者用于包括胞元710、720及沿着Z方向布置的附加层的纳米片材。

在一个实施例中,胞元720的有源区用作胞元720的相应晶体管的源极特征或漏极特征,以实行特定逻辑功能。所述四个有源区702、704、706、708中的每一者可包含半导体材料,例如硅,且可包含n型掺杂剂或p型掺杂剂。在一个实例中,有源区702、708植入有n型掺杂剂;并且有源区704、706植入有p型掺杂剂。

此外,根据一些实施例,胞元720包括多个栅极图案722,栅极图案722在与有源区沿其进行延伸的方向(X方向)实质上正交的方向(Y方向)上延伸,以形成p型MOSFET及n型MOSFET的相应栅极。在一个实施例中,每一栅极图案可包括在有源区702、704、706、708上沿着Y方向延伸的介电层724,以及在介电层724上沿着Y方向延伸的金属层726。

在一个实施例中,除胞元710填充到电路位置中以外,胞元710的有源区不实行任何特定功能。在图7中所示的实例中,胞元720可被称为功能性胞元,且胞元710可被称为填充胞元(filler cell)。胞元710与胞元720具有相似的结构。在功能性胞元被放置到电路设计布局中之后,填充胞元被放置到没有放置功能性胞元的电路位置中。在此实例中,胞元710包括在Y方向上延伸的多个虚设栅极图案712。如图7中所示,胞元710、720还具有设置在相邻胞元之间的边界上的边缘栅极730。虚设栅极图案712及边缘栅极730可具有与功能性栅极图案722相同的结构及材料。例如,虚设栅极图案712及边缘栅极730中的每一者可包括在有源区702、704、706、708上沿着Y方向延伸的介电层724,以及在介电层724上沿着Y方向延伸的金属层726。

在一个实施例中,有源区702、704、706、708中的至少一者具有沿着X方向变化的宽度。如图7中所示,有源区702、704、706、708中的每一者具有沿着X方向变化的宽度。例如,有源区702的宽度在每一胞元内改变,且沿着X方向跨越两个相邻胞元710、720改变。

图8示出根据本发明一些实施例的FinFET或纳米走线中的胞元在一个或多个布局层级处的对应布局设计800的俯视图。如图8中所示,布局设计800包括布置在相同的行中的两个相邻胞元810、820。沿着此行,胞元810及820分别包括沿着X方向连续地延伸跨越胞元810及820的四个有源区组802、804、806、808。在此实例中,胞元810、820的每一有源区包括鳍形结构。有源区组802、804、806、808中的每一有源区可为FinFET结构的鳍或者纳米走线结构的走线,所述纳米走线结构包括沿着Z方向布置的多个层。

在一个实施例中,胞元820的有源区用作胞元820的相应晶体管的源极特征或漏极特征,以实行特定逻辑功能。每一有源区可包含半导体材料,例如硅,且可包含n型掺杂剂或p型掺杂剂。在一个实例中,有源区组802、808植入有n型掺杂剂;并且有源区组804、806植入有p型掺杂剂。

此外,根据一些实施例,胞元820包括多个栅极图案822,栅极图案822在与有源区沿着其延伸的方向(X方向)实质上正交的方向(Y方向)上延伸,以形成p型晶体管及n型晶体管的相应栅极。在一个实施例中,每一栅极图案可包括在有源区组802、804、806、808上沿着Y方向延伸的介电层824,以及在介电层824上沿着Y方向延伸的金属层826。

在一个实施例中,除胞元810填充到电路位置中以外,胞元810的有源区不实行任何特定功能。在图8中所示的实例中,胞元820可被称为功能性胞元,且胞元810可被称为填充胞元。胞元810与胞元820具有相似的结构。在功能性胞元被放置到电路设计布局中之后,填充胞元被放置到没有放置功能性胞元的电路位置中。在此实例中,胞元810包括在Y方向上延伸的多个虚设栅极图案812。如图8中所示,胞元810、820还具有设置在相邻胞元之间的边界上的边缘栅极830。虚设栅极图案812及边缘栅极830可具有与功能性栅极图案822相同的结构及材料。例如,虚设栅极图案812及边缘栅极830中的每一者可包括在有源区组802、804、806、808上沿着Y方向延伸的介电层824,以及在介电层824上沿着Y方向延伸的金属层826。

在一个实施例中,尽管有源区组802、804、806、808中的每一有源区在不同胞元之间具有固定宽度,然而有源区组802、804、806、808中的至少一者中的有源区数量沿着X方向变化。如图8中所示,有源区组802中的有源区数量沿着X方向跨越所述两个相邻胞元810、820改变。有源区组804中的有源区数量沿着X方向在胞元820内改变。

图9示出根据本发明一些实施例的平面板或纳米片材中的胞元结构900的俯视图。如图9中所示,胞元结构900包括沿着X方向延伸的p型有源区902及n型有源区904。不同的有源区902、904沿着与X方向正交的Y方向布置,以在纳米片材中形成平面板或片材,所述纳米片材具有沿着Z方向堆叠的多个片材。

如图9中所示,p型有源区902的宽度被标记为W

图9示出根据本发明一些实施例的平面板或纳米片材中的胞元结构900的俯视图。如图9中所示,胞元结构900包括沿着X方向延伸的p型有源区902及n型有源区904。不同的有源区902、904沿着与X方向正交的Y方向布置,以在纳米片材中形成平面板或片材,所述纳米片材具有沿着Z方向堆叠的多个片材。胞元结构900还包括在有源区902、904上且跨越有源区902、904沿着Y方向延伸的多个栅极912。

如图9中所示,p型有源区902的宽度被标记为W

图10示出根据本发明一些实施例的FinFET或纳米走线中的胞元结构1000的俯视图。如图10中所示,胞元结构1000包括沿着X方向延伸的p型有源区组1002及n型有源区组1004。不同的有源区组1002、1004沿着与X方向正交的Y方向布置。胞元结构1000还包括在有源区组1002、1004上且跨越有源区组1002、1004沿着Y方向延伸的多个栅极1012。有源区组1002、1004中的每一有源区可为FinFET结构的鳍或者纳米走线的走线,所述纳米走线具有沿着Z方向堆叠的多个层。

如图10中所示,有源区组1002中的p型有源区数量被标记为N

如图10中所示,N

图11示出根据本发明一些实施例的由高性能(HP)胞元及低功率(LP)胞元构成的胞元系列。如图11中所示,HP胞元1110包括沿着X方向延伸的p型有源区1112及n型有源区1114。不同的有源区1112、1114沿着与X方向正交的Y方向布置。HP胞元1110还包括在有源区1112、1114上且跨越有源区1112、1114沿着Y方向延伸的多个栅极1115。两个相邻栅极1115之间的距离被称为栅极节距(gate pitch)P。如图11中所示,HP胞元1110具有胞元高度H

如图11中所示,HP胞元1110中的有源区1112、1114中的每一者具有沿着X方向变化的第一宽度。根据各种实施例,第一宽度在和胞元高度H

如图11中所示,LP胞元1120包括沿着X方向延伸的p型有源区1122及n型有源区1124。不同的有源区1122、1124沿着Y方向布置。LP胞元1120还包括在有源区1122、1124上且跨越有源区1122、1124沿着Y方向延伸的多个栅极1125。每两个相邻的栅极1125也彼此具有栅极节距P。LP胞元1120具有胞元高度H

如图11中所示,LP胞元1120中的有源区1122、1124中的每一者具有沿着X方向变化的第二宽度。根据各种实施例,第二宽度在和胞元高度H

在一些实施例中,胞元1110、1120是从具有不同胞元高度的相应标准胞元库检索。更具体来说,胞元1110可从包括多个胞元的第一标准胞元库(下文中称为“胞元库HP”)检索,所述多个胞元中的每一者共享第一胞元高度(下文中称为“胞元高度H

尽管图11中的胞元1110、1120是平面板或纳米片材中的HP胞元及LP胞元,然而相似的胞元结构可应用于其中每一胞元具有沿着X方向延伸的一定数目的鳍的FinFET或纳米走线。每一鳍具有固定宽度,但是每一胞元中的鳍的数量可沿着X方向变化。在一个实施例中,HP胞元中的鳍的数量在和胞元高度H

比较图11中的所述两个胞元1110、1120,所述两个胞元1110、1120可具有相同的栅极节距P、相同或不同的宽度W

图12示出根据本发明一些实施例的具有各种HP对LP行比率的布局设计。图12中的每一布局设计包括在X方向上延伸的第一多个胞元行(HP行),以及在X方向上延伸的第二多个胞元行(LP行)。图12中的每一HP行具有第一行高度,且包括多个HP胞元如同图11中公开的HP胞元1110;并且图12中的每一LP行具有与第一行高度不同的第二行高度,且包括多个LP胞元如同图11中公开的LP胞元1120。在一个实施例中,每一行的行高度对应于放置在其中的胞元的胞元高度。例如,每一行的行高度实质上等于放置在其中的胞元的胞元高度。

如图12中所示,根据HP行的数目与LP行的数目之间的比率,HP行与LP行沿着与X方向垂直的Y方向进行混合和布置。例如,对于布局设计1210,HP行的数量与LP行的数量之间的比率是2/1,对于布局设计1220是1/1,且对于布局设计1230是1/2。根据各种实施例,例如1/3、2/3、3/2、1/4、3/1、4/1等任何其他行比率仍然在本发明的范围内。

图13示出根据本发明一些实施例的由合并式HP-LP胞元1310、1320、1330、1340构成的胞元系列。如图13中所示,HLP胞元1310是通过沿着Y方向连结HP胞元1311与LP胞元1315而形成。HLP胞元1310包括均沿着X方向延伸的两个p型有源区1312、1318及两个n型有源区1314、1316。不同的有源区1312、1314、1316、1318沿着Y方向布置。如图13中所示,HLP胞元1310具有胞元高度H

与HLP胞元1310相似,图13中的HLP胞元1320是通过沿着Y方向连结HP胞元1321与LP胞元1325而形成。HLP胞元1320包括均沿着X方向延伸的两个n型有源区1322、1328及两个p型有源区1324、1326。不同的有源区1322、1324、1326、1328沿着Y方向布置。尽管HLP胞元1310具有沿着Y方向布置的两个相邻的n型有源区1314、1316,然而HLP胞元1320具有沿着Y方向布置的两个相邻的p型有源区1324、1326。如图13中所示,HLP胞元1320也具有胞元高度H

与HLP胞元1310相似,图13中的HLP+胞元1330是通过沿着Y方向连结HP胞元1331与LP胞元1335并将两个相邻的n型有源区合并成合并式有源区而形成。HLP+胞元1330包括均沿着X方向延伸的两个p型有源区1332、1336及合并式n型有源区1334。不同的有源区1332、1334、1336沿着Y方向布置。如图13中所示,HLP+胞元1330具有胞元高度H

与HLP胞元1320相似,图13中的HLP+胞元1340是通过沿着Y方向连结HP胞元1341与LP胞元1345并将两个相邻的p型有源区合并成合并式有源区而形成。HLP+胞元1340包括均沿着X方向延伸的两个n型有源区1342、1346及合并式p型有源区1344。不同的有源区1342、1344、1346沿着Y方向布置。如图13中所示,HLP+胞元1340还具有胞元高度H

在一些实施例中,合并式HP-LP胞元1310、1320、1330、1340是从具有不同胞元高度的相应标准胞元库检索。更具体来说,HLP胞元1310、1320可从包括多个胞元的第三标准胞元库(下文中称为“胞元库HLP”)检索,所述多个胞元中的每一者共享第三胞元高度(下文中称为“胞元高度H

尽管图13中的胞元1310、1320、1330、1340是平面板或纳米片材中的HLP胞元及HLP+胞元,然而相似的胞元结构可应用于其中每一胞元具有沿着X方向延伸的一定数目的鳍的FinFET或纳米走线。每一鳍具有固定宽度,但是每一胞元中的鳍的数量可沿着X方向变化。在一个实施例中,HLP胞元或HLP+胞元中的鳍的数量等于HP胞元中的鳍的第一数量与LP胞元中的鳍的第二数量的和。在一个实施例中,HLP+胞元中的有源区组的鳍是通过将HP胞元与LP胞元的两个相邻有源区组的鳍合并而形成。

图14示出根据本发明一些实施例的具有1/1的HP/LP行比率的示例性集成电路的对应布局设计1400的俯视图。如图14中所示,集成电路的布局设计1400包括在第一方向(X方向)上延伸的第一多个胞元行1410、1430、1450,以及在第一方向上延伸的第二多个胞元行1420、1440。第一多个胞元行1410、1430、1450中的每一者具有第一行高度,且包括设置在其中的多个第一胞元;第二多个胞元行1420、1440中的每一者具有与第一行高度不同的第二行高度,且包括设置在其中的多个第二胞元。在一个实施例中,第一多个胞元行1410、1430、1450是LP行,且第一胞元是LP胞元;第二多个胞元行1420、1440是HP行,且第二胞元是HP胞元。HP行与LP行根据1/1比率沿着与第一方向垂直的第二方向(Y方向)进行混合。在图14中所示的实例中,HP行与LP行根据1/1比率沿着Y方向交替设置。

如图14中所示,每一LP行中的LP胞元包括第一多个有源区1412、1414,第一多个有源区1412、1414中的每一者在X方向上连续地延伸跨越LP胞元;并且每一HP行中的HP胞元包括第二多个有源区1442、1444,第二多个有源区1442、1444中的每一者在X方向上连续地延伸跨越HP胞元。第一多个有源区及第二多个有源区中的至少一个有源区具有沿着X方向变化的宽度。在图14中所示的实例中,每一LP胞元所具有的胞元高度等于LP行1410、1430、1450的行高度;并且每一HP胞元所具有的胞元高度等于HP行1420、1440的行高度。

如图14中所示,布局设计1400还可包括HLP胞元1462,HLP胞元1462是由沿着Y方向彼此相邻的LP胞元与HP胞元一起形成的合并式胞元。因此,HLP胞元1462所具有的胞元高度等于LP行高度与HP行高度的和。

如图14中所示,布局设计1400还可包括HLP+胞元1464,HLP+胞元1464是由沿着Y方向彼此相邻的LP胞元与HP胞元一起、通过将LP胞元及HP胞元的两个相邻有源区合并以形成合并式有源区而形成的合并式胞元。合并式有源区沿着Y方向延伸跨越LP胞元及HP胞元,且具有沿着X方向变化的宽度。HLP+胞元1464所具有的胞元高度等于LP行高度与HP行高度的和。如图14中所示,LP行1410、1430、1450中的每一LP胞元可为独立的LP胞元或者合并式HP-LP胞元(例如,HLP胞元或HLP+胞元)的LP胞元部分;HP行1420、1440中的每一HP胞元可为独立的HP胞元或者合并式HP-LP胞元(例如,HLP胞元或HLP+胞元)的HP胞元部分。

在图14中所示的实例中,胞元的胞元宽度可为灵活的,而无论所述胞元是:HP胞元、LP胞元、HLP胞元还是HLP+胞元。但是LP胞元的胞元高度比HP胞元的胞元高度短。另外,HLP胞元的胞元高度等于HLP+胞元的胞元高度,且等于LP胞元与HP胞元的胞元高度的和。

如图14中所示,布局设计1400中的每一胞元可为实行设计功能的功能性胞元,或者是除填充到功能性胞元之间的电路空间中以外不实行任何特定功能的填充胞元。功能性胞元及填充胞元可具有相似的结构。每一功能性胞元可具有与以下胞元中的一者相同的胞元结构:HP胞元、LP胞元、HLP胞元或HLP+胞元。相似地,每一填充胞元也可具有与以下胞元中的一者相同的胞元结构:HP胞元、LP胞元、HLP胞元或HLP+胞元。在制作电路期间,在功能性胞元的放置完成之后,可将填充胞元放置到功能性胞元之间的空间中。

在此实施例中,栅极图案1470中的每一者形成穿过集成电路的不同行的直线。即,在每一栅极图案1470中,不同行中的多晶硅栅极在Y方向上沿着相同的线彼此对准。在其他实施例中,不同行中的多晶硅栅极可不在Y方向上彼此对准。尽管布局设计1400是基于具有连续有源区的平面板或纳米片材,然而相似的布局设计可应用于具有量化(quantized)有源区或鳍的FinFET或纳米走线。

图15示出根据本发明一些实施例的具有2/1的HP/LP行比率的示例性集成电路的对应布局设计1500的俯视图。如图15中所示,集成电路的布局设计1500包括在X方向上延伸的第一多个胞元行(LP行)1510、1540,以及在X方向上延伸的第二多个胞元行(HP行)1520、1530、1550。LP行1510、1540中的每一者具有第一行高度,且包括设置在其中的多个LP胞元;HP行1520、1530、1550中的每一者具有与第一行高度不同的第二行高度,且包括设置在其中的多个HP胞元。除布局设计1500中的HP行与LP行根据2/1比率沿着与X方向垂直的Y方向进行混合以外,布局设计1500与图14中的布局设计1400相似。在图15中所示的实例中,HP行与LP行沿着Y方向以2:1比率交替设置。由于所述2:1比率,在给定布局设计的总行数的情况下,与布局设计1400相比,布局设计1500具有较小数目的相邻HP行与LP行。因此,与图14中的布局设计1400相比,布局设计1500具有较少的可用胞元位置来放置HLP胞元或HLP+胞元。

图16示出根据本发明一些实施例的具有1/2的HP/LP行比率的示例性集成电路的对应布局设计1600的俯视图。如图16中所示,集成电路的布局设计1600包括在X方向上延伸的第一多个胞元行(HP行)1610、1640,以及在X方向上延伸的第二多个胞元行(LP行)1620、1630、1650。HP行1610、1640中的每一者具有第一行高度,且包括设置在其中的多个HP胞元;LP行1620、1630、1650中的每一者具有与第一行高度不同的第二行高度,且包括设置在其中的多个LP胞元。除布局设计1600中的HP行与LP行根据1/2比率沿着与X方向垂直的Y方向进行混合以外,布局设计1600与图14中的布局设计1400相似。在图16中所示的实例中,HP行与LP行沿着Y方向以1:2比率交替设置。由于所述1:2比率,在给定布局设计的总行数的情况下,与布局设计1400相比,布局设计1600具有较小数目的相邻HP行与LP行。因此,与图14中的布局设计1400相比,布局设计1600具有较少的可用胞元位置来放置HLP胞元或HLP+胞元。

图17示出根据本发明一些实施例的平面板或纳米片材中的胞元的对应布局设计1700的俯视图,对应布局设计1700具有灵活有源区宽度及灵活有源区转变。为简单起见,图17中未示出栅极图案。如图17中所示,集成电路的布局设计1700包括在X方向上延伸的第一多个胞元行(LP行)1710、1730、1750,以及在X方向上延伸的第二多个胞元行(HP行)1720、1740。LP行1710、1730、1750中的每一者具有第一行高度,且包括设置在其中的多个LP胞元;HP行1720、1740中的每一者具有与第一行高度不同的第二行高度,且包括设置在其中的多个HP胞元。布局设计1700中的HP行与LP行沿着Y方向以1:1比率交替设置。在一个实施例中,布局设计1700中的一些胞元是功能性胞元,且布局设计1700中的其他胞元是填充胞元。

如图17中所示,存在有在HP、LP、HLP及HLP+胞元上且跨越HP、LP、HLP及HLP+胞元沿着X方向延伸的p型有源区及n型有源区。有源区宽度或片材宽度可为灵活的,且沿着X方向变化。在一个实例中,沿着X方向,LP行1730中的p型有源区可在一个位置处具有宽度W1,且在另一个位置处具有宽度W2。在此实例中,W1>W2,且W1及W2二者均小于1/2H

在另一个实例中,沿着X方向,HP行1740中的p型有源区可在一个位置处具有宽度W3,且在另一个位置处具有宽度W4。在此实例中,W3>W4,且W3及W4二者均小于1/2H

在又一个实例中,沿着X方向,跨越LP行1730及HP行1740设置的n型合并式有源区可在一个位置处具有宽度W5,且在另一个位置处具有宽度W6。在此实例中,W5 如图17中所示,由于变化的片材宽度和/或合并式片材,因此在布局设计1700中存在各种有源区转变1781、1782、1783、1784。在一个实例中,在转变1781处,有源区沿着X方向从较窄的片材连续地转变为较宽的片材。在一个实例中,在转变1782处,有源区沿着X方向从较宽的片材连续地转变为较窄的片材。 在另一个实例中,在转变1783处,两个有源区沿着X方向转变为一个合并式有源区。在又一个实例中,在转变1784处,一个合并式有源区沿着X方向被分成两个有源区。 图18示出根据本发明一些实施例的FinFET或纳米走线中的胞元的对应布局设计1800的俯视图,对应布局设计1800具有灵活鳍数目及灵活有源区转变。为简单起见,图18中未显示栅极图案。如图18中所示,集成电路的布局设计1800包括在X方向上延伸的第一多个胞元行(LP行)1810、1830、1850,以及在X方向上延伸的第二多个胞元行(HP行)1820、1840。LP行1810、1830、1850中的每一者具有第一行高度,且包括设置在其中的多个LP胞元;HP行1820、1840中的每一者具有与第一行高度不同的第二行高度,且包括设置在其中的多个HP胞元。布局设计1800中的HP行与LP行沿着Y方向以1:1比率交替设置。在一个实施例中,布局设计1800中的一些胞元是功能性胞元,且布局设计1800中的其他胞元是填充胞元。 如图18中所示,存在有在HP、LP、HLP及HLP+胞元上且跨越HP、LP、HLP及HLP+胞元沿着X方向延伸的p型有源区组及n型有源区组。每一有源区组的鳍数目或走线数目可为灵活的,且沿着X方向变化。在一个实例中,沿着X方向,LP行1830中的p型有源区组可在一个位置处具有N1个鳍,且在另一个位置处具有N2个鳍。在此实例中,N1>N2,且N1及N2二者均为正整数。在另一个实例中,沿着X方向,HP行1840中的p型有源区组可在一个位置处具有N3个鳍,且在另一个位置处具有N4个鳍。在此实例中,N3>N4,且N3及N4二者均为正整数。在又一个实例中,沿着X方向,跨越LP行1830及HP行1840设置的n型合并式有源区组可在一个位置处具有N5个鳍,且在另一个位置处具有N6个鳍。在此实例中,N5 如图18中所示,由于变化的鳍数目和/或合并式鳍组,在布局设计1800中存在各种有源区转变1881、1882、1883、1884。在一个实例中,在转变1881处,鳍组或有源区组沿着X方向从较小数目的鳍连续地转变为较大数目的鳍。在一个实例中,在转变1882处,鳍组沿着X方向从较大数目的鳍连续地转变为较小数目的鳍。 在另一个实例中,在转变1883处,两个鳍组沿着X方向转变为一个合并式鳍组,其中至少一个鳍沿着X方向从左到右在转变1883之后出现。在又一个实例中,在转变1884处,一个合并式鳍组沿着X方向被分成两个鳍组,其中至少一个鳍沿着X方向从左到右在转变1884之后终止。 图19示出根据本发明一些实施例的用于产生用于制作的集成电路的物理布局的示例性方法1900的流程图。在操作1902处,提供包括多个第一胞元的第一库,所述多个第一胞元各自具有第一胞元高度且包括沿着第一方向连续地延伸的多个有源区。在操作1904处,提供包括多个第二胞元的第二库,所述多个第二胞元各自具有与第一胞元高度不同的第二胞元高度且包括沿着第一方向连续地延伸的多个有源区。在操作1906处,从第一库检索所述多个第一胞元的第一子集,且从第二库检索所述多个第二胞元的第二子集。在操作1908处,将沿着第一方向延伸的所述多个第一胞元的第一子集放置在第一多个胞元行中,且将沿着第一方向延伸的所述多个第二胞元的第二子集放置在第二多个胞元行中。在操作1910处,例如基于集成电路的性能要求,确定沿着与第一方向垂直的第二方向布置的第一多个胞元行的数目与第二多个胞元行的数目之间的比率。在操作1912处,基于所述比率,沿着第二方向放置第一多个胞元行及第二多个胞元行,以形成布局。在操作1914处,基于所述布局来制作集成电路。在一个实施例中,在第一多个胞元行及第二多个胞元行中的每一胞元行中,有源区数量沿着第一方向变化。在各种实施例中,方法1900的操作是由图3中所示的相应组件实行。根据本发明的各种实施例,图19中的操作次序可进行改变。 在一个实施例中,一种集成电路结构包括:第一多个胞元行,在第一方向上延伸,第一多个胞元行中的每一者具有第一行高度且包括设置在其中的多个第一胞元;以及第二多个胞元行,在第一方向上延伸,第二多个胞元行中的每一者具有与第一行高度不同的第二行高度且包括设置在其中的多个第二胞元。所述多个第一胞元包括第一多个有源区,第一多个有源区中的每一者在第一方向上连续地延伸跨越所述多个第一胞元,且其中所述多个第二胞元包括第二多个有源区,第二多个有源区中的每一者在第一方向上连续地延伸跨越所述多个第二胞元。 在另一个实施例中,一种集成电路结构包括:多个第一胞元,各自具有第一胞元高度,其中所述多个第一胞元的第一子集沿着第一方向设置在第一胞元行中;以及多个第二胞元,各自具有与第一胞元高度不同的第二胞元高度,其中所述多个第二胞元的第二子集沿着第一方向设置在与第一胞元行不同的第二胞元行中。所述多个第一胞元各自包括第一多个有源区,第一多个有源区各自连续地延伸跨越所述多个第一胞元的第一子集,且其中所述多个第二胞元各自包括第二多个有源区,第二多个有源区各自连续地延伸跨越所述多个第二胞元的第二子集。 在又一个实施例中,一种集成电路设计系统包括:非暂时性存储介质,被用指令集进行编码;以及硬件处理器,与非暂时性存储介质通信耦合,且被配置成执行所述指令集,所述指令集被配置成使处理器:提供包括多个第一胞元的第一库,所述多个第一胞元各自包括沿着第一方向连续地延伸的第一多个有源区;提供包括多个第二胞元的第二库,所述多个第二胞元各自包括沿着第一方向连续地延伸的第二多个有源区,其中第一多个有源区与第二多个有源区的相应数目彼此不同;从第一库检索所述多个第一胞元的第一子集和/或从第二库检索所述多个第二胞元的第二子集;以及将沿着第一方向延伸的所述多个第一胞元的第一子集放置在第一多个胞元行中,和/或将沿着第一方向延伸的所述多个第二胞元的第二子集放置在第二多个胞元行中。 在一个实施例中,一种集成电路结构包括:第一多个胞元行,在第一方向上延伸;以及第二多个胞元行,在第一方向上延伸。第一多个胞元行中的每一者具有第一行高度且包括设置在其中的多个第一胞元。第二多个胞元行中的每一者具有与第一行高度不同的第二行高度且包括设置在其中的多个第二胞元。所述多个第一胞元包括第一多个有源区,第一多个有源区中的每一者在第一方向上连续地延伸跨越所述多个第一胞元。所述多个第二胞元包括第二多个有源区,第二多个有源区中的每一者在第一方向上连续地延伸跨越所述多个第二胞元。第一多个有源区及第二多个有源区中的至少一个有源区具有沿着第一方向变化的宽度。在一实施例中,其中所述至少一个有源区的所述宽度在胞元内沿着所述第一方向改变。在一实施例中,其中所述至少一个有源区的所述宽度沿着所述第一方向跨越两个相邻胞元而改变。在一实施例中,其中所述第一多个有源区中的每一者具有沿着所述第一方向在第一最小宽度与第一最大宽度之间变化的第一宽度,并且所述第二多个有源区中的每一者具有沿着所述第一方向在第二最小宽度与第二最大宽度之间变化的第二宽度。在一实施例中,其中所述第一最小宽度及所述第一最大宽度与所述第一行高度相关联,并且所述第二最小宽度及所述第二最大宽度与所述第二行高度相关联。在一实施例中,其中所述第一最小宽度与所述第二最小宽度不同,并且所述第一最大宽度与所述第二最大宽度不同。在一实施例中,其中根据所述第一多个胞元行的数目与所述第二多个胞元行的数目之间的比率,所述第一多个胞元行与所述第二多个胞元行沿着与所述第一方向垂直的第二方向混合。在一实施例中,其中所述比率是以下中的一者:1/2、1/3、1/4、2/3、3/2、2/1、3/1、4/1及1/1。在一实施例中,其中所述多个第一胞元中的第一胞元与所述多个第二胞元中的第二胞元沿着与所述第一方向垂直的第二方向彼此相邻,并且所述第一胞元与所述第二胞元一起形成合并式胞元,所述合并式胞元所具有的胞元高度等于所述第一行高度与所述第二行高度的和。在一实施例中,其中所述合并式胞元具有沿着所述第二方向延伸跨越所述第一胞元及所述第二胞元的合并式有源区,并且所述合并式有源区具有沿所述第一方向变化的宽度。 在不同的实施例中,一种集成电路结构包括:第一多个胞元行,在第一方向上延伸;以及第二多个胞元行,在第一方向上延伸。第一多个胞元行中的每一者具有第一行高度且包括设置在其中的多个第一胞元。第二多个胞元行中的每一者具有与第一行高度不同的第二行高度且包括设置在其中的多个第二胞元。所述多个第一胞元中的每一者包括多个有源区,所述多个有源区中的每一者沿着第一方向以固定宽度延伸。所述多个第二胞元中的每一者包括多个有源区,所述多个有源区中的每一者沿着第一方向以固定宽度延伸。在第一多个胞元行及第二多个胞元行中的至少一个胞元行中,有源区数量沿着第一方向变化。在一实施例中,其中所述有源区数量在胞元内沿着所述第一方向改变。在一实施例中,其中所述有源区数量沿着所述第一方向跨越两个相邻胞元而改变。在一实施例中,其中所述多个第一胞元具有数量沿着所述第一方向在第一最小数量与第一最大数量之间变化的有源区,并且所述多个第二胞元具有数量沿着所述第一方向在第二最小数量与第二最大数量之间变化的有源区。在一实施例中,其中所述第一最小数量及所述第一最大数量与所述第一行高度相关联。所述第二最小数量及所述第二最大数量与所述第二行高度相关联。所述第一最小数量与所述第二最小数量不同,并且所述第一最大数量与所述第二最大数量不同。在一实施例中,其中所述多个第一胞元及所述多个第二胞元的每一有源区包括具有鳍形结构的区。在一实施例中,其中所述多个第一胞元中的第一胞元与所述多个第二胞元中的第二胞元沿着与所述第一方向垂直的第二方向彼此相邻,并且所述第一胞元与所述第二胞元一起形成合并式胞元,所述合并式胞元所具有的胞元高度等于所述第一行高度与所述第二行高度的和。 在另一个实施例中,一种集成电路设计系统包括:非暂时性存储介质,被用指令集进行编码;以及硬件处理器,与非暂时性存储介质通信耦合,且被配置成执行所述指令集,所述指令集被配置成使硬件处理器:提供包括多个第一胞元的第一库,所述多个第一胞元各自具有第一胞元高度且包括沿着第一方向连续地延伸的多个有源区;提供包括多个第二胞元的第二库,所述多个第二胞元各自具有第二胞元高度且包括沿着第一方向连续地延伸的多个有源区,其中第二胞元高度与第一胞元高度不同;从第一库检索所述多个第一胞元的第一子集及从第二库检索所述多个第二胞元的第二子集;以及将沿着第一方向延伸的所述多个第一胞元的第一子集放置在第一多个胞元行中,且将沿着第一方向延伸的所述多个第二胞元的第二子集放置在第二多个胞元行中。在第一多个胞元行及第二多个胞元行中的至少一个胞元行中,有源区数量沿着第一方向变化。在一实施例中,其中在所述第一多个胞元行及所述第二多个胞元行中的每一胞元行中,所述有源区数量沿着所述第一方向变化。在一实施例中,其中所述指令集被配置成进一步使所述硬件处理器:基于所述集成电路的性能要求,确定沿着与所述第一方向垂直的第二方向布置的所述第一多个胞元行的数目与所述第二多个胞元行的数目之间的比率,以及基于所述比率,沿着所述第二方向放置所述第一多个胞元行及所述第二多个胞元行,以形成集成电路的布局。 以上概述了若干实施例的特征,以使所属领域中的普通技术人员可更好地理解本发明的各个方面。所属领域中的技术人员应理解,他们可容易地使用本发明作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,此种等效构造并不背离本发明的精神及范围,且在不背离本发明的精神及范围的情况下,他们可对其进行各种改变、代替及变更。

- 集成电路结构和形成集成电路结构的方法

- 电源开关电路与其集成电路结构以及集成电路结构形成方法