一种用于封装基板的同侧电性测量方法及一种封装基板

文献发布时间:2023-06-19 13:49:36

技术领域

本发明有关于一种用于封装基板的电性测量技术,特别是指一种封装基板以及用于封装基板的同侧电性测量方法。

背景技术

现有的半导体制程中,扇出式晶圆封装(fan-out wafer level package,FOPLP)被认为是具有成本效益的下一代高集成封装IC技术。图1A为一现有扇出式晶圆封装的封装基板10,其包括载板11、再分布层(redistribution layer,RDL)13。再分布层13具有一个或多个叠合的介电层14、15,每一介电层14、15具有多个导电通孔16、17。该等多个导电通孔16、17上覆盖着导电图案18、19,因而形成多层的再分布电路,以连接不同介电层的导电图案。参考图1A与图1B,封装基板10接着与芯片20接合,再涂布封装材料30,以完成芯片20的封装,如图1B所示。

如上所述,如果要知道封装基板10是否为良品,必须在封装基板10与芯片20接合之后才能进行电性测量。如此一来,一旦封装基板10的再分布电路不正常工作时,必须连同已经接合的芯片20一起报废,损失甚大。

因此,如何能够在封装基板10与芯片20接合之前即对于封装基板10的再分布电路进行检测的技术,以减少芯片20因为封装基板10的故障而一起报废的风险,进而提升封装芯片的良率,已成为电子封装产业与其相关电子产业的重要研发课题之一。

发明内容

有鉴于此,本发明提供一种用于封装基板的电性测量技术,藉由导电粘着层的使用,可以实现一种封装基板以及用于封装基板的同侧电性测量方法。

为达上述目的,于一实施例中,本发明提出一种用于封装基板的同侧电性测量方法,包括以下步骤:提供载板;涂布导电粘着层于载板上;形成再分布层,通过导电粘着层而粘合于载板上,再分布层具有一个或多个叠合的介电层,每一介电层具有多个导电通孔,多个导电通孔上覆盖着导电图案,因而形成多层的再分布电路,以连接不同介电层的导电图案;以及在再分布层上提供一对电极性相反的测量探针,以测量再分布层的同侧上的任两个导电通孔之间的电阻值,以判断同侧上任两个导电通孔之间的导通性。

于一实施例中,载板由玻璃、塑胶、印刷电路板或其他介电材料所形成。

于一实施例中,多个导电通孔与多个导电图案由沉积制程、微影制程与刻蚀制程而形成。

于一实施例中,导电粘着层可剥离,以将再分布层与载板分离。

于一实施例中,用于封装基板的同侧电性测量方法,更包括以下步骤:移除导电粘着层与载板;以及在再分布层上提供一对电极性相反的测量探针,以测量再分布层的同侧上的任两个导电通孔之间的电阻值,以判断同侧上任两个导电通孔之间的绝缘性。

于另一实施例中,本发明提出一种封装基板,包括:载板;导电粘着层,涂布于载板上;以及再分布层,通过导电粘着层而粘合于载板上,再分布层具有一个或多个叠合的介电层,每一介电层具有多个导电通孔,多个导电通孔上覆盖着导电图案,因而形成多层的再分布电路,以连接不同介电层的导电图案。

综合上述,本发明提供一种用于封装基板的电性测量技术,藉由导电粘着层的使用,可以实现一种封装基板以及用于封装基板的同侧电性测量方法,进而在封装基板与芯片接合之前即对于封装基板的再分布电路进行检测,以减少芯片因为封装基板的故障而一起报废的风险,并且提升封装芯片的良率。

附图说明

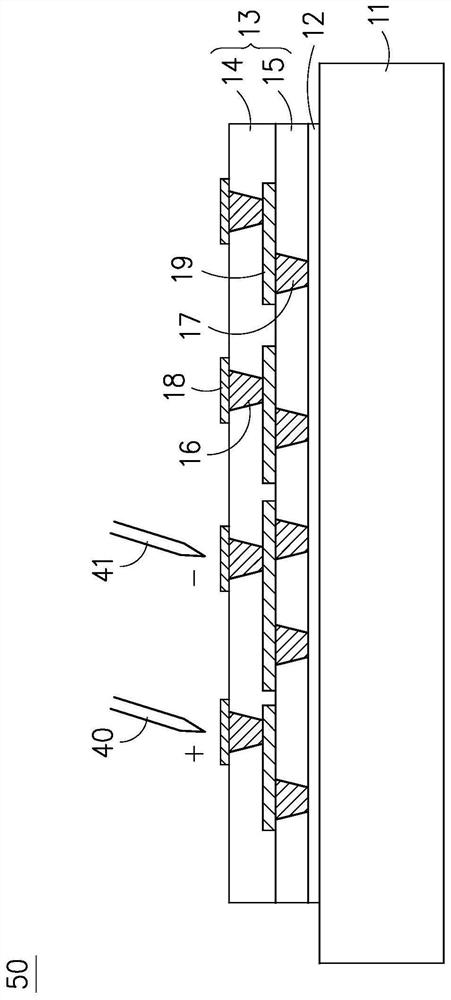

图1A是现有封装基板的横截面示意图;

图1B是现有已完成封装的芯片的横截面示意图;

图2A是本发明封装基板的横截面示意图以及进行同侧电性测量的实施例;以及

图2B是本发明封装基板的横截面示意图以及进行同侧电性测量的另一实施例。

附图标记列表:10、50、60-封装基板;11-载板;12-导电粘着层;13-再分布层;14、15-介电层;16、17-导电通孔;18、19-导电图案;20-芯片;30-封装材料;40、41-测量探针。

具体实施方式

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

请配合参考图2A,其显示本发明封装基板50的横截面示意图以及进行同侧电性测量的实施例。在图2A中,首先提供载板11。接着,涂布导电粘着层12于载板11上。之后,形成再分布层13,其通过导电粘着层12而粘合于载板11上。再分布层13具有一个或多个叠合的介电层14、15。于一实施例中,可以使用两层介电层14、15。然而,本发明的范围并不受限于叠合的介电层的数目。于一实施例中,每一介电层具有多个导电通孔16、17,其上方覆盖着导电图案18、19,因而形成多层的再分布电路,以通过导电通孔16、17连接不同介电层14、15的导电图案18、19。接着,在再分布层13上提供一对电极性相反的测量探针40、41。藉由导电粘着层12的导电特性,可以测量再分布层的同侧上的任两个导电通孔之间的电阻值,以判断同侧上任两个导电通孔16之间的导通性。

于一实施例中,载板11由玻璃、塑胶、印刷电路板或其他介电材料所形成。于一实施例中,介电层14、15由沉积制程、微影制程与刻蚀制程而形成。详而言之,在介电层14形成后,形成多个开口,再利用导电材料的沉积与研磨,形成多个导电通孔16,其上方再接着形成导电图案18。同理,在以沉积制程形成介电层15后,形成多个开口,再利用导电材料的沉积与研磨,形成多个导电通孔17,其上方再接着形成导电图案19。

简言之,多个导电通孔16、17与多个导电图案18、19由沉积制程、微影制程与刻蚀制程而形成。上述相关的半导体制程已为本技术领域中的人士所知悉,其详细制程在此不予赘述。

于一实施例中,导电粘着层12可剥离,以将再分布层13与载板11分离。基于上述特性,请配合参考图2B,其显示本发明封装基板60的横截面示意图以及进行同侧电性测量的另一实施例。于一实施例中,可以从封装基板60中移除导电粘着层12与载板11。接着,在再分布层13上提供一对电极性相反的测量探针40、41,以测量再分布层的同侧上的任两个导电通孔之间的电阻值。由于此时已经没有导电粘着层12来传导另一侧的电流,可以藉以判断同侧上任两个导电通孔16之间的绝缘性。

因此,于另一实施例中,请配合参考图2A,本发明提出一种封装基板50,包括载板11;导电粘着层12,涂布于载板11上;以及再分布层13,通过导电粘着层12而粘合于载板11上,再分布层具有一个或多个叠合的介电层14、15,每一介电层14、15具有多个导电通孔16、17,上方上覆盖着导电图案18、19,因而形成多层的再分布电路,以连接不同介电层的导电图案。藉由导电粘着层12的导电特性,可以在再分布层13上提供一对电极性相反的测量探针40、41,以测量再分布层的同侧上的任两个导电通孔16之间的电阻值,进而判断同侧上任两个导电通孔16之间的导通性。

于一实施例中,导电粘着层12可剥离,以将再分布层13与载板11分离,而形成图2B所示的封装基板60。由于此时已经没有导电粘着层12来传导另一侧的电流,可以在再分布层13上提供一对电极性相反的测量探针40、41,以测量再分布层的同侧上的任两个导电通孔16之间的电阻值,进而判断同侧上任两个导电通孔16之间的绝缘性。

综合上述,本发明提供一种用于封装基板的电性测量技术,藉由导电粘着层的使用,可以实现一种封装基板以及用于封装基板的同侧电性测量方法,进而在封装基板与芯片接合之前即对于封装基板的再分布电路进行检测,以减少芯片因为封装基板的故障而一起报废的风险,并且提升封装芯片的良率。

虽然本发明的技术内容已经以较佳实施例揭露如上,然其并非用以限定本发明,任何熟习此技艺者,在不脱离本发明的精神所作些许的更动与润饰,皆应涵盖于本发明的范畴内,因此本发明的保护范围当视后附的申请专利范围所界定者为准。