一种基于SAR逻辑消除寄生的电容数字转换器

文献发布时间:2023-06-19 09:24:30

技术领域

本发明涉及一种电容数字转换器,尤其涉及一种基于SAR逻辑消除寄生的电容数字转换器。

背景技术

电容数字转换器具有体积小、重量轻、功耗低、等优点。随着电容数字转换器的日益发展,其测量精度、可靠性等方面性能不断提升,在生物医疗和近程传感上以及触摸屏上均有着广泛应用。而随着检测环境的更加复杂以及更快的转换速度要求,因此,电容数字转换器需要有高分辨率、高寄生容忍度、高线性度、抗环境干扰等特点。

在单片集成系统中,传统的电容数字转换方案中,通过对电容进行充放电,采用电荷放大器,将电容值转换为电压值,再采用A/D转换器将模拟电压量转换为数字量输出。上述方案存在以下问题:由于工艺尺寸不断缩小,电压阈上的限制使得检测范围受到限制,动态范围缩小;工艺尺寸的缩小使得电路对寄生更加敏感,影响转换精度,不适用于复杂,高寄生的检测环境;电荷放大器会由于开关的不理想导致电荷泄漏,降低检测精度。上述各因素均会降低电容数字转换器整体的性能。

发明内容

本发明目的在于提供一种基于SAR逻辑消除寄生的电容数字转换器,以克服传统ADC电容数字转换器的线性度以及动态范围受限问题,同时通过SAR逻辑消除高寄生电容对电容检测精度的影响,提高电容数字转换器的抗干扰能力。

本发明所述的一种基于SAR逻辑消除寄生的电容数字转换器,第一放电电流源串接开关K2后与被测电容Cx、寄生电容Cpara并联在第一高速比较器的负端与地之间,参考电平V

寄生补偿电流源阵列和第二放电电流源并联后一端接地,另一端串接开关K4后连接第二高速比较器负端;所述参考电平V

参考电平V

所述鉴相器通过SAR控制逻辑模块对所述寄生补偿电流源阵列输出控制信号,SAR控制逻辑模块对所述预处理逻辑模块输出使能信号,所述预处理逻辑模块通过时间数字转换器对外输出校正后的时间数字信号。

所述的预处理逻辑模块包括两个与门、两延时链、两选择器和一裁决器;所述使能信号同时输入两个与门,所述输出端STO连接一与门后分别连接延时链Buffer1的输入端和裁决器的一输入端,所述输出端STA连接另一与门后分别连接延时链Buffer2的输入端和裁决器的另一输入端;裁决器输出端的同相信号输入选择器MUX1的选通输入端,反相信号输入选择器MUX2的选通输入端;延时链Buffer1的输出端分别输入两延时链的一输入端,延时链Buffer2的输出端分别输入两延时链的另一输入端;选择器MUX1对所述时间数字转换器输出领先信号,选择器MUX2对所述时间数字转换器输出滞后信号。

所述时间数字转换器为二级式结构,包括依次电性连接的计数器TDC、残差提取模块和游标型TDC;所述计数器TDC作为第一级量化电路,对输入信号进行粗量化,输出为时间数字信号的高位数据;残差提取模块和游标型TDC作为第二级量化电路,对第一级量化电路的残差进行细量化,输出为时间数字信号的低位数据。

本发明所述的一种基于SAR逻辑消除寄生的电容数字转换器,其优点在于,利用寄生补偿电流源阵列逐周期补偿,可消除测量通道的寄生电容影响。通过实现电容变化到连续时间的转换,克服传统C/V结构的限制,提高了电容检测范围。采用两级TDC量化结构,克服电容检测范围和检测精度的矛盾,实现高动态范围、高精度电容检测。除前端C-T转换的电路之外,其他电路均为数字电路,面积,功耗得到优化。因此,本发明可以广泛应用于复杂环境下电容检测和传感,适用于高度集成的传感电路。

附图说明

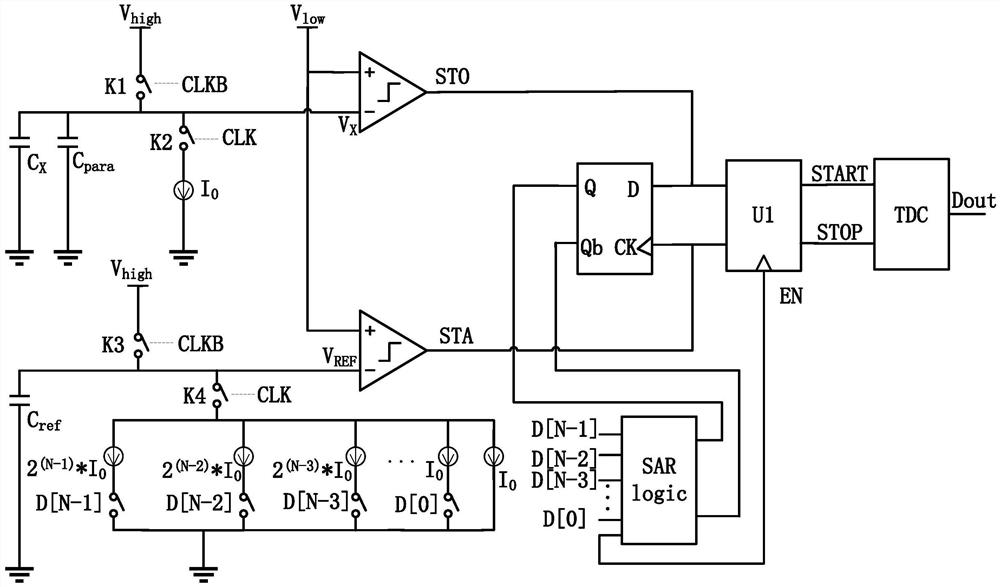

图1是本发明所述基于SAR逻辑消除寄生的电容数字转换器的结构示意图;

图2为本发明的SAR逻辑消除寄生时序图;

图3为本发明的预处理逻辑电路框图;

图4为本发明的TDC电路原理框图。

具体实施方式

如图1所示,本发明所述的一种基于SAR逻辑消除寄生的电容数字转换器包括依次电性连接的前端C-T转换电路,鉴相器、寄生电容消除电路、预处理逻辑模块U1和时间数字转换器。

所述前端C-T转换电路主要包括两个电容充放电通道;第一通道充放电结构包括被被测电容Cx、寄生电容Cpara、开关K1、开关K2、第一放电电流源和第一高速比较器。被测电容Cx和寄生电容Cpara负端接地,正端连接到开关K1和开关K2漏端以及第一高速比较器负端,开关K1源端连接到参考电平V

所述鉴相器内置一个D触发器,其数据输入端连接第一高速比较器的输出端STO,时钟输入端连接第二高速比较器的输出端STA,D触发器的输出端与SAR控制逻辑模块相连。

所述寄生电容消除电路包括SAR控制逻辑模块和寄生补偿电流源阵列,SAR控制逻辑模块根据鉴相器的输出逐周期输出N bit的控制信号和1bit使能信号,控制信号与寄生补偿电流源阵列的控制开关相连,使能信号与预处理逻辑模块U1相连。所述寄生补偿电流源阵列包括N个二进制电流源和N个控制开关,由SAR逻辑模块控制逐个周期控制导通和关断。二进制电流源与控制开关一一对应串联,串联后并入开关K4源极和地之间。

如图3所示,所述预处理逻辑模块U1包括两与门、延时链Buffer1、延时链Buffer2、裁决器、选择器MUX1和选择器MUX2。所述使能信号同时输入两个与门,所述输出端STO连接一与门后分别连接延时链Buffer1的输入端和裁决器的一输入端,所述输出端STA连接另一与门后分别连接延时链Buffer2的输入端和裁决器的另一输入端;裁决器输出端的同相信号输入选择器MUX1的选通输入端,反相信号输入选择器MUX2的选通输入端;延时链Buffer1的输出端分别输入两延时链的一输入端,延时链Buffer2的输出端分别输入两延时链的另一输入端;选择器MUX1对所述时间数字转换器输出领先信号,选择器MUX2对所述时间数字转换器输出滞后信号。

如图4所示,所述时间数字转换器包括两级量化电路。包括依次电性连接的计数器TDC、残差提取模块和游标型TDC。所述计数器TDC作为第一级量化电路,对输入信号进行粗量化,输出Dout[m-1]到Dout[m-k]共k位数字输出,输出为时间数字信号的高位数据。残差提取模块和游标型TDC作为第二级量化电路,对第一级量化电路的残差进行细量化,输出Dout[m-k-1]到Dout[0]共m-k位数字输出,实现时间数字的m位量化,输出为时间数字信号的低位数据。

本发明所述基于SAR逻辑消除寄生的电容数字转换器用于复杂环境下电容检测,工作原理如下:

所述前端C-T转化电路用于电容读出,将检测电容转换为连续时间量,并输出到所述鉴相器电路以及预处理逻辑模块U1。所述鉴相器电路将连续时间差信号转换成数字控制信号,并发送到所述寄生电容消除电路。所述寄生电容消除电路通过SAR控制逻辑前端C-T电路消除寄生,形成闭环。所述的预处理逻辑模块U1判断校准后的前端C-T转换电路输出信号的正负,裁决领先和滞后信号,输出到所述时间数字转换器。所述时间数字转换器将时间差信号转换成能够反映时间差的数字信号。

如图2所示,校准阶段共N个周期,在第n个时钟周期对寄生电容Cpara和参考电容Cref充放电,充电电压V

综上所述,本发明基于SAR逻辑、两级TDC结构,对校准和测量分阶段进行,实现具有线性度高、面积小、抗干扰能力强、检测动态范围大等优点。同时,电容检测采用差分输入结构,且相同基准电压源进行电容充放电,具有较高的PVT鲁棒性;SAR控制逻辑和TDC可复用时钟。

对于本领域的技术人员来说,可根据以上描述的技术方案以及构思,做出其它各种相应的改变以及形变,而所有的这些改变以及形变都应该属于本发明权利要求的保护范围之内。

- 一种基于SAR逻辑消除寄生的电容数字转换器

- 一种消除超快速半导体元器件测试中寄生电容影响的方法