在SOI平台上光子部件的集成

文献发布时间:2023-06-19 09:30:39

本申请要求2018年5月15日提交的美国申请62/671830的优先权,所述申请的内容和要素出于所有目的以引用的方式并入本文。

发明领域

本发明涉及使用缓冲区域在SOI平台上集成光子部件,并且具体地(但不排他地)涉及将利用III-V族材料的部件集成到SOI衬底上。

背景技术

由III-V族材料形成的电吸收调制器(III-V族EAM)用于在光学系统中调制光。

绝缘体上硅(SOI)晶片可用作可在上面形成光学部件和/或电路的衬底。然而,由于Si与III-V族材料之间的晶格失配,III-V族EAM在SOI衬底上的单片集成一直未成功。

鉴于以上考虑,设计了本发明。

发明内容

在第一方面中,本发明可提供一种光电有源器件,所述光电有源器件包括:绝缘体上硅(SOI)衬底,所述SOI衬底包括硅基底层、在所述硅基底层的顶部上的掩埋氧化物(BOX)层、在所述BOX层的顶部上的SOI层和衬底空腔,所述衬底空腔延伸穿过所述SOI层、所述BOX层并延伸到所述硅基底层中,使得所述衬底空腔的基部由所述硅基底层的一部分形成;光电有源波导,所述光电有源波导包括在所述衬底空腔内的光电有源堆叠体;以及缓冲区域,所述缓冲区域在所述衬底空腔内处于所述光电有源波导下方,所述缓冲区域包括Ge层和GaAs层。

由于所述缓冲区域修改了在上面形成有所述波导的晶格结构,因此所述缓冲区域允许所述光电有源波导与所述SOI衬底的更好的集成。这个具有所述缓冲区域的器件可用作可在上面形成光电有源和/或无源波导的模板。

所述缓冲区域可包括渐变InAlAs层。所述缓冲区域可包括InGaAs或InP层。所述缓冲区域可包括:InGaAs或InP层,所述层位于渐变InAlAs层的顶部上,所述渐变InAlAs层位于GaAs层的顶部上,所述GaAs层位于Ge层的顶部上。

所述Ge层可具有1000nm+/-20%的厚度,并且/或者GaAs层可具有1000nm+/-20%的厚度,并且/或者渐变InAlAs层可具有1300nm+/-30%的厚度,并且/或者InGaAs或InP层可具有500nm至1000nm的厚度。

所述缓冲区域可由本征或非故意掺杂(uid)材料组成。所述缓冲区域可外延生长到所述衬底空腔的所述基部上。所述缓冲区域在所述衬底空腔的所述基部上的外延生长改进了所述缓冲区域与所述硅基底层在所述衬底空腔的所述基部处的集成。已外延生长出的层鉴于所形成的结构可能能够通过显微镜和/或SEM来检测。

所述光电有源堆叠体可直接位于所述缓冲区域的顶部上。所述光电有源堆叠体可外延生长在所述缓冲区域上。所述光电有源堆叠体在所述缓冲区域上的外延生长改进了所述堆叠体与所述缓冲区域的集成。

所述光电有源堆叠体与所述缓冲区域之间的界面可在所述衬底空腔中定位在比所述SOI衬底中的所述硅基底层与所述BOX层之间的界面更深之处,使得所述光电有源堆叠体的一部分可定位在与所述硅基底层的一部分相同的高度处。

所述光电有源堆叠体可包括III-V族半导体层。由于存在所述缓冲区域,因此III-V族半导体可与所述SOI单片地集成。所述堆叠体可为III-V族EPI堆叠体,并且所述III-V族EPI堆叠体可包括MQW和/或本体III-V族材料。

所述光电有源堆叠体可包括多量子阱区域。

所述光电有源堆叠体可形成电吸收调制器(EAM)。所述EAM可为III-V族EAM,并且/或者所述EAM可包括利用量子限制斯塔克效应(QCSE)和/或弗朗兹-凯尔迪什(FK)效应的器件。所述光电有源波导可被配置为使得所述光电有源波导的光学性质能够根据QCSE效应或FK效应来修改。

所述光电有源器件可包括在所述光电有源堆叠体与所述衬底空腔的侧壁之间的通道;其中所述通道可用衬里和填充材料填充,所述衬里和所述填充材料具有类似于或大于形成所述衬底空腔的侧壁的材料的折射率的折射率,从而在所述通道中在所述SOI层与所述光电有源堆叠体之间形成桥波导。所述填充材料可为非晶硅或硅锗(SiGe),并且所述衬里可由氮化硅(Si

所述光电有源堆叠体的顶表面可定位在比所述SOI层的顶表面更高之处,使得所述光电有源堆叠体的一部分从所述衬底空腔突出。

所述光电有源器件可包括在所述SOI层的顶部上的氮化硅(Si

所述光电有源器件可包括:在第一掺杂区域上的第一电极接触件,所述第一掺杂区域形成所述光电有源堆叠体的最下层;在所述第一掺杂区域中的隔离空腔;绝缘材料,所述绝缘材料位于所述光电有源堆叠体的侧表面上并且延伸到所述第一掺杂区域中的所述隔离空腔中并为所述隔离空腔加衬里;以及在第二掺杂区域上的第二电极接触件,所述第二掺杂区域形成所述光电有源堆叠体的顶层,所述接触件从所述第二掺杂区域沿着所述绝缘材料延伸并延伸到所述第一掺杂区域中的所述隔离空腔中。

所述光电有源器件的组成和所述层的性质和/或高度可能能够使用光学显微镜和/或SEM来检测。

在第二方面中,本发明可提供一种产生光电有源器件的方法,所述方法包括以下步骤:提供绝缘体上硅(SOI)衬底,所述SOI衬底包括硅基底层、在所述硅基底层的顶部上的掩埋氧化物(BOX)层和在所述BOX层的顶部上的绝缘体上硅(SOI)层;在所述绝缘体上硅(SOI)衬底的一部分中穿过所述SOI层,穿过所述BOX层蚀刻衬底空腔并且蚀刻到所述硅基底层中;在所述衬底空腔内形成缓冲区域,形成缓冲区域的步骤包括外延生长Ge层并且外延生长GaAs层;在所述衬底空腔内并在所述缓冲区域的顶部上外延生长光电有源堆叠体;蚀刻所述光电有源堆叠体以形成光电有源波导;以及蚀刻所述SOI衬底以形成SOI波导,所述SOI波导被配置为引导光波通过所述光电有源波导。

在所述衬底空腔内形成缓冲区域的步骤可包括外延生长渐变InAlAs层。在所述衬底空腔内形成缓冲区域的步骤可包括外延生长InGaAs或InP层。

在所述衬底空腔内形成缓冲区域的步骤可包括:在所述硅基底层的形成所述衬底空腔的基部的一部分上外延生长Ge层;接着在所述Ge层上外延生长GaAs层;接着在所述GaAs层上外延生长渐变InAlAs层;接着在所述渐变InAlAs层上外延生长InGaAs或InP层。

所述光电有源堆叠体与所述缓冲区域之间的界面可在所述衬底空腔中定位在比所述SOI衬底中的所述硅基底层与所述BOX层之间的界面更深之处,使得所述光电有源堆叠体的一部分定位在与所述硅基底层的一部分相同的高度处。

所述方法可包括以下步骤:在蚀刻所述衬底空腔之前,将氮化硅层沉积在所述SOI衬底上,使得所述氮化硅的顶表面在所述SOI衬底上方具有第一高度,其中在生长出所述光电有源堆叠体之后,所述光电有源堆叠体的一部分从所述衬底空腔突出等于所述第一高度的高度,使得所述氮化硅层的所述顶表面与所述光电有源堆叠体的顶表面对准。

所述方法可包括在外延生长所述缓冲区域之前将氮化硅沉积在所述衬底空腔的侧壁上。

所述外延生长的光电有源堆叠体在与所述衬底空腔的侧壁相邻的区域中可具有刻面;并且所述方法可包括以下步骤:蚀刻所述区域,从而去除所述刻面并且在所述侧壁与所述堆叠体之间产生通道;以及用填充材料填充所述通道,所述填充材料具有类似于或大于形成所述侧壁的材料的折射率的折射率,使得所述填充材料在所述通道中在所述SOI波导与所述光电有源堆叠体之间形成桥波导。

所述外延生长的光电有源堆叠体在与所述衬底空腔的侧壁相邻的区域中可具有刻面;并且所述方法可包括以下步骤:蚀刻所述区域,从而去除所述刻面并且在所述侧壁与所述堆叠体之间产生通道;用衬里为所述通道加衬里以提供带衬里的通道;以及用填充材料填充所述带衬里的通道,所述填充材料具有类似于形成所述侧壁的材料的折射率的折射率,使得所述填充材料在所述通道中在所述SOI波导与所述光电有源堆叠体之间形成桥波导。

所述衬里可由氮化硅形成。所述填充材料可为非晶硅或硅锗(SiGe)。

蚀刻所述区域,从而去除所述刻面并且在所述侧壁与所述堆叠体之间产生所述通道的步骤可包括以下任一者:穿过所述光电有源堆叠体蚀刻并且蚀刻到所述缓冲区域中,使得所述通道的基部由所述缓冲区域的一部分形成;或者蚀刻到所述光电有源堆叠体中,使得所述通道的基部由所述光电有源堆叠体的一部分形成。

蚀刻所述区域,从而去除所述刻面并且在所述侧壁与所述堆叠体之间产生所述通道的步骤可包括:蚀刻到比所述SOI衬底中的所述硅基底层与所述BOX层之间的界面更低的位置,使得在所述通道的基部处的所述衬里的顶表面处于与所述BOX层的顶表面相同的高度。

所述方法可包括以下步骤:将第一电极接触件沉积在第一掺杂区域上,所述第一掺杂区域形成所述光电有源堆叠体的底层;在所述第一掺杂区域中蚀刻隔离空腔;将绝缘材料沉积在所述光电有源堆叠体的侧表面上以及所述第一掺杂区域中的所述隔离空腔中,以便为所述隔离空腔加衬里,从而将所述隔离空腔与所述光电有源堆叠体电隔离;以及将第二电极接触件沉积在第二掺杂区域上,所述第二掺杂区域形成所述光电有源堆叠体的顶层,所述接触件延伸到所述第一掺杂区域中的所述隔离空腔中。

所述方法可包括以下步骤:从所述SOI衬底上方并接近于所述空腔的区蚀刻非晶硅层,接着是以下步骤:对所述光电有源堆叠体上方的SiO

在本申请中,相对于作为器件的基部的衬底论述了部件和层的取向。层或波导的高度在远离硅基底层或远离衬底空腔的基部的方向上进行测量。层或波导的顶表面是最远离硅基底层或衬底空腔的基部的表面,并且层或波导的底表面是最靠近硅基底层或衬底空腔的底部的表面。例如,在垂直于硅基底层与BOX层之间的界面的方向上从SOI层的底表面到SOI层的顶表面测量SOI层的高度。术语在……下方表示更靠近硅基底层或衬底空腔的基部。衬底空腔的深度指代在与高度相反的方向上距衬底空腔的基部的距离。层在空腔内越处于深处,所述层越靠近衬底空腔基部。

堆叠体的顶部可具有大于SOI层的高度的高度,使得堆叠体可突出到衬底空腔的顶部上方。这种堆叠体仍被视为在空腔内,只要光电有源堆叠体的一部分处于硅基底层上方与SOI层相同的高度即可。以此方式,来自SOI层中的输入波导的光可进入光电有源堆叠体,并且光可离开堆叠体进入SOI层中的输出波导。

本发明包括所描述的方面和优选特征的组合,除非这种组合是明显不允许的或明确避免的。

附图说明

现将参考附图论述说明本发明的原理的实施方案和实验,在附图中:

图1示出了在Si衬底上的单片III-V族EAM的顶视图。

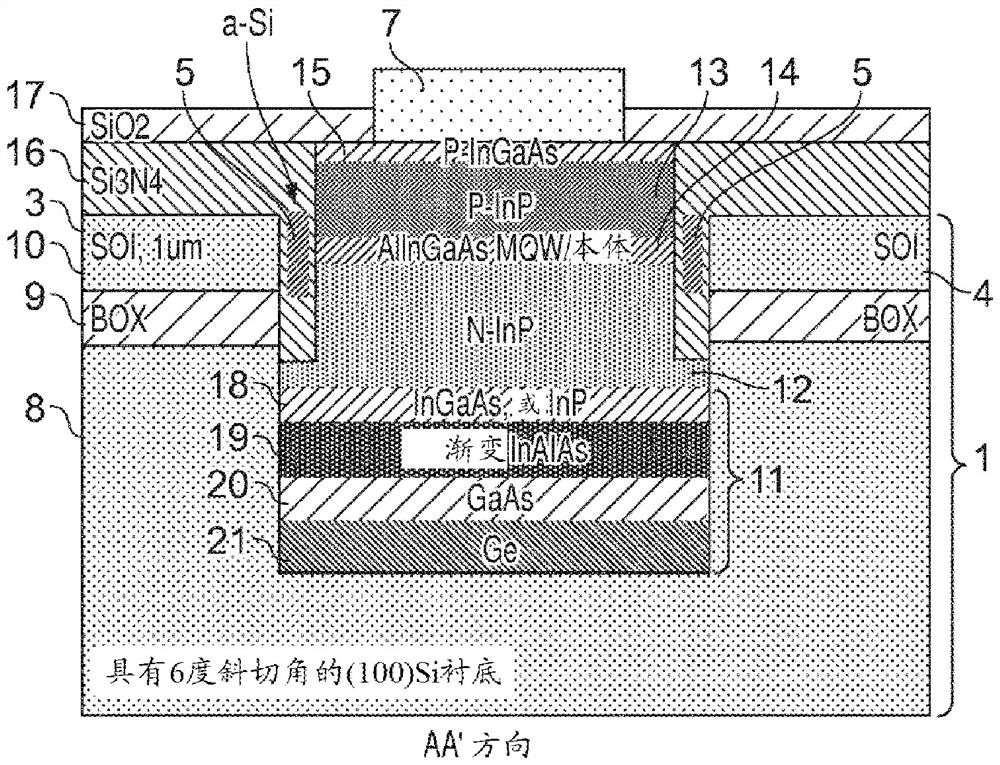

图2示出了图1的EAM的版本的截面图,EAM是在1μm SOI平台上的AlInGaAs MQW或本体InGaAsP EAM,截面图是沿着图1的线A-A’。

图3示出了沿着图1的线B-B’的图2的EAM的截面图。

图4示出了图1的EAM的版本的截面图,EAM是在1μm SOI平台上的InGaNAs MQWEAM,截面图是沿着图1的线A-A’。

图5示出了沿着图1的线B-B’的在1μm SOI平台上的InGaNAs MQW EAM的截面图。

图6示出了沿着图1的线C-C’的图1的EAM的截面图。

图7示出了沿着图1的线D-D’的图1的EAM的截面图。

图8A至图8V示出了制造EAM的方法中的步骤。

图9A至图9U示出了制造EAM的方法中的步骤。

具体实施方式

现将参照附图论述本发明的各方面和实施方案。其他方面和实施方案对于本领域技术人员而言将是显而易见的。在本文中提及的所有文档都以引用的方式并入本文。

图1中示出了SOI衬底1上的III-V族MQW/本体波导EAM 2的顶视图。输入SOI波导3为光进入EAM 2的波导提供路径,并且输出SOI波导4为光离开EAM 2提供路径。电极6和7为可使用来将偏压施加在EAM的整个光电有源堆叠体上以调制EAM中的光的电子器件提供连接。在输入波导3与EAM之间存在非晶硅区5,并且在EAM与输出波导4之间存在另一个非晶硅区5。区5形成填充材料,并且可提供在输入波导与输出波导之间的桥波导以及光电有源堆叠体。非晶硅区5被Si

图2和图3示出了图1所示的EAM的示例。EAM形成于包括硅基底层8、掩埋氧化物层9和SOI层10的SOI平台1上。图2所示的EAM是在SOI层10具有1 μm的高度的1 μm SOI平台上,但是在其他实施方案中,可使用其他平台大小和SOI层高度。硅基底层可为具有6度斜切角的(100)硅衬底。

衬底空腔延伸穿过SOI层10、穿过BOX层9并延伸到硅基底层8中。空腔的基部形成于硅基底层8中。

光电有源堆叠体形成于衬底空腔内。在此示例中,堆叠体由掺杂N的InP层12、AlInGaAs层14、掺杂P的InP层和掺杂P的InGaAs层15形成。AlInGaAs层14可为多量子阱层或主体层。堆叠体的顶部具有大于SOI层10的高度的高度,使得堆叠体突出到衬底空腔的顶部上方。可将其他层添加到堆叠体,可从堆叠体中省略一个或多个层并且/或者其他层可替换堆叠体中的一个或多个层。可对所述层重新排序。

P掺杂层和N掺杂层包围本征或uid AlInGaAs层14,从而在堆叠体中形成竖直PIN结。可将偏压施加在整个PIN结上以产生调制区域。

EAM还在光电有源波导下方具有缓冲区域11。缓冲区域11在此示例中由Ge层21、GaAs层20、渐变InAlAs层19和InGaAs或InP层18组成。InGaAs或InP层18是在渐变InAlAs层19的顶部上,渐变InAlAs层19是在GaAs层20的顶部上并且GaAs层20是在Ge层21的顶部上。可将其他层添加到缓冲区域,可从缓冲区域中省略一个或多个层并且/或者其他层可替换缓冲区域中的一个或多个层。可对所述层重新排序。

缓冲区域11是在衬底空腔的基部上。光电有源堆叠体是在缓冲区域11上。

掺杂N的InP层12是在缓冲区域11的顶部上,AlInGaAs层14是在掺杂N的InP层12的顶部上,掺杂P的InP层是在AlInGaAs层14的顶部上并且掺杂P的InGaAs层15是在掺杂P的InP层的顶部上。在其他实施方案中,可颠倒所述层,使得一个或多个P掺杂层定位在比AlInGaAs层14更低之处(更靠近衬底空腔的基部),并且一个或多个N掺杂层被定位在比AlInGaAs层14更高之处。在其他实施方案中,其他掺杂和未掺杂或非故意掺杂层可形成光电有源堆叠体。

电极6接触光电有源堆叠体的下部掺杂层,并且电极7接触光电有源堆叠体的上部掺杂层。因此,在图2和图3的实施方案中,电极6接触光电有源堆叠体的掺杂N的InP层12,并且电极7接触光电有源堆叠体的掺杂P的InGaAs层15。在其他实施方案中,电极6可接触P掺杂层,并且电极7可接触N掺杂层。

在SOI层10的顶部上存在Si

表1针对利用QCSE的MQW EAM示出了这个实施方案的层高度和组成的示例。含GaAsN和GaAs的额外层被包括在AlGaAs层与InGaNAs层之间。含GaAsN和GaAs的额外层还被包括在InGaNAs层与AlGaAs层之间。

在表2中针对利用FK效应用本体族材料实现的EAM示出了在此实施方案中使用的层的高度和组成的另一个示例。FK效应的使用优于QCSE的使用,因为FK效应与偏振无关。表2中的InGaAsP层可由如图2和图3所示的AlInGaAs,或者InGaNAs替换。所述示例在掺杂P的InP层与掺杂P的InGaAs层之间具有含InGaAsP的额外层。

在图4和图5中分别沿着图1的线A-A’和B-B’示出了另一个实施方案。除了缓冲区域11的组成和光电有源堆叠体的组成,这个实施方案与图2和图3所示的实施方案相同。

光电有源堆叠体由掺杂N的GaAs层22、掺杂N的AlGaAs层23、InGaNAs层24、掺杂P的AlGaAs层25和掺杂P的GaAs层26形成。掺杂P的GaAs层26是在掺杂P的AlGaAs层25的顶部上,掺杂P的AlGaAs层25是在InGaNAs层24的顶部上并且InGaNAs层24是在掺杂N的AlGaAs层23的顶部上。可将其他层添加到堆叠体,可从堆叠体中省略一个或多个层并且/或者其他层可替换堆叠体中的一个或多个层。可对所述层重新排序。InGaNAs层24可具有MQW结构。

P掺杂层和N掺杂层包围本征或uid InGaNAs层24,从而在堆叠体中形成竖直PIN结。可将偏压施加在整个PIN结上以产生调制区域。

光电有源堆叠体是在缓冲区域11的顶部上。

缓冲区域11由Ge层21和GaAs层20形成。Ge层21是在衬底空腔的基部上,并且GaAs层20是在Ge层上。可将其他层添加到缓冲区域,可从缓冲区域中省略一个或多个层并且/或者其他层可替换缓冲区域中的一个或多个层。可对所述层重新排序。

表3针对利用QCSE的MQW EAM示出了这个实施方案中的层的高度的示例。如由这个示例所显示,在本申请中论述的层可由在其掺杂剂含量方面可能有所不同的子层构成。例如,在表3中,InP层由各自具有不同的硅掺杂水平的三个子层(层6、7、8)形成。另外,如由这个示例所说明,额外层可被包括在堆叠体中和/或缓冲区域中。在表3的示例中,含InGaAsP的额外层也被包括在相应的InP层与AlInGaAs层之间。InGaAsP层还被添加在掺杂P的InP层与掺杂P的InGaAs层之间。n/u/p列描述了层的掺杂。表中uid的标记表示层可能是非故意掺杂的,并且虽然没有将掺杂剂主动施加到所述层,但是由于层的薄度和被掺杂的相邻层,可能存在一些残余掺杂。

图6示出了穿过图1的线C-C’的截面图并且示出了输入波导3。波导是形成于SOI层10中的肋形波导。Si

图7示出了穿过图1的线D-D’的截面图并且示出了非晶硅区5。在器件的这个区域中,Si

如图7所示的相同结构提供在光电有源堆叠体与输出波导之间,其中非晶硅的肋形波导与光电有源堆叠体和输出波导对准。

图2和图3所示的器件可如下文参考图8A至图8V所描述来形成。可使用类似方法来通过替代缓冲区域和堆叠体中的适当的层而形成图4和图5所示的实施方案。

将Si

如图8A所示,在衬底中蚀刻出衬底空腔28。空腔延伸穿过Si

然后,如图8B所示将20nm的Si

将多晶III-V族(聚合物)沉积在Si

将SiO

如图8F所示,之后将SiO

如图8H所示,之后将富含硅的Si

如图8I所示,然后沉积非晶硅来填充通道并且在Si

如图8K所示,接着使用CMP来去除SiO

然后蚀刻非晶硅,使得非晶硅的顶表面具有与SOI层10的顶表面相同的高度(参见图8L)。如图8M和图8N所示,之后沉积Si

然后沉积SiO

如图8Q所示通过穿过掺杂P的InGaAs层15、掺杂P的InP层13和AlInGaAs层14蚀刻沟槽来在堆叠体中形成肋形波导。沟槽还延伸到掺杂N的InP层12的上部部分中。肋形波导的脊由在所蚀刻的沟槽之间的堆叠体形成。在此步骤中并未蚀刻Si

如图8R中可见,然后将SiO

图8T示出了隔离空腔,所述隔离空腔穿过掺杂N的InP层蚀刻到InGaAs或InP层,使得顶部电极能够与下部N掺杂区域更好地隔离以减小寄生电容。隔离空腔衬有诸如SiO

如图8V所示,然后使用金属化来在接触点处形成电极6和7。

可根据以下方法参考图9A至图9U来形成3 μm SOI平台上的另一个实施方案。

衬底是SOI衬底,其中SOI层具有3 μm的高度。将SiO

然后,如图9B所示将20nm的Si

将聚合物沉积在Si

缓冲区域11在此实施方案中由在衬底空腔的基部上的Ge层21、在Ge层21上的GaAs层20、在GaAs层20上的渐变InAlAs层19和在渐变InAlAs层19上的InGaAs或InP层18组成。光电有源堆叠体包括下部InP层31、InGaAsP层33和上部InP层32。当沉积时,层可能是未掺杂的,并且可能会稍后在工艺中发生掺杂。InGaAsP层33的底表面可具有等于SOI层的底表面的高度的高度。

可将其他层添加到堆叠体/缓冲区域,可从堆叠体/缓冲区域中省略一个或多个层并且/或者其他层可替换堆叠体/缓冲区域中的一个或多个层。可对所述层重新排序。

将SiO

如图9F所示,之后将SiO

如图9H所示,之后将富含硅的Si

如图9I所示,然后沉积非晶硅来填充通道并且在Si

如图9K所示,接着使用CMP来去除SiO

然后使用光刻胶29来对SiO

如图9M所示通过穿过上部InP层32、InGaAsP层33和下部InP层31蚀刻沟槽来在堆叠体中形成肋形波导。沟槽还延伸到InGaAs或InP层18的上部部分中。肋形波导的脊由在所蚀刻的沟槽之间的堆叠体形成。同时,通过蚀刻SiO

之后将近似20-50nm厚度的SiO

之后用光刻胶覆盖暴露部分,并且在另一第二沟槽的基部、波导的脊上的第二沟槽的侧壁和脊形波导的顶表面的一部分上的SiO

去除在第一沟槽的基部上的SiO

去除在第二沟槽的基部上的SiO

掺杂步骤的次序可根据实践重新安排。

如图8S所示,然后将500nm的SiO

之后去除在N+区域和P+区域上方的SiO

在图9U中示出了所得的EAM器件。EAM形成于包括硅基底层8、掩埋氧化物层9和SOI层10的SOI平台1上。图9U所示的EAM是在SOI层10具有3 μm的高度的3 μm SOI平台上,但是在其他实施方案中,可使用其他平台大小。硅基底层可为具有6度斜切角的(100)硅衬底。

衬底空腔延伸穿过SOI层10、穿过BOX层9并延伸到硅基底层8中。空腔的基部形成于硅基底层8中。

光电有源堆叠体形成于衬底空腔内。堆叠体由下部InP层31、InGaAsP层33和上部InP层32形成。InGaAsP层33和上部InP层在一侧上是N掺杂的并且在相对侧上是P掺杂的(如图9U所示分别为左侧和右侧)。形成于堆叠体中的肋形波导的平板区域由下部InP层31和InGaAsP层33的一部分形成。平板在一侧的一部分上是N掺杂的,并且在相对侧的一部分上是P掺杂的(如图9U所示分别为左侧和右侧)。堆叠体的顶表面具有等于SOI层10的顶表面的高度的高度,使得堆叠体不会突出到衬底空腔的顶部上方。

在此实施方案中,在光电有源堆叠体的任一侧上在P掺杂区域与N掺杂区域之间水平地形成PIN结。

在光电有源堆叠体下方的缓冲区域11由在衬底空腔的基部上的Ge层21、在Ge层21上的GaAs层20、在GaAs层20上的渐变InAlAs层19和在渐变InAlAs层19上的InGaAs或InP层18组成。缓冲区域11是在衬底空腔的基部上。光电有源堆叠体是在缓冲区域11上。

可将其他层添加到堆叠体/缓冲区域,可从堆叠体/缓冲区域中省略一个或多个层并且/或者其他层可替换堆叠体/缓冲区域中的一个或多个层。可对所述层重新排序。

电极6接触光电有源堆叠体的平板的N+掺杂区域,并且电极7接触光电有源堆叠体的平板的P+掺杂区域。

像在上文描述的实施方案中那样,非晶硅区5是在输入波导3与光电有源堆叠体之间,并且在光电有源堆叠体与输出波导4之间。非晶硅区5被Si

在表4中针对利用FK效应用本体III-V族材料在3 μm SOI平台上实现的EAM示出了在此实施方案中使用的层的高度和组成的示例。InGaSaP层可由AlInGaAs层替换。

表1:具有InGaNAs MQW的EAM EPI堆叠体(QCSE)

表2:通过FK效应用本体III-V族材料实现的EAM EPI堆叠体

表3:具有AlInGaAs MQW的EAM EPI堆叠体(QCSE)

表4:通过FK效应用3 μm本体III-V族材料实现的EAM EPI堆叠体

在前文描述中,或所附权利要求中或附图中公开的以其特定形式或者在用于执行所公开的功能的装置、或者用于获得所公开的结果的方法或过程方面表述的特征在适当时可单独地或与此类特征的任何组合一起用于以多样化形式实现本发明。

虽然已结合上文描述的示例性实施方案描述了本发明,但是当给出本公开时,许多等同修改和变型对于本领域技术人员而言将是显而易见的。因此,上文阐述的本发明的示例性实施方案应被视为是说明性的而非限制性的。在不脱离本发明的精神和范围的情况下可对所描述的实施方案作出各种改变。

为了避免任何疑义,本文提供的任何理论解释是出于提高读者的理解的目的而提供的。发明人不希望受到这些理论解释中的任何解释的束缚。

本文使用的任何章节标题仅用于组织目的并且不应被解释为限制所描述的主题。

贯穿本说明书(包括所附的权利要求),除非上下文另外要求,否则词语“包含”和“包括”以及诸如“包含(comprises)”、“包含(comprising)”和“包括(including)”之类的变型将被理解为暗示包括所陈述的整数或步骤、或者整数或步骤组,但是并不排除任何其他整数或步骤、或者整数或步骤组。

必须注意,除非上下文另外明确指明,否则如在本说明书和所附权利要求中所使用的单数形式“一个/种(a/an)”和“所述”包括复数个提及物。范围在本文可被表述为从“约”一个特定值,和/或至“约”另一个特定值。当表述这种范围时,另一个实施方案包括从一个特定值和/或至另一个特定值。类似地,当通过使用先行词“约”将值表述为近似值时,将理解,特定值形成另一个实施方案。关于数值的术语“约”是任选的并且表示例如+/-10%。

- 在SOI平台上光子部件的集成

- 一种航空小尺寸部件渗透检测集成工作平台