半导体装置的制造方法

文献发布时间:2023-06-19 09:47:53

技术领域

本发明涉及半导体装置的制造方法。

背景技术

为了响应半导体装置的小型化和高性能化的要求,构成半导体装置的电极或者配线等的微细化得到促进。特别是在化合物半导体领域,为了有效利用材料所具有的优异的高频特性,强烈要求使栅电极变细。但是,由于通过使栅电极变细而电场集中于狭窄的区域,因此还存在以短沟道效应等为代表的微细化的弊端。作为解决该问题的手段之一,有效的是使栅电极靠近源电极侧来扩大与施加电压的漏电极之间的间隔的偏置栅极构造。

专利文献1:日本特开平11-126782号公报

在现有技术中分别形成了凹陷形成用的抗蚀剂和栅电极形成用的抗蚀剂的图案。但是,由于在第一次和第二次的图案化产生对准偏差,因此栅电极在凹陷内的位置产生偏差。因此,特性发生变动,制品的成品率降低。另外,由于需要两次的图案化,因此工序数增大,制造成本上升。

另外,还提出有以下方法,即,使用形成有大小两个开口的抗蚀剂来形成凹陷,用绝缘膜封堵其中的小开口,并经由其中的大开口在凹陷形成栅电极(例如,参照专利文献1)。但是,导致在干蚀刻绝缘膜时对栅电极正下方的半导体造成损伤。因此,载流子减少,缺陷和陷阱增加,因此存在可靠性降低的问题。

发明内容

本发明是为了解决上述那样的课题而完成的,其目的是获得一种能够提高制品的成品率和可靠性并能够减少制造成本的半导体装置的制造方法。

本发明所涉及的半导体装置的制造方法的特征在于,具备:在半导体基板之上涂覆抗蚀剂,并在上述抗蚀剂形成第1开口和宽度比上述第1开口窄的第2开口的工序;使用上述抗蚀剂作为掩膜来对上述半导体基板进行湿蚀刻而在上述第1开口和第2开口之下形成连续的一个凹陷的工序;在形成上述凹陷后,使收缩材料与上述抗蚀剂进行交联反应,而使得上述第1开口没有被封堵而上述第2开口被封堵的工序;以及在封堵上述第2开口后,经由上述第1开口在上述凹陷形成栅电极的工序。

在本发明中,对半导体基板进行湿蚀刻来在抗蚀剂的第1和第2开口之下形成连续的一个凹陷。接下来,使收缩材料与抗蚀剂进行交联反应来使抗蚀剂图案收缩,而使得宽度宽的第1开口没有被封堵,而宽度窄的第2开口完全被封堵。接下来,在第1开口的形成区域,在凹陷内形成栅电极。由此,栅电极在凹陷内的位置不发生偏差,因此制品的成品率提高。另外,对抗蚀剂进行图案化的工序数减少,从而能够减少制造成本。另外,也不会对栅电极正下方的半导体造成损伤,因此可靠性提高。

附图说明

图1是表示实施方式1所涉及的半导体装置的制造方法的剖视图。

图2是表示实施方式1所涉及的半导体装置的制造方法的剖视图。

图3是表示实施方式1所涉及的半导体装置的制造方法的剖视图。

图4是表示实施方式1所涉及的半导体装置的制造方法的剖视图。

图5是表示比较例所涉及的半导体装置的制造方法的剖视图。

图6是表示比较例所涉及的半导体装置的制造方法的剖视图。

图7是表示比较例所涉及的半导体装置的制造方法的剖视图。

图8是表示比较例所涉及的半导体装置的制造方法的剖视图。

图9是表示实施方式2所涉及的抗蚀剂的第1开口和第2开口的俯视图。

图10是沿着图9的I-II剖开的剖视图。

图11是表示实施方式1所涉及的抗蚀剂的第1开口和第2开口的俯视图。

图12是表示实施方式3所涉及的半导体装置的制造方法的剖视图。

图13是表示实施方式3所涉及的半导体装置的制造方法的剖视图。

图14是表示实施方式3所涉及的半导体装置的制造方法的剖视图。

图15是表示实施方式3所涉及的半导体装置的制造方法的剖视图。

图16是表示实施方式4所涉及的半导体装置的制造方法的剖视图。

图17是表示实施方式4所涉及的半导体装置的制造方法的剖视图。

图18是表示实施方式4所涉及的半导体装置的制造方法的剖视图。

图19是表示实施方式4所涉及的半导体装置的制造方法的剖视图。

具体实施方式

参照附图对实施方式所涉及的半导体装置的制造方法进行说明。存在对相同的或者对应的结构要素标注相同的附图标记并省略反复说明的情况。

实施方式1

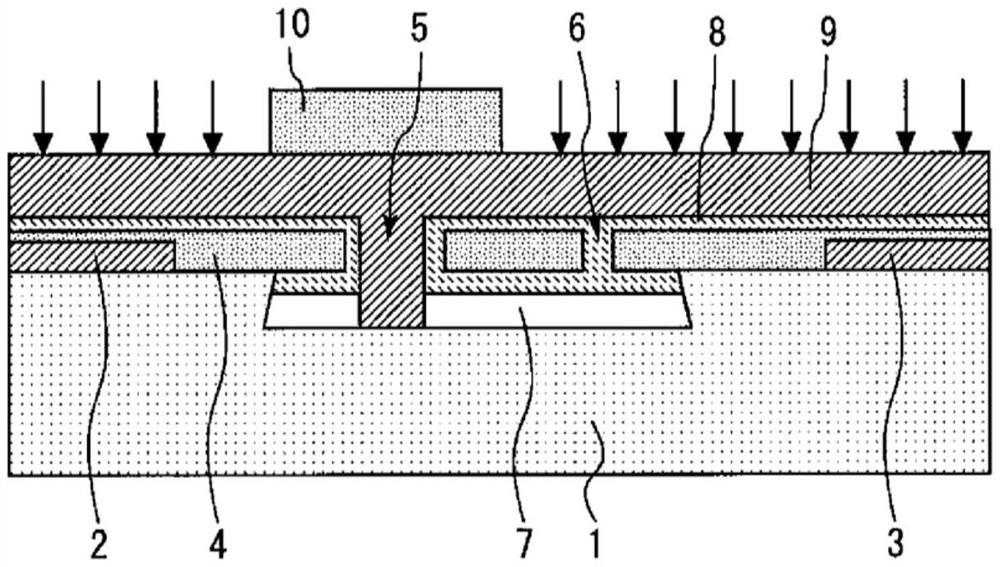

图1~图4是表示实施方式1所涉及的半导体装置的制造方法的剖视图。首先,如图1所示,在半导体基板1之上形成源电极2和漏电极3。半导体基板1由GaAs等构成。源电极2和漏电极3由Ti/Pt/Au等构成。

在半导体基板1、源电极2以及漏电极3之上涂覆抗蚀剂4。抗蚀剂4例如是住友化学工业公司制SUMIRESIST等。通过光刻法等而在抗蚀剂4形成第1开口5、和宽度比第1开口5窄的第2开口6。这里,将第1开口5形成于源电极2侧,将第2开口6形成于漏电极3侧。第1开口5的宽度是0.2~0.6μm。第2开口6的宽度是0.1~0.5μm。第1开口5与第2开口6的间隔是0.1~0.2μm。

将抗蚀剂4作为掩膜使用并将半导体基板1浸渍于磷酸或者柠檬酸数秒~数分钟来进行湿蚀刻,而在第1开口5和第2开口6之下形成一个连续的凹陷7。凹陷7不仅形成于第1开口5和第2开口6的下方,还形成于两者之间的抗蚀剂4的下方而连续。

接下来,如图2所示,在抗蚀剂4涂覆收缩材料8。收缩材料8是AZ ElectronicMaterials公司制RELACS等。将收缩材料8加热至适当温度来与抗蚀剂4进行交联反应,从而使抗蚀剂4图案收缩(pattern shrinking)。由此,使得宽度宽的第1开口5没有被封堵,而宽度窄的第2开口6完全被封堵。

接下来,如图3所示,通过溅射或者真空蒸镀而在整个面形成金属膜9。金属膜9不仅形成于抗蚀剂4和收缩材料8的上表面,还经由第1开口5到达至凹陷7的底面。在金属膜9之上形成抗蚀剂10。通过光刻法等,而在第1开口5的上方以比第1开口5宽的宽度残留抗蚀剂10,并除去其以外的抗蚀剂10。通过使用抗蚀剂10来作为掩膜的干蚀刻对金属膜9进行图案化。其后,除去抗蚀剂4、10以及收缩材料8。由此,如图4所示,在第1开口5的形成部分并在凹陷7内形成T字形的栅电极11。干蚀刻例如是使用了Ar气体等的数秒~数十分钟的离子蚀刻等。此外,也可以利用剥离工艺(lift-off process)形成栅电极11。

接着,将本实施方式的效果与比较例比较来进行说明。图5~图8是表示比较例所涉及的半导体装置的制造方法的剖视图。在比较例中,如图5所示,在抗蚀剂12仅形成一个开口13。使用该抗蚀剂12作为掩膜来对半导体基板1进行湿蚀刻而在开口13之下形成凹陷7。接下来,如图6所示,除去抗蚀剂12。接下来,如图7所示,在整个面形成抗蚀剂14,在凹陷7内,在抗蚀剂14形成开口15。接下来,如图8所示,在开口15的形成部分,在凹陷7内形成栅电极11。其后,除去抗蚀剂14。在比较例中,由于在第一次和第二次的抗蚀剂的图案化产生对准偏差,因此栅电极11在凹陷7内的位置产生偏差。因此,特性发生变动,制品的成品率降低。另外,由于需要两次的图案化,因此工序数增大,制造成本上升。

另一方面,在本实施方式中,对半导体基板1进行湿蚀刻而在抗蚀剂4的第1开口5和第2开口6之下形成连续的一个凹陷7。接下来,使收缩材料8与抗蚀剂4进行交联反应来使抗蚀剂4图案收缩,使得宽度宽的第1开口5没有被封堵,而宽度窄的第2开口6完全被封堵。接下来,在第1开口5的形成区域,在凹陷7内形成栅电极11。由此,栅电极11在凹陷7内的位置不产生偏差,因此制品的成品率提高。另外,对抗蚀剂进行图案化的工序数减少,从而能够减少制造成本。另外,也不会对栅电极11正下方的半导体造成损伤,因此可靠性提高。

另外,将第1开口5形成于源电极2侧,将第2开口6形成于漏电极3侧。由此,能够实现将栅电极11向源电极2侧错开的偏置栅极构造来提高高频特性。另外,在形成栅电极11后除去抗蚀剂4和收缩材料8。由此栅极电容减少,因此高频特性提高。

实施方式2

图9是表示实施方式2所涉及的抗蚀剂的第1开口和第2开口的俯视图。图10是沿着图9的I-II剖切的剖视图。第2开口6具有相互分离的多个开口6a、6b、6c。在多个开口6a、6b、6c之间存在没有开口的部位4a、4b。

接着,将本实施方式的效果与实施方式1比较来进行说明。图11是表示实施方式1所涉及的抗蚀剂的第1开口和第2开口的俯视图。在实施方式1中第2开口6是一个细长的开口。因此,若第1开口5与第2开口6的间隔窄,则存在两者之间的抗蚀剂4崩坏的可能性。另一方面,在本实施方式中,由于在多个开口6a、6b、6c之间存在不开口的部位4a、4b,因此能够加强抗蚀剂4。由此,能够形成稳定的图案,从而制品的成品率提高。其他的结构和效果与实施方式1相同。

实施方式3

图12~图15是表示实施方式3所涉及的半导体装置的制造方法的剖视图。到形成凹陷7并使收缩材料8与抗蚀剂4进行交联反应为止的工序与实施方式1相同。接下来,如图12所示,通过溅射或者蒸镀经由第1开口5在凹陷7的底面形成薄的Pt膜16。接下来,如图13所示,通过灰化(ashing)稍微扩大第1开口5的开口宽度。

接下来,如图14所示,通过溅射或者蒸镀形成经由扩大了开口宽度的第1开口5到达至凹陷7的底面的金属膜9。与实施方式1相同,通过使用抗蚀剂10作为掩膜的干蚀刻来对金属膜9进行图案化。金属膜9由与Pt膜16不同的金属构成。其后,除去抗蚀剂4和收缩材料8。

接下来,如图15所示,通过热处理使半导体基板1与Pt膜16反应来使Pt膜16沉入于半导体基板1。栅电极11具有:Pt膜16,沉入至半导体基板1;和金属膜9,由与Pt膜16不同的金属构成,宽度比Pt膜16宽,并重叠于Pt膜16之上。

一般来说,在晶体管中,电场集中于栅电极的漏极侧的下端部。与此相对地,在本实施方式中,电场容易集中的栅电极11的下端部变为阶梯状。因此,能够分散电场强度集中的部位。因此,根据偏置栅极的效果来抑制短沟道效应,从而提高高频特性。

另外,在经由第1开口5形成Pt膜16后,经由通过灰化扩大了开口宽度的第1开口5形成金属膜9,并通过热处理使Pt膜16沉入至半导体基板1。由此,能够容易地形成下端部变为阶梯状的栅电极11。

实施方式4

图16和图19是表示实施方式4所涉及的半导体装置的制造方法的剖视图。到形成凹陷7为止的工序与实施方式1相同。接下来,如图16所示,使收缩材料8与抗蚀剂4进行交联反应,直至收缩材料8到达至凹陷7的底面为止进行图案收缩。

接下来,如图17所示,使用抗蚀剂4和收缩材料8作为掩膜来对凹陷7的底面进行蚀刻,而在第1开口5的下方形成第1凹部17a,并在第2开口6的下方形成第2凹部17b。这里,由于收缩材料8到达至凹陷7的底面,因此仅第1开口5和第2开口6的部分被蚀刻。而且,蚀刻率取决于图案的开口尺寸,因此第1凹部17a的深度比第2凹部17b的深度深。

接下来,如图18所示,通过溅射或者真空蒸镀而在整个面形成金属膜9。金属膜9不仅形成于抗蚀剂4和收缩材料8的上表面,还分别经由第1开口5和第2开口6到达至第1凹部17a和第2凹部17b。通过使用抗蚀剂12作为掩膜的干蚀刻对金属膜9进行图案化。其后,除去抗蚀剂4、10以及收缩材料8。由此,如图19所示,经由第1开口5在第1凹部17a形成T字形的第1栅电极11a,并经由第2开口6在第2凹部17b形成T字形的第2栅电极11b。此外,也可以通过剥离工艺形成第1栅电极11a和第2栅电极11b。

如上述那样由于第1凹部17a与第2凹部17b的深度不同,因此形成于第1凹部17a的第1栅电极11a、和形成于第2凹部17b的第2栅电极11b的阈值不同。因此,能够形成在相同的凹陷内具有不同的阈值电压的晶体管。而且,与实施方式1相同,第1栅电极11a和第2栅电极11b在凹陷7内的位置不产生偏差,因此制品的成品率提高。另外,对抗蚀剂进行图案化的工序数减少,能够减少制造成本。

附图标记说明

1…半导体基板;2…源电极;3…漏电极;4…抗蚀剂;5…第1开口;6…第2开口;6a、6b、6c…多个开口;7…凹陷;8…收缩材料;9…金属膜;11…栅电极;11a…第1栅电极;11b…第2栅电极;16…Pt膜(金属薄膜);17a…第1凹部;17b…第2凹部。

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置

- 半导体装置的制造方法、显示装置的制造方法、半导体装置、半导体元件的制造方法以及半导体元件