一种高速RS译码器

文献发布时间:2023-06-19 09:54:18

技术领域

本发明涉及通信中的译码领域,具体涉及一种高速RS译码器。

背景技术

随着光纤通信技术的发展与普及,光网络的性能迎来了新的挑战。由于现实中的各种需求,光网络需要满足距离远,速率高,存储大的要求,但是伴随满足这些需求的同时会产生大量的误码,对接收器的纠错能力是一个巨大的挑战,所以前向纠错技术(FEC)就变得十分重要。而Reed-Solomon码(RS码)属于一种性能优良的前向纠错技术,并且特别适合纠正突发错码,因此广泛应用于无线通讯,光通讯,存储系统等方面。RS译码器中包括伴随多项式计算,关键方程计算,错误图样计算以及纠错过程,随着通信系统传输速率的提高,译码器的硬件资源需求和延时越来越大。目前RS现有并行译码电路在RS(544,514)码长、8路并行情况下,吞吐量可达36Gbit/s;在RS(255,239)码长、3路并行情况下,吞吐量为11.4Gbit/s。但是现有的并行译码电路设计没有提出在数据高速传输情况下针对长码的译码方案。因此,在高速率的通信系统中如何设计出一款高速且硬件资源少的译码电路就成为了必须要解决的问题。

发明内容

本发明针对高速传输的通信系统,提供了一种实现硬件资源少,速度快的高速RS译码器,由于处理数据效率较高,因而本发明可以应对长码。

本发明的技术方案是:

一种高速RS译码器,其特殊之处在于:

包括伴随多项式运算模块、欧几里得算法模块、钱搜索和福尼算法模块,以及纠错模块;

伴随多项式运算模块用于对输入的p*m bit接收码进行处理,得到n-k个伴随子s

欧几里得算法模块用于计算x

钱搜索和福尼算法模块用于对所述错误位置多项式和错误值多项式进行数据预处理、并行分流为p路数据,计算p路数据的错误图样;

纠错模块用于对所述p*m bit接收码和所述p路数据的错误图样按高低位进行异或操作,完成纠错并输出。

进一步地,伴随多项式运算模块包括p路并行的伴随子预处理模块、伴随多项式计算模块和输出控制模块;

p路并行的伴随子预处理模块用于对当前输入的p路m bit数据均乘以α

伴随多项式计算模块由多路选择器、数据存储器及n-k个伽罗华域乘法器构成;

多路选择器用于根据伴随子预处理模块输出的p个计算结束标志信号,单周期内仅选通其中一路伴随子预处理模块的结果输出;

数据存储器存储用于存储以p为倍数的伽罗华域乘法因子

n-k个伽罗华域乘法器用于将所述以p为倍数的伽罗华域乘法因子,与经多路选择器所选择的伴随子预处理模块的输出结果相乘;

输出控制模块接收n-k个伽罗华域乘法器的计算结果并对其依次累加,完成伴随多项式计算,输出包含n-k项伴随多项式。

进一步地,欧几里得算法模块为由多级结构相同的欧几里得算法基础模块级联构成的L级流水线结构;

单个欧几里得算法基础模块包括除法模块、错误值多项式计算模块和错误位置多项式计算模块;

除法模块用于计算

错误值多项式计算模块由错误值寄存器、错误值备用寄存器、错误值乘法矩阵和迭代次数计数器构成;错误值寄存器用于存储当前计算使用的错误值;错误值备用寄存器用于存储迭代过程中需要赋值给错误值寄存器的数值;错误值乘法矩阵的输入是来自错误值寄存器的数据ω

错误位置多项式计算模块由错误位置寄存器、错误位置备用寄存器、错误位置异或寄存器和错误位置乘法矩阵构成;错误位置寄存器用于存储当前计算使用的错误位置信息;错误位置备用寄存器用于存储迭代过程中需要赋值给错误位置寄存器的数值;错误位置异或寄存器用于计算错误位置乘法矩阵的输出值与错误位置备用寄存器的输出值的异或结果并存储;错误位置乘法矩阵的输入是来自错误位置寄存器的数据λ

迭代次数计数器用于累计除法模块、错误值多项式计算模块、错误位置多项式计算模块的迭代次数,当计数值为3*(n-k)时,错误值寄存器和错误位置寄存器将错误值多项式和错误位置多项式输出。

进一步地,除法模块由数据存储器、第一寄存器、第二寄存器和伽罗华域乘法器构成;

数据存储器用于存储伽罗华域不同次幂本原元α

第一寄存器、第二寄存器分别用于存储除数多项式最高项系数的倒数和存储被除数多项式的最高项系数;

伽罗华域乘法器用于将第一寄存器、第二寄存器的输出值相乘,得到商q。

进一步地,钱搜索和福尼算法模块包括初始化模块以及p个钱搜索算法和福尼算法计算模块;

初始化模块包括错误值输入寄存器、错误位置输入寄存器、计数器一、输入选择器、伽罗华域数据存储单元、第一乘法矩阵、计数器二、输出选择器、错误值输出寄存器和错误位置输出寄存器;

错误值输入寄存器和错误位置输入寄存器分别用于存储所述欧几里得算法模块输出的含有n-k项的错误位置多项式和含有n-k项的错误值多项式;

计数器一用于控制所述输入选择器输出到第一乘法矩阵的参数,前p个输出为错误值多项式系数,后p个输出为错误位置多项式系数;

第一乘法矩阵用于将接收到的错误值多项式系数与所述伽罗华域数据存储单元中的p个数组相乘,以及将接收到的错误位置多项式系数与所述伽罗华域数据存储单元中的p个数组相乘;

计数器二用于控制所述输出选择器将第一乘法矩阵的初始化结果,对应存储在所述错误值输出寄存器或者错误位置输出寄存器中;

所述错误值输出寄存器和错误位置输出寄存器分别用于存储p组错误值初始化结果和p组错误位置初始化结果。

进一步地,单个钱搜索算法和福尼算法计算模块包括错误位置多项式输入寄存器、错误值多项式输入寄存器、第二乘法矩阵、第三乘法矩阵、第一加法器、第二加法器、第三加法器和除法器;

错误位置多项式输入寄存器、错误值多项式输入寄存器分别用于存储所述初始化模块输出的错误位置多项式系数和错误值多项式系数;

第二乘法矩阵用于将错误位置多项式输入寄存器中的数据对应按顺序乘以伽罗华域本原元的递增次幂;

第三乘法矩阵用于将错误值多项式输入寄存器中的数据对应按顺序乘以伽罗华域本原元的递增次幂;

第一加法器用于基于第二乘法矩阵的输出结果,计算错误位置多项式偶数项之和以及错误位置多项式奇数项之和;

第二加法器用于基于第三乘法矩阵的输出结果,计算错误值多项式各项之和;

除法器用于将所述错误值多项式各项之和除以错误位置多项式奇数项之和,得到错误图样。

进一步地,单个钱搜索算法和福尼算法计算模块还包括错误数计数器;所述错误数计数器用于根据错误位置多项式偶数项之和以及错误位置多项式奇数项之和,计算错误数量;

所述钱搜索和福尼算法模块还包括加法器;所述加法器用于根据p个钱搜索算法和福尼算法计算模块输出的错误数量值,计算总错误数量。

本发明的优点是:

1.本发明设计实现了高速RS译码器,提高了译码过程的吞吐量与处理速度。

在现有并行译码电路中,以RS(544,514)为例,该码长下总消息符号个数为544,其中信码符号个数为514,校验码符号个数为30,纠错能力为15个符号,每个符号位宽为10bit,以8路并行的方式实现;其综合后的电路时序为446MHZ,资源使用为20014个LUT,吞吐量为36Gbit/s。

本发明电路中,以RS(1023,847)码为例,该码长下总消息符号个数为1023,其中信码符号个数为847,校验码符号个数为176,纠错能力为88个符号,每个符号位宽为10bit,以7路并行的方式实现;其综合后的电路时序为454MHZ,资源使用为93312个ALMs,约等于373248个LUT(1个ALM等于4个LUT),吞吐量为32Gbit/s。

虽然本发明中的吞吐量比现有的并行译码电路低,资源比它大一些,但是本发明所使用的码长较长,校验码长度是其5.9倍,纠错能力也是其5.9倍,但占用的硬件资源仅是其18.6倍,显而易见,本发明确实比现有并行译码电路效率更高。

2.本发明实现的电路与现有的并行译码电路相比,大大降低了硬件资源。

基于本发明实现的RS(255,223)译码器在9路并行情况下占用资源为32174ALMs;在已有并行译码电路中,RS(255,239)码长3路并行情况下占用资源为28968ALMs;经过对比发现尽管本设计占用资源是已有并行电路的1.1倍,但本设计并行度是其3倍,计算时长是其1/3倍,因此可以得出“本发明与现有的并行译码电路相比,大大降低了硬件资源”的结论。另外本发明也实现了应用于长码的并行译码电路设计,RS(1023,847)译码器在7路并行情况下占用资源为93312ALMs。

设定义在伽罗华域GF(2

在伴随多项式计算阶段,本发明以p路m bit数据并行输入,p个基本计算单元每周期使用的伽罗华域乘法器数量为n-k个,伴随多项式计算模块处理一个块消息花费周期为n/p;在欧几里得算法阶段,本发明的输入数据为(n-k)*mbit,每次迭代使用的伽罗华域乘法器数量为5*(n-k)个,处理一个块消息花费周期为3*(n/p);在钱搜索算法和福尼算法计算阶段,本发明的输入数据为2*(n-k)*mbit,每次迭代使用的伽罗华域乘法器数量为(n-k)*p个,处理一个块消息花费的周期为2*(n/p)。

附图说明

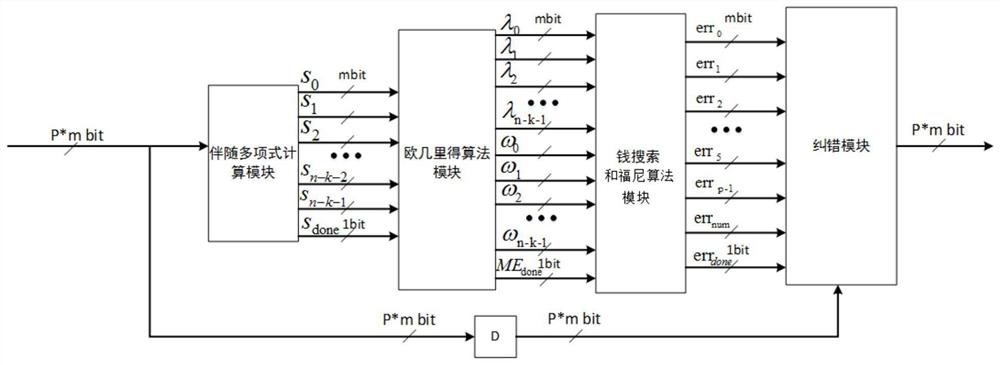

图1是本发明RS译码器的顶层结构。

图2是本发明RS译码器中伴随多项式运算模块并行结构图。

图3是本发明RS译码器中伴随多项式预处理单元结构示意图。

图4是本发明RS译码器中欧几里得算法模块电路整体结构示意图。

图5是本发明RS译码器中欧几里得算法模块基本单元示意图。

图6是本发明RS译码器中钱搜索算法和福尼算法模块并行结构图。

图7是本发明RS译码器中钱搜索算法和福尼算法初始化模块结构示意图。

图8是本发明RS译码器中钱搜索算法和福尼算法计算模块结构示意图。

具体实施方式

设定义在伽罗华域GF(2

以下结合附图和实例对本发明作详细说明。

如图1所示,本发明提供了一种适用于不同码长RS码的并行译码器,其结构包括:伴随多项式运算模块、欧几里得算法模块、钱搜索和福尼算法模块,以及纠错模块。

首先,p*m bit接收码输入伴随多项式运算模块,经过n/p个周期的计算,输出n-k个m bit数据s

接着,该n-k个s

接着,错误位置多项式和错误值多项式及done_Euclide标志信号进入钱搜索和福尼算法计算模块计算,经过2p+(n/p-1)个周期,钱搜索和福尼算法模块将错误数量和错误图样以及标志着该块消息完成钱搜索算法和福尼算法阶段的done_chien标志进行输出;

最后,错误图样与接收码输入纠错模块,完成纠错。

1.伴随多项式运算模块结构及相应算法

伴随多项式运算模块如图2所示,包括p路并行的伴随子预处理模块、伴随多项式计算模块和输出控制模块;

p路并行的伴随子预处理模块用于对数据进行预处理操作。如图3所示,预处理是对当前输入的p路mbit数据均乘以α

伴随多项式计算模块由多路选择器、数据存储器(rom)及n-k个伽罗华域乘法器组成;多路选择器受伴随子预处理模块输出的p个计算结束标志信号控制,单周期内仅有一个计算结束标志信号有效,举例来说,若计算结束标志信号1有效,其余计算结束标志信号无效,则多路选择器选择第1路伴随子预处理模块的结果输出(多路选择器每一轮输出的结果有n-k项,分别送入n-k个伽罗华域乘法器中);数据存储器存储以p为倍数的伽罗华域乘法因子

伴随多项式结构如式1所示:

s(x)=s

本发明的伴随多项式运算模块需要的计算结果是式1每一项的系数s

S

式3是式2中n-k个伴随子的展开表示,r

式4将n项数据以p为单位分割为

式5的形式对应式3中前p列数据的形式,该过程称为预处理过程;预处理之后依据数据传输的先后顺序由多路选择器根据p个预处理单元输出的有效计算结束标志信号决定输出给后续n-k个伽罗华域乘法器的一组预处理数据,而数据存储器中存储着对应预处理块需要的α次幂,也由p个预处理单元输出的有效计算结束标志信号控制,输出对应多路选择器输出的数据需要的剩余α次幂,例如:

2.欧几里得算法模块结构及相应算法

欧几里得算法模块采用伽罗华域除法器计算x

除法计算通过

式6中

欧几里得算法模块顶层结构如图4所示,为由多级欧几里得算法基础模块(Euclide_unit1,Euclide_unit2,…,Euclide_unitx)构成的L级流水线结构,每一级欧几里得算法基础模块结构相同,第一级欧几里得算法基础模块的输入为n-k个伴随子s

单个欧几里得算法基础模块具体的功能结构如图5所示,包括除法模块、错误值多项式计算模块、错误位置多项式计算模块和迭代次数计数器;除法模块用于计算

当接收到伴随多项式运算模块的输出数据,欧几里得算法模块开始对数据进行初始化,初始化过程如式8所示:

将输入的n-k个伴随子s

步骤四:重复步骤一至步骤三n-k-1次,待图5中迭代次数计数器(count)计数到3*(n-k)时,错误值寄存器和错误位置寄存器将错误值多项式ω

3.钱搜索和福尼算法模块结构

钱搜索和福尼算法模块用于对欧几里得算法模块输出的错误位置多项式和错误值多项式进行计算,得到错误图样。

钱搜索算法和福尼算法电路功能类似,都是计算多项式在位置α

如图6所示,钱搜索和福尼算法模块包括初始化模块和p个钱搜索算法和福尼算法计算模块。

初始化模块的结构如图7所示,功能是对当前输入的数据预处理及并行分流,具体初始化流程是:先将欧几里得算法模块输出的含有n-k项的错误位置多项式和含有n-k项的错误值多项式存储进各自的寄存器,之后由计数器count控制选择输出到第一乘法矩阵的参数,前p个输出为错误值多项式系数,后P个输出为错误位置多项式系数。故先进行错误值多项式的初始化:由错误值多项式依次乘以伽罗华域数据存储单元中的p个数组,每个数组中的数据有n-k个,相邻两个数组之间的伽罗华域数据相差

错误位置多项式的初始化与错误值多项式初始化的过程相同,只是输入数据是错误位置多项式系数而不是错误值多项式系数。

待错误位置多项式和错误值多项式初始化完成时,将p组数据(从初始化模块输出的是2p组数据,将第一路错误位置初始化结果和第一路错误值初始化结果一起输入至钱搜索算法和福尼算法计算模块1,后续p-1路数据的输入以此类推)输入至钱搜索算法和福尼算法计算模块1~p,进行后续阶段数据的处理。

p个钱搜索算法和福尼算法计算模块的结构相同,如图8所示,展示了单个钱搜索算法和福尼算法计算模块的基本结构:图8左端输入的是经过初始化模块处理的错误位置多项式系数和错误值多项式系数,经过各自寄存器存储之后变为λreg_i,ωreg_i(i∈[0,n-k-1])参与后续运算,在第二乘法矩阵和第三乘法矩阵中分别完成的操作为:λreg_i,ωreg_i对应按顺序乘以伽罗华域本原元的递增次幂,例如:

其中,k为迭代次数,

如式10所示,计算过程共需要

ω

求和之后再根据运算公式得到错误数量和错误值。错误数量是根据错误位置的奇数项之和与偶数项之和是否相等来判定的,在第k次迭代时,若奇数之项和与偶数项之和相等,则错误数计数器加一,共判断

错误图样是利用错误值多项式第k次迭代的总和,除以错误位置多项式第k次迭代的奇数项之和得到的,如式12所示:

因此,经过p个钱搜索算法和福尼算法计算模块便得到了p路错误数量值和错误图样。图7中加法器的作用是对这p路错误数量值进行求和,得到总错误数量,用于向用户反馈信道质量。

p个钱搜索算法和福尼算法计算模块的原理一致,只是输入数据不同,和伴随多项式计算模块异曲同工,缩短了迭代周期(n>n/p)。

4.纠错模块

纠错模块的输入信号是译码器输入的p*m bit接收码和钱搜索和福尼算法模块输出的错误图样,将两个输入数据按高低位进行异或操作,完成纠错并输出。

实施例:

本实施例以RS(1023,847)码长为例,对于RS(1023,847),每一个符号大小为m=10bit,总符号数n=1023,信码符号数k=847,相应的校验码符号数为n-k=176,纠错能力t=88个符号数。

本实施例按实际应用场景的需求经过计算得到并行分路的数量p为7,具体计算过程不在此赘述。故译码器输入数据位宽为7*10=70bit。因为输入数据还用于纠错模块,所以决定了钱搜索和福尼算法模块输出并行度。

伴随多项式运算模块中对输入的70bit数据进行分流后,进行了并行伴随子计算,得到176个伴随子,运算周期约为147。

欧几里得算法用伴随多项式进行辗转相除,经过176次迭代得到两组数据:错误位置多项式和错误值多项式。

钱搜索和福尼算法模块对176项系数的错误位置多项式和176项系数的错误值多项式进行计算,得到错误图样和错误数量。

以RS(1023,847)为例描述图2伴随多项式模块,顶层由7路并行的伴随子预处理模块、伴随多项式计算模块和输出控制模块组成;7路并行的伴随子预处理模块用于对数据进行预处理操作,如图3所示,预处理对输入数据均乘以α

RS(1023,847)码长下的伴随多项式结构如式13所示:

s(x)=s

伴随多项式运算模块需要的计算结果是式13每一项的系数s

S

式15是式14中176个伴随子的展开表示,r

式16将1023项数据以7为单位分割为147份,分段处理。伴随子预处理过程包含7个伴随子预处理模块,各模块计算过程一致,都是对不同的输入数据r

式17的形式对应式15中前7列数据的形式,该过程称为预处理过程;预处理之后依据数据传输的先后顺序由多路选择器根据7个伴随子预处理单元输出的有效结束标志信号决定输出给伽罗华域乘法器的一组预处理数据,而数据存储器中存储着对应预处理块数据需要的α次幂,也由7个伴随子预处理单元输出的结束标志信号控制,输出对应多路选择器输出的数据需要的剩余α次幂,例如:α

以RS(1023,847)为例描述图4、图5中欧几里得算法模块结构与功能。

图4为欧几里得算法模块电路整体结构示意图,若以RS(1023,847)为例,流水线的总级数

当接收到伴随多项式运算模块的输出数据,欧几里得算法模块开始对数据进行初始化,初始化过程如式18所示:

将输入的176个伴随子赋给错误值寄存器;而错误值备用寄存器第176项初始化为1,其余175个数据初始化为0;错误位置备用寄存器以及错误位置异或寄存器中存储的数据的176个数据都初始化为0,错误值寄存器中的第0个数据初始化为1,其余175个数据初始化为0;初始化结束后开始进行图5中欧几里得算法的迭代过程,步骤一:图5中除法模块计算

步骤四:重复步骤一至步骤三175次,待图5中迭代次数计数器count计数到3*176=528时,将错误值多项式ω

结合图6描述RS(1023,847)钱搜索和福尼算法模块并行结构,RS(1023,847)钱搜索和福尼算法模块并行结构包含预处理模块和7个钱搜索算法和福尼算法计算单元。结合图7初始化模块和图8钱搜索算法和福尼算法计算模块与RS(1023,847)的应用场景来说:钱搜索和福尼算法模块包括初始化模块和计算模块1~7。初始化模块的结构如图7所示,功能是对当前输入的数据预处理及并行分流,具体流程是:先将欧几里得算法模块输出的含有176项的错误位置多项式和含有176项的错误值多项式存储进各自的寄存器,之后由计数器count控制选择输出到第一乘法矩阵的参数,前7个输出为错误值多项式系数,后7个输出为错误位置多项式系数。故先进行错误值多项式的初始化:由错误值多项式依次乘以伽罗华域数据存储单元中的7个数组,每个数组中的数据有176个,相邻两个数组之间的伽罗华域数据相差α

其中,k为迭代次数,k∈[1,147];

如式20所示,计算过程共需要147次求和迭代,每迭代一次输出一次,输出的结果用于求和计算,不同的是:错误位置多项式按奇数项和偶数项区分求和,而错误值多项式是集体求和,例如:

求和之后再根据运算公式得到错误数量和错误值。错误数量是根据错误位置的奇数项和与偶数项和是否相等来判定的,在第k次迭代时,若奇数项和与偶数项和相等,则错误数计数器加一,共判断147次,伪代码如下:

错误值是利用错误值多项式第k次迭代的总和除以错误位置多项式第k次迭代的奇数和得到的,如式22所示:

因此,经过7个钱搜索算法和福尼算法计算模块便得到了7路错误数量值和错误值。图7中加法器的作用是对这7路错误数量进行求和,得到总错误数量。在后续纠错过程中应用到的只有错误值,错误数量用于向用户反馈信道质量。这7个钱搜索算法和福尼算法计算模块它们的计算原理一致,只是输入数据不同,和伴随多项式计算模块异曲同工,缩短了迭代周期(n>n/p)。

最后的纠错过程就是错误图样和接收码的异或操作,需要注意的是:因为钱搜索和福尼算法模块对数据进行分割,钱搜索和福尼算法模块数据的输出形式为(error_out

例如输出数据时,第一拍时钟输出d

d

1023个符号经过纠错后得到译码结果,译码器后续处理是将1023个符号按照数据先后关系进行拼接,之后将拼接后的结果和总错误数量进行输出。

- 一种高速RS译码器

- 一种基于FPGA的高速RS编译码器实现方法