具有三维鳍式场效应晶体管结构的分裂栅非易失性存储器单元及其制造方法

文献发布时间:2023-06-19 09:57:26

本专利申请要求于2018年7月5日提交的名称为“具有三维鳍式场效应晶体管结构的分裂栅非易失性存储器单元及其制造方法(Split Gate Non-volatile Memory CellsWith Three-Dimensional FINFET Structure,And Method Of Making Same)”的美国专利申请16/028244号的优先权。

技术领域

本发明涉及非易失性闪存存储器单元阵列。

背景技术

分裂栅非易失性存储器设备在本领域中是熟知的。例如,美国专利7927994公开了分裂栅非易失性存储器单元。图1示出形成在半导体衬底12上的此类分裂栅存储器单元的示例。源极区16和漏极区14以扩散区的形式形成在衬底12中,并且在两者之间限定沟道区18。存储器单元包括四个导电栅:浮栅22,该浮栅设置在沟道区18的第一部分和源极区16的部分的上方并且与沟道区的第一部分和源极区的部分绝缘;控制栅26,该控制栅设置在浮栅22上方并与浮栅绝缘;擦除栅24,该擦除栅设置在源极区16上方并与源极区绝缘;以及选择栅20,该选择栅设置在沟道区18的第二部分上方并与沟道区的第二部分绝缘。导电触点10可以形成为电连接到漏极区14。由于沟道区沿半导体衬底的平坦表面形成,因此随着器件几何形状变小,沟道区的总面积(例如,宽度)也变小。这减少了源极区和漏极区之间的电流流动,从而需要更敏感的感测放大器等来检测存储器单元的状态。

因为缩小光刻尺寸从而减少沟道宽度的问题会影响所有半导体器件,所以已经提出了鳍式场效应晶体管型的结构。在鳍式场效应晶体管型的结构中,半导体材料的鳍形构件将源极区连接到漏极区。鳍形构件包括两个侧表面,该侧表面终止在顶表面。然后,从源极区到漏极区的电流可沿两个侧表面和顶表面流动。因此,沟道区的宽度增加,从而增加了电流。然而,通过将沟道区“折叠”成两个侧表面和顶表面增加沟道区的宽度而不牺牲更多的半导体衬底面,从而减少沟道区的“覆盖区”。已经公开了使用此类鳍式场效应晶体管的非易失性存储器单元,其中浮栅邻近鳍形构件的侧表面中的一个侧表面设置。现有技术的鳍式场效应晶体管非易失性存储器结构的一些示例(尽管栅极的数量和配置不同于图1中的上述平面示例)包括美国专利号7423310、7410913和8461640以及美国专利公开案2017/0345840。还提出了在鳍形构件上形成逻辑器件。参见例如美国专利公开案2017/0125429和待审美国专利申请15/933124。

然而,这些现有技术的鳍式场效应晶体管结构已经公开了在堆叠栅极配置中使用浮栅,或使用俘获材料,或使用富硅氧化物(SRO)或使用纳米晶体硅来存储电荷,或其他更复杂的存储器单元配置。

发明内容

上述问题和需求通过一种存储器设备来解决,该存储器设备包括半导体衬底,该半导体衬底具有上表面,该上表面具有多个向上延伸的鳍,其中该鳍中的每个鳍包括彼此相对并且终止于顶表面的第一侧表面和第二侧表面。存储器单元形成在多个鳍中的第一鳍上。该存储器单元包括:源极区和漏极区,该源极区和该漏极区在第一鳍中间隔开,其中第一鳍的沟道区沿第一鳍的顶表面和相对的侧表面在源极区和漏极区之间延伸;浮栅,该浮栅沿沟道区的第一部分延伸,其中浮栅沿第一鳍的第一侧表面和第二侧表面以及顶表面延伸并且与第一鳍的第一侧表面和第二侧表面以及顶表面绝缘;选择栅,该选择栅沿沟道区的第二部分延伸,其中选择栅沿第一鳍的第一侧表面和第二侧表面以及顶表面延伸并与第一鳍的第一侧表面和第二侧表面以及顶表面绝缘;控制栅,该控制栅沿浮栅延伸并与浮栅绝缘;以及擦除栅,该擦除栅沿源极区延伸并且与源极区绝缘。多个鳍中的第二鳍具有在第一方向上延伸的长度,其中第一鳍具有在垂直于第一方向的第二方向上延伸的长度,并且其中源极区在第一鳍和第二鳍的交汇处形成于第一鳍中。

存储器设备包括半导体衬底,该半导体衬底具有上表面,该上表面具有多个向上延伸的第一鳍和多个向上延伸的第二鳍。第一鳍和第二鳍中的每个鳍包括彼此相对并且终止于顶表面的第一侧表面和第二侧表面。第一鳍中的每个鳍具有在第一方向上延伸的长度。第二鳍中的每个鳍具有在垂直于第一方向的第二方向上延伸的长度。第一鳍以网格状方式与第二鳍相交。多个存储器单元形成在第一鳍上,其中该存储器单元中的每个存储器单元形成在第一鳍中的一个鳍上并且包括:源极区和漏极区,该源极区和该漏极区在一个第一鳍中间隔开,其中该一个第一鳍的沟道区沿该一个第一鳍的顶表面和相对的侧表面在源极区和漏极区之间延伸;浮栅,该浮栅沿沟道区的第一部分延伸,其中浮栅沿该一个第一鳍的第一侧表面和第二侧表面以及顶表面延伸并且与该一个第一鳍的第一侧表面和第二侧表面以及顶表面绝缘;选择栅,该选择栅沿沟道区的第二部分延伸,其中选择栅沿该一个第一鳍的第一侧表面和第二侧表面以及顶表面延伸并与该一个第一鳍的第一侧表面和第二侧表面以及顶表面绝缘;控制栅,该控制栅沿浮栅延伸并且与浮栅绝缘;以及擦除栅,该擦除栅沿源极区延伸并且与源极区绝缘,其中源极区形成在该一个第一鳍和第二鳍中的一个鳍的交汇处。

一种形成存储器设备的方法包括:在半导体衬底的上表面中形成多个向上延伸的鳍,其中该鳍中的每个鳍包括彼此相对并且终止于顶表面的第一侧表面和第二侧表面;以及在多个鳍中的第一鳍上形成存储器单元。通过以下方式形成存储器单元:形成源极区和漏极区,该源极区和该漏极区在第一鳍中间隔开,其中第一鳍的沟道区沿第一鳍的顶表面和相对的侧表面在源极区和漏极区之间延伸;形成浮栅,该浮栅沿沟道区的第一部分延伸,其中浮栅沿第一鳍的第一侧表面和第二侧表面以及顶表面延伸并且与第一鳍的第一侧表面和第二侧表面以及顶表面绝缘;形成选择栅,该选择栅沿沟道区的第二部分延伸,其中选择栅沿第一鳍的第一侧表面和第二侧表面以及顶表面延伸并与第一鳍的第一侧表面和第二侧表面以及顶表面绝缘;形成控制栅,该控制栅沿浮栅延伸并与浮栅绝缘;以及形成擦除栅,该擦除栅沿源极区延伸并且与源极区绝缘。多个鳍中的第二鳍具有在第一方向上延伸的长度,其中第一鳍具有在垂直于第一方向的第二方向上延伸的长度,并且其中源极区在第一鳍和第二鳍的交汇处形成于第一鳍中。

一种形成存储器设备的方法包括:在半导体衬底的上表面中形成多个向上延伸的第一鳍和多个向上延伸的第二鳍,其中第一鳍和第二鳍中的每个鳍包括彼此相对并且终止于顶表面的第一侧表面和第二侧表面,第一鳍中的每个鳍具有在第一方向上延伸的长度,第二鳍中的每个鳍具有在垂直于第一方向的第二方向上延伸的长度,并且第一鳍以网格状方式与第二鳍相交。该方法还包括:在第一鳍上形成多个存储器单元,其中每个存储器单元通过以下方式形成在第一鳍中的一个鳍上:形成源极区和漏极区,该源极区和该漏极区在一个第一鳍中间隔开,其中该一个第一鳍的沟道区沿该一个第一鳍的顶表面和相对的侧表面在源极区和漏极区之间延伸;形成浮栅,该浮栅沿沟道区的第一部分延伸,其中该浮栅沿该一个第一鳍的第一侧表面和第二侧表面以及顶表面延伸并且与该一个第一鳍的第一侧表面和第二侧表面以及顶表面绝缘;形成选择栅,该选择栅沿沟道区的第二部分延伸,其中该选择栅沿该一个第一鳍的第一侧表面和第二侧表面以及顶表面延伸并与该一个第一鳍的第一侧表面和第二侧表面以及顶表面绝缘;形成控制栅,该控制栅沿浮栅延伸并且与浮栅绝缘;以及形成擦除栅,该擦除栅沿源极区延伸并且与源极区绝缘,其中源极区形成在该一个第一鳍和第二鳍中的一个鳍的交汇处。

通过查看说明书、权利要求书和附图,本发明的其他目的和特征将变得显而易见。

附图说明

图1为常规的非易失性存储器单元的侧面剖视图。

图2是存储器区域的顶视图,示出了其他附图的各种剖视图方向。

图3A、图4A、图5A、图6A、图7A、图8A、图9A、图10A、图11A至图11C、图12A至图12D、图13A至图13D、图14A至图14D、图15A至图15D、图16A至图16D、图17A至图17D、图18A至图18D、图19A至图19D、图20A至图20D、图22A至图22D、图23A至图23D、图24A至图24D、图25A至图25D、图26A至图26B、图27A至图27B和图28是存储器区域的不同横截面位置和方向的侧剖视图,示出了形成本发明的存储器设备的步骤。

图3B、图4B、图5B、图6B、图7B、图8B、图9B、图10B、图11D、图12E、图13E、图14E、图15E、图16E、图17E、图18E、图19E、图20E、图21、图22E、图23E、图24E、图25E和图26C是逻辑器件区域的侧剖视图,示出了形成本发明的存储器设备的步骤。

图9C是存储器区域的顶视图,示出了衬底的竖直和水平延伸的鳍。

具体实施方式

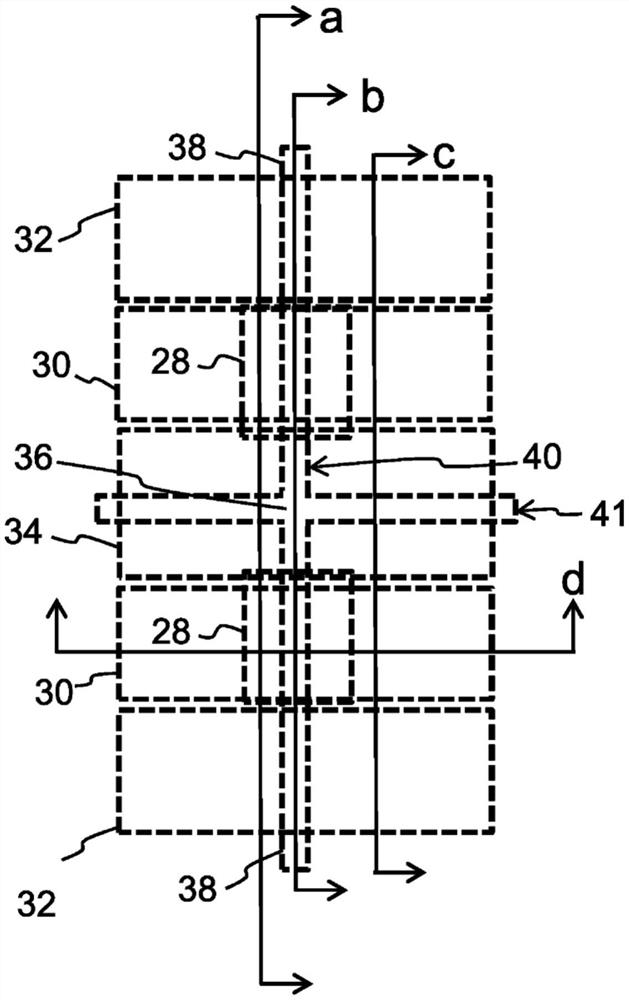

本发明是具有鳍式场效应晶体管分裂栅型存储器单元的存储器设备,每个单元具有四个栅极:浮栅28、控制栅30、选择栅32和擦除栅34。鳍式场效应晶体管逻辑器件形成在与存储器单元相同的衬底上。图2是示出衬底的存储器区域中的一镜像对的存储器单元的配置的顶视图。该镜像对的存储器单元共享公共源极区36(即,衬底的具有不同于衬底的第一导电类型的第二导电类型的区域),其中(第二导电类型的)漏极区38在相邻存储器单元对(未示出)之间共享。衬底包括半导体衬底42的上表面的交叉鳍形部分40和41。存储器单元形成在鳍形部分40上。图2还示出了用于随后所述附图的剖视图方向a、b、c和d。

制造工艺从选择性地植入半导体衬底42的不同区域开始。衬底42的各个区域在图3A和图3B中示出(即,图3A和图3B示出相同衬底42的不同区域),其中衬底具有与存储器单元和逻辑器件相关的四个区域:存储器区域42a(其中形成存储器单元)、HV区域42b(其中形成高电压逻辑器件)、逻辑核心区域42c(其中形成核心逻辑器件)和逻辑IO区域42d(其中形成输入/输出逻辑器件)。区域42b、42c和42d在本文中统称为逻辑区域。优选地,选择性植入开始于用掩模材料覆盖除HV区域之外的衬底,该HV区域经受一个或多个植入步骤(例如,抗穿通植入,该抗穿通植入将防止形成于该区域中的高电压逻辑器件中的源极到漏极泄漏)。这可针对存储器区域重复(例如,用掩模材料覆盖其他区域,并且执行抗穿通植入,该抗穿通植入将防止形成在该区域中的存储器单元中的源极到漏极泄漏)。

然后,与衬底42的逻辑区域相比,使衬底的存储器区域的上表面凹陷(降低),如图4A和图4B所示。这优选地通过以下方式来完成:在衬底42上形成材料(例如,氮化硅)层,之后进行掩模步骤(即,光致抗蚀剂沉积、选择性光刻曝光和选择性光致抗蚀剂去除),从而在逻辑区域中的氮化硅上留下光致抗蚀剂,但使氮化硅暴露在存储器区域中。使用氮化硅蚀刻从存储器区域去除氮化硅,使衬底表面暴露。衬底42的(在存储器区域中的)暴露部分被氧化,之后进行湿法氧化物蚀刻以去除衬底的氧化部分,这有效地去除衬底的顶部部分(有效地降低/凹陷其上表面)。可重复这些步骤,直到实现所需水平的表面凹陷R(例如,300nm至500nm)。然后,使用氮化物蚀刻以去除氮化物。

然后在衬底上表面中形成鳍。具体地,交叉鳍形成在存储器区域中,而平行鳍形成在逻辑区域中。二氧化硅(氧化物)层46形成于衬底42的所有四个区域(存储器区域、HV区域、逻辑核心区域和逻辑IO区域)中的上表面上。在氧化物层46上形成氮化硅(氮化物)层48。在氮化物层48上形成硬掩模材料(例如,无定形碳)50。在硬掩模材料上形成光致抗蚀剂52,并使用掩模步骤对其进行图案化以暴露硬掩模材料条,如图5A和图5B所示。执行蚀刻以去除硬掩模材料的曝光部分,留下如图6A和图6B所示的硬掩模材料条(在光致抗蚀剂去除之后)。

氧化物层54形成在结构上方。该层在逻辑区域中是共形的,因为硬掩模材料条之间的间距大于存储器区域(其中层填充硬掩模材料条之间的空间)中的间距,如图7A和图7B所示。接下来进行各向异性氧化物蚀刻,这在硬掩模条的竖直侧壁上留下间隔物。使用碳湿条蚀刻来去除碳硬掩模材料,如图8A和图8B所示。存储器区域中的图6A中的两个相邻图案之间的间距优选地小于或等于氧化物层54的厚度的两倍,以便形成如图8A所示的合并间隔物。光致抗蚀剂形成在结构上方并且被图案化以留下光致抗蚀剂条,该光致抗蚀剂条覆盖存储器区域中的交替氧化物间隔物/块并且可能覆盖逻辑区域中的部分氧化物间隔物。然后使用氧化物蚀刻去除由光致抗蚀剂暴露的那些留下的氧化物间隔物。在去除光致抗蚀剂之后,执行一次或多次蚀刻以去除不在氧化物间隔物下方的氮化物48、氧化物46和衬底42的上部部分的那些部分,这导致形成延伸到衬底中的沟槽56,并且在相邻沟槽56之间形成衬底42的薄鳍结构58。鳍58在存储器区域中在竖直/列方向和水平/行方向两者上延伸。所得结构示于图9A至图9B中(在去除氧化物间隔物之后)。图9C示出了存储器区域的顶视图,其中鳍58以网格图案在行和列方向上延伸(即,具有在列方向上延伸的长度的竖直延伸的鳍与具有在行方向上延伸的长度的水平延伸的鳍以网格状方式相交)。在存储器区域中,每个鳍58的最终宽度可为大约10nm至50nm。

虽然图9B仅示出HV区域、逻辑核心区域和逻辑IO区域中的每一者中的一个鳍58,并且图9A仅示出存储器区域中的两个鳍58,但在每个区域中形成有多个鳍。虽然未示出,但是鳍之间的间距将基于区域而变化。例如,逻辑核心区域中相邻鳍之间的距离优选地为存储器区域中分开相邻鳍的距离的大约一半。在这些结构上方形成绝缘材料60(例如,氧化物)(包括用氧化物60填充沟槽56),然后进行氧化物平坦化(例如,CMP)以去除氮化物48的顶部上的氧化物60的任何部分。在逻辑区域上方而不在存储器区域上方形成硬掩模层(例如,氮化物)62。然后使用氧化物蚀刻来使存储器区域中的氧化物60凹陷(即,去除该氧化物的上部部分)。所得结构在图10A和图10B中示出。

去除存储器区域中的鳍56的顶部上的氮化物48和氧化物46(使用光致抗蚀剂来保护逻辑区域中的氮化物层62)。然后在存储器区域中的每个鳍58的两个侧表面和顶表面上形成氧化物层64(例如,通过氧化)。然后在结构上(包括在氧化物64上)形成多晶硅(poly)共形层66,如图11A至图11D所示。然后执行多晶硅层60的原位掺杂。执行掩模步骤和多晶硅蚀刻以去除存储器区域中的沟槽56的底部中(鳍58之间)的多晶硅层66的所选择的部分,如图12A至图12E所示。在这些结构上形成绝缘层67(如,具有氧化物-氮化物-氧化物子层的ONO)。然后在ONO层67(其可经受原位掺杂)上形成多晶硅厚层68。然后,在多晶硅层68上形成硬掩模层69(例如,无定形碳)。所得结构示于图13A至图13E中。

执行掩模步骤和一次或多次蚀刻以沿存储器区域中的鳍58的顶部去除硬掩模层69、多晶硅层68和ONO层67的所选择的部分,从而在存储器区域中的每个鳍58的顶表面上留下成对的栅极堆叠S1和S2,如图14A至图14E所示。执行HTO沉积和退火以沿栅极堆叠S1和S2的侧面形成氧化物层70。执行氮化物沉积和蚀刻以沿氧化物层70形成氮化物层71。通过氧化物沉积和蚀刻沿氮化物层71形成牺牲氧化物间隔物72。所得结构示于图15A至图15E中。

使用掩模步骤在栅极堆叠对S1和S2中的每一者之间形成光致抗蚀剂74。然后执行WLVT植入,之后进行氧化物蚀刻,以去除叠堆对S1和S2的外侧上的氧化物间隔物72,如图16A至图16E所示。在去除光致抗蚀剂之后,使用多晶硅蚀刻(从堆叠S1和堆叠S2之间)去除浮栅多晶硅层66的暴露部分,如图17A至图17E所示。然后通过氧化物沉积和蚀刻沿堆叠S1和S2的侧面形成氧化物间隔物75,如图18A至图18E所示。使用掩模步骤在存储器区域的部分上选择性地形成光致抗蚀剂,然后进行蚀刻以从逻辑区域和存储器区域的所选择的部分去除硬掩模69、多晶硅层68和66以及ONO层67。在去除光致抗蚀剂之后,使用掩模步骤用光致抗蚀剂覆盖除HV区域之外的结构,该HV区域经受氧化物和氮化物蚀刻以去除鳍58上的氮化物和氧化物,并且在鳍58的任一侧上使氧化物60凹陷。然后在HV区域(例如,RTO+HTO和退火)和存储器区域中的暴露的鳍58上形成氧化物层80,如图19A至图19E所示。

使用掩模步骤用光致抗蚀剂覆盖除栅极堆叠对S1和S2中的每一者之间的区域之外的结构。在栅极堆叠对S1和S2中的每一者之间的衬底中执行植入(即,用于形成源极线SL的源极线植入,即,如b横截面所示的源极区;和如a横截面和c横截面所示的在水平/行方向上延伸的鳍58中的源极线)。然后使用氧化物蚀刻来去除同一区域中的间隔物75和72,之后在多晶硅层66的暴露表面以及栅极堆叠S1和S2的内侧壁上形成隧道氧化物层84(例如,通过湿法或部分湿法沉积以使衬底上的氧化物增厚,之后进行HTO沉积以在多晶硅层66上实现期望的厚度),如图20A至图20E所示(在去除光致抗蚀剂之后)。

存储器区域和HV区域被光致抗蚀剂PR覆盖,并且逻辑核心区域和逻辑IO区域经受氧化物蚀刻以凹陷氧化物60,如图21所示。然后执行一个或多个植入(其优选地包括抗穿通植入,该抗穿通植入将在这些区域中形成的逻辑器件中防止源极至漏极泄漏)。在去除光致抗蚀剂之后,在栅极叠堆S1和S2和逻辑区域中的每一者之间的区域中形成光致抗蚀剂PR,之后进行氧化物蚀刻以去除衬底鳍58上的位于叠堆对外部的氧化物,如图22A至图22E所示。然后在存储器区域和HV区域上形成光致抗蚀剂,之后进行氧化物和氮化物蚀刻以去除鳍58上的氧化物和氮化物。然后在逻辑核心区域和逻辑IO区域(以及衬底42的其他暴露部分)中的暴露的鳍58上形成氧化物86,如图23A至图23E所示。逻辑核心区域和逻辑IO区域中的鳍58上的氧化物86比HV区域中的鳍上的氧化物80薄。

在这些结构上形成多晶硅层88,如图24A至图24E所示。使用化学机械抛光(CMP)来去除该结构的上部部分并使该结构平面化,如图25A至图25E所示。掩模步骤和多晶硅蚀刻用于去除多晶硅层88在相邻栅极叠堆对之间的一部分,从而在栅极叠堆S1和S2中的每一者之间留下多晶硅块88a,并且在每对栅极叠堆S1和S2的外部部分上留下多晶硅块88b和88c,如图26A和图26B所示。多晶硅蚀刻还去除逻辑区域中的鳍58上的多晶硅层88的部分,留下多晶硅块88d,如图26C所示。使用一个或多个掩模和植入步骤选择性地将衬底植入逻辑区域中。

执行一次或多次植入以在用于存储器单元和逻辑器件的衬底42中形成源极区和漏极区。具体地,存储器单元漏极区38与多晶硅块88b和88c相邻地形成。逻辑源极区和逻辑漏极区形成在与剩余多晶硅块88d相邻的HV、逻辑核心区域和逻辑IO区域中。绝缘层(例如,氧化物)98形成在这些结构上方并且平面化(例如,通过将多晶硅块88用作研磨终止的CMP)。自对准多晶硅化物100优选地形成在多晶硅块88和68的暴露表面上。所得结构在图27A和图27B中示出。

附加的绝缘材料形成在该结构上方。接触孔形成在绝缘材料中,该接触孔延伸到漏极区38以及多晶硅块88和68并暴露漏极区38以及多晶硅块88和68。优选地,可将用于逻辑器件和存储器单元的漏极区的鳍的源极区和漏极区至少部分地蚀刻掉,随后进行SiGe(用于PFet器件)或SiC(用于NFet器件)外延处理,以形成存储器单元的凸起漏极区38a以及逻辑器件的凸起源极区和漏极区,这引起改善迁移率(即,减小串联电阻)的压缩应力或拉伸应力。然后用金属填充接触孔以形成电连接到漏极区38以及多晶硅块88和68的金属触点110,如图28所示。

存储器区域42a中的鳍58上的最终结构在图28中示出。存储器单元对沿每个鳍58首尾相接地形成。每个存储器单元包括在源极区36和漏极区38之间延伸的衬底的沟道区112(即,沿源极区/漏极区36/38之间的鳍58的两个侧表面和顶表面的衬底的那些部分)。多晶硅66是浮栅28,其设置在沟道区112的第一部分之上并与其绝缘。多晶硅68是控制栅30,其在浮栅28上方延伸并与其绝缘。多晶硅88b/c各自为选择栅32,该选择栅中的每个选择栅设置在沟道区112的第二部分上方并且与该沟道区的第二部分绝缘。多晶硅88a各自为擦除栅34,该擦除栅中的每个擦除栅与一对浮栅28相邻并绝缘,并且在源极区36上方且与源极区绝缘。擦除栅34包括面向浮栅的拐角的凹口。鳍58具有两个相对的侧表面和一个顶表面。浮栅28缠绕在鳍58周围,使得其与鳍58的两个相对的侧表面以及顶表面相邻并绝缘。选择栅32也缠绕在鳍58周围,使得其与鳍58的两个相对的侧表面以及顶表面相邻并绝缘。因此,本配置的一个优点是沟道区112的表面积相对于平面沟道区上方的相等尺寸的存储器单元在尺寸上更大(即,浮动栅和选择栅与衬底之间的表面重叠量大于由这些元件占据的衬底的水平面积)。

HV区域42b、逻辑核心区域42c和逻辑IO区域42d中的鳍58上和周围的最终结构的相似之处在于,栅极各自缠绕在相应鳍58周围,使得其与鳍58的两个相对的侧表面和顶表面相邻并绝缘。因此,本配置的另一个优点是,逻辑器件中的每个逻辑器件的沟道区的表面积相对于平面沟道区上方的相等尺寸的逻辑器件在尺寸上更大(即,逻辑栅和衬底之间的表面重叠量大于该元件所占据的衬底的水平面积)。对于更高的电压操作,HV区域中的栅极氧化物80比其他逻辑区域中的栅极氧化物86厚。每个逻辑器件包括逻辑源极区和逻辑漏极区,两者间具有逻辑沟道区。

其他优点包括缠绕在鳍58的顶部和两个侧表面周围的共形栅极形成在存储器区域(即,浮栅和选择栅)和逻辑区域(即,逻辑栅)两者中。此外,通过使鳍在存储器区域中凹陷,即使存储器单元的栅极叠堆高于逻辑器件的逻辑栅,存储器单元的顶部和逻辑器件也大致彼此相等。此外,存储器单元和三种不同类型的逻辑器件均形成在相同半导体衬底的鳍形衬底结构上,其中每个存储器单元形成在单个鳍上,并且每个逻辑器件形成在单个鳍上,这使得鳍间间距能够减小。

最后,源极线SL中的每一源极线沿水平延伸的鳍58中的一个鳍延伸并且穿过一行存储器单元,从而提供连续源极线,该连续源极线延伸跨过相邻单元之间的隔离区(在行方向上)。这允许将单元按比例缩小到较小尺寸,因为这种配置不需要形成每对存储器单元的源极线触点。相反,沿鳍延伸的连续源极线可通过周期性条带接触(例如,每32或64列)电连接到条带。通过每32或64列具有一次接触而不是每列具有一次接触,尺寸是存储器单元,因此可以显著减小存储器单元的存储器阵列。

应当理解,本发明不限于上述的和在本文中示出的实施方案,而是涵盖在由此支持的任何权利要求书的范围内的任何和所有变型形式。例如,对本文中本发明的引用不旨在限制任何权利要求书或权利要求术语的范围,而是仅参考可由一项或多项权利要求书覆盖的一个或多个特征。上文所述的材料、工艺和数值的示例仅为示例性的,而不应视为限制任何权利要求。另外,并非所有方法步骤都需要按所示的准确顺序执行。鳍可在存储器区域和逻辑区域之间连续延伸。例如,存储器区域(其上形成有存储器单元)中的一个或多个鳍可连续地延伸出存储器区域并进入逻辑区域(其上形成有逻辑器件),在这种情况下,存储器设备和逻辑器件可形成在同一连续形成的鳍上。最后,单个材料层可被形成为多个此类或类似材料层,反之亦然。

应当指出的是,如本文所用,术语“在…上方”和“在…上”均包括性地包括“直接在…上”(之间没有设置中间材料、元件或空间)和“间接在…上”(之间设置有中间材料、元件或空间)。类似地,术语“相邻”包括“直接相邻”(之间没有设置中间材料、元件或空间)和“间接相邻”(之间设置有中间材料、元件或空间),“被安装到”包括“被直接安装到”(之间没有设置中间材料、元件或空间)和“被间接安装到”(之间设置有中间材料、元件或空间),并且“被电耦接到”包括“被直接电耦接到”(之间没有将元件电连接在一起的中间材料或元件)和“被间接电耦接到”(之间有将元件电连接在一起的中间材料或元件)。例如,“在衬底上方”形成元件可包括在两者间无中间材料/元件的情况下直接在衬底上形成该元件,以及在两者间有一种或多种中间材料/元件的情况下间接在衬底上形成该元件。

- 具有三维鳍式场效应晶体管结构的分裂栅非易失性存储器单元及其制造方法

- 具有鳍式场效应晶体管结构和HKMG存储器和逻辑栅的分裂栅非易失性存储器单元及其制备方法