一种区分主机写入操作的AHB-to-APB转换桥

文献发布时间:2023-06-19 10:19:37

技术领域

本发明涉及芯片设计技术领域,特别涉及一种区分主机写入操作的AHB-to-APB转换桥。

背景技术

随着深亚纳米工艺制造技术的飞速发展,集成电路芯片的规模也越来越大。AMBA(Advanced Microcontroller Bus Architecture,片上总线协议)总线作为一种应用最广泛的总线协议,是由ARM公司提出的一个SoC体系结构开放标准。AHB-to-APB转换桥则是连接AMBA总线上AHB和APB的桥梁,其对整个系统的传输效率有着重要的影响。

当前总线桥的设计大致分为不带缓存的总线桥和带缓存的总线桥。不带缓存的总线桥结构简单,它能单独处理每一个读写操作,每次读写操作都需要等到APB执行完毕才释放AHB总线。该传输方法稳定可靠,但是对于高分频的情况下,对于主机的挂起时间太长,严重影响主机的执行效率。带缓存的总线桥有带一级缓存也有带多级或者带FIFO的结构。它能存储AHB总线上的写传输,并且在APB空闲的时候去完成滞留的操作。该传输方法高效快速,但是对于主机需要确定APB上的外设是否已经写入的应用无法满足。

发明内容

本发明的目的在于提供一种区分主机写入操作的AHB-to-APB转换桥,以解决背景技术的问题。

为解决上述技术问题,本发明提供了一种区分主机写入操作的AHB-to-APB转换桥,包括AHB总线和APB总线;

所述AHB总线在传输时分为地址周期和数据周期,地址周期产生地址信号和各类控制信号,数据周期用于上个地址的数据读写,地址周期和数据周期交替并行出现,以增加数据的吞吐量;

所述APB总线在传输时分为选择周期和使能周期,选择周期产生地址信号和各类控制信号,使能周期用于数据读写,选择周期和使能周期交替串行出现;

所述AHB总线和所述APB总线之间通过总线桥来转换控制信号以及传输数据。

可选的,所述AHB总线的地址周期的信号通过寄存器REG_OUT传输到所述APB总线上。

可选的,所述AHB总线和所述APB总线之间还设有一级寄存器REG_LOCK,若当前有一个带缓存的写传输时,用于缓存下一次传输的地址和控制信号。

可选的,所述AHB总线上的数据信号HWDATA通过组合逻辑直接产生PWDATA至所述APB总线。

可选的,所述AHB总线和所述APB总线之间还设有一级寄存器REG_LOCK,若当前有一个带缓存的写传输时,缓存一次数据信号。

可选的,AHB-to-APB转换桥区分当前的主机和读写操作来控制HREADY信号,如当前是一次带缓存的写操作,则保持HREADY信号有效,所述AHB总线处于空闲状态;如当前是一次不带缓存的写操作或者读操作时,则使HREADY信号无效,所述AHB总线处于忙碌状态,阻止主机再次传输。

可选的,所述AHB-to-APB转换桥中的状态机存在四种状态:

IDEL状态:APB总线处于空闲状态;

WAIT_PCLKEN状态:AHB总线发出读写请求,等待APB总线响应;

SEL_STA状态:APB总线开始读写传输;

ENABLE_STA状态:APB总线正在读写传输。

可选的,所述状态机处于IDLE状态时,若AHB总线无有效传输信号,则状态机始终处于IDLE状态;若AHB总线接收到传输请求信号并且PCLKEN信号无效,则状态机跳转至WAIT_CLK_EN状态;若AHB总线接收到传输请求信号并且PCLKEN信号有效,则状态机跳转至APB_SEL_STA状态;

在状态机处于WAIT_CLK_EN状态时,若PCLKEN信号无效,则状态机始终处于WAIT_CLK_EN状态;若PCLKEN信号有效,则状态机跳转至APB_SEL_STA状态;

在状态机处于APB_SEL_STA状态时,若PCLKEN信号无效,则状态机始终处于APB_SEL_STA状态;若PCLKEN信号有效,则状态机跳转至APB_ENABLE_STA状态;

在状态机处于APB_ENABLE_STA状态时,若PCLKEN信号无效或者APB总线未传输完成时,APB总线始终处于APB_ENABLE_STA状态;若PCLKEN信号有效并且APB总线传输完成时,当前有缓存的AHB传输或者正好有下一次AHB传输时,状态机跳转至APB_SEL_STA状态;若PCLKEN信号有效并且APB总线传输完成时,没有任何新的传输请求,则状态机跳转至IDLE状态。

可选的,所述APB总线的时钟频率能够动态调节,与所述AHB总线相同,或经过分频后产生该APB总线的时钟频率。

在本发明提供的区分主机写入操作的AHB-to-APB转换桥中,包括AHB总线和APB总线;所述AHB总线在传输时分为地址周期和数据周期,地址周期产生地址信号和各类控制信号,数据周期用于上个地址的数据读写,地址周期和数据周期交替并行出现,以增加数据的吞吐量;所述APB总线在传输时分为选择周期和使能周期,选择周期产生地址信号和各类控制信号,使能周期用于数据读写,选择周期和使能周期交替串行出现;所述AHB总线和所述APB总线之间通过总线桥来转换控制信号以及传输数据。为了满足不同主机对于外设访问的时的需求,本发明中的AHB-to-APB转换桥可以通过对HREADY信号的控制来区分不同主机的写入操作;其电路结构简单,并且可以支持同频和分频;在电路中增加了一级缓存,控制方法简单,传输可靠。

附图说明

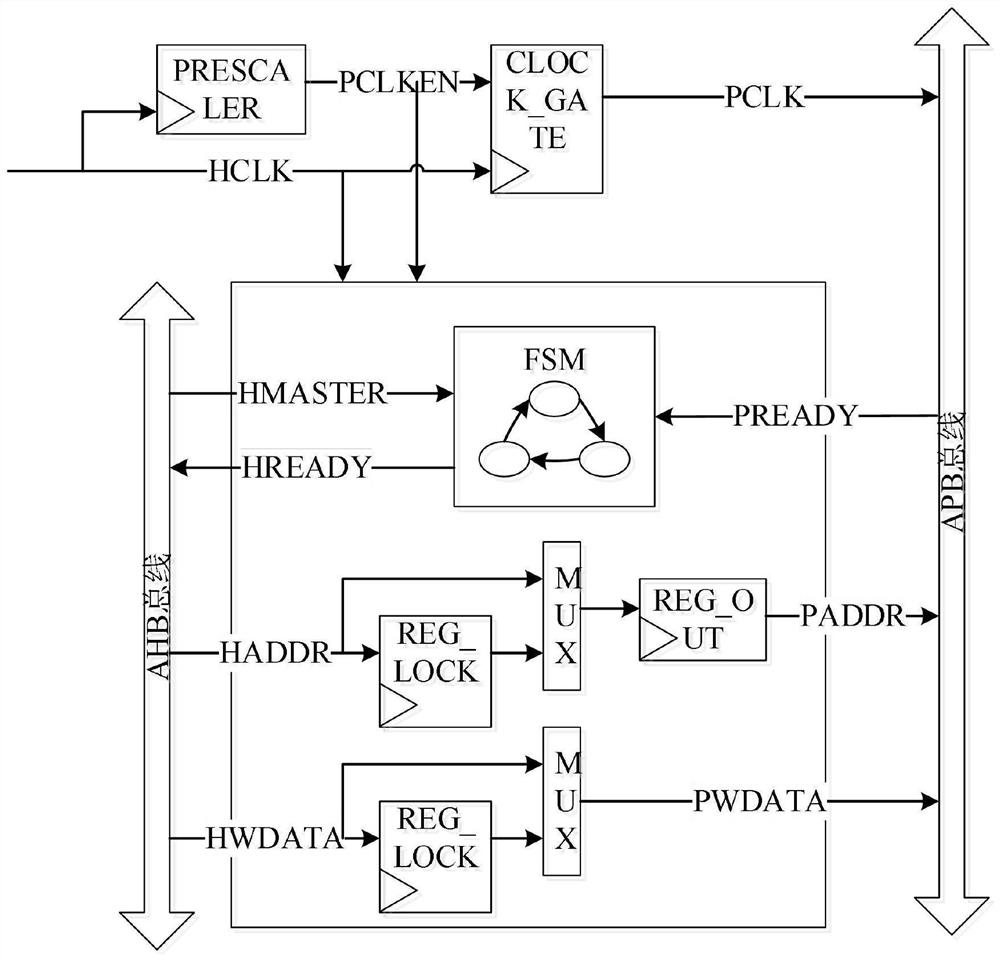

图1是本发明提供的区分主机写入操作的AHB-to-APB转换桥结构框图;

图2是AHB-to-APB转换桥的状态机的跳转图;

图3是AHB-to-APB转换桥上的数据传输情况示意图;

图4是AHB-to-APB转换桥上的数据传输情况Ⅰ的传输时序图;

图5是AHB-to-APB转换桥上的数据传输情况Ⅱ的传输时序图;

图6是AHB-to-APB转换桥上的数据传输情况Ⅲ的传输时序图;

图7是AHB-to-APB转换桥上的数据传输情况Ⅳ的传输时序图;

图8是AHB-to-APB转换桥上的数据传输情况Ⅴ的传输时序图。

具体实施方式

以下结合附图和具体实施例对本发明提出的一种区分主机写入操作的AHB-to-APB转换桥作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

实施例一

本发明提供了一种区分主机写入操作的AHB-to-APB转换桥,其设计框图如图1所示,包括AHB总线和APB总线。AHB总线是一种支持多主机和提供高带宽操作的高性能总线,在其传输时分为地址周期和数据周期,地址周期产生地址信号和各类控制信号,数据周期用于上个地址的数据读写,地址周期和数据周期交替并行出现,相当于2级流水,从而能够增加数据的吞吐量。所述APB总线是一种功耗低,接口复杂度低的低速总线,在其传输时分为选择周期和使能周期,选择周期产生地址信号和各类控制信号,使能周期用于数据读写,选择周期和使能周期交替串行出现;所述AHB总线和所述APB总线之间通过总线桥来转换控制信号以及传输数据。AHB-to-APB转换桥区分当前的主机和读写操作来控制HREADY信号,如当前是一次带缓存的写操作,则保持HREADY信号有效,所述AHB总线处于空闲状态;如当前是一次不带缓存的写操作或者读操作时,则使HREADY信号无效,所述AHB总线处于忙碌状态,阻止主机再次传输。所述APB总线的时钟频率能够动态调节,与所述AHB总线相同,或经过分频后产生。

所述AHB总线的地址周期的信号通过寄存器REG_OUT传输到所述APB总线上。所述AHB总线和所述APB总线之间还设有一级寄存器REG_LOCK,若当前有一个带缓存的写传输时,用于缓存下一次传输的地址和控制信号。所述AHB总线上的数据信号HWDATA通过组合逻辑直接产生PWDATA至所述APB总线。所述AHB总线和所述APB总线之间还设有一级寄存器REG_LOCK,若当前有一个带缓存的写传输时,缓存一次数据信号。

请继续参阅图1,HCLK是AHB总线的时钟,HCLK驱动分频计数器(即PRESCALER),计数器根据需要分频的系数递减,当减到0时,产生PCLKEN。PCLKEN为脉冲信号,其作为时钟门控(CLOCK_GATE)的使能端,产生PCLK,PCLK是APB总线的时钟信号;同时,PCLKEN作为控制信号送给AHB-to-APB转换桥。

如图2所示为AHB-to-APB转换桥中状态机的跳转图,所述状态机存在四种状态:

IDEL状态:APB总线处于空闲状态;

WAIT_PCLKEN状态:AHB总线发出读写请求,等待APB总线响应;

SEL_STA状态:APB总线开始读写传输,并且处于PSEL阶段;

ENABLE_STA状态:APB总线正在读写传输,并且处于PENABLE阶段。

所述状态机处于IDLE状态时,若AHB总线无有效传输信号(条件Ⅰ),则状态机始终处于IDLE状态;若AHB总线接收到传输请求信号并且PCLKEN信号无效(条件Ⅱ),则状态机跳转至WAIT_CLK_EN状态;若AHB总线接收到传输请求信号并且PCLKEN信号有效(条件Ⅲ),则状态机跳转至APB_SEL_STA状态;

在状态机处于WAIT_CLK_EN状态时,若PCLKEN信号无效(条件Ⅰ),则状态机始终处于WAIT_CLK_EN状态;若PCLKEN信号有效(条件Ⅱ),则状态机跳转至APB_SEL_STA状态;

在状态机处于APB_SEL_STA状态时,若PCLKEN信号无效(条件Ⅰ),则状态机始终处于APB_SEL_STA状态;若PCLKEN信号有效(条件Ⅱ),则状态机跳转至APB_ENABLE_STA状态;

在状态机处于APB_ENABLE_STA状态时,若PCLKEN信号无效或者APB总线未传输完成时(条件Ⅰ),APB总线始终处于APB_ENABLE_STA状态;若PCLKEN信号有效并且APB总线传输完成时,当前有缓存的AHB传输或者正好有下一次AHB传输时(条件Ⅱ),状态机跳转至APB_SEL_STA状态;若PCLKEN信号有效并且APB总线传输完成时,没有任何新的传输请求,则状态机跳转至IDLE状态。

图3为该AHB-to-APB转换桥上的数据传输情况,大致可以分为五种。BW(包括BW1和BW2)传输表示不会把HREADY信号置为无效的写传输,该传输执行的过程可以响应下一次传输;W传输表示会把HREADY信号置为无效的写传输,该传输需要传输完成以后才可以响应下一次传输;R传输表示读传输。方框内字幕“S”表示开始周期,“E”表示结束周期,无色方框表示正在进行的传输,带斜线的方框表示在缓存中的传输。情况Ⅰ表示两次不连续的BW传输,中间可以间隔多个时钟周期或者0个时钟周期(即ncycle);情况Ⅱ表示两次首尾相交的BW传输;情况Ⅲ表示在一次BW传输的过程中发起另一次BW传输;情况Ⅳ表示在第一次BW传输的过程中发起一次BW传输,并且在第二次BW传输刚开始的时候又发起一次BW传输;情况Ⅴ表示在一次BW传输的过程中发起一次R/W传输。

图4为情况Ⅰ的时序图,情况Ⅰ与情况Ⅱ未使用地址缓存寄存器。AHB_TRANS_TRIG表示主机有传输请求;AHB_TRANS_END表示当前AHB总线上的传输已经完成;HADDR_LOCK是缓存地址信号的寄存器;PADDR_OUT是地址输出寄存器;HWDATA_LOCK是缓存数据信号的寄存器;THROUGHT表示数据从HWDATA直通PWDATA;PWDATA是数据输出信号。在T2时刻,主机发起一次BW传输,AHB_TRANS_TRIG转为高电平一个时钟周期。T3时刻,PADDR_OUT输出HADDR的值,同时PWDATA直接输出HWDATA的值,并且HWDATA_LOCK锁存住HWDATA。T4时刻,PWDATA切换到HWDATA_LOCK的值。在T10时刻,该时刻是本传输的最后一个时钟周期,AHB_TRANS_END转为高电平一个时钟周期。在T11时刻重复T2时刻的过程。在本次传输过程中,由于两次都是BW传输,因此HREADY信号始终有效,不会使主机挂起,保证了系统的效率。

图5为情况Ⅱ的时序图,从T2时刻到T9时刻与情况Ⅰ相同。在T10时刻,该时刻是本传输的最后一个时钟周期,同时主机正好发起一次BW传输。此时AHB-to-APB转换桥直接开始下一次传输,地址不会存入缓存,状态机切换到下一个SEL_STA进行连续传输。同样在本次传输过程中,由于两次都是BW传输,因此HREADY信号始终有效。

图6为情况Ⅲ的时序图,情况Ⅲ与情况Ⅳ需使用地址缓存寄存器。BUFFER_TRIG表示在传输的过程中有AHB_TRANS_TRIG,或者在传输完成同时有BUFFERED_REQ和AHB_TRANS_TRIG;BUFFERED_REQ表示在缓存中的传输发起的请求。从T2时刻到T6时刻与情况Ⅰ相同。在T7时刻,主机发起第二次BW传输,BUFFER_TRIG转为高电平一个时钟周期。在T8时刻,HADDR_LOCK锁存第二次传输的地址信号,同时BUFFERED_REQ有效,由于第一次的传输正在进行,第二次的传输已保存在缓存中,AHB-to-APB转换桥无法接受第三次传输,此时HREADY信号无效。在T10时刻,第一次传输完成,HREADY信号有效。在T11时刻,HWDATA_LOCK缓存第二次传输的数据,同时PADDR_OUT和PWDATA输出缓存在寄存器中的地址和数据信号,BUFFERED_REQ无效。在T13时刻,主机发起第三次传输,本次传输与第二次传输相同。

图7为情况Ⅳ的时序图。从T2时刻到T9时刻与情况Ⅲ相同。在T10时刻,该时刻是本传输的最后一个时钟周期,同时主机正好发起第三次BW传输。在T11时刻,HWDATA_LOCK缓存第二次传输的数据,同时PADDR_OUT和PWDATA输出缓存在寄存器中的地址和数据,BUFFERED_REQ继续有效,并且HADDR_LOCK锁存第三次传输的地址,由于第二次传输正在进行,第三次的传输已保存在缓存中,AHB-to-APB转换桥无法接受第四次传输,此时HREADY信号无效。在T14时刻,第二次传输完成,HREADY信号有效。在T15时刻,HWDATA_LOCK缓存第三次传输的数据,同时PADDR_OUT和PWDATA输出缓存在寄存器中的地址和数据。在T19时刻,第三次传输完成。

图8为情况Ⅴ的时序图。从T2时刻到T6时刻与情况Ⅰ相同。在T7时刻,主机发起第二次W传输,BUFFER_TRIG转为高电平一个时钟周期,同时HREADY信号无效。在T8时刻,HADDR_LOCK锁存第二次传输的地址信号,同时BUFFERED_REQ有效。在T10时刻,第一次传输完成,由于第二次传输不是BW传输,所以HREADY信号保持无效。在T11时刻,HWDATA_LOCK缓存第二次传输的数据,同时PADDR_OUT和PWDATA输出缓存在寄存器中的地址和数据信号,BUFFERED_REQ无效。在T14时刻,第二次传输完成,HREADY信号有效。

上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

- 一种区分主机写入操作的AHB-to-APB转换桥

- 一种主机交互操作方法、系统及中间转换装置