一种互连微焊点、芯片及芯片的焊接方法

文献发布时间:2023-06-19 10:38:35

技术领域

本发明涉及电子元器件的封装技术,尤其涉及一种互连微焊点、芯片及芯片的焊接方法。

背景技术

随着电子元器件的封装技术的不断进步,三维集成封装已变得越来越受大众的欢迎,三维集成封装对系统性能具有优势,包括外形尺寸小、异质集成以及显著降低系统集成成本和功耗。因此,用于倒装芯片键合的焊点的间距尺寸应该减小。

通常,在倒装芯片键合中使用高度为几微米且具有锡(Sn)或锡-铜(Sn-Ag)帽的铜(Cu)柱凸点。铜/锡(Cu/Sn)或者锡/银(Sn-Ag)柱微凸点的倒装焊形成了铜-锡-铜(Cu-Sn-Cu)互连结构。在铜-锡(Cu-Sn)或锡-铜(Sn-Cu)的界面处形成了Cu

因此,如何消除互连微焊点之间的孔洞成为一个急需解决的问题。

发明内容

本发明提供了一种互连微焊点、芯片及芯片的焊接方法,以解决上述背景技术中存在的问题。

为了实现上述目的,本发明通过如下的技术方案来实现:

本发明提供一种互连微焊点,包括第一铜层、第一阻挡层、第一锡层、第二锡层、第二阻挡层以及第二铜层,所述第一阻挡层设于所述第一铜层上,所述第一锡层设于所述第一阻挡层上,所述第二阻挡层设于所述第二铜层上,所述第二锡层设于所述第二阻挡层上,在焊接状态下,所述第一锡层与所述第二锡层键合于一体。

可选地,所述第一阻挡层为镍层、金层或者银层中的至少一种。

可选地,所述第二阻挡层为镍层、金层或者银层中的至少一种。

可选地,所述镍层、所述金层或者所述银层的厚度大于或等于2um。

可选地,所述第一铜层和/或所述第二铜层的材料包括锌。

作为一个总的发明构思,本申请还提供一种芯片,包括如上所述的互连微焊点。

作为一个总的发明构思,本申请还提供一种互连微焊点的焊接方法,包括:

形成第一铜层和第二铜层;

在所述第一铜层上电镀第一阻挡层,在所述第二铜层上电镀第二阻挡层;

在第一阻挡层上电镀第一锡层,在第二阻挡层上电镀第二锡层;

使所述第一锡层和所述第二锡层键合于一体。

可选地,所述使所述第一锡层和所述第二锡层键合于一体,包括:

采用热压焊基于预设温度在设定的键合时间内键合所述第一锡层和所述第二锡层。

可选地,所述预设温度高于锡的熔点,所述键合时间为5-20s。

有益效果:

本发明提供了一种互连微焊点、芯片及芯片的焊接方法,该互连微焊点包括第一铜层、第一阻挡层、第一锡层、第二锡层、第二阻挡层以及第二铜层,第一阻挡层设于第一铜层上,第一锡层设于第一阻挡层上,第二阻挡层设于第二铜层上,第二锡层设于第二阻挡层上,在焊接状态下,第一锡层与第二锡层键合于一体。这样,可以通过第一阻挡层和第二阻挡层抑制互连微焊点之间的孔洞,能防止由于孔洞扩散成裂纹影响芯片结构。

附图说明

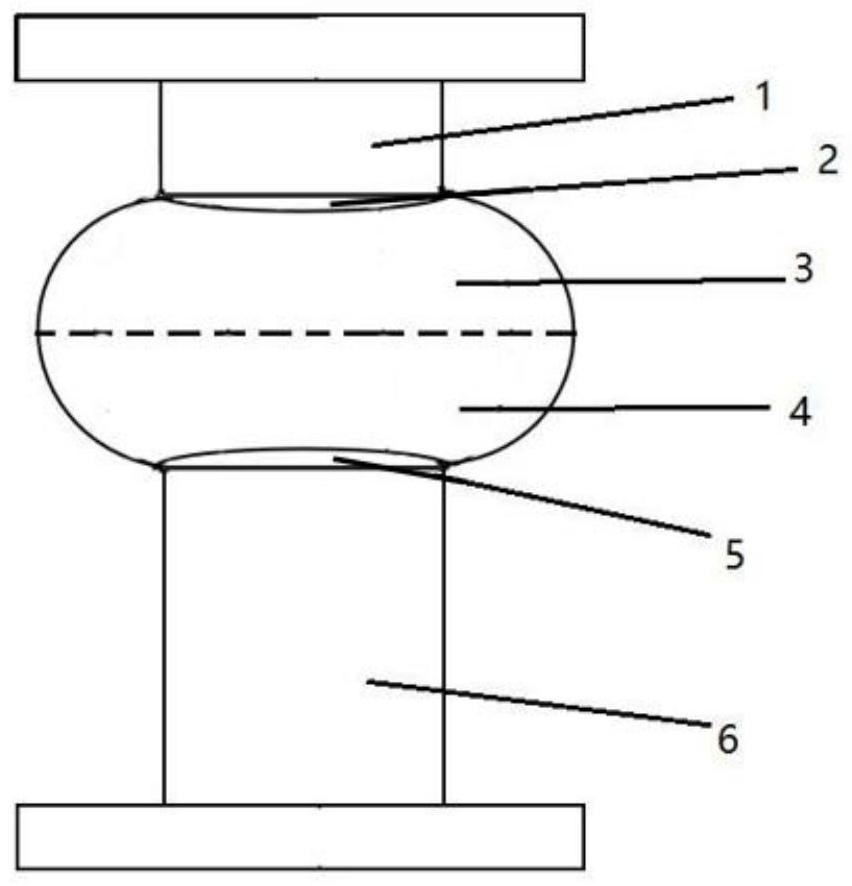

图1为本发明优选实施例的互连微焊点的结构示意图。

附图标记:

1、第一铜层;2、第一阻挡层;3、第一锡层;4、第二锡层;5、第二阻挡层;6、第二铜层。

具体实施方式

下面对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

如图1所示,本发明提供了一种互连微焊点,包括第一铜层1、第一阻挡层2、第一锡层3、第二锡层4、第二阻挡层5以及第二铜层6,第一阻挡层2设于第一铜层1上,第一锡层3设于第一阻挡层2上,第二阻挡层5设于第二铜层6上,第二锡层4设于第二阻挡层5上,在焊接状态下,第一锡层3与第二锡层4键合于一体。

在该实施方式中,第一铜层1和第二铜层6的材料为铜(Cu),第一锡层3和第二锡层4的材料为(Sn)。需要说明的是,该互连微焊点的两端连接两个芯片,例如,第一铜层1、第一阻挡层2、第一锡层3设于第一个芯片上,第二锡层4、第二阻挡层5以及第二铜层6设于第二个芯片上,在封装时,将第一锡层3与第二锡层4键合于一体,即可实现这两个芯片的集成。

上述的互连微焊点,通过第一阻挡层2和第二阻挡层5抑制互连微焊点之间的孔洞,能防止由于孔洞扩散成裂纹影响芯片结构。

可选地,第一阻挡层2为镍层、金层或者银层中的至少一种。

也就是说,对于第一阻挡层2的材料,可以为镍(Ni),也可以为金(Au),也可以为银(Ag),还可以是该三者中任意两者或者三者的组合,此处,仅作示例不做限定,可变换地,在其他可行的实施方式中,还可以对第一阻挡层2的材料做适当调整,但不论其作何变换,都在本申请实施例保护的范围之内。

由于在相同键合温度下,Ni,Au在钎料中的扩散系数和溶解度非常低,在该实施方式中,通过设置第一阻挡层2,可防止Sn和Cu的相互扩散,可以阻止第一铜层1和第一锡层3之间的中间化合物(IMC)的形成,防止生成孔洞,并为芯片的封装提供耐用的导电表面。

可选地,第二阻挡层5为镍层、金层或者银层中的至少一种。

也就是说,对于第二阻挡层5的材料,可以为镍(Ni),也可以为金(Au),也可以为银(Ag),还可以是该三者中任意两者或者三者的组合,此处,仅作示例不做限定,可变换地,在其他可行的实施方式中,还可以对第二阻挡层5的材料做适当调整,但不论其作何变换,都在本申请实施例保护的范围之内。

在该实施方式中,通过设置第二阻挡层5可以阻止第二铜层6和第二锡层4之间的中间化合物(IMC)的形成,防止生成孔洞。

可选地,镍层、金层或者银层的厚度大于或等于2um。具体地,其厚度根据互连微焊点的大小确定,例如,当互连微焊点的直径在15-100um时,可以使第一阻挡层2或者第二阻挡层5的厚度为2um。

可选地,在另一个可行的实施方式中,第一铜层1和/或第二铜层6的材料包括锌。也就是说,可以在第一铜层1的材料中加入锌(Zn),也可以在第二铜层6的材料中加入锌(Zn),还可以在第一铜层1的材料和第二铜层6的材料中都加入锌(Zn),这样,可以防止在第一铜层1与第一锡层3之间,或者在第二铜层6与第二锡层4之间,生成中间化合物(IMC)。

本申请实施例还提供一种芯片,该芯片包括如上所述的互连微焊点。由于本实施例的技术方案包含了上述实施例的全部技术方案,因此至少能实现上述实施例的全部技术效果,此处不再一一赘述。

本申请实施例还提供一种芯片的焊接方法,包括:

形成第一铜层1和第二铜层6;

在第一铜层1上电镀第一阻挡层2,在第二铜层6上电镀第二阻挡层5;

在第一阻挡层2上电镀第一锡层3,在第二阻挡层5上电镀第二锡层4;

使第一锡层3和第二锡层4键合于一体。

需要说明的是,现有Cu-Sn-Cu互连结构的中间化合物IMC随着初始厚度和键合温度的生长速率较快,采用上述方法在Cu/Sn层中间加入Ni层后,可以降低IMC的生长速率。

可变换地,在另一个可行的实施方式中,第一阻挡层2和第二阻挡层5的制备可用电镀,还可以用磁控溅射,CVD(化学气象沉积)等方法实现。此处仅做实例,不做限定。

具体地,使第一锡层3和第二锡层4键合于一体,包括:

采用热压焊基于预设温度在设定的键合时间内键合第一锡层3和第二锡层4。

具体地,焊点键合方法可用热压焊,键合焊点温度高于Sn焊点熔点,键合间隙以上下焊点完全接触且不溢Sn为宜,键合时间可以是5s~20s。

以上详细描述了本发明的较佳具体实施例。应当理解,本领域的普通技术人员无需创造性劳动就可以根据本发明的构思作出诸多修改和变化。因此,凡本技术领域中技术人员依本发明的构思在现有技术的基础上通过逻辑分析、推理或者有限的实验可以得到的技术方案,皆应在由权利要求书所确定的保护范围内。

- 一种互连微焊点、芯片及芯片的焊接方法

- 一种具有记忆特性的芯片叠层封装互连焊点的制备方法