一种三维集成电路及其制造方法

文献发布时间:2023-06-19 10:44:55

技术领域

本发明属于半导体制造工艺和集成电路封装工艺技术领域,具体涉及一种三维集成电路及其制造方法。

背景技术

随着半导体行业的迅猛发展,器件越来越趋于微小型化,I/O数逐步增加。集成电路的发展趋势也一直遵循着摩尔定律,集成电路的密度逐渐提高。这种集成度提高的主要驱动力是特征尺寸的不断减小,在一个特定的区域中能够集成更多的器件,但这主要是在二维方向上的集成,集成密度无法进一步的提高下去。目前感存算一体电路系统主要的封装方式,都是采用二维集成的方法,图1为该方法的剖视图。如图1所示,将CIS管芯2(晶圆切割后得到的部分称为管芯,die)、硅光电池管芯3、忆阻器存算一体管芯4、蓝牙数据传输管芯5都通过引线键合单独封装出来得到单独的电路元器件。将管芯封装完成之后,通过表面贴装工艺(SMT,Surface Mounted Technology)将每个分立元件焊接在印刷电路板1(PCB,Print Circuit Board)上。

目前的技术存在以下问题:

现有的感存算一体系统的集成方法,成本较高,每一个独立的裸芯片都需要先封装出来,然后再焊接到PCB板上,在二维方向上提高集成度的同时也增加了整个存算一体系统的面积,不能做到高密度的集成,因此存储和计算能力无法进一步提高,无法满足现有的需求。

因此,目前急需一种将供能芯片,传感芯片,存储芯片,计算芯片,以及数据传输芯片高密度集成的三维集成电路结构,以满足日益发展的能感存算一体系统的要求。

发明内容

为了解决现有技术的问题,本发明提供了一种三维集成电路及其制造方法。

本发明采用的技术方案是:

一种三维集成电路,包括FPC柔性基板,封装在FPC柔性基板上的多种芯片的管芯;其特征在于,所述FPC柔性基板通过弯折的方式,形成在同一垂直面平行并列的多层电路板结构,每层电路板之间通过FPC柔性基板的弯折部分首尾相连;在每一层电路板沿水平面的直线部分,间隔封装芯片的管芯,相邻管芯之间具有间距,且管芯是通过倒装焊的封装方法集成在FPC柔性基板正反面对应的位置上,每个管芯的边缘涂抹有环氧树脂胶;沿垂直方向,上下相邻的每层电路板之间填充有电气绝缘材料。

进一步的,所述三维集成电路通过引线键合的方式整合为一个封装体;三维集成电路的引线由FPC柔性基板两端引出,即弯折次数为偶数时,引线由集成电路两端引出,弯折次数为奇数时,引线由集成电路一侧引出,弯折次数对应了电路板的层数。

进一步的,所述三维集成电路通过BGA焊接的方法焊接在PCB板上。

进一步的,所述电气绝缘材料为涤纶树脂PET、环氧树脂、聚酰亚胺PI中的一种。

进一步的,所述管芯包括供能芯片的管芯、传感芯片的管芯、存储芯片的管芯和计算芯片的管芯。

进一步的,所述管芯包括硅光电池芯片的管芯、CIS芯片的管芯、忆阻器存算一体芯片的管芯、蓝牙数据传输芯片的管芯,且硅光电池芯片的管芯和CIS芯片的管芯上方的电气绝缘材料具备可透光的特性。

一种三维集成电路的制造方法,包括以下步骤:

S1、选取FPC柔性基板;

S2、在FPC柔性基板上制备电路图形;

S3、通过凸点制作方法,将硅光电池芯片的管芯、CIS芯片的管芯、忆阻器存算一体芯片的管芯、蓝牙数据传输芯片的管芯利用倒装焊的封装方法集成在FPC柔性基板正反面对应的位置上;

S4、在各个管芯的边缘涂抹环氧树脂胶,利用毛细作用原理让其渗透到管芯和凸点之间的位置,然后加热固化;

S5、对管芯和管芯间距中间处的FPC柔性基板加热,并在FPC柔性基板的一侧末端施加拉力将FPC柔性基板进行弯折,形成在同一垂直面平行并列的多层电路板结构,每层电路板之间通过FPC柔性基板的弯折部分首尾相连;

S6、沿垂直方向,在上下相邻的电路板之间空隙中填充电气绝缘材料;

S7、在电气绝缘材料材料和FPC柔性基板之间的空隙中填充环氧树脂胶,并沿垂直方向,在FPC柔性基板的上下两端施加压力,然后加热固化。

本发明的有益效果在于:本发明为利用CMOS图像传感器为传感模块、忆阻器器件作为存储单元,再辅以相应运算单元,在单片上实现了感存算一体电路。相比于传统的存内计算电路,该设计将传感与存内计算融为一体,能够极大地提高电路对传感数据的运算速度,且集成度高、结构简单、功耗低。

附图说明

图1是目前传统感存算一体电路系统结构主要的封装和集成的方式;

图2是将硅光电池芯片、CIS芯片、忆阻器存算一体芯片、蓝牙数据传输芯片平面集成在基底上的示意图;

图3是在各个芯片凸点之间填充环氧树脂胶的示意图;

图4是将FPC柔性基底弯折成U形的过程示意图;

图5是将FPC柔性基底加热加压定形后的示意图;

图6是将能感传存算一体电路系统所用的芯片集成后形成的蛇形结构的示意图;

图7是在已折叠基底上下部分之间空隙中填充电气绝缘材料的示意图;

图8是在电气绝缘材料和FPC柔性基底空隙中填充环氧树脂胶的示意图;

图9是通过引线键合的方法将整个电路系统连接在封装基板上的示意图;

图10是将封装后的电路系统焊接到PCB印刷电路板上的示意图;

图11是折叠次数为奇数时的结构和封装方式的示意图。

具体实施方式

下面结合附图对本发明进一步地详细说明。

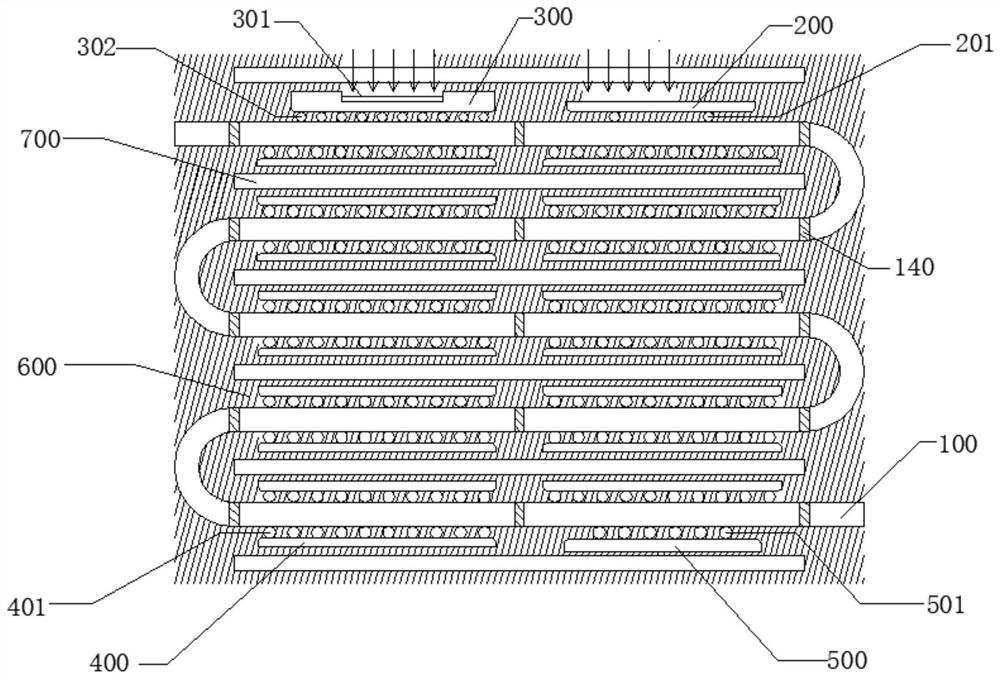

如图2所示,将硅光电池芯片200、CIS芯片300、忆阻器存算一体芯片400、蓝牙数据传输芯片500平面集成在柔性基底100上,将微米量级的pad通过金属图形化工艺引出至毫米量级的焊盘上,并在焊盘上进行机械打孔140从而实现基底上下芯片的电气连接;通过制作第一凸点201,第二凸点302,第三凸点401,第四凸点502分别将对应的管芯倒装焊接在柔性基底100上;首先通过平面工艺集成,和现有的工艺兼容性较高;

如图3所示,在各个芯片凸点之间填充环氧树脂胶600;利用毛细作用原理把环氧树脂胶材料600涂抹在芯片的边缘让其渗透到芯片和凸点之间的位置,然后加热予以固化,它能有效提高焊点的机械强度,从而提高芯片的使用寿命,进一步提高整个能感传存算一体三维集成电路结构的可靠性;

如图4所示,在芯片与芯片间距的中间处加热并在FPC柔性基底100的最右端处加一个圆周力,将基板弯折成U型;加热和加压同时进行,不仅能够使得FPC柔性基底100容易折叠,还能够保证U型结构的均匀性,进一步降低制作过程中的热应力;

如图5所示,通过加热加压将FPC柔性基底100折叠后得到图中所示的U形电路结构;

如图6所示,进一步高密度集成,首先通过上述步骤在平面上大规模集成,然后将FPC柔性基底100折叠多次,得到如图所示的蛇形结构,图中示意的是折叠次数为偶数的情况;大规模集成忆阻器存算一体芯片能够有效提升能感传存算一体三维集成电路结构的计算能力和存储能力;

如图7所示,由于已经折叠后的基底上下管芯以及基板上的Cu箔之间存在电气绝缘的问题,在空隙中填充电气绝缘材料板700能够有效防止上下管芯以及FPC柔性基板Cu箔与Cu箔之间发生短路的现象;

如图8所示,为了使上下管芯之间电气绝缘,并且保证管芯之间的相对位置,在电气绝缘材料600和FPC柔性基底100空隙中填充环氧树脂胶,能够有效提高管芯的使用寿命,进一步提高整个电路系统的可靠性和稳定性;

如图9所示,针对折叠次数为偶数的集成电路系统,引线在两侧引出,通过引线键合的方法将整个电路系统封装在封装基板(Package Substrate,简称PKG基板)上;

如图10所示,将已经封装好的电路系统作为一个分立元件焊接在PCB印刷电路板上;

如图11所示,当折叠次数为奇数时,整个集成电路系统的引线可在一侧引出,通过引线键合的方法将整个电路系统封装在封装基板(Package Substrate,简称PKG基板)上,然后将封装好的电路系统作为一个分立元件焊接在PCB印刷电路板上。

- 三维集成电路、处理器、半导体芯片及三维集成电路的制造方法

- 三维集成电路、处理器、半导体芯片及三维集成电路的制造方法