一种三维存储器及三维存储器的形成方法

文献发布时间:2023-06-19 10:54:12

技术领域

本申请实施例涉及半导体技术领域,涉及但不限于一种三维存储器及三维存储器的形成方法。

背景技术

相变存储器(Phase Change Memory,PCM)由于具有高速读取、高可擦写次数、非易失性、元件尺寸小、功耗低、抗强震动和抗辐射等优点,而被广泛地使用。

相变存储器是利用相变材料的晶态和非晶态的特性来存储数据,例如,对相变材料(Ge

然而,在商用3D X-Point存储器中,相变材料的结晶速度慢,导致PCM SET速度约为几百纳秒,限制了相变存储器的数据写入速率。

发明内容

有鉴于此,本申请实施例提供一种三维存储器及三维存储器的形成方法,能够促进相变材料的结晶速度,提高相变存储器的数据写入速率。

本申请实施例的技术方案是这样实现的:

第一方面,本申请实施例提供一种三维存储器,包括:

多条第一导电线,沿第一方向延伸;

多条第二导电线,沿第二方向延伸;

设置在每一所述第一导电线与对应的所述第二导电线之间、且与所述第一导电线和所述第二导电线均垂直的相变存储单元;其中,所述相变存储单元至少包括沿第三方向依次叠置的存储层和选通层,所述存储层包括交替堆叠的至少一个相变层和至少一个结晶促进层,所述结晶促进层用于促进所述相变层的结晶过程;

所述第三方向与所述第一方向和所述第二方向两两相互垂直。

在一些实施例中,所述结晶促进层由第一材料组成,所述相变层由第二材料组成;

所述第一材料的熔点大于所述第二材料的熔点,且所述第一材料的熔点与所述第二材料的熔点之间的差值大于预设温度值,所述预设温度值大于或等于200℃。

在一些实施例中,所述第一材料与所述第二材料具有相同的晶体结构,且所述第一材料的晶格常数与所述第二材料的晶格常数之间的差值的绝对值小于预设差值。

在一些实施例中,所述第一材料包括以下任意一种:AlSb、InP、PbS、InAs、ZnTe、CdSe或PbSe。

在一些实施例中,所述相变存储单元还包括位于所述存储层之上的顶部电极层以及位于所述存储层与所述选通层之间的中间电极层;

所述存储层中的最上层相变层与所述顶部电极层相邻,且所述存储层中的最下层相变层与所述中间电极层相邻;或者,

所述存储层中的最上层相变层与所述顶部电极层相邻,且所述存储层中的最下层结晶促进层与所述中间电极层相邻;或者,

所述存储层中的最上层结晶促进层与所述顶部电极层相邻,且所述存储层中的最下层相变层与所述中间电极层相邻;或者,

所述存储层中的最上层结晶促进层与所述顶部电极层相邻,且所述存储层中的最下层结晶促进层与所述中间电极层相邻。

在一些实施例中,所述存储层包括沿第一方向依次堆叠的至少一个相变层和至少一个结晶促进层;或者,

所述存储层包括沿第二方向依次堆叠的至少一个相变层和至少一个结晶促进层;或者,

所述存储层包括沿第三方向依次堆叠的至少一个相变层和至少一个结晶促进层。

在一些实施例中,相邻两个所述相变存储单元之间存在间隙,所述间隙中填充有隔热材料,所述隔热材料用于隔离相邻的所述存储层之间的热串扰。

在一些实施例中,所述第一导电线与所述第二导电线沿所述第三方向交替设置;

每一所述第一导电线和对应的所述第二导电线之间均设有所述相变存储单元;所述相变存储单元与所述第一导电线和所述第二导电线均垂直,且所述相变存储单元沿所述第三方向延伸,以形成沿所述第三方向堆叠的多层堆栈结构。

第二方面,本申请实施例提供一种三维存储器的形成方法,包括:

形成半导体堆叠结构,所述半导体堆叠结构至少包括沿第三方向依次堆叠的第二导电线、选通层、存储层和第一导电线;所述存储层包括交替堆叠的至少一个相变层和至少一个结晶促进层,所述结晶促进层用于促进所述相变层的结晶过程;

在第一方向和/或第二方向上,将所述半导体堆叠结构刻蚀为具有多个间隙的相变存储单元,以形成所述三维存储器;

其中,所述第三方向与所述第一方向和所述第二方向两两相互垂直。

在一些实施例中,所述半导体堆叠结构还包括:位于所述选通层和所述存储层之间的中间电极层;

形成所述存储层,通过以下步骤实现:

通过预设的沉积工艺,在所述中间电极层之上,沿所述第一方向或所述第二方向或所述第三方向,依次交替沉积所述相变层和所述结晶促进层,以形成具有至少一个相变层和至少一个结晶促进层的所述存储层。

在一些实施例中,所述方法还包括:

形成多个沿所述第三方向依次堆叠的所述半导体堆叠结构;

在所述第一方向和/或所述第二方向上,将每一所述半导体堆叠结构刻蚀为具有多个所述间隙的所述相变存储单元,以形成沿所述第三方向堆叠的多层堆栈结构。

本申请实施例提供的三维存储器及三维存储器的形成方法,由于设置在每一第一导电线与对应的第二导电线之间、且与第一导电线和第二导电线均垂直的相变存储单元具有沿第三方向依次叠置的存储层和选通层,且存储层包括交替堆叠的至少一个相变层和至少一个结晶促进层,结晶促进层可以促进相变层的结晶过程。如此,通过结晶促进层促进相变层快速地结晶,极大地提高了相变存储器的数据写入速率。

附图说明

在附图(其不一定是按比例绘制的)中,相似的附图标记可在不同的视图中描述相似的部件。具有不同字母后缀的相似附图标记可表示相似部件的不同示例。附图以示例而非限制的方式大体示出了本文中所讨论的各个实施例。

图1A为相关技术中3D X-Point存储器的透射电镜图;

图1B为相关技术中3D X-Point存储器的透视图;

图1C为相关技术中的3D X-Point存储器的局部放大透射电镜图;

图1D为相关技术中3D X-Point存储器发生相变时的时间、温度和电流三者之间的关系图;

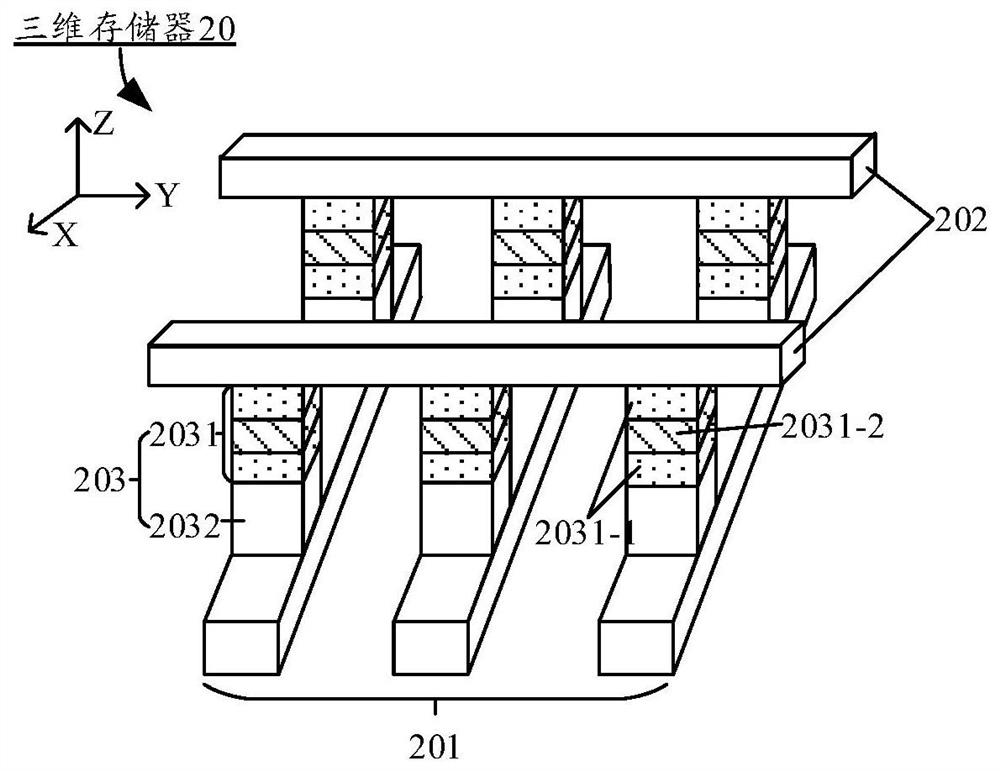

图2A为本申请实施例提供的三维存储器的结构示意图;

图2B为本申请实施例提供的三维存储器在第一方向上的一种可选的剖面图;

图2C为本申请实施例提供的三维存储器在第二方向上的一种可选的剖面图;

图2D为本申请实施例提供的具有多层堆栈结构的三维存储器的结构示意图;

图3A至图3E为本申请实施例提供的三维存储器的一种可选的结构剖视图;

图4A为本申请实施例提供的维存储器的形成方法的一个可选的实现流程示意图;

图4B为本申请实施例提供的存储叠层的剖视图;

图4C为本申请实施例提供的在第一方向上刻蚀半导体堆叠结构的剖视图;

图4D为本申请实施例提供的在第二方向上刻蚀半导体堆叠结构的剖视图;

图4E为本申请实施例提供的形成多层堆栈结构的结构示意图。

具体实施方式

为使本申请实施例的目的、技术方案和优点更加清楚,下面将结合本申请实施例中的附图,对发明的具体技术方案做进一步详细描述。以下实施例用于说明本申请,但不用来限制本申请的范围。

如本申请和权利要求书中所示,除非上下文明确提示例外情形,“一”、“一个”、“一种”和/或“该”等词并非特指单数,也可包括复数。一般来说,术语“包括”与“包含”仅提示包括已明确标识的步骤和元素,而这些步骤和元素不构成一个排他性的罗列,方法或者装置也可能包含其他的步骤或元素。

空间关系术语例如“在……上”、“在……下面”、“下面的”、“在……之下”、“在……之上”、“上面的”等,在这里可为了方便描述而被使用,从而描述图中所示的一个元件或特征与其他元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语意图还包括使用和操作中的器件的不同取向。当元件或层被称为“在……上”、“与……相邻”或“连接到”其他元件或层时,其可以直接地在其他元件或层上、与之相邻或连接到其他元件或层,或者可以存在居间的元件或层。

在详述本申请实施例时,为便于说明,表示器件结构的剖面图会不依一般比例作局部放大,而且所述示意图只是示例,其在此不应限制本申请保护的范围。此外,在实际制作中应包含长度、宽度及深度的三维空间尺寸。

三维相变存储器包括三维交叉点(3D X-Point)存储器,其基于块体材料属性的电阻改变(例如,处于高电阻状态或低电阻状态)来存储数据。3D X-Point存储器具有无晶体管的交叉点架构,该架构使存储单元位于垂直导体的相交处,这里的垂直导体包括彼此垂直相交的字线(Word Line,WL)与位线(Bit Line,BL),WL和BL一般由图案化工艺之后形成的20nm/20nm等幅线宽(Line/Space,L/S)构成。如图1A所示,为相关技术中3D X-Point存储器的透射电镜图,3D X-Point存储器包括:底部位线101、在底部位线101上方的同一平面中的顶部位线102、底部字线111、在底部字线111上方的同一平面中的顶部字线112、位于底部位线101和底部字线111之间的底部存储单元121以及位于顶部位线102和顶部字线112之间的顶部存储单元122。

如图1B所示,为相关技术中3D X-Point存储器的透视图,图1B中左边的图为一层堆栈结构的透视图,图1B中右边的图为两层堆栈结构的透视图,可以看出,3D X-Point存储器包括:顶部存储单元,或者,底部存储单元和顶部存储单元;其中,底部存储单元包括底部字线111、底部位线101以及位于底部字线111和底部位线101之间的底部存储单元121;顶部存储单元122包括顶部字线112、顶部位线102以及位于顶部字线112和顶部位线102之间的顶部存储单元122;堆叠两层WL/BL/存储单元,用来提高3D X-Point存储器的位密度。

3D X-Point存储器是利用相变材料的晶态和非晶态的特性来存储数据,例如,对相变材料(Ge

如图1D所示,为相关技术中3D X-Point存储器发生相变时的时间、温度和电流三者之间的关系图,在写操作模式下,如果数据是“1”,字线WL选通,写电流通过位线BL注入相变存储器,加热相变材料。相变材料的温度大于融化(Melting)温度Tm,相变材料变为非结晶态,此时需要的电流Ir(Amorphizing RESET Pulse)为相变的RESET电流,然后迅速减小注入电流,使相变材料的温度迅速下降,相变材料来不及变为结晶态,因此锁定在非晶态,处于高阻状态,把信号“1”存储在非结晶的状态。如果数据是“0”,字线WL选通,写电流Is(Crystallization SET Pulse)通过位线BL注入相变存储器,加热相变材料。相变材料的温度大于结晶(Crystallization)温度Tx,并保持一段时间,相变材料变为结晶态。相变材料锁定在结晶态,处于低阻状态,把信号“0”存储在结晶的状态。图1D中的t1为相变材料的RESET时间,t2为相变材料的SET时间,从图中可以看出t2远远大于t1。由于相变材料的结晶速度慢,导致PCM SET速度慢,限制了相变存储器的数据写入速率。

基于相关技术中3D X-Point存储器存在的上述问题,本申请实施例提供一种三维存储器及三维存储器的形成方法,能够促进相变材料的结晶速度,提高相变存储器的数据写入速率。

图2A为本申请实施例提供的三维存储器的结构示意图,如图2A所示,所述三维存储器20包括:

多条第一导电线201,沿第一方向延伸。

这里,所述第一方向为X轴方向,所述第一导电线201的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、多晶硅、掺杂硅、硅化物或其任何组合。

多条第二导电线202,沿第二方向延伸。

本申请实施例中,所述第二方向为Y轴方向,所述第二导电线202的材料包括但不限于钨(W)、钴(Co)、铜(Cu)、铝(Al)、多晶硅、掺杂硅、硅化物或其任何组合。

设置在每一所述第一导电线与对应的所述第二导电线之间、且与所述第一导电线和所述第二导电线均垂直的相变存储单元203;其中,所述相变存储单元至少包括沿第三方向依次叠置的存储层和选通层,所述存储层包括交替堆叠的至少一个相变层和至少一个结晶促进层,所述结晶促进层用于促进所述相变层的结晶过程;所述第三方向与所述第一方向和第二方向两两相互垂直。

这里,所述相变存储单元203位于所述第一导线201和所述第二导线202之间,且所述相变存储单元203与所述第一导线201和所述第二导线202相互垂直。所述第三方向为Z轴方向,所述相变存储单元203至少包括沿Z轴方向依次叠置的存储层2031和选通层2032。所述存储层2031包括交替堆叠的至少一个相变层和至少一个结晶促进层。如图2A所示,示例性地示出所述存储层2031包括交替堆叠的两个相变层2031-1和一个结晶促进层2031-2。

在一些实施例中,所述选通层2032由OTS(Ovonic Threshold Switch)材料形成,例如,Zn

在一些实施例中,所述结晶促进层2031-2由第一材料组成,所述相变层2031-1由第二材料组成;所述第一材料的熔点大于所述第二材料的熔点,且所述第一材料的熔点与所述第二材料的熔点之间的差值大于预设温度值,所述预设温度值大于或等于200℃。

在一些实施例中,所述第一材料的熔点为第一材料的理论结晶温度,而第一材料的实际结晶温度小于第一材料的理论结晶温度。所述第二材料的熔点为第二材料的理论结晶温度,而第二材料的实际结晶温度小于第二材料的理论结晶温度。本申请实施例中,当第一材料的实际温度大于第一材料的理论结晶温度时,第一材料开始从晶态转化为非晶态;当第一材料的实际温度小于的理论结晶温度时,第一材料开始从非晶态转化为晶态。当第二材料的实际温度大于第二材料的理论结晶温度时,第二材料开始从晶态转化为非晶态;当第二材料的实际温度小于的理论结晶温度时,第二材料开始从非晶态转化为晶态。

在一些实施例中,由于第一材料的熔点大于第二材料的熔点,因此,第一材料的理论结晶温度大于第二材料的理论结晶温度;并且,由于第一材料与第二材料具有相同的晶体结构,且第一材料和第二材料的物理性质和化学性质相似,因此,第一材料的实际结晶温度也大于第二材料的实际结晶温度。本申请实施例中,相变存储器的SET过程是相变存储器的相变材料从非晶态转化为晶态的过程,即温度降低的过程,由于第一材料的实际结晶温度大于第二材料的实际结晶温度,因此,在相变存储器的SET过程中第一材料最先降到实际结晶温度,所以,第一材料可以作为晶种,使得第二材料在未达到实际结晶温度时,直接结晶化,由此,可以缩短相变存储器的SET时间。

本申请实施例中,所述第二材料可以为含锗、锑、碲的合成材料(GST),例如,Ge

在一些实施中,所述第一材料与所述第二材料具有相同的晶体结构,且所述第一材料的晶格常数与所述第二材料的晶格常数之间的差值的绝对值小于预设差值。

例如,第一材料和第二材料均为立方晶系;所述第一材料的晶格常数为第一材料晶胞的边长,所述第二材料的晶格常数为第二材料晶胞的边长,本申请实施例中,所述第一材料晶胞的边长与第二材料晶胞的边长之间的差值的绝对值小于所述预设差值,本申请实施例中,对预设差值的大小不进行限定。

本申请实施例中,所述第一材料包括但不限于以下任意一种:AlSb、InP、PbS、InAs、ZnTe、CdSe或PbSe。

在一些实施例中,所述相变存储单元还包括位于所述存储层之上的顶部电极层(图中未示出)、位于所述存储层与所述选通层之间的中间电极层(图中未示出)以及位于所述选通层执之下的底部电极层(图中未示出);所述存储层中的最上层相变层与所述顶部电极层相邻,且所述存储层中的最下层相变层与所述中间电极层相邻;或者,所述存储层中的最上层相变层与所述顶部电极层相邻,且所述存储层中的最下层结晶促进层与所述中间电极层相邻;或者,所述存储层中的最上层结晶促进层与所述顶部电极层相邻,且所述存储层中的最下层相变层与所述中间电极层相邻;或者,所述存储层中的最上层结晶促进层与所述顶部电极层相邻,且所述存储层中的最下层结晶促进层与所述中间电极层相邻。

在一些实施例中,所述顶部电极层、中间电极层和底部电极层的材料可以是碳材料,例如,非晶碳(Amorphous Carbon,a-C)。

本申请实施例中,所述存储层的最底层可以是相变层或者结晶促进层,所述存储层的最顶层也可以是相变层或者结晶促进层。所述结晶促进层用于促进所述相变层的结晶过程,使得相变层能够快速地结晶。

在一些实施例中,所述存储层包括沿第一方向依次堆叠的至少一个相变层和至少一个结晶促进层;或者,所述存储层包括沿第二方向依次堆叠的至少一个相变层和至少一个结晶促进层;或者,所述存储层包括沿第三方向依次堆叠的至少一个相变层和至少一个结晶促进层。

请继续参见图2A,所述存储层2031包括沿第三方向依次堆叠的两个相变层2031-1和一个结晶促进层2031-2。

图2B为本申请实施例提供的三维存储器在第一方向上的一种可选的剖面图,如图2B所示,每一相变存储单元203的存储层2031包括沿第二方向依次堆叠的三个相变层2031-1和两个结晶促进层2031-2。

图2C为本申请实施例提供的三维存储器在第二方向上的一种可选的剖面图,如图2C所示,每一相变存储单元203的存储层2031包括沿第一方向依次堆叠的两个相变层2031-1和一个结晶促进层2031-2。

在一些实施例中,相邻两个所述相变存储单元203之间存在间隙204,所述间隙204中填充有隔热材料,所述隔热材料用于隔离相邻的所述存储层之间的热串扰。所述隔热材料可以是气凝胶,例如,二氧化硅气凝胶、碳气凝胶、金属氧化物气凝胶或聚合物气凝胶。

在一些实施例中,所述第一导电线与所述第二导电线沿所述第三方向交替设置;每一所述第一导电线和对应的所述第二导电线之间均设有所述相变存储单元;所述相变存储单元与所述第一导电线和所述第二导电线均垂直,且所述相变存储单元沿所述第三方向延伸,以形成沿所述第三方向堆叠的多层堆栈结构。

如图2D所示,为本申请实施例提供的具有多层堆栈结构的三维存储器的结构示意图,可以看出,所述三维存储器20'包括两层堆栈结构,每一层所述堆栈结构具有如图2A中三维存储器20所示的结构,且每一层堆栈结构沿Z轴方向依次堆叠。

本申请实施例提供的三维存储器,由于设置在每一第一导电线与对应的第二导电线之间、且与第一导电线和第二导电线均垂直的相变存储单元具有沿第三方向依次叠置的存储层和选通层,且存储层包括交替堆叠的至少一个相变层和至少一个结晶促进层,结晶促进层可以促进相变层的结晶过程,如此,通过结晶促进层促进相变层快速地结晶,极大地提高了相变存储器的数据写入速率。

本申请实施例提出了结晶促进层(Crystallization Promotion,CP)以形成3D X-Point存储器,通过结晶促进层,相变材料(对应上述实施例中的第二材料)可以跳过成核过程,而仅在相变材料和结晶促进层附近开始晶体生长,因此,结晶促进层的存在可以促进结晶速度,从而可以提高PCM SET速度。

在一些实施例中,PCM层的主要材料为GST,结晶促进层的选择需要考虑以下几个方面的因素:

第一:相同的对称性和接近的晶格参数;第二:相同的化学键性质;第三:是否为热稳定层,促进永久成核;第四:熔点比GST高出至少200℃;第五:基本不与GST发生化学反应;第六:数据耐久性和加工难度;第七:热和电行为改变性能;第八:结晶提升与数据保留性能。

如下表1示出了一些结晶促进层材料及其晶体性能参数,其中,表1中的第1行为PCM层的材料GST,表1中的第2行至第8行是结晶促进层的一些候选材料,通过以上几点需要考虑的因素,确定下表中的AlSb、InP、PbS、InAs、ZnTe、CdSe或PbSe中的任意一个材料均可以作为本申请实施例中的结晶促进层的材料。

表1一些结晶促进层材料及其晶体性能参数

在一些实施例中,在堆叠的3D X-Point存储器中,结晶促进层可以是一层,两层或多层;结晶促进层可以形成在PCM层底部的电极和PCM层之间、PCM层顶部的电极和PCM层之间或PCM层的内部,这里,每一层PCM层和每一层结晶促进层共同形成上述实施例中的存储层。

如图3A所示,为本申请实施例提供的三维存储器的一种可选的结构剖视图,如图3A所示,所述三维存储器包括两个堆栈结构30,每一堆栈结构的所述结晶促302进层位于PCM层301内,并且形成了两个结晶促进层/相变材料界面。

如图3B所示,为本申请实施例提供的三维存储器的一种可选的结构剖视图,如图3B所示,所述三维存储器包括两个堆栈结构30,每一堆栈结构的所述结晶促进层302位于PCM层301与PCM层底部的电极层303之间,并且形成了一个结晶促进层/相变材料界面。

如图3C所示,为本申请实施例提供的三维存储器的一种可选的结构剖视图,如图3C所示,所述三维存储器包括两个堆栈结构30,每一堆栈结构的所述结晶促进层302位于PCM层301与PCM层顶部的电极层304之间,并且形成了一个结晶促进层/相变材料界面。

如图3D所示,为本申请实施例提供的三维存储器的一种可选的结构剖视图,如图3D所示,所述三维存储器包括两个堆栈结构30,每一堆栈结构包括两个结晶促进层302,其中一个结晶促进层302位于PCM层301与PCM层顶部的电极层304之间,另外一个结晶促进层302位于PCM层301与PCM层底部的电极层303之间,并且形成了两个结晶促进层/相变材料界面。

如图3E所示,为本申请实施例提供的三维存储器的一种可选的结构剖视图,如图3E所示,所述三维存储器包括两个堆栈结构30,每一堆栈结构包括三个结晶促进层302,且所述三个结晶促进层302间隔地插入到PCM层301内部,并且形成了六个结晶促进层/相变材料界面。

本申请实施例中,通过结晶促进层可以促进相变材料的结晶速度,提高PCM SET的速度,进而提高了相变存储器的写入速率。

除此之外,本申请实施例还提供一种三维存储器的形成方法,图4A为本申请实施例提供的三维存储器的形成方法的一个可选的实现流程示意图,如图4A所示,所述方法包括以下步骤:

步骤S401、形成半导体堆叠结构,所述半导体堆叠结构至少包括沿第三方向依次堆叠的第二导电线、选通层、存储层和第一导电线;所述存储层包括交替堆叠的至少一个相变层和至少一个结晶促进层,所述结晶促进层用于促进所述相变层的结晶过程。

在一些实施例中,所述半导体堆叠结构还包括:位于所述存储层与所述第一导电线之间的顶部电极层、位于所述选通层和所述存储层之间的中间电极层以及位于所述选通层和所述第二导电线之间的底部电极层。其中,所述顶部电极层、中间电极层和底部电极层均为碳电极。

在一些实施例中,所述形成半导体堆叠结构,包括:沿第三方向,由下至上依次堆叠形成第二导电线、底部电极层、选通层、中间电极层、存储层、顶部电极层和第一导电线。所述形成所述存储层,通过以下步骤实现:通过预设的沉积工艺,在所述中间电极层之上,沿所述第一方向或所述第二方向或所述第三方向,依次交替沉积所述相变层和所述结晶促进层,以形成具有至少一个相变层和至少一个结晶促进层的所述存储层。所述预设的沉积工艺包括以下任意一种:化学气相沉积(Chemical Vapor Deposition,CVD)、物理气相沉积(Physical Vapor Deposition,PVD)或原子层沉积(Atomic Layer Deposition,ALD)工艺。

图4B为本申请实施例提供的存储叠层的剖视图,如图4B所示,所述存储叠层40包括由下至上依次堆叠的第二导电线407、底部电极层406、选通层405、中间电极层404、存储层、顶部电极层402和第一导电线401,所述存储层包括依次交替堆叠的两个相变层403-1和两个结晶促进层403-2。

在一些实施例中,所述结晶促进层403-2由第一材料组成,所述相变层403-1由第二材料组成;所述第一材料的熔点大于所述第二材料的熔点,且所述第一材料的熔点与所述第二材料的熔点之间的差值大于预设温度值,所述预设温度值大于或等于200℃。

在一些实施例中,所述第一材料与所述第二材料具有相同的晶体结构,且所述第一材料的晶格常数与所述第二材料的晶格常数之间的差值的绝对值小于预设差值。

在一些实施例中,所述第一材料包括以下任意一种:AlSb、InP、PbS、InAs、ZnTe、CdSe或PbSe。

步骤S402、在第一方向和/或第二方向上,将所述半导体堆叠结构刻蚀为具有多个间隙的相变存储单元,以形成所述三维存储器。

其中,所述第三方向与所述第一方向和第二方向两两相互垂直。

在一些实施例中,所述间隙包括第一间隙和第二间隙,所述在第一方向和/或第二方向上,将所述半导体堆叠结构刻蚀为具有多个间隙的相变存储单元,包括:

在第一方向和/或第二方向上由上至下依次刻蚀所述第一导电线、所述顶部电极层、所述存储层、所述中间电极层、所述选通层和所述底部电极层,直至暴露出所述第二导电线时为止,形成沿所述第二方向和/或所述第一方向排列的多个所述第一间隙和/或所述第二间隙,得到与所述第一间隙和/或所述第二间隙交替排列的所述相变存储单元,其中,刻蚀所述第一导电线、所述顶部电极层、所述存储层、所述中间电极层、所述选通层和所述底部电极层的刻蚀方向,与所述第一方向和所述第二方向垂直。

本申请实施例中,刻蚀所述半导体堆叠结构的过程包括两次刻蚀过程,第一次是在第一方向上对所述半导体堆叠结构进行刻蚀,第二次是在第二方向上对第一次刻蚀后的半导体堆叠结构进行刻蚀。

图4C为本申请实施例提供的在第一方向上刻蚀半导体堆叠结构的剖视图,如图4C所示,在第一方向上,由上至下依次对所述第一导电线、所述顶部电极层、所述存储层、所述中间电极层、所述选通层和所述底部电极层进行刻蚀,对应形成了第一次刻蚀后的第一导电线401'、第一次刻蚀后的顶部电极层402'、第一次刻蚀后的存储层403'-1、第一次刻蚀后的中间电极层404'、第一次刻蚀后的选通层405'和第一次刻蚀后的底部电极层406',并且形成了沿第二方向排列的多个第一间隙409和第一相变存储单元408。

图4D为本申请实施例提供的在第二方向上刻蚀半导体堆叠结构的剖视图,如图4D所示,在第二方向上,由上至下依次对第一次刻蚀后的第一导电线、第一次刻蚀后的顶部电极层、第一次刻蚀后的存储层、第一次刻蚀后的中间电极层、第一次刻蚀后的选通层和第一次刻蚀后的底部电极层进行刻蚀,对应形成了第二次刻蚀后的第一导电线401”、第二次刻蚀后的顶部电极层402”、第二次刻蚀后的存储层403”-1、第二次刻蚀后的中间电极层404”、第二次刻蚀后的选通层405”和第二次刻蚀后的底部电极层406”,并且形成了沿第一方向排列的多个第二间隙410和第二相变存储单元408'。本申请实施例中,所述相变存储单元包括第一相变存储单元408和第二相变存储单元408'。

在一些实施例中,所述三维存储器的形成方法还包括以下步骤:

步骤S10、形成多个沿所述第三方向依次堆叠的所述半导体堆叠结构。

步骤S20、在所述第一方向和/或所述第二方向上,将每一所述半导体堆叠结构刻蚀为具有多个所述间隙的所述相变存储单元,以形成沿所述第三方向堆叠的多层堆栈结构。

图4E为本申请实施例提供的形成多层堆栈结构的结构示意图,如图4E所示,形成了两个沿第三方向依次堆叠的半导体堆叠结构40,且每一半导体堆叠结构40具有相变存储单元408。

本申请实施例中,堆叠多层的堆栈结构用来提高三维存储器的存储能力。

本申请实施例三维存储器的形成方法与上述实施例中的三维存储器类似,对于本申请实施例中未详尽披露的技术特征,请参考上述实施例进行理解。

本申请实施例提供的三维存储器的形成方法,由于形成的三维存储器的存储层包括交替堆叠的至少一个相变层和至少一个结晶促进层,结晶促进层可以促进相变层的结晶过程,如此,使得相变层能够快速地结晶,极大地提高了三维存储器的数据写入速率。

本领域内的技术人员应明白,本申请提供三维存储器及三维存储器的形成方法的其他构成以及作用,对于本领域的技术人员而言都是已知的,为了减少冗余,本申请实施例不做赘述。

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”“具体示例”或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本申请的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

尽管已经示出和描述了本申请的实施例,本领域的普通技术人员可以理解:在不脱离本申请的原理和宗旨的情况下可以对这些实施例进行多种变化、修改、替换和变型,本申请的范围由权利要求及其等同限定。

- 一种三维存储器件的形成方法及三维存储器件

- 一种三维存储器及三维存储器的形成方法