显示装置

文献发布时间:2023-06-19 10:54:12

本申请是中国发明专利申请(申请号:201710071011.2,申请日:2017年02月09日,发明名称:显示装置)的分案申请。

技术领域

本发明涉及一种半导体结构,特别是涉及一种显示装置的半导体结构。

背景技术

由于平面显示器具有体积薄、重量轻及低幅射的优点,近年来逐渐被广泛使用。显示器中的薄膜晶体管结构,可以是具有高载流子移动率特性的多晶硅薄膜晶体管,或者是具有低漏电特性的金属氧化物薄膜晶体管,目前的显示器仍无法结合该两种晶体管,亦无相关的电路设计。

发明内容

本发明提供一种显示装置,包括一基底、一第一晶体管、一第二晶体管以及一第一电容电极。第一晶体管设置于基底之上,并包括一第一半导体层以及一第一栅极电极。第一栅极电极位于第一半导体层之上。第二晶体管设置于基底之上,并包括一第二半导体层。第一电容电极位于第一半导体层之上。第一电容电极在基底的垂直方向上和第一栅极电极重叠。第一半导体层包括硅半导体层。第二半导体层包括氧化半导体层。

本发明另提供一种显示装置,包括一基底、一第一晶体管、一第二晶体管以及一第一电容电极。第一晶体管设置于基底之上,并包括一第一半导体层、一第一栅极电极以及一第一栅极绝缘层。第一半导体层包括氧化半导体层。第一栅极电极和第一半导体层重叠。第一栅极绝缘层设置于第一半导体层与第一栅极电极之间。第二晶体管设置于基底之上,并包括一第二半导体层以及一第二栅极电极。第二半导体层包括硅半导体层。第二栅极电极和第二半导体层重叠。第一电容电极在基底的垂直方向上和第二栅极电极重叠。第一栅极绝缘层位于第一电容电极之上。

为让本发明的特征和优点能更明显易懂,下文特举出优选实施例,并配合所附的附图,作详细说明如下:

附图说明

图1为本发明的显示装置的示意图;

图2A为本发明的像素的一可能实施例的示意图;

图2B为本发明的像素的另一可能实施例的示意图;

图2C为本发明的像素的另一可能实施例的示意图;

图2D为本发明的像素的另一示意图;

图3A为本发明的像素的另一可能实施例的示意图;

图3B为本发明的像素的另一可能实施例的示意图;

图3C为本发明的像素的另一可能实施例的示意图;

图3D为本发明的像素的另一可能实施例的示意图;

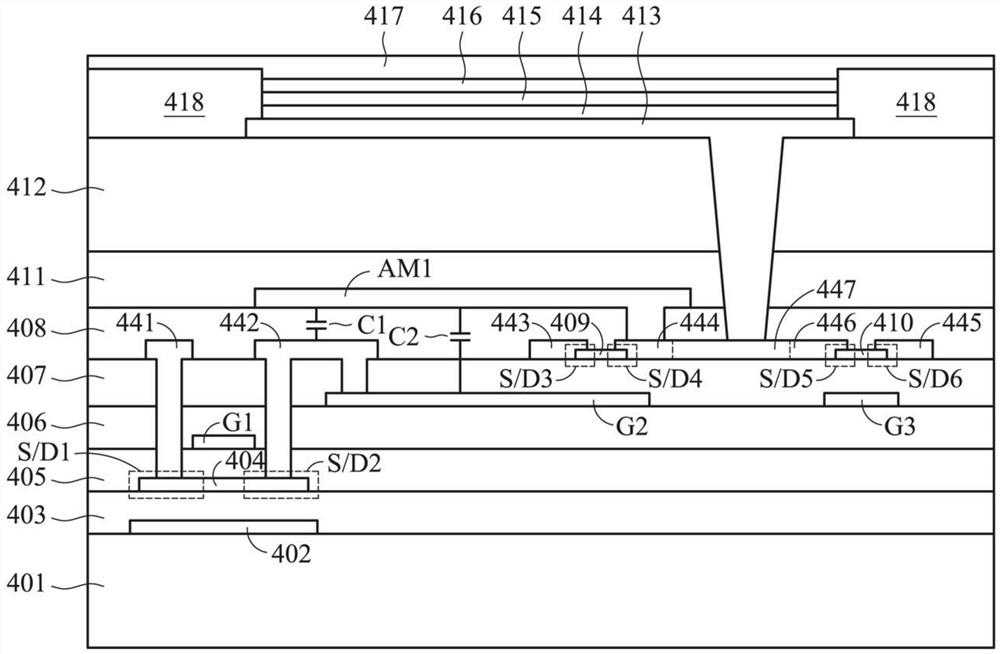

图4A为本发明的像素的半导体结构示意图;

图4B为本发明的像素的另一半导体结构示意图;

图4C为本发明的像素的另一半导体结构示意图;

图4D为本发明的像素的另一半导体结构示意图;

图5为本发明的像素的另一半导体结构示意图;

图6为本发明的像素的另一半导体结构示意图;

图7为本发明的像素的另一半导体结构示意图;

图8A为本发明的像素的另一半导体结构示意图;

图8B为本发明的像素的另一半导体结构示意图;

图9为本发明的像素的另一半导体结构示意图;

图10A为本发明的像素的另一半导体结构示意图;

图10B为本发明的像素的另一半导体结构示意图;

图10C为本发明的像素的另一半导体结构示意图;

图10D为本发明的像素的另一半导体结构示意图;

图10E为本发明的像素的另一半导体结构示意图;

图10F为本发明的像素的另一半导体结构示意图;

图11A为本发明的像素的另一半导体结构示意图;

图11B为本发明的像素的另一半导体结构示意图;

图11C为本发明的像素的另一半导体结构示意图;

图12为本发明的像素的另一半导体结构示意图;

图13为本发明的像素的另一半导体结构示意图;

图14为本发明的像素的另一半导体结构示意图;

图15为本发明的像素的另一半导体结构示意图;

图16A为本发明的像素的另一半导体结构示意图;图16B为本发明的像素的另一半导体结构示意图。

符号说明

100:显示装置;

110:栅极驱动器;

120:源极驱动器;

P

S

D

210、310:切换晶体管;

220、330:驱动晶体管;

230、340:重置晶体管;

Cst、Cst1、Cst2:存储电容;

240、350:有机发光二极管;

A、B:节点;

Vdd、Vss:操作电压;

Vref:参考电压;

C1~C37、C40:电容;

250、260、360、370:辅助电容;

270、320:点亮晶体管;

EN:点亮信号;

Rst:重置信号;

vini:起始电压;

380:控制晶体管;

SCNT:控制信号;

S

401、403、405、406、407、408、411、412、501、502、506、510、511、512、513、601、602、604、606~609、612、701、702、706、710、711、713、715、801、802、806、10、812、813、815、901~904、908、912、914~916、1001~1004、1006、1008~1010、1013、1101~1104、1106~1108、1111、1301、1302、1304、1306~1308、1312、1313、1401~1404、1406、1408~1410、1413、1501~1504、1506、1508~1510、1513、1516、1601、1602、1606、1608、1611~1613、1616:绝缘层;

402、503~505、603、703~705、803、804、805、905~907、1005A、1005E、1114、1303、1405、1505、1603~1605:阻挡层;

404、507、605、707、807、909、1007A、1007B、1105、1305、1407、1507、1607:第一半导体层;

409、508、610、708、808、910、1011、1109、1310、1411、1511、1609:第二半导体层;

410、509、611、709、809、911、1012、1110、1311、1412、1512、1610:第三半导体层;

419:第四半导体层;

S/D1:第一源/漏极区;

S/D2:第二源/漏极区;

S/D3:第三源/漏极区;

S/D4:第四源/漏极区;

S/D5:第五源/漏极区;

S/D6:第六源/漏极区;

S/D7:第七源/漏极区;

S/D8:第八源/漏极区;

G1、G1A、G1B、G1C:第一栅极电极;

G2:第二栅极电极;

G3:第三栅极电极;

G4:第四栅极电极;

441、451、541、641、741、841、941、1041、1141、1341、1441、1541、1641:第一源/漏极电极;

442、452、542、642、742、842、942、1042、1142、1342、1442、1542、1642:第二源/漏极电极;

443、453、543、643、743、843、943、1043、1143、1346、1443、1543、1643:第三源/漏极电极;

444、454、545、644、745、845、945、1044、1144、1347、1444、1544、1644:第四源/漏极电极;

446、458、546、646、747、847、947、1046、1146、1350、1446、1546、1646:第五源/漏极电极;

445、455、547、645、746、846、946、1045、1145、1348、1445、1545、1645:第六源/漏极电极;

456、1344:第七源/漏极电极;

457、1345:第八源/漏极电极;

447、459、544、647、744、748、811、844、848、913、944、948、1046~1048、1147、1343、1349、1351、1447、1547、1647:连接电极;

1201~1203、413、417、514、613、716、847、918、1015、1113、1315、1415、1515、1615:电极;

AM1、AM2、AM4、AM5、AM6、AM8、AM9、AM19、AM11、AM12、AM15、AM18、AM41:第一电容电极;

AM3、AM7、AM9、AM10、AM13、AM16:第二电容电极;

AM14、AM17:第三电容电极;

414:空穴传输层;

415:发光层;

416:电子传输层;

418:像素限定层;

515、615、717、816、917、1014、1112、1314、1414、1514、1614:有机发光二极管;

凹槽1200。

具体实施方式

图1为本发明的显示装置的示意图。如图所示,显示装置100包括一栅极驱动器110、一源极驱动器120以及多个像素P

本发明并不限定像素P

切换晶体管210的栅极电极接收扫描信号S

随着显示面板尺寸越来越小,驱动晶体管220的栅极与源极之间的间隔越来越小。因此,存储电容Cst的容值越来越小。在此例中,通过至少一电容电极与一特定金属层形成一存储电容或形成一辅助电容,用以增加存储电容Cst的容值。在一可能实施例中,电容电极的电位的绝对值大于0。本发明并不限定特定金属层的种类。在一可能实施例中,特定金属层指驱动晶体管220的栅极电极或是有机发光二极管240的阳极。另外,本发明并不限定电容电极的位置。稍后将通过图4A、图4B、图4C、图4D、图5、图6、图7、图8A、图8B、图9、图10A、图10B、图10C、图10D、图10E、图10F、图11A、图11B、图11C、图12、图13、图14、图15、图16A及图16B说明电容电极的位置。

图2B为本发明的像素的另一可能实施例。图2B相似图2A,不同之处在于图2B多了辅助电容250。辅助电容250的一端接收一预设电压S

图2C为本发明的像素的另一可能实施例。图2C相似图2B,不同之处在于图2C多了辅助电容260。辅助电容260的一端接收预设电压S

图2D为本发明的像素的另一示意图。图2D相似图2A,不同之处在于,图2D多了一点亮晶体管270。点亮晶体管270的栅极电极接收一点亮信号EN,其漏极接收操作电压Vdd,其源极耦接驱动晶体管220的漏极。在其它实施例中,图2D的点亮晶体管270可应用于图2B或是图2C中。

图3A为本发明的像素的另一可能实施例。在本实施例中,像素P

图3B为本发明的像素的另一可能实施例。图3B相似图3A,不同之处在于图3B多了辅助电容360。辅助电容360一端接收一预设电压S

图3C为本发明的像素的另一可能实施例。图3C相似图3B,不同之处在于图3C多了辅助电容370。辅助电容370一端接收预设电压S

图3D为本发明的像素的另一可能实施例。图3D相似图3C,不同之处在于图3D多了控制晶体管380。控制晶体管380的栅极接收一控制信号SCNT,其漏极接收一预设电压S

图4A为本发明的像素的半导体结构示意图。如图所示,阻挡层402形成在基底401之上。绝缘层403形成在阻挡层402之上。第一半导体层404形成在绝缘层403之上,并重叠阻挡层402。在本实施例中,阻挡层402的面积大于第一半导体层404。第一半导体层404具有一第一源/漏极区S/D1以及一第二源/漏极区S/D2。在一可能实施例中,第一半导体层404的材料为低温多晶硅(Low Temperature Poly-silicon;LTPS)或非晶硅。在此例中,第一半导体层404可称为一硅半导体层。绝缘层405形成在第一半导体层404之上。

第一栅极电极G1形成在绝缘层405之上,并重叠第一半导体层404。绝缘层406形成在第一栅极电极G1之上。第二栅极电极G2与第三栅极电极G3形成在绝缘层406之上。绝缘层407形成在第二栅极电极G2与第三栅极电极G3之上。第一源/漏极电极441、第二源/漏极电极442、第三源/漏极电极443、第二半导体层409、第四源/漏极电极444、连接电极447、第五源/漏极电极446、第三半导体层410以及第六源/漏极电极445形成在绝缘层407之上。

第一源/漏极电极441电连接第一源/漏极区S/D1。第二源/漏极电极442电连接第二源/漏极区S/D2与第二栅极G2。在本实施例中,第一栅极电极G1、第一源/漏极电极441以及第二源/漏极电极442构成一第一晶体管。另外,由于第一栅极电极G1位于第一半导体层404的上方,故第一晶体管称为上栅极电极(top gate)架构。在一可能实施例中,第一源/漏极电极441作为第一晶体管的源极。在此例中,第二源/漏极电极442作为第一晶体管的漏极。在另一可能实施例中,第一源/漏极电极441作为第一晶体管的漏极。在此例中,第二源/漏极电极442作为第一晶体管的源极。另外,由于绝缘层405隔离第一栅极电极G1与第一半导体层404,故绝缘层405可称为栅极绝缘层。

第二半导体层409重叠第二栅极电极G2,并具有一第三源/漏极区S/D3以及一第四源/漏极区S/D4。第三源/漏极电极443电连接第三源/漏极区S/D3。第四源/漏极电极444电连接第四源/漏极区S/D4。在一可能实施例中,第二半导体层409的材料为氧化铟镓锌。(indium gallium zinc oxide;IGZO)。在此例中,第二半导体层409可称为一氧化半导体层。另外,第二栅极电极G2、第三源/漏极电极443以及第四源/漏极电极444可构成一第二晶体管。在一可能实施例中,第三源/漏极电极443与第四源/漏极电极444的一者作为第二晶体管的源极,并且第三源/漏极电极443与第四源/漏极电极444的另一者作为第二晶体管的漏极。另外,由于第二栅极电极G2位于第二半导体层409的下方,故第二晶体管称为下栅极电极(bottom gate)架构。

第三半导体层410重叠第三栅极电极G3,并具有一第五源/漏极区S/D5以及一第六源/漏极区S/D6。第五源/漏极电极446电连接第五源/漏极区S/D5。在本实施例中,第五源/漏极电极446通过连接电极447电连接第四源/漏极电极444。第六源/漏极电极445电连接第六源/漏极区S/D6。在一可能实施例中,第三半导体层410的材料也是氧化铟镓锌。在本实施例中,第三栅极电极G3、第五源/漏极电极446以及第六源/漏极电极445构成一第三晶体管。在一可能实施例中,第五源/漏极电极446以及第六源/漏极电极446的一者作为第三晶体管的源极,另一者作为第三晶体管的漏极。再者,由于第三栅极电极G3位于第三半导体层410的下方,故第三晶体管称为下栅极电极架构。

绝缘层408形成于第一源/漏极电极441、第二源/漏极电极442、第三源/漏极电极443、第二半导体层409、第四源/漏极电极444、连接电极447、第五源/漏极电极446、第三半导体层410以及第六源/漏极电极445之上。一第一电容电极AM1设置在绝缘层408之上,并电连接第四源/漏极电极444。绝缘层411形成在一第一电容电极AM1之上。在本实施例中,第一电容电极AM1重叠第二源/漏极电极442与第二栅极电极G2。因此,第一电容电极AM1、绝缘层408与第二源/漏极电极442构成一电容C1。另外,第一电容电极AM1、绝缘层408、绝缘层407与第二栅极电极G2构成一电容C2。在一可能实施例中,电容C1与电容C2作为图2A至图2D的任一者所示的存储电容Cst或辅助电容或是图3A至图3D的任一者所示的存储电容Cst1或辅助电容。

绝缘层412形成在绝缘层411之上。电极413形成在绝缘层412之上。在本实施例中,电极413电连接至连接电极447,用以电连接第四源/漏极电极444与第五源/漏极电极446,但并非用以限制本发明。电极413作为一有机发光二极管的阳极(anode)。本发明并不限定有机发光二极管显示装置的半导体结构。为方便说明,图4A显示有机发光二极管显示装置的一可能半导体结构,但并非用以限制本发明。

如图所示,一空穴传输层(hole transport layer)414形成在电极413之上。一发光层(emissive layer)415形成在空穴传输层414之上。一电子传输层(electrontransport layer)416形成发光层415之上。一电极417形成在电子传输层416之上。在本实施例中,电极417作为有机发光二极管的阴极(cathode)。另外,像素限定层418(pixeldefining layer;PDL)418用以隔离相邻的有机发光二极管。

在一可能实施例中,当第一源/漏极电极441接收一数据信号(如D

图4B为本发明的像素的另一半导体结构示意图。图4B相似图4A,不同之处在于图4B多了一第四栅极电极G4。第四栅极电极G4设置于绝缘层408之上,并重叠第三半导体层410。在本实施例中,第三晶体管具有两栅极电极G3与G4,故第三晶体管为一双栅极电极(dual gate)架构。

图4C为本发明的像素的另一半导体结构示意图。图4C相似图4A,不同之处在于,在图4C中,第四源/漏极电极444并未直接电连接至第五源/漏极电极446。在本实施例中,第一电容电极AM1分别电连接第四源/漏极电极444与第五源/漏极电极446。因此,第四源/漏极电极444间接地电连接第五源/漏极电极446。另外,电极413电连接至第一电容电极AM1。在本实施例中,第一电容电极AM1并未重叠电极442,但并非用以限制本发明。

图4D为本发明的像素的另一半导体结构示意图。在本实施例中,阻挡层402形成于基板401之上。绝缘层403位于阻挡层402之上。第一半导体层404形成于绝缘层403之上。第一半导体层404重叠阻挡层402,并具有一第一源/漏极区S/D1以及一第二源/漏极区S/D2。绝缘层405形成于第一半导体层404之上。在本实施例中,第一半导体层404的材料为低温多晶硅。

第一栅极电极G1与第三栅极电极G3形成于绝缘层405之上。第一栅极电极G1重叠第一半导体层404。绝缘层406形成于第一栅极电极G1之上。第一源/漏极电极451、第二源/漏极电极452与第二栅极G2形成在绝缘层406之上。第一源/漏极电极451电连接第一源/漏极区S/D1。第二源/漏极电极452电连接第二源/漏极区S/D2。在本实施例中,第一栅极电极G1、第一源/漏极电极451与第二源/漏极电极452构成一第一晶体管。由于第一栅极电极G1在第一半导体层404的上方,故第一晶体管为上栅极电极架构。

在本实施例中,绝缘层407形成于第一源/漏极电极451、第二源/漏极电极452与第二栅极G2之上。第四半导体层419、第二半导体层409以及第三半导体层410形成于绝缘层407之上。第二半导体层409重叠第二栅极电极G2,并具有一第三源/漏极区S/D3以及一第四源/漏极区S/D4。在本实施例中,第三源/漏极电极453与第四源/漏极电极454形成于绝缘层407之上。第三源/漏极电极453电连接第三源/漏极区S/D3。第四源/漏极电极454电连接第四源/漏极区S/D4与连接电极459。第二栅极电极G2、第三源/漏极电极453与第四源/漏极电极454构成一第二晶体管。由于第二栅极电极G2在第二半导体层409的下方,故第二晶体管为下栅极电极架构。在一可能实施例中,第二半导体层409的材料为氧化铟镓锌。

第三半导体层410重叠第三栅极电极G3,并具有一第五源/漏极区S/D5以及一第六源/漏极区S/D6。在本实施例中,第五源/漏极电极458与第六源/漏极电极455形成于绝缘层407之上。第五源/漏极电极458电连接第五源/漏极区S/D5与连接电极459。第六源/漏极电极455电连接第六源/漏极区S/D6。第三栅极电极G3、第五源/漏极电极458以及第六源/漏极电极455构成一第三晶体管。由于第三栅极电极G3在第三半导体层410的下方,故第三晶体管为下栅极电极架构。在一可能实施例中,第三半导体层410的材料为氧化铟镓锌。第四半导体层419具有第七源/漏极区S/D7以及第八源/漏极区S/D8。在本实施例中,第七源/漏极电极456与第八源/漏极电极457形成于绝缘层407之上。第七源/漏极电极456电连接第七源/漏极区S/D7。第八源/漏极电极457电连接第八源/漏极区S/D8。

绝缘层408形成于第二半导体层409、第三半导体层410、第四半导体层419、第七源/漏极电极456、第八源/漏极电极457、第三源/漏极电极453、第四源/漏极电极454、连接电极459、第五源/漏极电极458与第六源/漏极电极455之上。一第四栅极电极G4以及一第一电容电极AM1形成于绝缘层408之上。第四栅极电极G4与第一电容电极AM1彼此电性隔离。绝缘层411形成于第四栅极电极G4以及第一电容电极AM1之上。

第四栅极电极G4重叠第四半导体层419。在本实施例中,第四栅极电极G4、第七源/漏极电极456以及第八源/漏极电极457构成一第四晶体管。在一可能实施例中,第七源/漏极电极456以及第八源/漏极电极457的一者作为第四晶体管的源极,而另一者作为第四晶体管的漏极。由于第四栅极电极G4在第四半导体层419的上方,故第四晶体管为上栅极电极架构。在一可能实施例中,第四半导体层419的材料为氧化铟镓锌。

第一电容电极AM1并重叠第二栅极电极G2。因此,第一电容电极AM1、绝缘层408、绝缘层407与第二栅极电极G2构成一电容C3。在本实施例中,第一电容电极AM1电连接第八源/漏极电极457与第三源/漏极电极453,但并非用以限制本发明。在另一可能实施例中,第七源/漏极电极456接收一参考电压(如Vref),第一源/漏极电极451接收一数据信号(如D

图5为本发明的像素的另一半导体结构示意图。如图所示,阻挡层503、阻挡层504与阻挡层505形成在基底501之上。绝缘层502形成在阻挡层503、阻挡层504与阻挡层505之上。阻挡层503、阻挡层504与阻挡层505彼此独立设置,在另一实施例中,阻挡层503、阻挡层504与阻挡层505也可以相互连接。第一半导体层507、第二半导体层508以及第三半导体层509形成在绝缘层502之上,并分别重叠阻挡层503、阻挡层504与阻挡层505。在一可能实施例中,第一半导体层507的材料为低温多晶硅,第二半导体层508与第三半导体层509的材料为氧化铟镓锌。第一半导体层507具有一第一源/漏极区S/D1以及一第二源/漏极区S/D2。第二半导体层508具有一第三源/漏极区S/D3以及一第四源/漏极区S/D4。第三半导体层509具有一第五源/漏极区S/D5以及一第六源/漏极区S/D6。

绝缘层506设置在第一半导体层507、第二半导体层508以及第三半导体层509之上。第一栅极电极G1、第二栅极电极G2与第三栅极电极G3形成在绝缘层506之上。第一栅极电极G1重叠第一半导体层507。第二栅极电极G2重叠第二半导体层508。第三栅极电极G3重叠第三半导体层509。

绝缘层510形成在第一栅极电极G1、第二栅极电极G2与第三栅极电极G3之上。第一源/漏极电极541、第二源/漏极电极542、第三源/漏极电极543、连接电极544、第四源/漏极电极545、第五源/漏极电极546以及第六源/漏极电极547形成在绝缘层510之上。如图所示,第一源/漏极电极541电连接第一源/漏极区S/D1。第二源/漏极电极542电连接第二源/漏极区S/D2。第三源/漏极电极543电连接第三源/漏极区S/D3。连接电极544电连接第二栅极电极G2。在一可能实施例中,连接电极544电连接第二源/漏极电极542。第四源/漏极电极545电连接第四源/漏极区S/D4。第五电极546电连接第五源/漏极区S/D5。第六源/漏极电极547电连接第六源/漏极区S/D6。

第一栅极电极G1、第一源/漏极电极541与第二源/漏极电极542构成一第一晶体管。由于第一栅极电极G1设置于第一半导体层507的上方,故第一晶体管属上栅极电极架构。第二栅极电极G2、第三源/漏极电极543与第四源/漏极电极545构成一第二晶体管。由于第二栅极电极G2设置于第二半导体层508的上方,故第二晶体管属上栅极电极架构。在本实施例中,第二栅极电极G2的宽度(水平方向)大于第一栅极电极G1的宽度,但并非用以限制本发明。另外,第三栅极电极G3、第五源/漏极电极546与第六源/漏极电极547构成一第三晶体管。由于第三栅极电极G3设置于第三半导体层509的上方,故第三晶体管属上栅极电极架构。

绝缘层511设置在第一源/漏极电极541、第二源/漏极电极542、第三源/漏极电极543、连接电极544、第四源/漏极电极545、第五源/漏极电极546以及第六源/漏极电极547之上。第一电容电极AM1设置在绝缘层511之上。在本实施例中,第一电容电极AM1电连接第四源/漏极电极545与第五源/漏极电极546,但并非用以限制本发明。由于第一电容电极AM1重叠第二栅极电极G2,故第一电容电极AM1、绝缘层511、绝缘层510与第二栅极电极G2构成一电容C4。在本实施例中,第四源/漏极电极545通过第一电容电极AM1间接地电连接第五源/漏极电极546。

绝缘层512形成在第一电容电极AM1之上。绝缘层513形成在绝缘层512之上。有机发光二极管515形成于绝缘层513之上。本发明并不限定有机发光二极管显示装置的半导体结构。在本实施例中,有机发光二极管515的电极514电连接第一电容电极AM1。

在一可能实施例中,第一栅极电极G1接收一扫描信号(如S

图6为本发明的像素的另一半导体结构示意图。如图所示,阻挡层603形成于基底601之上。绝缘层602形成于阻挡层603之上。第一半导体层605设置在绝缘层602之上,第一半导体层605重叠阻挡层603,并具有第一源/漏极区S/D1以及第二源/漏极区S/D2。在一可能实施例中,第一半导体层605的材料为低温多晶硅。

绝缘层604形成于第一半导体层605之上。第一电容电极AM2设置于绝缘层604之上。绝缘层606形成于第一电容电极AM2之上。第一栅极电极G1与第二电容电极AM3设置于绝缘层606之上。第一栅极电极G1重叠第一半导体层605。第二电容电极AM3重叠第一电容电极AM2。因此,第二电容电极AM3、绝缘层606与第一电容电极AM2构成一电容C6。另外,第一电容电极AM2位于第一栅极电极G1与第一半导体层605之间。

绝缘层607形成于第一栅极电极G1与第二电容电极AM3之上。第二栅极电极G2与第三栅极电极G3设置于绝缘层607之上。在本实施例中,第二栅极电极G2重叠第一电容电极AM2。因此,第二栅极电极G2、绝缘层607、绝缘层606以及第一电容电极AM2构成一电容C5。

绝缘层608形成于第二栅极电极G2与第三栅极电极G3之上。第二半导体层610与第三半导体层611设置于绝缘层608之上。在一可能实施例中,第二半导体层610与第三半导体层611的材料为氧化铟镓锌。如图所示,第二半导体层610重叠第二栅极电极G2,并具有第三源/漏极区S/D3以及第四源/漏极电区S/D4。第三半导体层611重叠第三栅极电极G3,并具有第五源/漏极区S/D5以及第六源/漏极区S/D6。

在本实施例中,第一源/漏极电极641、第二源/漏极电极642、第三源/漏极电极643、第四源/漏极电极644、连接电极647、第五源/漏极电极646以及第六源/漏极电极645设置于绝缘层608之上。如图所示,第一源/漏极电极641电连接第一源/漏极区S/D1。第二源/漏极电极642电连接第二源/漏极区S/D2、第二电容电极AM3与第二栅极电极G2。第三源/漏极电极643电连接第三源/漏极区S/D3。第四源/漏极电极644电连接第四源/漏极区S/D4。第五源/漏极电极646电连接第五源/漏极区S/D5。在本实施例中,连接电极647电连接第四源/漏极电极644、第一电容电极AM2以及第五源/漏极电极646。第六源/漏极电极645电连接第六源/漏极区S/D6。在本实施例中,第一栅极电极G1、第一源/漏极电极641与第二源/漏极电极642构成一第一晶体管。第二栅极电极G2、第三源/漏极电极643与第四源/漏极电极644构成一第二晶体管。第三栅极电极G3、第五源/漏极电极646与第六源/漏极电极645构成一第三晶体管。

绝缘层609形成于第一源/漏极电极641、第二源/漏极电极642、第三源/漏极电极643、第二半导体层610、第四源/漏极电极644、连接电极647、第五源/漏极电极646、第三半导体层611以及第六源/漏极电极645之上。绝缘层612形成于绝缘层609之上。有机发光二极管615形成于绝缘层612之上。本发明并不限定有机发光二极管显示装置的半导体结构。在一可能实施例中,有机发光二极管615可能具有一空穴注入层、一空穴传输层、一发光层以及一电子传输层。在本实施例中,有机发光二极管615的电极613电连接连接电极647。

由于第一栅极电极G1位于第一半导体层605的上方,故第一晶体管为上栅极电极结构。另外,第二栅极电极G2与第三栅极电极G3分别位于第二半导体层610与第三半导体层611的下方,故第二晶体管与第三晶体管为下栅极电极结构。另外,在本实施例中,绝缘层606位于第一电容电极AM2之上,而绝缘层606位于第一栅极电极G1与第一半导体层605之间。

图7为本发明的像素的另一半导体结构示意图。阻挡层703、阻挡层704与阻挡层705位于基底701之上。绝缘层702形成于阻挡层703、阻挡层704与阻挡层705之上。第一半导体层707、第二半导体层708以及第三半导体层709位于绝缘层702之上。第一半导体层707重叠阻挡层703并具有第一源/漏极区S/D1以及第二源/漏极区S/D2。在一可能实施例中,第一半导体层707的材料为低温多晶硅。第二半导体层708重叠阻挡层704并具有第三源/漏极区S/D3以及第四源/漏极区S/D4。第三半导体层709重叠阻挡层705并具有第五源/漏极区S/D5以及第六源/漏极区S/D6。在一可能实施例中,第二半导体层708与第三半导体层709的材料为氧化铟镓锌。

绝缘层706形成于第一半导体层707、第二半导体层708以及第三半导体层709之上。第一电容电极AM4位于绝缘层706之上。绝缘层710形成于第一电容电极AM4之上。第一栅极电极G1、第二栅极电极G2以及第三栅极电极G3设置于绝缘层710之上。第一栅极电极G1重叠第一半导体层707。第二栅极电极G2重叠第二半导体层708。第三栅极电极G3重叠第三半导体层709。另外,第二栅极电极G2重叠第一电容电极AM4。因此,第二栅极电极G2、绝缘层710以及第一电容电极AM4构成一电容C7。在一可能实施例中,电容C7作为图2A至图2D的任一者所示的存储电容Cst或是图3A至图3D的任一者所示的存储电容Cst1。

绝缘层711形成于第一栅极电极G1、第二栅极电极G2以及第三栅极电极G3之上。第一源/漏极电极741、第二源/漏极电极742、第三源/漏极电极743、连接电极744、第四源/漏极电极745、连接电极748、第五源/漏极电极747以及第六电极746位于绝缘层711之上。第一源/漏极电极741电连接第一源/漏极区S/D1。第二源/漏极电极742电连接第二源/漏极区S/D2。在本实施例中,第一栅极电极G1、第一源/漏极电极741以及第二源/漏极电极742构成一第一晶体管。第三源/漏极电极743电连接第三源/漏极区S/D3。连接电极744电连接第二栅极电极G2。在另一可能实施例中,连接电极744还电连接第二源/漏极电极742。第四源/漏极电极745电连接第四源/漏极区S/D4。在本实施例中,第二栅极电极G2、第三源/漏极电极743以及第四源/漏极电极745构成一第二晶体管。连接电极748电连接第四源/漏极电极745、第一电容电极AM4以及第五源/漏极电极747。第五源/漏极电极747电连接第五源/漏极区S/D5。第六源/漏极电极746电连接第六源/漏极区S/D6。在本实施例中,第三栅极电极G1、第五源/漏极电极747以及第六源/漏极电极746构成一第三晶体管。

绝缘层713形成于第一源/漏极电极741、第二源/漏极电极742、第三源/漏极电极743、连接电极744、第四源/漏极电极745、连接电极748、第五源/漏极电极747以及第六电极746之上。绝缘层715形成于绝缘层713之上。有机发光二极管717形成于绝缘层715之上。本发明并不限定有机发光二极管显示装置的半导体结构。任何有机发光二极管显示装置的半导体结构均可应用至图7中。在本实施例中,有机发光二极管717的电极716电连接连接电极748,但并非用以限制本发明。

在本实施例中,由于第一栅极电极G1、第二栅极电极G2以及第三栅极电极G3分别位于第一半导体层707、第二半导体层708以及第三半导体层709之上,故第一晶体管、第二晶体管及第三晶体管均为上栅极电极结构。另外,在本实施例中,第一电容电极AM4位于第二栅极电极G2与第二半导体层708之间,但并非用以限制本发明。

图8A为本发明的像素的另一半导体结构示意图。如图所示,阻挡层803、阻挡层804与阻挡层805设置于基底801之上。绝缘层802形成于阻挡层803、阻挡层804与阻挡层805之上。第一半导体层807、第二半导体层808以及第三半导体层809位于绝缘层802之上。第一半导体层807重叠阻挡层803,并具有第一源/漏极区S/D1以及第二源/漏极区S/D2。第二半导体层808重叠阻挡层804,并具有第三源/漏极区S/D3以及第四源/漏极区S/D4。第三半导体层809重叠阻挡层805,并具有第五源/漏极区S/D5以及第六源/漏极区S/D6。在一可能实施例中,第一半导体层807的材料为低温多晶硅,并且第二半导体层808与第三半导体层的材料为氧化铟镓锌。在另一可能实施例中,第一半导体层807的材料为氧化铟镓锌,而第二半导体层808与第三半导体层809的材料为低温多晶硅。

绝缘层806形成在第一半导体层807、第二半导体层808以及第三半导体层809之上。第二栅极电极G2、连接电极811以及第三栅极电极G3位于绝缘层806之上。第二栅极电极G2重叠第二半导体层808。连接电极811电连接阻挡层804。第三栅极电极G3重叠第三半导体层809。另外,第二栅极电极G2、绝缘层806、绝缘层802以及阻挡层804构成一电容C8。在本实施例中,阻挡层804作为电容C8的一端,故阻挡层804可作为一电容电极。在此例中,电容电极的材料与阻挡层803与阻挡层805的材料相同。

绝缘层810形成于第二栅极电极G2、连接电极811以及第三栅极电极G3之上。第一栅极电极G1A与第一电容电极AM5设置于绝缘层810之上。第一栅极电极G1A重叠第一半导体层807。第一电容电极AM5重叠第二栅极电极G2。因此,第一电容电极AM5、绝缘层810以及第二栅极电极G2构成一电容C9。在一可能实施例中,电容C8与电容C9作为图2A、图2B、图2C或是图2D的存储电容Cst或是图3A、图3B、图3C或是图3D的存储电容Cst1。

绝缘层812形成于第一栅极电极G1A与第一电容电极AM5之上。第一源/漏极电极841、第二源/漏极电极842、第三源/漏极电极843、连接电极844、第四源/漏极电极845、连接电极848、第五源/漏极电极847以及第六源/漏极电极846位于绝缘层812之上。在本实施例中,第一源/漏极电极841电连接第一源/漏极区S/D1。第二源/漏极电极842电连接第二源/漏极区S/D2。因此,第一栅极电极G1、第一源/漏极电极841以及第二源/漏极电极842构成一第一晶体管。第三源/漏极电极843电连接第三源/漏极区S/D3。连接电极844电连接第二栅极电极G2。第四源/漏极电极845电连接第四源/漏极区S/D4。在本实施例中,第二栅极电极G2、第三源/漏极电极843以及第四源/漏极电极845构成一第二晶体管。连接电极848电连接第四源/漏极电极845、第一电容电极AM5、连接电极811以及第五源/漏极电极847。第五源/漏极电极847电连接第五源/漏极区S/D5。第六源/漏极电极846电连接第六源/漏极区S/D6。在本实施例中,第三栅极电极G3、第五源/漏极电极847以及第六源/漏极电极846构成一第三晶体管。

绝缘层813形成于第一源/漏极电极841、第二源/漏极电极842、第三源/漏极电极843、连接电极844、第四源/漏极电极845、连接电极848、第五源/漏极电极847以及第六源/漏极电极846之上。绝缘层815形成于绝缘层813之上。有机发光二极管816形成于绝缘层815之上。本发明并不限定有机发光二极管显示装置的半导体结构。在本实施例中,有机发光二极管816的阳极847电连接连接电极848,并重叠第一电容电极AM5,但并非用以限制本发明。在其它实施例中,有机发光二极管816可能耦接其它电极。

图8B为本发明的像素的另一半导体结构示意图。图8B相似图8A,不同之处在于,图8B中的第一晶体管的第一栅极电极G1B位于绝缘层806之上。绝缘层810形成于第一栅极电极G1B之上。绝缘层810位于绝缘层812与绝缘层806之间。由于第一栅极电极G1B的特性与图8A中的第一栅极电极G1A相似,故不再赘述。另外,在图8A中,第一栅极电极G1A与第一电容电极AM5位于相同的绝缘层(如812)中。在图8B中,第一栅极电极G1B与第一电容电极AM5位于不同的绝缘层中。再者,图8A及图8B的第一晶体管、第二晶体管以及第三晶体管均为上栅极电极架构。

图9为本发明的像素的另一半导体结构示意图。如图所示,绝缘层902位于基底901之上。在本实施例中,绝缘层902作为一缓冲层。第一电容电极AM6设置于绝缘层902之上。绝缘层903形成于第一电容电极AM6之上。阻挡层905、阻挡层906与阻挡层907设置于绝缘层903之上。在一可能实施例中,第一电容电极AM6的材料与阻挡层905的材料相同。在另一可能实施例中,第一电容电极AM6可与阻挡层905位于相同的绝缘层之中。在本实施例中,第一电容电极AM6位于阻挡层906的下方。

绝缘层904形成于阻挡层905、阻挡层906与阻挡层907之上。第一半导体层909、第二半导体层910以及第三半导体层911设置于绝缘层904之上。第一半导体层909重叠阻挡层905,并具有第一源/漏极区S/D1以及第二源/漏极区S/D2。在一可能实施例中,第一半导体层909的材料为低温多晶硅。第二半导体层910重叠阻挡层906,并具有第三源/漏极区S/D3以及第四源/漏极区S/D4。第三半导体层911重叠阻挡层907,并具有第五源/漏极区S/D5以及第六源/漏极区S/D6。在一可能实施例中,第二半导体层910与第三半导体层911的材料为氧化铟镓锌。

绝缘层908形成于第一半导体层909、第二半导体层910以及第三半导体层911之上。第一栅极电极G1、第二栅极电极G2、连接电极913以及第三栅极电极G3设置于绝缘层908之上。第一栅极电极G1重叠第一半导体层909。在本实施例中,由于绝缘层908隔离第一栅极电极G1与第一半导体层909,故绝缘层908称为一栅极绝缘层。在本实施例中,第一半导体层909、第二半导体层910以及第三半导体层911位于第一电容电极AM6之上。第二栅极电极G2重叠第二半导体层910。另外,由于第二栅极电极G2重叠第一电容电极AM6,因此第二栅极电极G2、绝缘层908、绝缘层904、绝缘层903以及第一电容电极AM6构成一电容C10。另外,第三栅极电极G3重叠第三半导体层911。连接电极913电连接第一电容电极AM6。

绝缘层912形成于第一栅极电极G1、第二栅极电极G2、连接电极913以及第三栅极电极G3之上。第二电容电极AM7设置于绝缘层912之上。在本实施例中,第二电容电极AM7重叠第二栅极电极G2。因此,第二电容电极AM7、绝缘层912以及第二栅极电极G2构成一电容C11。在一可能实施例中,电容C11与电容C10可作为图2A、图2B、图2C、图2D、图3A、图3B、图3C或是图3D中的存储电容Cst或Cst1。

绝缘层914形成于第二电容电极AM7之上。第一源/漏极电极941、第二源/漏极电极942、第三源/漏极电极943、连接电极944、第四源/漏极电极945、连接电极948、第五源/漏极电极947以及第六源/漏极电极946位于绝缘层914之上。在本实施例中,第一源/漏极电极941电连接第一源/漏极区S/D1。第二源/漏极电极942电连接第二源/漏极区S/D2。在一可能实施例中,第一栅极电极G1、第一源/漏极电极941与第二源/漏极电极942构成一第一晶体管。第三源/漏极电极943电连接第三源/漏极区S/D3。连接电极944电连接第二栅极电极G2。第四源/漏极电极945电连接第四源/漏极区S/D4。在本实施例中,第二栅极电极G2、第三源/漏极电极943与第四源/漏极电极945构成一第二晶体管。连接电极948电连接第四源/漏极电极945、第二电容电极AM7、连接电极913以及第五源/漏极电极947。第五源/漏极电极947电连接第五源/漏极区S/D6。第六源/漏极电极946电连接第六源/漏极区S/D6。在本实施例中,第三栅极电极G3、第五源/漏极电极947与第六源/漏极电极946构成一第三晶体管。

绝缘层915形成于第一源/漏极电极941、第二源/漏极电极942、第三源/漏极电极943、连接电极944、第四源/漏极电极945、连接电极948、第五源/漏极电极947以及第六源/漏极电极946之上。绝缘层916形成于绝缘层915之上。有机发光二极管917形成于绝缘层916之上。本发明并不限定有机发光二极管显示装置的半导体结构。任何有机发光二极管显示装置的半导体结构均可应用至图9中。在本实施例中,有机发光二极管917的电极918电连接至连接电极948,但并非用以限制本发明。另外,电极918重叠第一电容电极AM6。

图10A为本发明的像素的另一半导体结构示意图。如图所示,绝缘层1002形成于基底1001之上。第一电容电极AM8设置于绝缘层1002之上。绝缘层1003形成于第一电容电极AM8之上。阻挡层1005A设置于绝缘层1003之上。绝缘层1004形成于阻挡层1005A之上。第一半导体层1007A设置于绝缘层1004之上。第一半导体层1007A重叠阻挡层1005A,并具有第一源/漏极区S/D1以及第二源/漏极区S/D2。在一可能实施例中,第一半导体层1007A的材料为低温多晶硅,但并非用以限制本发明。

绝缘层1006形成于第一半导体层1007A之上。第一栅极电极G1设置于绝缘层1006之上。第一栅极电极G1重叠第一半导体层1007A。绝缘层1008形成于第一栅极电极G1之上。第二栅极电极G2与第三栅极电极G3设置于绝缘层1008之上。在本实施例中,第二栅极电极G2部分重叠第一电容电极AM8。因此,第二栅极电极G2、绝缘层1008、绝缘层1006、绝缘层1004、绝缘层1003与第一电容电极AM8构成一电容C40。另外,第一电容电极AM8位于阻挡层1005A与基底1001之间。再者,绝缘层1002作为一缓冲层,并且第一电容电极AM8位于该缓冲层之上。

绝缘层1009形成于第二栅极电极G2与第三栅极电极G3之上。第二半导体层1011以及第三半导体层1012设置于绝缘层1009之上。第二半导体层1011重叠第二栅极电极G2,并具有第三源/漏极区S/D3以及第四源/漏极区S/D4。在一可能实施例中,第二半导体层1011的材料为氧化铟镓锌。第三半导体层1012重叠第三栅极电极G3,并具有第五源/漏极区S/D5以及第六源/漏极区S/D6。在一可能实施例中,第三半导体层1012的材料为氧化铟镓锌。

在本实施例中,第一源/漏极电极1041、第二源/漏极电极1042、第三源/漏极电极1043、第四源/漏极电极1044、连接电极1047、第五源/漏极电极1046以及第六源/漏极电极1045位于绝缘层1009之上。如图所示,第一源/漏极电极1041电连接第一源/漏极区S/D1。在一可能实施例中,电极1041接收一数据信号(如D

绝缘层1010形成于第一源/漏极电极1041、第二源/漏极电极1042、第三源/漏极电极1043、第二半导体层1011、第四电极1044、连接电极1047、第五源/漏极电极1046、第三半导体层1012以及第六源/漏极电极1045之上。绝缘层1013形成于绝缘层1010之上。有机发光二极管1014形成于绝缘层1013之上。本发明并不限定有机发光二极管显示装置的半导体结构。任何有机发光二极管显示装置的半导体结构均可应用至图10A-图10F中。在本实施例中,有机发光二极管1014的电极1015电连接连接电极1047。

在本实施例中,第一电容电极AM8位于阻挡层1005A的下方。另外,由于第一栅极电极G1位于第一半导体层1007A的上方,故第一晶体管为上栅极电极架构。由于第二栅极电极G2位于第二半导体层1011的下方,故第二晶体管为下栅极电极架构。同样地,由于第三栅极电极G3也是位于第三半导体层1012的下方,故第三晶体管亦为下栅极电极架构。

图10B为本发明的像素的另一半导体结构示意图。图10B相似图10A,不同之处在于,第一半导体层1007B的第二源/漏极区S/D2重叠第一电容电极AM8。因此,第二源/漏极区S/D2、绝缘层1004、绝缘层1003与第一电容电极AM8构成一电容C12。

图10C为本发明的像素的另一半导体结构示意图。图10C相似图10B,不同之处在于,图10C多了一第二电容电极AM9。第二电容电极AM9位于绝缘层1006之上。第二电容电极AM9重叠第二栅极电极G2。因此,第二电容电极AM9、绝缘层1008与第二栅极电极G2构成一电容C14。另外,第二电容电极AM9重叠第二源/漏极区S/D2。因此,第二电容电极AM9、绝缘层1006与第二源/漏极区S/D2构成一电容C13。在本实施例中,第二源/漏极电极1042往第三源/漏极电极1043延伸,但未电连接第三源/漏极电极1043。在此例中,第二源/漏极电极1042、绝缘层1010、绝缘层1013与电极1015构成一电容C15。

图10D为本发明的像素的另一半导体结构示意图。图10D相似图10B,不同之处在于,在图10D中,第一栅极电极G1C与第二栅极电极G2设置在相同的绝缘层(如1009)中。另外,在图10D中,第二源/漏极电极1042往第三源/漏极电极1043延伸。在此例中,第二源/漏极电极1042、绝缘层1010、绝缘层1013以及电极1015构成电容C15。

图10E为本发明的像素的另一半导体结构示意图。图10E相似图10A,不同之处在于,在图10E中,第一栅极电极G1C与第二栅极电极G2位于相同的绝缘层,如1009。另外,阻挡层1005E重叠第一电容电极AM8。因此,阻挡层1005E、绝缘层1003与第一电容电极AM8构成一电容C16。在本实施例中,第二电极1042电连接第二源/漏极区S/D2、阻挡层1005E以及第二栅极电极G2。

图10F为本发明的像素的另一半导体结构示意图。图10F相似图10E,不同之处在于,图10F还具有连接电极1046与连接电极1048。连接电极1046与连接电极1048位于绝缘层1006之上。连接电极1046电连接第一电容电极AM8。在此例中,连接电极1047电连接连接电极1046。因此,连接电极1047间接地电连接第一电容电极AM8。另外,第二源/漏极电极1042通过连接电极1048间接地电连接阻挡层1005E。

图11A为本发明的像素的另一半导体结构示意图。如图所示,绝缘层1102形成于基底1101之上。第一电容电极AM19与第二电容电极AM10设置于绝缘层1102之上。在本实施例中,第一电容电极AM19并未电连接第二电容电极AM10。绝缘层1103形成于第一电容电极AM19与第二电容电极AM10之上。

第一半导体层1105设置于绝缘层1103之上。第一半导体层1105重叠第一电容电极AM9,并具有第一源/漏极区S/D1与第二源/漏极区S/D2。在一可能实施例中,第一半导体层1105的材料为低温多晶硅。绝缘层1104形成于第一半导体层1105之上。第一栅极电极G1设置于绝缘层1104之上。第一栅极电极G1重叠第一半导体层1105。绝缘层1106形成于第一栅极电极G1之上。

第二栅极电极G2与第三栅极电极G3设置于绝缘层1106之上。在本实施例中,第二栅极电极G2重叠第二电容电极AM10。因此,第二栅极电极G2、绝缘层1106、绝缘层1104、绝缘层1103与第二电容电极AM10构成一电容C17。绝缘层1107形成于第二栅极电极G2与第三栅极电极G3之上。

第二半导体层1109与第三半导体层1110设置于绝缘层1107之上。第二半导体层1109重叠第二栅极电极G2,并具有第三源/漏极区S/D3与第四源/漏极区S/D4。第三半导体层1110重叠第三栅极电极G3,并具有第五源/漏极区S/D5与第六源/漏极区S/D6。在一可能实施例中,第二半导体层1109与第三半导体层1110的材料为氧化铟镓锌。

第一源/漏极电极1141、第二源/漏极电极1142、第三源/漏极电极1143、第四源/漏极电极1144、连接电极1147、第五源/漏极电极1146以及第六源/漏极电极1145位于绝缘层1107之上。如图所示,第一源/漏极电极1141电连接第一源/漏极区S/D1。第二源/漏极电极1142电连接第二源/漏极区S/D2与第二栅极电极G2。在本实施例中,第一栅极电极G1、第一源/漏极电极1141与第二源/漏极电极1142构成一第一晶体管。在此例中,第一电容电极AM19作为第一晶体管的阻挡层。

第三源/漏极电极1143电连接第三源/漏极区S/D3。第四源/漏极电极1144电连接第四源/漏极区S/D4。在本实施例中,第二栅极电极G2、第三源/漏极电极1143与第四源/漏极电极1144构成一第二晶体管。连接电极1147电连接第四源/漏极电极1144、第五源/漏极电极1146以及第二电容电极AM10。第五源/漏极电极1146电连接第五源/漏极区S/D5。第六源/漏极电极1145电连接第六源/漏极区S/D6。在本实施例中,第三栅极电极G3、第五源/漏极电极1146与第六源/漏极电极1145构成一第三晶体管。

绝缘层1108形成于第一源/漏极电极1141、第二源/漏极电极1142、第三源/漏极电极1143、第二半导体层1109、第四源/漏极电极1144、连接电极1147、第五源/漏极电极1146、第三半导体层1110以及第六源/漏极电极1145之上。绝缘层1111形成于绝缘层1108之上。有机发光二极管1112形成于绝缘层1111之上。本发明并不限定有机发光二极管显示装置的半导体结构。任何有机发光二极管显示装置的半导体结构均可应用至图11A~图11C中。在本实施例中,有机发光二极管1112的电极1113电连接连接电极1147,但并非用以限制本发明。

图11B为本发明的像素的另一半导体结构示意图。图11B相似图11A,不同之处在于,图11B还具有一阻挡层1114。阻挡层1114位于绝缘层1102之上,并重叠第一半导体层1105。另外,在本实施例中,第二电容电极AM10与第一半导体层1105位于相同的绝缘层(如1104)中。在本实施例中,第二栅极电极G2、绝缘层1106、绝缘层1104与第二电容电极AM10构成一电容C18。

图11C为本发明的像素的另一半导体结构示意图。图11C相似图11A,不同之处在于图11C的第一电容电极AM19位于第一源/漏极电极1141与第二源/漏极电极1142的至少一者与第一栅极G1之间。在本实施例中,第一电容电极AM19重叠重叠第一栅极G1与电极1113。在一可能实施例中,第一电容电极AM19的材料与第二栅极电极G2的材料相同。在另一可能实施例中,第一电容电极AM19的电位的绝对值大于0。

图12为本发明的像素的另一半导体结构示意图。图12与图6相似,不同之处在于,在图12中,多了电极1201、电极1202与电极1203。如图所示,电极1201、电极1202与1203彼此电连接,其中电极1202电连接第一栅极电极G1。在一可能实施例中,电极1202耦接至一栅极驱动器(如图1的110)。通过多个电极电连接电极1202,以避免电极1202因断线而无法正常传送扫描信号予第一栅极电极G1。在本实施例中,电极1201、电极1202与1203位于一凹槽1200中。凹槽1200的设计用以增加半导体结构的可弯曲性。

图13为本发明的像素的另一半导体结构示意图。如图所示,阻挡层1303设置于基底1301之上。绝缘层1302形成于阻挡层1303之上。第一半导体层1305设置于绝缘层1302之上。第一半导体层1305重叠阻挡层1303,并具有第一源/漏极区S/D1以及第二源/漏极区S/D2。在一可能实施例中,第一半导体层1305的材料为低温多晶硅。绝缘层1304形成于第一半导体层1305之上。

第一栅极电极G1、第三栅极电极G3以及第一电容电极AM11设置于绝缘层1304之上。第一栅极电极G1重叠第一半导体层1305。绝缘层1306形成于第一栅极电极G1、第三栅极电极G3以及第一电容电极AM11之上。第一源/漏极电极1341、第二源/漏极电极1342、第二栅极G2与连接电极1343设置于绝缘层1306之上。第一源/漏极电极1341电连接第一源/漏极区S/D1。第二源/漏极电极1342电连接第二源/漏极区S/D2。在本实施例中,第一栅极电极G1、第一源/漏极电极1341与第二源/漏极电极1342构成一第一晶体管。连接电极1343重叠第一电容电极AM11。因此,电极1343、绝缘层1306与第一电容电极AM11构成一电容C19。在一可能实施例中,电容C19可作为图2B或图2C中的辅助电容250或是图3B、图3C或图3D或的辅助电容360。在此例中,第一电容电极AM11的电位的绝缘值可能大于0。在另一可能实施例中,电极1343电连接第二栅极电极G2。

绝缘层1307形成于一源/漏极电极1341、第二源/漏极电极1342、第二栅极G2与连接电极1343之上。第二半导体层1310、第三半导体层1311以及第四半导体层1309设置于绝缘层1307之上。第四半导体层1309具有第七源/漏极区S/D7以及第八源/漏极区S/D8。在一可能实施例中,第四半导体层1309的材料为氧化铟镓锌。第二半导体层1310重叠第二栅极电极G2,并具有第三源/漏极区S/D3与第四源/漏极区S/D4。在一可能实施例中,第二半导体层1310的材料为氧化铟镓锌。第三半导体层1311重叠第三栅极电极G3,并具有第五源/漏极区S/D5与第六源/漏极区S/D6。在一可能实施例中,第三半导体层1311的材料为氧化铟镓锌。

第三源/漏极电极1346、第四源/漏极电极1347、连接电极1351、第五源/漏极电极1350、第六源/漏极电极1348、第七源/漏极电极1344以及第八源/漏极电极1345位于绝缘层1307之上。在本实施例中,第七源/漏极电极1344电连接第七源/漏极区S/D7。第八源/漏极电极1345电连接第八源/漏极区S/D8。第三源/漏极电极1346电连接第三源/漏极区S/D3。第四源/漏极电极1347电连接第四源/漏极区S/D4。在本实施例中,第二栅极电极G2、第三源/漏极电极1346与第四源/漏极电极1347构成一第二晶体管。连接电极1351电连接第四源/漏极电极1347以及与第五源/漏极电极1350。第五源/漏极电极1350电连接第五源/漏极区S/D5。第六源/漏极电极1348电连接第六源/漏极区S/D6。在本实施例中,第三栅极电极G3、第五源/漏极电极1350与第六源/漏极电极1348构成一第三晶体管。

绝缘层1308形成于第七源/漏极电极1344、第四半导体层1309、第八源/漏极电极1345、第三源/漏极电极1346、第二半导体层1310、第四源/漏极电极1347、连接电极1351、第五源/漏极电极1350、第三半导体层1311以及第六源/漏极电极1348之上。第四栅极电极G4与连接电极1349设置于绝缘层1308之上。第四栅极电极G4重叠第四半导体层1309。在本实施例中,第四栅极电极G4、第七源/漏极电极1344与第八源/漏极电极1345构成一第四晶体管。连接电极1349电连接第八源/漏极电极1345与第三源/漏极电极1346。由于连接电极1349重叠第一电容电极AM11,故连接电极1349、绝缘层1308、绝缘层1307、绝缘层1306以及第一电容电极AM11构成一电容C20。在一可能实施例中,电容C20可作为图2C中的辅助电容260、图3C或图3D中的辅助电容370。在此例中,通过控制第一电容电极AM11的电压电位,便可稳定连接电极1349与连接电极1343的电位。另外,连接电极1349、绝缘层1308、绝缘层1307与第二源/漏极电极1342构成一电容C21。在一可能实施例中,电容C21可作为图2A、图2B、图2C、图2D中的存储电容Cst或是图3A、图3B、图3C、图3D中的存储电容Cst1。

绝缘层1312形成于第四栅极电极G4与连接电极1349之上。绝缘层1313形成于绝缘层1312之上。有机发光二极管1314形成于绝缘层1313之上。本发明并不限定有机发光二极管显示装置的半导体结构。任何有机发光二极管显示装置的半导体结构均可应用至图13中。在本实施例中,有机发光二极管1314的电极1315电连接至连接电极1349,但并非用以限制本发明。

图14为本发明的像素的另一半导体结构示意图。如图所示,绝缘层1402形成于基底1401之上。第一电容电极AM12与第二电容电极AM13设置于绝缘层1402之上。绝缘层1403形成于第一电容电极AM12与第二电容电极AM13之上。在本实施例中,第一电容电极AM12、绝缘层1403与第二电容电极AM13构成一电容C22。在一可能实施例中,电容C22作为图2B或图2C的辅助电容250或是图3B、图3C或图3D中的辅助电容360。

阻挡层1405设置于绝缘层1403之上。绝缘层1404形成于阻挡层1405之上。第一半导体层1407设置于绝缘层1404之上。第一半导体层1407重叠阻挡层1405,并具有第一源/漏极区S/D1以及第二源/漏极区S/D2。在本实施例中,第二源/漏极区S/D2重叠阻挡层1405、第一电容电极AM12以及第二电容电极AM13。因此,第二源/漏极区S/D2、绝缘层1404、绝缘层1403以及第一电容电极AM12构成一电容C23。在一可能实施例中,电容C23作为图2C的辅助电容260、图3C或图3D中的辅助电容370。另外。第二源/漏极区S/D2、绝缘层1404、绝缘层1403以及第二电容电极AM13构成一电容C24。

绝缘层1406形成于第一半导体层1407之上。第一栅极电极G1与第三电容电极AM14设置于绝缘层1406之上。第一栅极电极G1重叠第一半导体层1407。由于第三电容电极AM14重叠第二源/漏极区S/D2。因此,第三电容电极AM14、绝缘层1406与第二源/漏极区S/D2构成一电容C25。

绝缘层1408形成于第一栅极电极G1与第三电容电极AM14之上。第二栅极电极G2与第三栅极电极G3设置于绝缘层1408之上。由于第二栅极电极G2重叠第三电容电极AM14,故第二栅极电极G2、绝缘层1408与第三电容电极AM14构成一电容C26。绝缘层1409形成于第二栅极电极G2与第三栅极电极G3之上。

第二半导体层1411以及第三半导体层1412设置于绝缘层1409之上。第二半导体层1411重叠第二栅极电极G2,并具有第三源/漏极区S/D3以及第四源/漏极区S/D4。在一可能实施例中,第二半导体层1411的材料为氧化铟镓锌。第三半导体层1412重叠第三栅极电极G3,并具有第五源/漏极区S/D5以及第六源/漏极区S/D6。在一可能实施例中,第三半导体层1412的材料为氧化铟镓锌。

第一源/漏极电极1441、第二源/漏极电极1442、第三源/漏极电极1443、第四源/漏极电极1444、连接电极1447、第五源/漏极电极1446以及第六源/漏极电极1445位于绝缘层1409之上。在本实施例中,第一源/漏极电极1441电连接第一源/漏极区S/D1。第二源/漏极电极1442电连接第二源/漏极区S/D2与第二栅极电极G2。在本实施例中,第一栅极电极G1、第一源/漏极电极1441与第二源/漏极电极1442构成一第一晶体管。第三源/漏极电极1443电连接第三源/漏极区S/D3。第四源/漏极电极1444电连接第四源/漏极区S/D4。在本实施例中,第二栅极电极G2、第三源/漏极电极1443与第四源/漏极电极1444构成一第二晶体管。连接电极1447电连接第四源/漏极电极1444、第二电容电极AM13以及第五源/漏极电极1446。第五源/漏极电极1446电连接第五源/漏极区S/D5。第六源/漏极电极1445电连接第六源/漏极区S/D6。在本实施例中,第三栅极电极G3、第五源/漏极电极1446与第六源/漏极电极1445构成一第三晶体管。

绝缘层1410形成于第一源/漏极电极1441、第二源/漏极电极1442、第三源/漏极电极1443、第二半导体层1411、第四源/漏极电极1444、连接电极1447、第五源/漏极电极1446、第三半导体层1412以及第六源/漏极电极1445之上。绝缘层1413形成于绝缘层1410之上。有机发光二极管1414形成于绝缘层1413之上。本发明并不限定有机发光二极管显示装置的半导体结构。任何有机发光二极管显示装置的半导体结构均可应用至图14中。在本实施例中,有机发光二极管1414的电极1415电连接至连接电极1447,但并非用以限制本发明。另外,电极1415、绝缘层1413、绝缘层1410以及第二源/漏极电极1442构成一电容C27。在一可能实施例中,电容C24、电容C25、电容C26与电容C27作为图2A、图2B、图2C、图2D中的存储电容Cst或是图3A、图3B、图3C、图3D中的存储电容Cst1。

图15为本发明的像素的另一半导体结构示意图。在本实施例中,绝缘层1502形成于基底1501之上。第一电容电极AM15设置在绝缘层1502之上。绝缘层1503形成于第一电容电极AM15之上。阻挡层1505设置于绝缘层1503之上。绝缘层1504形成于阻挡层1505之上。第一半导体层1507设置于绝缘层1504之上。第一半导体层1507重叠阻挡层1505,并具有第一源/漏极区S/D1以及第二源/漏极区S/D2。在本实施例中,第二源/漏极区S/D2重叠第一电容电极AM15。因此,第二源/漏极区S/D2、绝缘层1504、绝缘层1503以及第一电容电极AM15构成一电容C28。

绝缘层1506设置在第一半导体层1507之上。第一栅极电极G1与第二电容电极AM16设置于绝缘层1506之上。第一栅极电极G1重叠第一半导体层1507。第二电容电极AM16重叠第二源/漏极区S/D2。因此,一电容C29形成于第二电容电极AM16与第二源/漏极区S/D2之间。绝缘层1508设置于第一栅极电极G1与第二电容电极AM16之上。

第二栅极电极G2与第三栅极电极G3设置于绝缘层1508之上。第二栅极电极G2重叠第二电容电极AM16。因此,一电容C30形成于第二栅极电极G2与第二电容电极AM16之间。绝缘层1509设置于第二栅极电极G2与第三栅极电极G3之上。

第二半导体层1511以及第三半导体层1512设置于绝缘层1509之上。第二半导体层1511重叠第二栅极电极G2,并具有第三源/漏极区S/D3以及第四源/漏极区S/D4。第三半导体层1512重叠第三栅极电极G3,并具有第五源/漏极区S/D5以及第六源/漏极区S/D6。

第一源/漏极电极1541、第二源/漏极电极1542、第三源/漏极电极1543、第四源/漏极电极1544、连接电极1547、第五源/漏极电极1546以及第六源/漏极电极1545设置于绝缘层1509之上。第一源/漏极电极1541电连接第一源/漏极区S/D1。第二源/漏极电极1542电连接第二源/漏极区S/D2以及第二栅极电极G2。在本实施例中,第一栅极电极G1、第一源/漏极电极1541与第二源/漏极电极1542构成一第一晶体管。第三源/漏极电极1543电连接第三源/漏极区S/D3。第四源/漏极电极1544电连接第四源/漏极区S/D4。在本实施例中,第二栅极电极G2、第三源/漏极电极1543与第四源/漏极电极1544构成一第二晶体管。连接电极1547电连接第四源/漏极电极1544、第一电容电极AM15以及第五源/漏极电极1546。第五源/漏极电极1546电连接第五源/漏极区S/D5。第六源/漏极电极1545电连接第六源/漏极区S/D6。在本实施例中,第三栅极电极G3、第五源/漏极电极1546与第六源/漏极电极1545构成一第三晶体管。

绝缘层1510设置于第一源/漏极电极1541、第二源/漏极电极1542、第三源/漏极电极1543、第四源/漏极电极1544、连接电极1547、第五源/漏极电极1546以及第六源/漏极电极1545之上。第三电容电极AM17设置于绝缘层1510之上。在本实施例中,第三电容电极AM17重叠第二源/漏极电极1542。因此,第三电容电极AM17、绝缘层1510以及第二源/漏极电极1542构成一电容C31。绝缘层1516设置于第三电容电极AM17之上。绝缘层1513设置于绝缘层1516之上。有机发光二极管1514形成于绝缘层1513之上。本发明并不限定有机发光二极管显示装置的半导体结构。任何有机发光二极管显示装置的半导体结构均可应用至图15中。在本实施例中,有机发光二极管1514的电极1515电连接至连接电极1547,但并非用以限制本发明。另外,电极1515与第三电容电极AM17之间具有一电容C32。

在一可能实施例中,电容C28、电容C29以及电容C30作为图2A、图2B、图2C、图2D中的存储电容Cst或是图3A、图3B、图3C、图3D中的存储电容Cst1。另外,电容C31可作为图2B、图2C中的辅助电容250或是图3B、图3C或是图3D中的存储电容360。电容C32可作为图2C中的辅助电容260、图3C或图3D中的辅助电容370。

图16A为本发明的像素的另一半导体结构示意图。在本实施例中,阻挡层1603、阻挡层1604以及阻挡层1605设置于基底1601之上。绝缘层1602设置在阻挡层1603、阻挡层1604以及阻挡层1605之上。第一半导体层1607设置于绝缘层1602之上。第一半导体层1607重叠阻挡层1603,并具有第一源/漏极区S/D1以及第二源/漏极区S/D2。绝缘层1606设置于第一半导体层1607之上。

第一电容电极AM41、第二半导体层1609以及第三半导体层1610设置于绝缘层1606之上。第二半导体层1609重叠阻挡层1604,并具有第三源/漏极区S/D3以及第四源/漏极区S/D4。第三半导体层1610重叠阻挡层1605,并具有第五源/漏极区S/D5以及第六源/漏极区S/D6。绝缘层1608设置于第一电容电极AM41、第二半导体层1609以及第三半导体层1610之上。

第一栅极电极G1、第二栅极电极G2以及第三栅极电极G3设置于绝缘层1608之上。在一可能实施例中,第一栅极电极G1的材料与第一电容电极AM41的材料相同,但并非用以限制本发明。在本实施例中,第一栅极电极G1重叠第一半导体层1607。第二栅极电极G2重叠第二半导体层1609。第三栅极电极G3重叠第三半导体层1610。绝缘层1611设置于第一栅极电极G1、第二栅极电极G2以及第三栅极电极G3之上。

第一源/漏极电极1641、第二源/漏极电极1642、第三源/漏极电极1643、第四源/漏极电极1644、连接电极1647、第五源/漏极电极1646以及第六源/漏极电极1645位于绝缘层1611之上。在本实施例中,第一源/漏极电极1641电连接第一源/漏极区S/D1。在一可能实施例中,第一源/漏极电极1641接收一数据信号(如D

绝缘层1612形成于第一源/漏极电极1641、第二源/漏极电极1642、第三源/漏极电极1643、第四源/漏极电极1644、连接电极1647、第五源/漏极电极1646以及第六源/漏极电极1645之上。绝缘层1613设置于绝缘层1612之上。有机发光二极管1614形成于绝缘层1613之上。本发明并不限定有机发光二极管显示装置的半导体结构。任何有机发光二极管显示装置的半导体结构均可应用至图16A~图16B中。在本实施例中,有机发光二极管1614的电极1615电连接第四源/漏极电极1644,但并非用以限制本发明。

电极1615、绝缘层1613、绝缘层1612以及第二源/漏极电极1642构成一电容C34。在一可能实施例中,电容C34可作为图2A、图2B、图2C、图2D中的存储电容Cst或是图3A、图3B、图3C、图3D中的存储电容Cst1。另外,电极1615、绝缘层1613、绝缘层1612、绝缘层1611、绝缘层1618与第一电容电极AM41构成一电容C35。在一可能实施例中,电容C35可作为图2C中的辅助电容260、图3C或图3D中的辅助电容370。在本实施例中,第一电容电极AM41设置于绝缘层1608之中,而绝缘层1608设置于第一栅极电极G1与第一半导体层1607之中。

图16B为本发明的像素的另一半导体结构示意图。图16B相似图16A,不同之处在于,图16B具有一第一电容电极AM18。第一电容电极AM18设置于绝缘层1612之上。在本实施例中,第一电容电极AM18、绝缘层1612与第二源/漏极电极1642构成一电容C36。在一可能实施例中,电容C36可作为图2B、图2C中的辅助电容250或是图3B、图3C、图3D中的辅助电容360。另外,电极1615、绝缘层1613、绝缘层1616与第一电容电极AM18构成一电容C37。在一可能实施例中,电容C37可作为图2C中的辅助电容260或是图3C或图3D中的辅助电容370。

综上所述,通过上述实施例中的任一结构增加图2A、图2B、图2C、图2D中的存储电容Cst的容值或是形成辅助电容250或辅助电容260或是增加图3A、图3B、图3C、图3D中的存储电容Cst1或存储电容Cst2的容值或是形成辅助电容360或辅助电容370。以图3C为例,节点A的电压很容易受到数据信号D

除非另作定义,在此所有词汇(包含技术与科学词汇)均属本发明所属技术领域中具有通常知识者的一般理解。此外,除非明白表示,词汇于一般字典中的定义应解释为与其相关技术领域的文章中意义一致,而不应解释为理想状态或过分正式的语态。

虽然结合以上优选实施例已公开了本发明,然而其并非用以限定本发明,任何所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,可作些许的更动与润饰,因此本发明的保护范围应当以附上的权利要求所界定的为准。

- 显示装置用基板、显示装置用基板的制造方法、显示装置、液晶显示装置、液晶显示装置的制造方法和有机电致发光显示装置

- 有机EL显示装置用粘合剂组合物、有机EL显示装置用粘合剂层、带有机EL显示装置用粘合剂层的偏振膜、以及有机EL显示装置