基于SRAM实现存储及模拟计算的电路及存储及模拟计算系统

文献发布时间:2023-06-19 10:54:12

技术领域

本发明涉及数据处理领域,特别是涉及一种基于SRAM实现存储及模拟计算的电路及存储及模拟计算系统。

背景技术

近年来AI相关技术的快速发展,在让我们的生活更美好的同时,也对各种应用场景下的算力提出了越来越高的要求。模拟运算(Analog Computing),省去了数据搬运造成的时间和功耗上的损失;并且适用于低功耗,高效率场景。在现有技术中,一般仅将SRAM应用于运作存储单元,并不能使SRAM作为基础的模拟运算单元,进而使用效率降低。

发明内容

鉴于以上所述现有技术的缺点,本发明的目的在于提供一种基于SRAM实现存储及模拟计算的电路及存储及模拟计算系统,解决了现有技术中一般仅将SRAM应用于运作存储单元,并不能使SRAM作为基础的模拟运算单元,进而使用效率降低的问题。

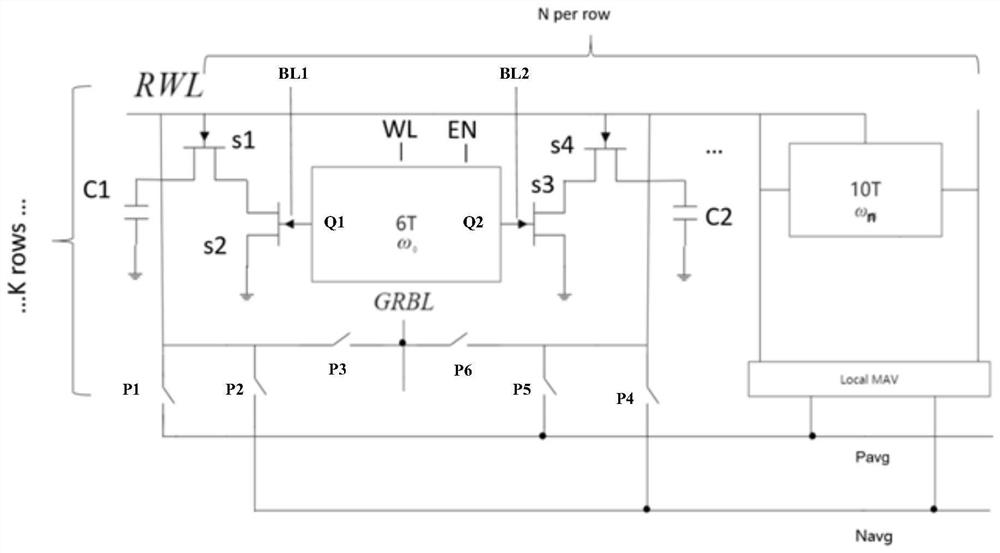

为实现上述目的及其他相关目的,本发明提供一种基于SRAM实现存储及模拟计算的电路,用于进行模拟计算和/或储存流程,所述电路包括:至少一6T SRAM单元,每个单元具有同时输入输出数据的输入输出端Q1以及Q2;第一NMOS管、第二NMOS管、第三NMOS管以及第四NMOS管;六个CMOS传输门,依次记为P1~P6;一端接地的第一电容以及第二电容;其中,所述6T SRAM单元的输入输出端Q1分别连接位线BL1端以及所述第二NMOS管的栅极,所述6TSRAM单元的输入输出端Q2分别连接位线BL2端以及所述第三NMOS管的栅极;所述第一NMOS管的漏极连接所述所述第二NMOS管的漏极,所述第四NMOS管的漏极连接所述第三NMOS管的漏极,且所述第一NMOS管的源极连接所述第一电容的另一端,所述第四NMOS管的源极连接所述第二电容的另一端;所述第一电容的另一端还分别连接CMOS传输门P1、CMOS传输门P2以及CMOS传输门P3;所述第二电容的另一端分别连接CMOS传输门P4、CMOS传输门P5以及CMOS传输门P6;与所述CMOS传输门P3以及CMOS传输门P6连接的输出端GRBL;读字线RWL分别与所述第二NMOS管的栅极、所述第四NMOS管的栅极、所述第一电容的另一端、所述第二电容的另一端、位线BL1端以及位线BL2端连接;字线控制端WL和使能控制端EN分别连接至所述电路的相应电平;所述正向平均电压输出端Pavg以及反向平均电压值输出端Navg分别与CMOS传输门P1、CMOS传输门P2、CMOS传输门P4以及CMOS传输门P5正向连接以及反向连接。

于本发明的一实施例中,所述CMOS传输门P1、CMOS传输门P2、CMOS传输门P4以及CMOS传输门P5用于在所述模拟计算流程中需进行正向平均电压值和/或反向平均电压值计算时打开开关;和/或,所述CMOS传输门P3以及CMOS传输门P6用于在所述模拟计算流程中需进行乘法计算时打开开关。

于本发明的一实施例中,所述模拟计算流程包括:在一个时钟信号内的充电步骤以及计算步骤。

于本发明的一实施例中,所述充电步骤包括:所述充电步骤包括:当所述读字线RWL、字线控制端WL和使能控制端EN输出为高电平时,所述CMOS传输门P3以及CMOS传输门P6输出为低电平时,所述第一电容和第二电容分别依次充电为SRAM单元中预先存储的输入输出端Q1以及Q2的电压;当所述读字线RWL、字线控制端WL和使能控制端EN输出为低电平时,所述CMOS传输门P3以及CMOS传输门P6输出为高电平,所述第一电容和第二电容放电到和GRBL电压相同,以完成乘法计算。

于本发明的一实施例中,所述计算步骤包括:所述计算步骤包括:当输出端GRBL输出为正电压时,所述CMOS传输门P1和CMOS传输门P4接通,所述CMOS传输门P2和CMOS传输门P5关闭,根据所述正向平均电压值输出端Pavg输出的正向平均电压值以及反向平均电压值输出端Navg输出的反向平均电压值相减获得输出电压值;当输出端GRBL输出为负电压时,所述CMOS传输门P2和CMOS传输门P5接通,所述CMOS传输门P1和CMOS传输门P4关闭,根据输出端Q2的输出与所述输出端GRBL的输出电压值进行乘法计算获得输出电压值。

于本发明的一实施例中,所述当输出端GRBL输出为正电压时,所述CMOS传输门P1和CMOS传输门P4接通,所述CMOS传输门P2和CMOS传输门P5关闭,根据所述正向平均电压值输出端Pavg输出的正向平均电压值以及反向平均电压值输出端Navg输出的反向平均电压值相减获得输出电压值的方式包括:当输出端GRBL输出为正电压时,在6T SRAM单元的输入输出端Q1输出为1,所述输入输出端Q2输出为0,所述第一NMOS管通电,所述读字线RWL输出端为高电平,所述第二NMOS管通电,所述正向平均电压值输出端Pavg输出的电压VPavg为0,所述反向平均电压值输出端Navg输出电压值VNavg等于所述输出端GRBL输出电压值VGRBL,则输出电压值V为:V=VPavg-VNavg=0-VGRBL。

于本发明的一实施例中,所述当输出端GRBL输出为负电压时,所述CMOS传输门P2和CMOS传输门P5接通,所述CMOS传输门P1和CMOS传输门P4关闭,根据输出端Q2的输出与所述输出端GRBL的输出电压值进行乘法计算获得输出电压值的方式包括:当输出端GRBL输出为负电压时,在6T SRAM单元的输入输出端Q1输出为0,所述输入输出端Q2输出值Q2为1,所述第二电容的另一端输出电压值为V

于本发明的一实施例中,所述储存流程包括:写入流程以及读出流程;其中,所述写入流程包括:当字线控制端WL以及使能控制端EN同时输出为高电平时,所述6T SRAM单元的输入输出端Q1以及Q2写入数据;所述读出流程包括:当所述使能控制端EN输出为高电平时,所述6T SRAM单元的输入输出端Q1以及Q2读出数据。

为实现上述目的及其他相关目的,本发明提供一种存储及模拟计算系统,所述系统包括:由多个所述的基于SRAM实现存储及模拟计算的电路构成的SRAM阵列;计算模块,连接所述SRAM阵列,用于基于模拟计算公式对所述SRAM阵列的输出电压值进行模拟计算。

于本发明的一实施例中,所述模拟计算公式包括:

其中,所述k为所述SRAM阵列中的第k行的电路,i为所述SRAM阵列中的第i列的电路,所述V

如上所述,本发明的一种基于SRAM实现存储及模拟计算的电路及存储及模拟计算系统,具有以下有益效果:本发明充分利用了SRAM的特性,让SRAM不仅有存的能力,同时又具备了算的能力,通过在每一个单元外接6个开关,赋予其可以进行乘加运算的能力,大大提高了使用效率。

附图说明

图1显示为本发明一实施例中的基于SRAM实现存储及模拟计算的电路的结构示意图。

图2显示为本发明一实施例中的存储及模拟计算系统的结构示意图。

具体实施方式

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

需要说明的是,在下述描述中,参考附图,附图描述了本发明的若干实施例。应当理解,还可使用其他实施例,并且可以在不背离本发明的精神和范围的情况下进行机械组成、结构、电气以及操作上的改变。下面的详细描述不应该被认为是限制性的,并且本发明的实施例的范围仅由公布的专利的权利要求书所限定。这里使用的术语仅是为了描述特定实施例,而并非旨在限制本发明。空间相关的术语,例如“上”、“下”、“左”、“右”、“下面”、“下方”、““下部”、“上方”、“上部”等,可在文中使用以便于说明图中所示的一个元件或特征与另一元件或特征的关系。

在通篇说明书中,当说某部分与另一部分“连接”时,这不仅包括“直接连接”的情形,也包括在其中间把其它元件置于其间而“间接连接”的情形。另外,当说某种部分“包括”某种构成要素时,只要没有特别相反的记载,则并非将其它构成要素,排除在外,而是意味着可以还包括其它构成要素。

其中提到的第一、第二及第三等术语是为了说明多样的部分、成分、区域、层及/或段而使用的,但并非限定于此。这些术语只用于把某部分、成分、区域、层或段区别于其它部分、成分、区域、层或段。因此,以下叙述的第一部分、成分、区域、层或段在不超出本发明范围的范围内,可以言及到第二部分、成分、区域、层或段。

再者,如同在本文中所使用的,单数形式“一”、“一个”和“该”旨在也包括复数形式,除非上下文中有相反的指示。应当进一步理解,术语“包含”、“包括”表明存在所述的特征、操作、元件、组件、项目、种类、和/或组,但不排除一个或多个其他特征、操作、元件、组件、项目、种类、和/或组的存在、出现或添加。此处使用的术语“或”和“和/或”被解释为包括性的,或意味着任一个或任何组合。因此,“A、B或C”或者“A、B和/或C”意味着“以下任一个:A;B;C;A和B;A和C;B和C;A、B和C”。仅当元件、功能或操作的组合在某些方式下内在地互相排斥时,才会出现该定义的例外。

本发明实施例中提供一种基于SRAM实现存储及模拟计算的电路,解决了现有技术中采用深度学习模型进行人脸识别不仅准确度不高以及在实际应用中具有局限性,还具有存储容量大、功耗多、计算延迟高以及对类别间数据的不平衡十分敏感的问题。本发明采用的基于SRAM实现存储及模拟计算的电路,不仅准确度高还还具有轻量级属性,并且适用于大数据集和小数据集,可以在确保一定准确率的情况下,使模型更加灵活,可以将其放在边缘端实现实时推理,并且兼容性和鲁棒性增加。

下面以附图为参考,针对本发明的实施例进行详细说明,以便本发明所述技术领域的技术人员能够容易地实施。本发明可以以多种不同形态体现,并不限于此处说明的实施例。

如图1所示,展示本发明实施例中的基于SRAM实现存储及模拟计算的电路的结构示意图。

用于进行模拟计算和/或储存流程,所述电路包括:

至少一6T SRAM单元ω

第一NMOS管S1、第二NMOS管S2、第三NMOS管S3以及第四NMOS管S4;

六个CMOS传输门,依次记为P1~P6;

一端接地的第一电容C1以及第二电容C2;

其中,所述6T SRAM单元ω

需要说明的是,这里提到的所述第一电容C1的另一端、所述第二电容C2的另一端分别为所述第一电容C1以及所述第二电容C2的非接地端。

可选的,所述CMOS传输门P1、CMOS传输门P2、CMOS传输门P4以及CMOS传输门P5用于在所述模拟计算流程中需进行正向平均电压值和/或反向平均电压值计算时打开开关;和/或,所述CMOS传输门P3以及CMOS传输门P6用于在所述模拟计算流程中需进行乘法计算时打开开关。

具体的,所述CMOS传输门P1、CMOS传输门P2、CMOS传输门P4以及CMOS传输门P5用于在需进行正向平均电压值和/或反向平均电压值计算时打开开关,否则则关闭开关;所述CMOS传输门P3以及CMOS传输门P6用于在所述模拟计算流程中需进行乘法计算时打开开关,否则则关闭开关。

优选的,所述CMOS传输门P1与所述CMOS传输门P4相同,所述CMOS传输门P2与所述CMOS传输门P5相同,所述CMOS传输门P3与所述CMOS传输门P6相同。

可选的,所述储存流程包括:写入流程以及读出流程;其中,所述写入流程包括:当字线控制端WL以及使能控制端EN同时输出为高电平时,所述6T SRAM单元ω

可选的,所述模拟计算流程包括:在一个时钟信号分割成的充电步骤以及计算步骤。

可选的,所述充电步骤包括:所述充电步骤包括:当所述读字线RWL、字线控制端WL和使能控制端EN输出为高电平时,所述CMOS传输门P3以及CMOS传输门P6输出为低电平时,所述第一电容和第二电容分别依次充电为SRAM单元中预先存储的输入输出端Q1以及Q2的电压;当所述读字线RWL、字线控制端WL和使能控制端EN输出为低电平时,所述CMOS传输门P3以及CMOS传输门P6输出为高电平,所述第一电容和第二电容放电到和GRBL电压相同,以完成乘法计算。

可选的,所述计算步骤包括:当输出端GRBL输出为正电压时,所述CMOS传输门P1和CMOS传输门P4接通,所述CMOS传输门P2和CMOS传输门P5关闭,根据所述正向平均电压值输出端Pavg输出的正向平均电压值以及反向平均电压值输出端Navg输出的反向平均电压值相减获得输出电压值;当输出端GRBL输出为负电压时,所述CMOS传输门P2和CMOS传输门P5接通,所述CMOS传输门P1和CMOS传输门P4关闭,根据输出端Q2的输出与所述输出端GRBL的输出电压值进行乘法计算获得输出电压值。

可选的,所述当输出端GRBL输出为正电压时,所述CMOS传输门P1和CMOS传输门P4接通,所述CMOS传输门P2和CMOS传输门P5关闭,根据所述正向平均电压值输出端Pavg输出的正向平均电压值以及反向平均电压值输出端Navg输出的反向平均电压值相减获得输出电压值的方式包括:

在需进行正向平均电压值以及反向平均电压值的计算时,所述CMOS传输门P1、CMOS传输门P2、CMOS传输门P4以及CMOS传输门P5打开,所述CMOS传输门P3与所述CMOS传输门P6关闭;

当输出端GRBL输出为正电压时,在6T SRAM单元的输入输出端Q1输出为1,所述输入输出端Q2输出为0,所述第一NMOS管S1通电,所述读字线RWL输出端为高电平,所述第二NMOS管S2通电,所述正向平均电压值输出端Pavg输出的电压VPavg为0,所述反向平均电压值输出端Navg输出电压值VNavg等于所述输出端GRBL输出电压值VGRBL,根据所述正向平均电压值输出端Pavg输出的正向平均电压值以及反向平均电压值输出端Navg输出的反向平均电压值相减获得输出电压值,则输出电压值V为:

V=V

可选的,所述当输出端GRBL输出为负电压时,所述CMOS传输门P2和CMOS传输门P5接通,所述CMOS传输门P1和CMOS传输门P4关闭,根据输出端Q2的输出与所述输出端GRBL的输出电压值进行乘法计算获得输出电压值的方式包括:

在需进行乘法计算时,所述CMOS传输门P3与所述CMOS传输门P6打开,所述CMOS传输门P1、CMOS传输门P2、CMOS传输门P4以及CMOS传输门P5关闭;

当输出端GRBL输出为负电压时,在6T SRAM单元的输入输出端Q1输出为0,所述输入输出端Q2输出值Q2为1,所述第三NMOS管S3通电,所述读字线RWL输出端为低电平,所述第四NMOS管S4通电,,所述第二电容C2的另一端输出电压值为V

V=Q2xV

如图2展示本发明实施例中的存储及模拟计算系统的结构示意图。

所述系统包括:

由多个如图1所示的所述的基于SRAM实现存储及模拟计算的电路211构成的SRAM阵列21;

计算模块22,连接所述SRAM阵列21,用于基于模拟计算公式对所述SRAM阵列的输出电压值进行模拟计算。

其中,所述基于SRAM实现存储及模拟计算的电路211包括:至少一6T SRAM单元,每个单元具有同时输入输出数据的输入输出端Q1以及Q2;第一NMOS管、第二NMOS管、第三NMOS管以及第四NMOS管;六个CMOS传输门,依次记为P1~P6;需要说明的是,具体各部件的连接关系与图1的连接方式相同,因此在此不作赘述。

可选的,所述基于SRAM实现存储及模拟计算的电路211的数量为至少两个,而图2中均以四个为例。

可选的,所述SRAM阵列21可以复制一个基于SRAM实现存储及模拟计算的电路211的连接方法,延伸成SRAM阵列,同时具备读写以及运算能力。延伸方式可以横向在列里面延伸成N个,也可以在延伸行数成K行,一个阵列总的电路个数=N x K。

可选的,所述模拟计算公式包括:

其中,所述k为所述SRAM阵列中的第k行的电路,i为所述SRAM阵列中的第i列的电路,所述V

具体的,所述计算模块22基于模拟计算公式对所述SRAM阵列的输出电压值进行模拟计算的方式包括:

先分别将第k行第i列的电路对应的6T SRAM单元输入输出端的输出值与对应的第k行第i列的电路中输出端GRBL的输出电压值VGRBLi进行乘法计算,再将各电路计算的乘法值进行求和并除以电路的个数,获得所述SRAM阵列中各电路的输出电压值的平均值;

则再将同一行的电路的输出电压值进行求和,等于所述正向平均电压值输出端Pavg输出的正向平均电压值以及反向平均电压值输出端Navg输出的反向平均电压值相减值。

综上所述,本发明基于SRAM实现存储及模拟计算的电路及存储及模拟计算系统,用于解决了现有技术中一般仅将SRAM应用于运作存储单元,并不能使SRAM作为基础的模拟运算单元,进而使用效率降低的问题。本发明充分利用了SRAM的特性,让SRAM不仅有存的能力,同时又具备了算的能力,通过在每一个单元外接6个开关,赋予其可以进行乘加运算的能力,大大提高了使用效率。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

上述实施例仅示例性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,但凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

- 基于SRAM实现存储及模拟计算的电路及存储及模拟计算系统

- 基于SRAM实现多比特权重存储与计算的电路及存储与模拟计算系统