提升共模瞬变抗扰度的隔离器及信号产生方法

文献发布时间:2023-06-19 11:14:36

技术领域

本发明涉及一种提升共模瞬变抗扰度的隔离器及信号产生方法。

背景技术

在一些电子设备中,同时存在可承受高电压的电路与无法承受高电压的电路。为了避免高电压对无法承受高电压的电路造成损坏,必须使用隔离器(isolator)将可承受高电压的电路与无法承受高电压的电路隔离开来。在需要隔离器的电子设备中,共模瞬变(common-mode transient)是导致信号传输错误的主要原因之一。共模瞬变抗扰(common-mode transient immunity,CMTI)的能力通常以kV/ms或kV/us为单位,CMTI值反映的是隔离器对于出现在隔离器的输入端和输出端之间的噪声的抵抗能力。一般来说,电子设备的精密越高,所要求的CMTI值就越高。例如,电动车、马达驱动装置及太阳能的电子设备等皆要求隔离器具备较高的CMTI值。有鉴于此,如何提高隔离器的共模瞬变抗扰能力是业界研究的重点之一。

发明内容

本发明的一方面公开一种隔离器。隔离器包括一输入侧电路、一输出侧电路及一信号传递单元。输入侧电路用以接收一输入信号,依据输入信号产生一编码信号。信号传递单元耦接输入侧电路,用以接收及传递编码信号。输出侧电路耦接信号传递单元,用以接收由信号传递单元传递的编码信号。编码信号包括一第一部分及一第二部分。第一部分为一脉冲信号,第二部分为一非振幅编码信号。

本发明的另一方面公开一种隔离器的信号产生方法。信号产生方法包括:藉由隔离器的一输入侧电路依据一输入信号产生一第一信号;藉由输入侧电路依据输入信号及该第一信号产生一第二信号;以及藉由输入侧电路依据第一信号及第二信号产生一编码信号,其中编码信号包括对应于第一信号的一第一部分及对应于第二信号的一第二部分,第一部分为一脉冲信号,第二部分为一非振幅编码信号。

为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合附图详细说明如下:

附图说明

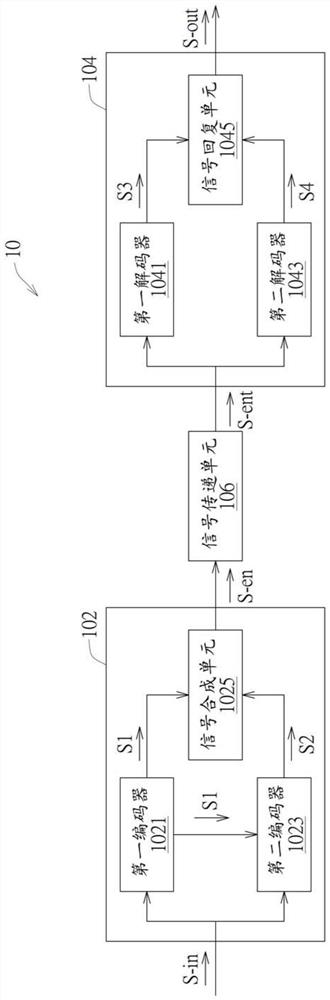

图1绘示依据本发明一实施例的隔离器的方块图。

图2绘示依据本发明另一实施例的隔离器的方块图。

图3A绘示依据本发明一实施例的隔离器的信号波形图。

图3B绘示依据本发明另一实施例的隔离器的信号波形图。

图4绘示依据本发明又一实施例的隔离器的方块图。

图5绘示依据本发明又一实施例的隔离器的信号波形图。

图6绘示依据本发明一实施例的信号产生方法的流程图。

图7绘示依据本发明一实施例的信号合成单元的方块图。

【符号说明】

10、20、40:隔离器

102、202、402:输入侧电路

104、204、404:输出侧电路

106、206、406:信号传递单元

1021、2021、4021:第一编码器

1023、2023、4023:第二编码器

1025、2025、4025:信号合成单元

1041、2041、4041:第一解码器

1043、2043、4043:第二解码器

1045、2045、4045:信号回复单元

S-in:输入信号

S-out:输出信号

S1:第一信号

S2:第二信号

S3:第三信号

S4:第四信号

Trg1:第一触发信号

S-en:编码信号

S-ent:经传送的编码信号

S-ft1:第一滤波信号

S-ft2:第二滤波信号

S-ft3:第三滤波信号

S-ft4:第四滤波信号

S-de1:第一解码信号

S-de2:第二解码信号

S-de4:第四解码信号

EdD:信号边沿检测器

PE:脉冲编码器

OSC:振荡器

OSC1:第一振荡器

OSC2:第二振荡器

FE:频率编码器

C:电容

FT:滤波器

FT1:第一滤波器

FT2:第二滤波器

FT3:第三滤波器

ED:包络检测器

ED1:第一包络检测器

ED2:第二包络检测器

CMP:比较器

CMP1:第一比较器

CMP2:第二比较器

具体实施方式

请参照图1,图1绘示依据本发明一实施例的隔离器的方块图。隔离器10包括一输入侧电路102、一输出侧电路104以及一信号传递单元106。信号传递单元106耦接至输入侧电路102及输出侧电路104。信号传递单元106可电性隔离输入侧电路102及输出侧电路104。输入侧电路102用以接收一输入信号,并将输入信号S-in编码为编码信号S-en。信号传递单元将编码信号S-en传递至输出侧电路104成为经传送的编码信号S-ent。输出侧电路104用以接收经传送的编码信号S-ent,并将经传送的编码信号S-ent解码为输出信号S-out。

在一实施例中,输入侧电路102可耦接至一第一电路(未绘示),输出侧电路104可耦接至一第二电路(未绘示),其中第一电路所能承受的电压较低,第二电路所能承受的电压较高。为了避免第二电路中所使用电压对第一电路造成损坏,因此需要藉由隔离器10来传递信号以及将第一电路与第二电路隔离。例如,在马达设备中,第一电路可为用以产生控制马达转速的控制信号的电路,第二电路可为依据控制信号驱动马达转动的驱动电路。

输入侧电路102包括一第一编码器1021、一第二编码器1023及一信号合成单元1025。在一实施例中,输入信号S-in为一脉冲宽度调制(Pulse Width Modulation,PWM)信号。第一编码器1021用以接收输入信号S-in。第一编码器1021检测输入信号S-in的信号边沿(signal edge),并依据输入信号S-in的信号边沿产生一第一信号S1。第一信号S1可为一脉冲信号(pulse)。第二编码器1023耦接至第一编码器1021。第二编码器1023用以依据输入信号S-in及第一信号S1产生一第二信号S2。第二信号S2可为一非振幅编码信号,例如一频率编码信号或一相位编码信号。信号合成单元1025耦接至第一编码器1021及第二编码器1023。信号合成单元1025用以将第一信号S1及第二信号S2合成以产生一编码信号S-en。编码信号S-en包括对应于第一信号S1的一第一部分及对应于第二信号S2的一第二部分。换句话说,本实施例中的编码信号S-en可包括脉冲信号的成分与非振幅编码信号的成分。编码信号S-en藉由信号传递单元106由输入侧电路102传递至输出侧电路104成为经传送的编码信号S-ent。

输出侧电路104包括一第一解码器1041、一第二解码器1043及一信号回复单元1045。第一解码器1041用以取出经传送的编码信号S-ent的第一部分(即脉冲信号的成分),并依据经传送的编码信号S-ent的第一部分产生一第三信号S3。第二解码器1043用以取出经传送的编码信号S-ent的第二部分,并依据经传送的编码信号S-ent的第二部分产生一第四信号S4。信号回复单元1045依据第三信号S3及第四信号S4产生输出信号S-out。进一步的细节将在下文详述。

请参照图2,图2绘示依据本发明另一实施例的隔离器的方块图。图2的实施例中绘示了第一编码器、第二编码器、第一解码器及第二解码器的进一步细节。隔离器20包括一输入侧电路202、一输出侧电路204及一信号传递单元206。输入侧电路202包括一第一编码器2021、一第二编码器2023及一信号合成单元2025。输出侧电路204包括一第一解码器2041、一第二解码器2043及一信号回复单元2045。

第一编码器2021包括一信号边沿检测器EdD及一脉冲编码器PE。在本实施例中,信号边沿检测器EdD在检测到输入信号S-in的上升沿(rising edge)及下降沿(followingedge)时会发送一个触发信号Trg1给脉冲编码器PE。脉冲编码器PE根据触发信号Trg1产生第一信号S1。在本实施例中,对应于输入信号S-in的上升沿与下降沿所产生出的第一信号S1会是相同的。在一个实际的例子中,对应于输入信号S-in的上升沿所产生出的第一信号S1是一个正脉冲,对应于输入信号S-in的下降沿所产生出的第一信号S1也是正脉冲。

第二编码器2023包括一第一振荡器OSC1、一第二振荡器OSC2及一频率编码器FE。第一振荡器OSC1及第二振荡器OSC2用以接收第一信号S1,并由第一信号S1触发而开始振荡。第一振荡器OSC1输出振荡频率为第一频率的第一振荡信号f1,第二振荡器OSC2输出振荡频率为第二频率的第二振荡信号f2。频率编码器FE耦接至第一振荡器OSC1及第二振荡器OSC2。在一实施例中,第一振荡器OSC1及第二振荡器OSC2在受到第一信号S1的触发后会在振荡一预设时间后停止,以节省功率消耗。例如,预设时间可根据以下方式设定:第一振荡信号f1的持续时间可小于或等于该输入信号维持为高电平的时间,且第二振荡信号f2的持续时间可小于或等于该输入信号维持为低电平的时间。频率编码器FE用以接收输入信号S-in,并判断输入信号S-in的电平,当输入信号S-in为高电平时,以第一频率的第一振荡信号f1编码输入信号S-in,当输入信号S-in为低电平时,以第二频率的第二振荡信号f2编码输入信号S-in,并将编码后的信号做为第二信号S2输出。

信号合成单元2025用以合成第一信号S1及第二信号S2以产生编码信号S-en。信号合成单元2025可采用直接耦合或电容耦合的方式,也可通过简单电路合成的方式来实现。

在一实施例中,信号合成单元2025为一直接耦合电路。直接耦合电路可接收第一信号S1和第二信号S2,将第一信号S1和第二信号S2相加,并产生编码信号S-en。

在另一实施例中,信号合成单元2025为一电容耦合电路。电容耦合电路包括一电容。电容的一第一端与一第二端分别接收第一信号S1和第二信号S2,并在第二端产生编码信号S-en。

在又一实施例中,如图7所示,信号合成单元2025可包括一第一延迟电路DLY1、一第二延迟电路DLY2、一D型触发器DFF以及一多工器MUX。第一延迟电路DLY1接收第一信号S1,产生经延迟的第一信号。第二延迟电路DLY2接受延迟后的第一信号S1,并产生经另一次延迟且被反相的第一信号。D型触发器DFF接收经延迟的第一信号与经另一次延迟且被反相的第一信号,产生一选择信号sel。多工器MUX接收第一信号S1与第二信号S2,并根据选择信号sel,产生编码信号S-en。当选择信号sel为低电平时,多工器MUX输出第一信号S1作为编码信号,当选择信号sel为高电平时,多工器MUX输出第二信号S2作为编码信号S-en。

在输入侧电路202中,第一编码器2021根据输入信号S-in的信号边沿产生的第一信号S1会被用做唤醒第二编码器2023的第一振荡器OSC1及第二振荡器OSC2的信号,而令第二编码器2023可以在第一信号S1产生后随即开始产生第二信号S2。如此一来,可以使得信号合成单元2025能够在不用调整第一信号S1与第二信号S2的时序的前提下,简单地将第一信号S1及第二信号S2合成为编码信号S-en。

从图3A绘示的波形图可看出,输入信号S-in的上升沿会被编码为一个正脉冲信号后接续一个频率为第一频率的频率编码信号,输入信号S-in的下降沿会被编码为一个正脉冲信号后接续一个频率为第二频率的频率编码信号。换句话说,输出侧电路204可藉由辨识正脉冲信号后接续的频率编码信号的频率来确定所收到是代表上升沿的信号还是代表下降沿的信号。

回到图2,第一解码器2041包括一第一滤波器FT1及一第一比较器CMP1。第一滤波器FT1可为一高通滤波器(high pass filter),用以依据经传送的编码信号S-ent输出一第一滤波信号S-ft1。在本实施例中,第一滤波器FT1是用以将经传送的编码信号S-ent中的一低频成分信号滤除,以将对应于第一信号S1的第一部分(即脉冲信号成分)滤出,其中低频成分信号包括对应于第二信号S2的第二部分所包括的第一振荡信号及第二振荡信号。第一比较器CMP1依据第一滤波信号S-ft1输出一第三信号S3。详细来说,第一比较器CMP1将第一滤波信号S-ft1与一第一既定电平进行比较,当第一滤波信号S-ft1不小于第一既定电平时,输出的第三信号S3为高电平(high),当第一滤波信号S-ft1小于第一既定电平时,输出的第三信号S3为低电平(low)。

第二解码器2043包括一第二滤波器FT2、一第三滤波器FT3、一第一包络检测器ED1、一第二包络检测器ED2及一第二比较器CMP2。第二滤波器FT2用以依据经传送的编码信号S-ent输出一第二滤波信号S-ft2。第二滤波器FT2可为一带通滤波器,第二滤波器FT2的中心频率可为第一频率。第二滤波器FT2可将经传送的编码信号S-ent中对应于第二信号S2中的第二部分(即频率编码信号)的频率为第一频率的成分滤出。第一包络检测器ED1用以检测第二滤波信号S-ft2的包络(envelope),并依据第二滤波信号S-ft2输出一第一解码信号S-de1(即输出第二滤波信号S-ft2的包络)。第三滤波器FT3用以依据经传送的编码信号S-ent输出一第三滤波信号S-ft3。第三滤波器FT3可为一带通滤波器,第三滤波器FT3的中心频率可为第二频率。第三滤波器FT3可将经传送的编码信号S-ent中对应于第二信号S2中的第二部分(即频率编码信号)的频率为第二频率的成分滤出。第二包络检测器ED2用以检测第三滤波信号S-ft3的包络,并依据第三滤波信号S-ft3输出一第二解码信号S-de2(即输出第三滤波信号S-ft3的包络)。第二比较器CMP2用以依据第一解码信号S-de1及第二解码信号S-de2输出第四信号S4。详细来说,第二比较器CMP2可为一三态比较器,会将第一解码信号S-de1及第二解码信号S-de2相减得到的第三解码信号与一第二既定电平及第三既定电平比较,当第三解码信号不小于第二既定电平时,输出的第四信号为高电平,当第三解码信号不大于第三既定电平时,输出的第四信号为低电平,当第三解码信号小于第二既定电平且大于第三既定电平时,输出的第四信号为一第三态电平(例如共模电平或零)。信号回复单元2045用以依据第三信号S3及第四信号S4产生输出信号S-out。信号回复单元2045可藉由第三信号S3来决定输出信号S-out信号转换的一时间点。信号回复单元2045可包括一乘法电路及一判断电路。乘法电路将第三信号S3与第四信号S4相乘。对于图3A的实施例来说,判断电路藉由第三信号S3及第四信号S4相乘的值来决定输出的输出信号S-out的电平。更详细来说,当第三信号S3及第四信号S4相乘的值大于0,则输出信号S-out进行低电平到高电平的转换;当第三信号S3及第四信号S4相乘的值小于0,则输出信号S-out进行高电平到低电平的转换;当第三信号S3及第四信号S4相乘的值等于0,则输出信号S-out不进行转换(即维持当前电平)。换句话说,在本实施例中,第三信号S3除了决定输出信号S-out中信号边沿的位置(高/低电平转换的时间点),还能和第四信号S4共同决定输出信号S-out的电平为高电平、低电平或维持当前电平。换句话说,第四信号S4还能帮助信号回复单元2045确认第三信号S3是否为真实的原编码信号经传送所产生而发噪声所造成,以降低噪声对解码造成的影响。

在替代的实施例中,对应于输入信号S-in的上升沿与下降沿所产生出的第一信号S1会是不同的。在一个实际的例子中,对应于输入信号S-in的上升沿所产生出的第一信号S1是一个正脉冲,对应于输入信号S-in的下降沿所产生出的第一信号S1是一个负脉冲。从图3B绘示的波形图可看出,输入信号S-in的上升沿会被编码为一个正脉冲信号后接续一个频率为第一频率的频率编码信号,输入信号S-in的下降沿会被编码为一个负脉冲信号后接续一个频率为第二频率的频率编码信号。对于图3B的实施例,第一比较器CMP1将第一滤波信号S-ft1与一第四既定电平及一第五既定电平进行比较,当第一滤波信号S-ft1不小于第四既定电平时,输出的第三信号S3为第一电平(例如高电平),当第一滤波信号S-ft1不大于第五既定电平时,输出的第三信号S3为第二电平(例如低电平),当第一滤波信号S-ft1大于第五既定电平且小于第四既定电平时,输出的第三信号S3为第三电平(例如共模电平或零)。信号回复单元2045的判断电路除了根据第三信号S3及第四信号S4相乘的乘积以外,还根据第三信号S3的值及第四信号S4的值来决定输出的输出信号S-out的电平。更详细来说,当第三信号S3及第四信号S4相乘的乘积大于0且第三信号S3及第四信号S4皆大于0,则输出信号S-out进行低电平到高电平的转换;当第三信号S3及第四信号S4相乘的乘积大于0且第三信号S3及第四信号S4皆小于0,则输出信号S-out进行高电平到低电平的转换;当第三信号S3及第四信号S4相乘的乘积小于或等于0,则输出信号S-out不进行转换(即维持当前电平)。

请参照图4,图4绘示依据本发明又一实施例的隔离器的方块图。图4的实施例中绘示了第一编码器、第二编码器、第一解码器及二解码器的进一步细节。隔离器40包括一输入侧电路402、一输出侧电路404及一信号传递单元406。输入侧电路402包括一第一编码器4021、一第二编码器4023及一信号合成单元4025。输出侧电路404包括一第一解码器4041、一第二解码器4043及一信号回复单元4045。

第一编码器4021包括一信号边沿检测器EdD及一脉冲编码器PE。在本实施例中,当信号边沿检测器EdD检测输入信号S-in的信号边沿产生的第一触发信号Trg1。脉冲编码器PE响应于第一个触发信号Trg1产生的第一信号S1为正脉冲,脉冲编码器PE响应于第二个触发信号Trg1产生的第一信号S1为负脉冲,以此类推。

第二编码器4023包括一振荡器OSC及一频率编码器FE。振荡器OSC输出振荡频率为第三频率的第三振荡信号f3。振荡器OSC受到第一信号S1的触发而开始振荡。频率编码器FE用以接收输入信号S-in,并以第三频率f3编码输入信号S-in做为第二信号S2输出。

信号合成单元4025类似于信号合成单元4025,可用以组合第一信号S1及第二信号S2以产生编码信号S-en。

也就是说,在输入侧电路402中,第一编码器4021根据输入信号S-in的信号边沿产生的第一信号S1会被用做唤醒第二编码器4023的振荡器OSC的信号,而令第二编码器4023可以在第一信号S1产生后随即开始产生第二信号S2。如此一来,可以使得信号合成单元406能够在不用调整第一信号S1与第二信号S2的时序的前提下,简单地将第一信号S1及第二信号S2合成。

图5绘示的是隔离器40的信号波形示意图。从图5中可看出输入信号S-in与编码信号S-en的关系,输入信号S-in的上升沿会被编码为一个正脉冲信号后接续一个频率为第三频率f3的频率编码信号,输入信号S-in的下降沿会被编码为一个负脉冲信号后接续一个频率为第三频率f3的频率编码信号。换句话说,输出侧电路404可藉由辨识脉冲信号为正或负来确定所收到是代表上升沿的信号还是代表下降沿的信号。

回到图4,第一解码器4041包括一第一滤波器FT1及一第一比较器CMP1。在本实施例中,第一滤波器FT1将经传送的编码信号S-ent中的一低频成分信号滤除,以将对应于第一信号S1的第一部分(即脉冲信号成分)滤出,其中低频成分信号包括对应于第二信号S2的第二部分所包括的振荡信号。第一比较器CMP1将第一滤波信号S-ft1与一第六既定电平及一第七既定电平进行比较,当第一滤波信号S-ft1不小于第六既定电平时,输出的第三信号S3为第一电平(例如高电平),当第一滤波信号S-ft1不大于第七既定电平时,输出的第三信号S3为第二电平(例如低电平),当第一滤波信号S-ft1大于第七既定电平且小于第六既定电平时,输出的第三信号S3为第三电平(例如共模电平或零)。

第二解码器4043包括一滤波器FT、一包络检测器ED及一比较器CMP。滤波器FT的中心频率可为第三频率。滤波器FT用以将经传送的编码信号S-ent中对应于第二信号S2的第二部分(频率编码成分)滤出,以输出一第四滤波信号S-ft4。包络检测器ED检测第四滤波信号S-ft4的包络,以输出第四解码信号S-de4。比较器CMP将第四解码信号S-de4与一第八既定电平比较,当第四解码信号S-de4不小于第八既定电平时,输出的第四信号S4为高电平,当第四解码信号S-de4小于第八既定电平时,输出的第四信号S4为低电平。信号回复单元4045依据第三信号S3及第四信号S4产生输出信号S-out。举例来说,信号回复单元2045可藉由第三信号S3来决定输出信号S-out信号转换的一时间点,而且输出信号S-out在该时间点的一转换类型则藉由将第三信号S3及第四信号S4相乘的值来决定。更详细来说,当第三信号S3及第四信号S4相乘的值大于0,则输出信号S-out进行低电平到高电平的转换;当第三信号S3及第四信号S4相乘的值小于0,则输出信号S-out进行高电平到低电平的转换;当第三信号S3及第四信号S4相乘的值等于0,则输出信号S-out不进行转换(即维持当前电平)。

在本实施例中,第三信号S3是用以决定输出信号S-out中信号边沿的位置,并和第四信号S4共同决定所定位的信号边沿是上升沿、下降沿或是维持当前电平。也就是说,第四信号S4可帮助信号回复单元4045确认藉由第三信号S3是否为真实的编码信号传送所产生,而非噪声所造成。

隔离器40的详细的信号波形可参考图5。值得一提的是,无论是在第3A、3B或5图所示的例子中,在传输过程中产生的噪声N在输出侧电路204、404会因输出信号S-out是由第三信号S3与第四信号S4所共同决定而无法对输出信号S-out的波形产生影响。

在上述的实施例中,信号传递单元是以感应线圈为例。然而,在其他实施例中,信号传递单元也可以是光耦合器、电荷耦合器等传递信号的手段,本发明不加以限定。

此外,本发明亦提供对应于上述隔离器的信号产生方法。如图6所示,信号产生方法包括S601~S605。

S601中,藉由隔离器的一输入侧电路的一第一编码器依据一输入信号产生一第一信号。

S603中,藉由隔离器的一第二编码器依据输入信号与第一信号产生一第二信号。

S605中,藉由隔离器的一信号合成单元依据第一信号与第二信号分别产生一编码信号,其中第一信号与第二信号分别对应于编码信号的一第一部分与一第二部分,第一部分为一脉冲信号,第二部分为一非振幅编码信号。

关于信号产生方法的细节可参考前文的实施例,在此不加赘述。

藉由本发明提供的隔离器藉由电路设计简单地将两种不同类型的编码整合,使得隔离器同时具备电路复杂度低、信号边沿定位准确与高抗噪能力,有助于提升隔离器的信号可靠度。

综上所述,虽然本发明已以实施例公开如上,然其并非用以限定本发明。本发明所属领域技术人员在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当视所附权利要求书界定范围为准。

- 提升共模瞬变抗扰度的隔离器及信号产生方法

- 采用用于共模瞬态抗扰度的陷波滤波器的数字隔离器的接收器架构