一种用于封装后调整的熔丝读写电路

文献发布时间:2023-06-19 11:21:00

技术领域

本发明涉及一种用于封装后调整的熔丝读写电路,即一种应用于参数后调整的熔丝读写电路,属于集成电路设计领域。

背景技术

熔丝电路的作用是将容易产生工艺离散或者性能参数指标要求较高的器件采用封装后调整的方式提升参数性能和产品良率。在集成电路中,普通结构的电路参数通常具有上下限,可以通过测试筛除参数离散较大,不满足指标需求的器件,通常由于器件参数指标要求高或者工艺离散较大、甚至受封装应力影响的情况下,器件参数指标极大依赖于芯片加工和封转条件,因此需要封装后调整测试来提升参数值指标从而提高产品良率。

发明内容

本发明的技术解决问题为:克服现有技术不足,提出一种用于封装后调整的熔丝读写电路,即一种新的主要用于多晶硅熔丝编程和编程后熔丝数据位读出的高性能熔丝读写电路,可以克服工艺容差实现满足熔丝数据读写时序性能参数指标要求。

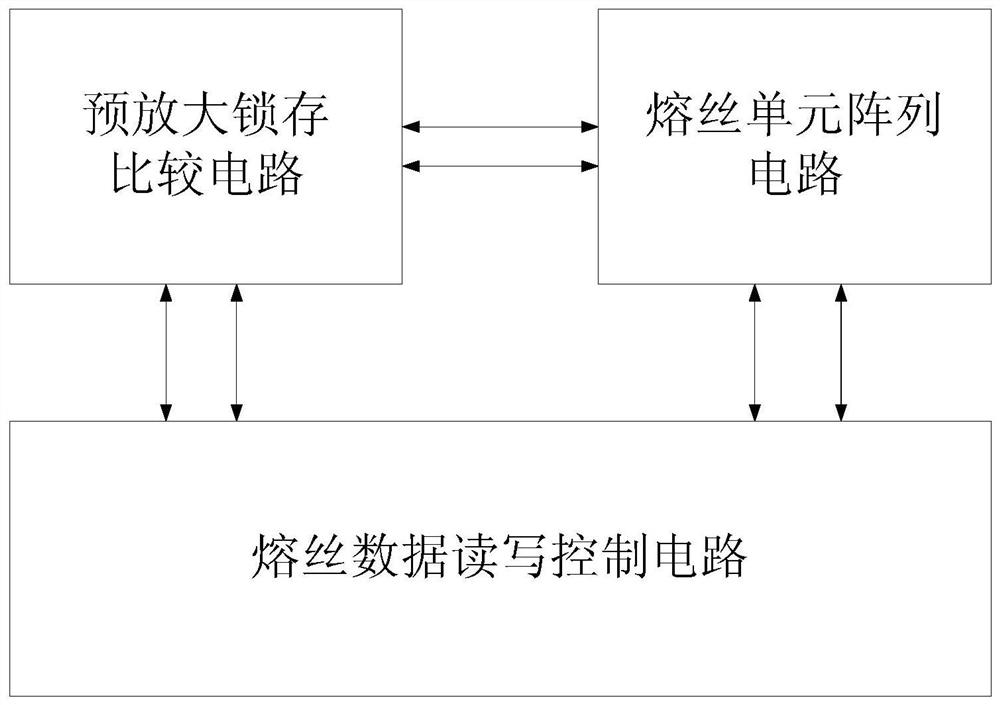

本发明的技术解决方案为:一种用于封装后调整的熔丝读写电路,包括预放大锁存比较电路、熔丝位读写控制电路和熔丝单元阵列电路;其中熔丝单元阵列电路由若干熔丝电阻并联组成;熔丝位读写控制电路对熔丝单元阵列电路进行熔断编程操作,预放大锁存比较电路对编程后的熔丝单元阵列电路进行数据读取,读取结果输出到熔丝位读写控制电路,熔丝位读写控制电路根据控制逻辑将接收到熔丝单元阵列电路数据输出至外部电路。

预放大锁存比较电路包括第一PMOS管、第二PMOS管、第三PMOS管、第四PMOS管、第五PMOS管、第六PMOS管、第七PMOS管、第一NMOS管、第二NMOS管;

第一PMOS管源级接电源电压,第一PMOS管栅级连接第二PMOS管集电极、第三PMOS管栅极、第四PMOS管源级和第七PMOS管集电极;第一PMOS管集电极连接第二PMOS管栅极、第三PMOS管源级、第四PMOS管栅极和第六PMOS管集电极,第一PMOS管集电极为预放大锁存比较电路的输出端;第二PMOS管源级接电源电压;第三PMOS管集电级连接第四PMOS管集电级、第一NMOS管集电级和第五PMOS管集电极;第一NMOS管源级连接第二NMOS管集电极;第二NMOS管源极连接地;第五PMOS管源极、第六PMOS管源极、第七PMOS管源极接熔丝单元阵列电路正端和电源电压。

熔丝位读写控制电路包括或非门、与非门、第三NMOS管、电容、RS触发器;

第一NMOS管栅极连接RS触发器的输出端Q;

第二NMOS管栅极、第五PMOS管栅极、第六PMOS管栅极、第七PMOS管栅极连接与非门输出端X;

或非门输入端分别接收外部写入信号D与外部使能信号ENN,或非门输出端连接第三NMOS管栅极;与非门输入端分别接收外部读取信号B和外部使能信号ENN,与非门输出端连接RS触发器的输入S端;第三NMOS管源极接地,电容正极连接与非门输出端X,第三NMOS管集电极连接熔丝单元阵列电路负端、RS触发器输入R端和预放大锁存比较电路输出端;电容负极接地;RS触发器输出端分别为输出端Q和输出端

使能信号ENN为低电平时,所述用于封装后调整的熔丝读写电路处于写入状态,此时读取信号B保持为高电平:若写入信号D为高电平时,第三NMOS管关断,熔丝单元阵列电路状态不变,写入数据为1;若写入信号D为低电平时,第三NMOS管打开,熔丝单元阵列电路熔断,写入数据为0;

使能信号ENN为高电平时,所述用于封装后调整的熔丝读写电路处于读数状态,此时读取信号B为低电平,读取熔丝单元阵列电路数据。

本发明相对现有技术的优点在于:

(1)本发明提供用于封装后调整的熔丝读写电路,采用门控使能方式实现熔丝单元阵列电路数据编程写入,写入电压低,常规电源电压即可。相对于目前常规熔丝烧调电路烧调电压的高压要求,具有写入模式功耗小的特点。

(2)本发明的预放大锁存比较电路用于读出熔丝单元阵列电路写入数据,其结构引入了自偏置灵敏放大器,既实现了熔丝单元阵列电路写入数据的有效读出,又同时保证数据读出后熔丝单元阵列电路不再有电流流过,从而保护熔丝结构不受长期电流冲击,满足了可靠性需求。

(3)本发明的预放大锁存比较电路利用电路结构延时作用下的窄脉冲工作区间读出数据,数据读出操作完成后自偏置灵敏放大器停止工作,从而使该部分电路静态功耗几乎为零,降低了器件整体功耗,满足了低功耗需求。

(4)本发明可以进行电路在线测试后调整,使得由于芯片工艺离散,封装引入误差等因素导致电参数指标不满足,电路生产良率低的问题。大大提高封装后成测成品率,克服了常规电路设计中易出现的基准电压,基准电流漂移离散的问题以及高性能参数指标不能很好满足造成器件良率偏低的实际问题,提高了电路生产良率和参数性能指标,提高了生产良率。

(5)本发明电路满足以下读写参数指标:读出时间仅需μs级,熔丝编程电压常规电源电压,写入电流10mA-30mA,静态功耗几乎为零。

附图说明

图1为本发明用于封装后调整的熔丝读写电路结构图。

图2为烧调电阻熔通条件下本发明读写数据时序图。

图3为烧调电阻未熔通条件下本发明读出数据时序图。

图4为本发明的结构框图。

具体实施方式

下面结合附图和具体实施方式对本发明进行详细说明。

本发明为一种多晶熔丝逻辑读写电路,线路连接如图1、4所示,为本发明的总体电路图,即本发明的基本形式,它由预放大锁存比较电路、熔丝位读写控制电路和熔丝单元阵列电路三部分组成。其中熔丝单元阵列电路由若干熔丝电阻并联组成;熔丝位读写控制电路对熔丝单元阵列电路进行熔断编程操作,预放大锁存比较电路对编程后的熔丝单元阵列电路进行数据读取,读取结果输出到熔丝位读写控制电路,熔丝位读写控制电路根据控制逻辑将接收到熔丝单元阵列电路数据输出至外部电路。

预放大锁存比较电路包括第一PMOS管101、第二PMOS管102、第三PMOS管103、第四PMOS管104、第五PMOS管107、第六PMOS管108、第七PMOS管109、第一NMOS管105、第二NMOS管106;第一PMOS管101源级接电源电压,第一PMOS管101栅级连接第二PMOS管102集电极、第三PMOS管103栅极、第四PMOS管104源级和第七PMOS管109集电极;第一PMOS管101集电极连接第二PMOS管102栅极、第三PMOS管103源级、第四PMOS管104栅极和第六PMOS管108集电极,第一PMOS管101集电极为预放大锁存比较电路的输出端;第二PMOS管102源级接电源电压;第三PMOS管103集电级连接第四PMOS管104集电级、第一NMOS管105集电级和第五PMOS管107集电极;第一NMOS管105源级连接第二NMOS管106集电极;第二NMOS管106源极连接地;第五PMOS管107源极、第六PMOS管108源极、第七PMOS管109源极接熔丝单元阵列电路正端和电源电压。

熔丝位读写控制电路包括或非门110、与非门111、第三NMOS管112、电容114、RS触发器115;第一NMOS管105栅极连接RS触发器115的输出端Q;第二NMOS管106栅极、第五PMOS管107栅极、第六PMOS管108栅极、第七PMOS管109栅极连接与非门111输出端X1;或非门110输入端分别接收外部写入信号D与外部使能信号ENN,或非门110输出端连接第三NMOS管112栅极;与非门111输入端分别接收外部读取信号B和外部使能信号ENN,与非门111输出端连接RS触发器115的输入S端;第三NMOS管112源极接地,电容114正极连接与非门111输出端X1,第三NMOS管112集电极连接熔丝单元阵列电路负端、RS触发器115输入R端和预放大锁存比较电路输出端;电容114负极接地;RS触发器115输出端分别为输出端Q和输出端

图2为熔丝单元阵列电路中的熔丝电阻位熔断条件下电路读写数据时序图。ENN为电路使能信号,ENN信号为低电平时,用于封装后调整的熔丝读写电路处于写入状态,此时读取信号B保持为高电平,D为写入信号,D信号为低电平时,开关管第三NMOS管112打开,熔丝单元阵列电路中的熔丝电阻位熔断形成断路,写入数据0。ENN信号为高电平时,用于封装后调整的熔丝读写电路处于读取状态,端口X1信号跳变为低电平,第五PMOS管107、第六PMOS管108和第七PMOS管109打开,对节点a、b和c进行预充电。读取信号B为低电平时读取熔丝单元阵列电路数据,由于RS触发器115的延迟作用,端口Q信号与端口X1信号同时输出高脉冲,预放大锁存比较电路工作,由于第一PMOS管101和第三PMOS管103尺寸大于第二PMOS管102和第四PMOS管104尺寸的自偏置结构设计,节点a电压迅速拉至低电平,输出信号Q为低电平,进而预放大锁存比较电路停止工作,节点a重新充电至高电平,RS触发器115处于锁存状态,输出Q保持前一状态,输出为低电平,实现了数据0的有效读写。其中节点a为第一PMOS管101集电极、第二PMOS管102栅极、第三PMOS管103源级、第四PMOS管104栅极和第六PMOS管108集电极的交点,节点b为第一PMOS管101栅级、第二PMOS管102集电极、第三PMOS管103栅极、第四PMOS管104源级和第七PMOS管109集电极交点,节点c为第三PMOS管103集电级、第四PMOS管104集电级、第一NMOS管105集电级和第五PMOS管107集电极交点。

图3为熔丝单元阵列电路中的熔丝电阻位未熔断条件下电路读写数据时序图。ENN为电路使能信号,ENN信号为低电平时,用于封装后调整的熔丝读写电路处于写入状态,此时读取信号B保持为高电平,D为写入信号,D为高电平时,开关管第三NMOS管112关断,熔丝单元阵列电路中的熔丝电阻位保持状态不变,写入数据1;ENN信号为高电平时,用于封装后调整的熔丝读写电路处于读取状态,读取信号B为低电平时,读取熔丝单元阵列电路数据。由于此时熔丝单元阵列电路中的熔丝电阻的上拉作用,RS触发器115的R输入端始终为高电平,输出端Q信号始终为高电平,实现了数据1的有效读写。

常规的熔丝读写电路采用电平比较读取数据,读取数据期间没有时钟控制,读取时间较长,在多晶硅电阻处产生长时间电流,该电流容易造成器件功耗增加,不利于电池供电的低功耗应用场景,且该熔断多晶硅长时间通电可能导致熔断不充分的或者熔断形态不好的多晶硅熔丝状态发生改变,从而影响编程数据。采用自偏置灵敏放大结构后,数据读取发生在很短的脉冲时刻,有效的降低了器件功耗,提升了器件可靠性。

本发明说明书中未作详细描述的内容属本领域专业技术人员的公知技术。

- 一种用于封装后调整的熔丝读写电路

- 用于封装后DRAM修复的耐熔熔丝电路