一种并行数据结构构建及其搜索的方法、系统

文献发布时间:2023-06-19 11:26:00

技术领域

本发明涉及数据结构以及存储技术领域,尤其涉及一种并行数据结构构建及其搜索的方法、系统。

背景技术

图形处理器(GPU)它起源于图形渲染,现在已出现高级语言支持GPU上的便捷编程。NVIDIA为其GPU提供了Compute Unified Device Architecture(CUDA)编程模型,拥有类C语言的编程接口。结合CUDA的GPU提供了强大的计算能力和非常高的存储带宽,适合于高度并行、计算密集的应用。尽管计算能力强大,但NVIDIA GPU的花销较低,而且普遍存在于PC或工作站等不太昂贵的机器中。

目前,使用CUDA在GPU上建立一个树型数据结构方面的工作较少。Zhou Kun等在GPU上构建了一个针对多维数据的KD-tree,他们将树的节点信息等存储在GPU的全局存储上,并使用该数据结构加速图像渲染中的光线追踪和K个最近邻搜索,但存在效率不高的问题。且现有实验证明该基于CUDA的八分树在树型结构构建全局存储上存在延迟较高的问题。

现有工作集中于在GPU的全局存储上构建一个单一的树型数据结构。这样的策略导致大量效率较低的无法优化的对全局存储的访问,而且由于线程竞争着将数据点插入到树中,致使CUDA程序的线程并行度较低,且其性能受到很大影响。

发明内容

本发明提供的一种并行数据结构构建及其搜索的方法、系统,利用GPU高速但有限的片上存储实现四分树的构建和搜索,极大地提升了存储访问的效率。同时,树群以每个CUDA线程块为单位实现一棵较小的四分树,线程并行度相对一个单一的四分树要高许多倍,从而提升了建树的效率。

第一方面,本发明实施例提供的一种并行数据结构构建及其搜索的方法,所述方法包括:

获取待组织数据并进行GPU全局存储模式;

根据所述待组织数据的属性确定GPU存储区域对应的区域格;

将所述待组织数据构建第一四分树群,且将所述待组织数据对应线程的数据点处理至对应的区域格;

根据所述数据点将所有待组织数据部署存储至所述区域格中。

在一种可能的设计中,所述方法,包括:根据所述待组织数据的分布范围和分布密度预估划分第一区域格;

所述根据所述待组织数据的属性确定GPU存储区域对应的区域格,包括:

若所述第一区域格中包含的数据点个数大于预设阈值,则将所述第一区域格划分为第一子区域格,并将所述第一子区域格作为所述待组织数据在GPU存储区域对应的区域格;其中所述第一子区域格包含至少一个数据点。

在一种可能的设计中,所述根据所述待组织数据的属性确定GPU存储区域对应的区域格,还包括:

若所述第一区域格中包含的数据点个数不大于预设阈值,则将所述第一区域格作为所述待组织数据在GPU存储区域对应的区域格。

在一种可能的设计中,将所述待组织数据对应线程的数据点处理至对应的区域格,包括:

将所述待组织数据对应线程的数据点组织到所述第一四分树群对应的区域格。

在一种可能的设计中,将所述待组织数据对应线程的数据点处理至对应的区域格,包括:

若所述第一四分树群内对应插入的叶节点已被其他数据点占用,则当前线程创建第一四分子树,其中所述第一四分子树具有四个空叶节点;

根据所述第一四分子树,将当前线程已有节点和其对应数据点插入所述第一四分子树的所述叶节点对应区域格。

在一种可能的设计中,所述方法还包括:

搜索所述GPU存储区域已有第二四分树群,为所述第一四分树群对应区域格内的每个数据点获取对应的临近数据点。

在一种可能的设计中,为所述第一四分树群对应区域格内的每个数据点获取对应的临近数据点,包括:

根据所述第一四分树群内对应区域格中线程的根数据点以及当前访问对应树深度,检测是否满足预设条件;

若满足所述预设条件,则根据所述第一四分树群内对应区域格中线程的根数据点以及当前访问对应树深度获取所述第一四分树群对应区域格内的每个数据点对应的临近数据点;

或者若不满足所述预设条件,则根据当前访问数据点对应其兄弟节点来确定所述第一四分树群对应区域格内的每个数据点对应的临近数据点。

在一种可能的设计中,在根据所述数据点将所有待组织数据部署存储至所述区域格中之后,还包括:

根据所述第一四分树群对应区域格内的数据点及其对应的临近数据点,获得目标数据。

在一种可能的设计中,每个所述线程对应一个四分树,且具有对应的数据点。

第二方面,本发明实施例提供的一种并行数据结构构建及其搜索的系统,包括存储器和处理器,存储器中存储有所述处理器的可执行指令;其中,所述处理器配置为经由执行所述可执行指令来执行第一方面任一项所述并行数据结构构建及其搜索的方法。

本发明提供的一种并行数据结构构建及其搜索的方法、系统,利用GPU高速但有限的片上存储实现四分树的构建和搜索,极大地提升了存储访问的效率。同时,树群以每个CUDA线程块为单位实现一棵较小的四分树,线程并行度相对一个单一的四分树要高许多倍,从而提升了建树的效率。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

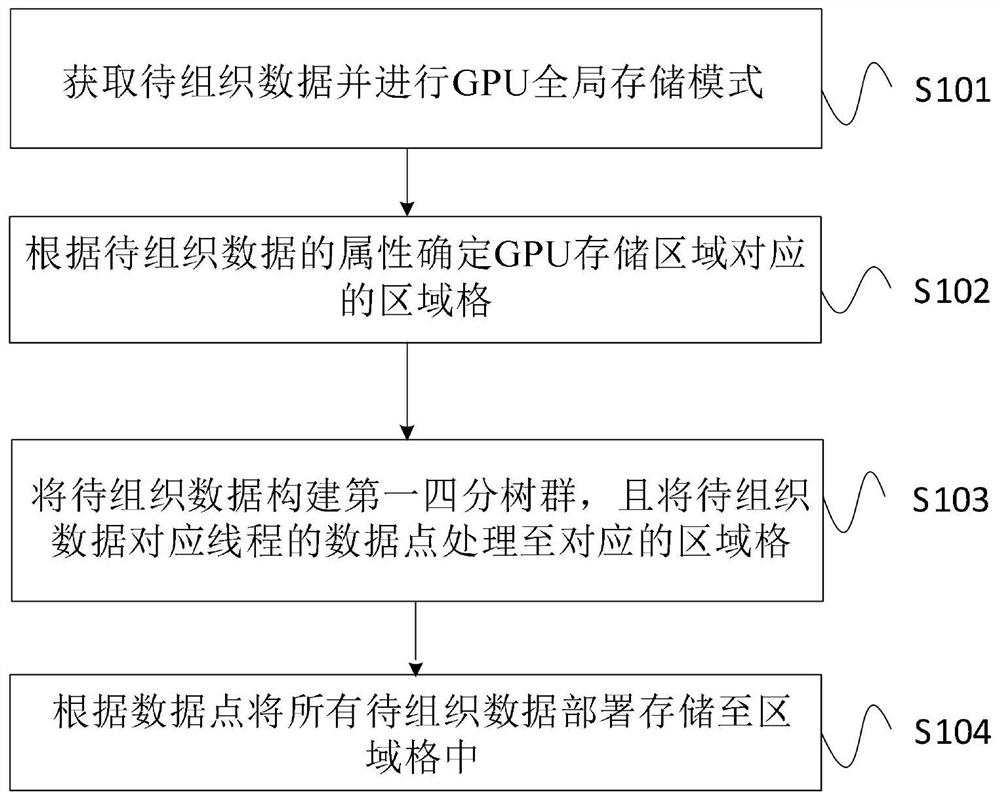

图1为本发明实施例提供的并行数据结构构建及其搜索的方法流程示意图;

图2为本实施例利用GPU片上树群实现二维数据近邻搜索的结构示意图;

图3为本发明实施例主机端代码的顺序执行和设备端代码的并行执行的示意图;

图4为本实施例区域格的二维层次递归划分的示意图;

图5为本实施例区域格四分树形式的数据点组织的示意图;

图6为本发明实施例提供的并行数据结构构建及其搜索的系统结构示意图。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”、“第三”、“第四”等(如果存在)是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,以便这里描述的本发明的实施例例如能够以除了在这里图示或描述的那些以外的顺序实施。此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖不排他的包含,例如,包含了一系列步骤或单元的过程、方法、系统、产品或设备不必限于清楚地列出的那些步骤或单元,而是可包括没有清楚地列出的或对于这些过程、方法、产品或设备固有的其它步骤或单元。

四分树是一种用于组织二维空间数据的多层次树状数据结构,在树内每个非叶节点最多有四个子节点。它将一个正方形区域规则地划分为4个子区域,每一个子区域再分为4个子区域,如此逐次划分,直至所有子区域最多只包含一个数据点为止。四分树的优点是空间关系隐含在数据模型之中,检索和处理速度较快。

GPU+CUDA架构被应用于加速各个科学计算领域中的计算密集型处理。在硬件层次,支持CUDA的GPU是一些单指令多数据流(SIMD)流多处理器(stream multiprocessor)的集合,每个流多处理器有32个流处理器(stream processor)。比如:NVIDIA Tesla C2070处理器有14个流多处理器,共448个流处理器。每个流多处理器有一个容量有限的快速片上共享存储,可被一个流多处理器内的所有流处理器共享。每个流处理器拥有一定数量的32位寄存器。流多处理器之间通过延迟较高的片外全局/设备存储进行通信。全局存储可被主机读写,而且在同一程序的不同核函数之间是一致的。共享存储显式地由程序员管理。

在软件层次,CUDA模型是大量并行执行线程的集合,CUDA程序以线程并行的模式执行。由主机控制调度、GPU实际执行的基本任务单元称为核函数,其形式和功能类似C语言中定义的函数。计算被组织成由一些线程块构成的线程网格(参见图3,图3为本发明实施例主机端代码的顺序执行和设备端代码的并行执行的示意图)。在指令层次,同一个线程块内的32个连续线程构成一个最小执行单元,称为线程warp。一个线程块是一批次同一时刻在同一流多处理器上SIMD并行运行的线程warp的集合。每个流多处理器同一时刻并发执行一个或多个线程块。对于任一线程,它的索引被用于确定其应该处理的数据。同一个线程块内的线程通过片上共享存储进行通信。

下面以具体地实施例对本发明的技术方案以及本申请的技术方案如何解决上述技术问题进行详细说明。下面这几个具体的实施例可以相互结合,对于相同或相似的概念或过程可能在某些实施例中不再赘述。下面将结合附图,对本发明的实施例进行描述。

本发明实施例提供一种并行数据结构构建及其搜索的方法、系统,具体提供一种基于NVIDIA的GPU+CUDA计算架构的高效四分树群和基于此数据结构的并行搜索近邻的方法,能够具有更有效、快速及时的性能为各种应用提供近邻搜索。

下面结合附图和算法实现伪码详细描述本发明中的数据结构、该数据结构的构建和使用该数据结构并行搜索数据点的近邻数据等过程。

图1为本发明实施例提供的并行数据结构构建及其搜索的方法流程示意图,如图1所示,本实施例中的并行数据结构构建及其搜索的方法可以包括:

S101、获取待组织数据并进行GPU全局存储模式。其中全局存储模式可以包括构建一种可驻留于GPU高速片上存储的数据结构—四分树群,使用其组织各种应用中的数据点,不仅在运行计算中作为加速数据结构,提高处理效率,还可以为全部数据点查找近邻数据提升并行性能。本实施例中将待组织数据由内存复制/拷贝到GPU全局存储。

本发明采用四分树群,即一个包含了大量规模较小的CUDA四分树的森林。将整个数据点部署区域分为大量正方形区域格,使得每个区域格包含不多于预设阈值数目的数据点,例如实验测试中预设阈值为64,即每个区域格最多包含64个数据点。每个区域格中的数据点用一个CUDA四分树组织起来。参见图4、图5,图4为本实施例区域格的二维层次递归划分的示意图;图5为本实施例区域格四分树形式的数据点组织的示意图。如图4所示,一个区域格首先划分为四个更小、均等的区域小格,然后每个区域小格再迭代划分,直到其包含不多于一个的数据点。最终,图4区域格内的所有数据点组织到了图5所示的CUDA四分树中,其中空间相近的数据点在树中互为兄弟节点。

与一棵大树相比,树群可最大化建树时的CUDA线程并行度;每个CUDA四分树较小,可完全驻留在GPU快速片上存储中,避免了访问全局存储招致的高延迟,能带来相当可观的性能提升。

本发明充分利用GPU高效的片上存储,构建四分树群和搜索四分树群的工作均在该存储中进行,构建好的四分树由线程协同以访存最优的存储融合的方式写入全局存储;在搜索四分树时,以相同的方式将四分树由全局存储读入片上存储,然后再进行搜索。

S102、根据所述待组织数据的属性确定GPU存储区域对应的区域格。其中,属性可以包括数据分布的范围和对分布密度的预估等。

具体地,依据待组织数据的数据分布的范围和对分布密度的经验预估将数据分布区域划分成区域格。本实施例中每个线程持有一个数据点,根据其坐标将其划归到特定的区域格中。

在一些实施例中,若所述第一区域格中包含的数据点个数大于预设阈值,则将所述第一区域格划分为第一子区域格,并将所述第一子区域格作为所述待组织数据在GPU存储区域对应的区域格;其中所述第一子区域格包含至少一个数据点。

在另一些实施例中,若所述第一区域格中包含的数据点个数不大于预设阈值,则将所述第一区域格作为所述待组织数据在GPU存储区域对应的区域格。

具体地,本发明将整个数据点部署区域等分为大量正方形区域格,使得每个区域格包含不多于预设阈值数目的数据点(例如预设阈值为64,即每个区域格最多包含64个数据点)。如果每个区域格包含的数据点数大于设定的阈值,则每个区域格分裂为四个更小的区域格;反之,停止数据点的划归。即若根据确定对应的第一区域格中包含的数据点个数大于预设阈值,则将该第一区域格继续划分为第一子区域格,并将该第一子区域格作为所述待组织数据在GPU存储区域对应的区域格;其中所述第一子区域格包含至少一个数据点;即若数据点个数大于预设阈值,则继续划分直至最后的第一子区域格包含不多于一个的数据点。或者,若该第一区域格中包含的数据点个数(例如为30)不大于预设阈值,则将该第一区域格作为所述待组织数据在GPU存储区域对应的区域格,即不需要继续进行区域格的划分。

S103、将所述待组织数据构建第一四分树群,且将所述待组织数据对应线程的数据点处理至对应的区域格。

本发明在生成四分树群时,每个CUDA线程块负责一个区域格,构建一棵CUDA-quadtree。其中,每个线程持有一个数据点。为了便利在CUDA-quadtree中搜索近邻,每个区域子格的中心点和边长组合构成“虚节点”以代表该区域,即CUDA-quadtree中的非叶节点。比如:以区域格的中心点和区域格边长组合四分树的“根虚节点”,代表该区域格覆盖的区域。假设一个区域格内最多有n个数据点,则生成的四分树最大可能占用空间为n*4+1,据此在共享存储上分配一固定大小的数组,以保存四分树信息。该信息数组逆序填充,即当有新数据点插入到CUDA-quadtree时,在数组已保存的数据点前一空白处存储新数据点信息。

本实施例中,将所述待组织数据构建第一四分树群,对应该第一四分树群每个CUDA线程块负责一个区域格,构建一棵CUDA-quadtree。其中,每个线程持有一个数据点。

在一些实施例中,将所述待组织数据对应线程的数据点组织到所述第一四分树群对应的区域格。

在另一些实施例中,若所述第一四分树群内对应插入的叶节点已被其他数据点占用,则当前线程创建第一四分子树,其中所述第一四分子树具有四个空叶节点;根据所述第一四分子树,将当前线程已有节点和其对应数据点插入所述第一四分子树的所述叶节点对应区域格。

具体地,如表1伪码所示,线程插入数据点是一个反复尝试的过程,其间线程竞争获取一次插入机会。首先,线程0初始化“根虚节点”并创建四个空叶节点。然后,每个线程根据持有数据点在区域格中的位置寻找合适的叶节点执行插入操作。当这样的位置找到后,一个竞争胜出线程对其添加唯一写入权限锁,独占该位置,插入持有的数据点(将该数据点写入信息数组),释放该位置,退出插入操作。

表1 GPU片上数据点插入的伪码示例

如果一个线程竞争失败,没有锁住合适的叶节点,则该线程等待下一次机会重新尝试前述插入操作。然而,在第二轮中,一个线程找到并锁住的叶节点位置已经被其他插入的数据点占用。于是,该线程创建一个带有四个空叶节点的子树,插入到该位置,并将原有节点和自己持有的数据点插入到该子树的叶节点中,释放该位置,退出插入操作。其余线程继续如表1所示继续尝试,直到其持有的数据点插入到CUDA-quadtree的一个叶节点中。最后,线程块内线程协同一次性以访存效率最优的数据融合方式将四分树信息数组写入全局存储。

在一些实施例中,本发明方法还包括:搜索所述GPU存储区域已有第二四分树群,为所述第一四分树群对应区域格内的每个数据点获取对应的临近数据点。

具体地,根据所述第一四分树群内对应区域格中线程的根数据点以及当前访问对应树深度,检测是否满足预设条件;若满足所述预设条件,则根据所述第一四分树群内对应区域格中线程的根数据点以及当前访问对应树深度获取所述第一四分树群对应区域格内的每个数据点对应的临近数据点;或者若不满足所述预设条件,则根据当前访问数据点对应其兄弟节点来确定所述第一四分树群对应区域格内的每个数据点对应的临近数据点,其中所述兄弟节点存储于所述第二四分树群中。

本实施例中四分树群以空间相近性为尺度把数据点组织起来,在搜索中能够以较小的计算开销迅速确定每个数据点周围的邻居数据点。根据空间距离,每个CUDA线程块负责的区域格内所有数据点的一定范围内的临近区域可直接确定,即该区域格及其若干邻居区域格。之后,CUDA线程块逐一搜索这些区域格对应的CUDA四分树,并发为该区域格内的所有数据点查找它们的临近数据点。在CUDA四分树内的下坠查找越深,则需要搜索的范围越小。当搜索一个区域格时,线程块内线程首先协同一次性以访存效率最优的数据融合方式将对应的CUDA四分树信息数组从全局存储读入GPU共享存储,然后在高速的共享存储中进行树的搜索。

表2伪码演示了一CUDA线程块内的一个线程warp如何采用深度优先方式对一个四分树进行搜索,并发地为一个线程warp内线程持有的所有数据点查找其临近数据点。该搜索维护两个踪迹信息,分别是从根节点到当前访问节点的树深度和不同深度访问节点在其兄弟节点中次序的信息栈。待访问CUDA四分树被载入共享存储后,该warp内的所有线程沿同一路径自根节点开始下坠搜索。当搜索到的位置为树内部的一个非叶节点,即“虚节点”时,warp内线程检测其持有数据点的临近范围否与该“虚节点”覆盖区域重叠;(即为预设条件)如果有任一检测符合要求,则warp继续下坠搜索该节点的子树,反之则放弃该节点及其子树,搜索其下一个兄弟节点(即对应于第二四分树)。当搜索到的位置为被一数据点占用的叶节点时,warp内线程同时计算其持有数据点与该数据点是否为近邻,然后决定是否依据特定应用做进一步的计算分析。当搜索到的叶节点为空时,warp继续访问其下一个兄弟节点。

表2 GPU片上搜索四分树的伪码示例

本发明不同与以往研究中的一棵驻留在全局存储的树,可驻留GPU高速片上存储的CUDA四分树提供了非常高效的数据访问,这对树内搜索很重要。同时,以一个线程warp为单位避免了损害CUDA程序性能的线程分歧。

参见图2,图2为本实施例利用GPU片上树群实现二维数据近邻搜索的结构示意图,如图2所示,与以往已在GPU上实现的树型数据结构不同,本发明利用GPU高速但有限的片上存储实现四分树的构建和搜索(即构建和搜索并行处理),极大地提升了存储访问的效率。同时,树群以每个CUDA线程块为单位实现一棵较小的四分树,线程并行度相对一个单一的四分树要高许多倍,从而提升了建树的效率。

S104、根据所述数据点将所有待组织数据部署存储至所述区域格中。

本发明所构建的数据结构为由许多四分树组成的树群,每个线程块负责一个四分树的构建和搜索,以便保证数据结构能够载入有限的片上存储和保证CUDA线程并行度尽可能大。根据所述数据点将所有待组织数据部署存储至所述区域格中。每个线程负责一个数据点,在四分树的构建过程中将该数据点插入到四分树中,在近邻搜索过程中为一个数据点搜索其周围的邻居。还可以为数据点搜索近邻时逐一将四分树以访存最优的方式载入片上存储,在高效的片上存储中完成查找工作。

本发明利用GPU高速但有限的片上存储实现四分树的构建和搜索,极大地提升了存储访问的效率。同时,树群以每个CUDA线程块为单位实现一棵较小的四分树,线程并行度相对一个单一的四分树要高许多倍,从而提升了建树的效率。该基于四分树群的近邻搜索算法性能优越,在图像处理和计算机仿真等领域中具有重要的应用价值。

在一些实施例中,在根据所述数据点将所有待组织数据部署存储至所述区域格中之后,还包括:

根据所述第一四分树群对应区域格内的数据点及其对应的临近数据点,获得目标数据。其中,目标数据可以包括依据特定应用。本实施例采用数据点及其对应临近数据点,可以依据特定应用进行后续的计算和分析。

在一些实施例中,每个所述线程对应一个四分树,且具有对应的数据点。本发明在生成四分树群时,每个CUDA线程块负责一个区域格,构建一棵CUDA-quadtree。

最终我们采用实验验证来证明本发明利用GPU高速但有限的片上存储实现四分树的构建和搜索,极大地提升了存储访问的效率。同时,树群以每个CUDA线程块为单位实现一棵较小的四分树,线程并行度相对一个单一的四分树要高许多倍,从而提升了建树的效率。

我们用CUDA编程实现了本发明所描述的算法,并且用实验测试验证了该并行近邻搜索方法的性能。实验使用一台HP Z800工作站,CPU是主频为2.93GHz的Intel Xeon X5647四核处理器,8GB的主机内存。所用GPU为NVIDIA Tesla C2070,它是专用于通用计算的GPU,有448个主频为1.15GHz的流处理器和6GB的全局存储。操作系统为Red Hat EnterpriseLinux WS 6.064位,安装有NVIDIA 270.41.19版本GPU驱动和CUDA 4.0工具包和软件开发包。

表3、4为本方法与Martin等人提出和实现的基于CUDA的八分树在相同条件下的实验测试,分别为两个数据结构的构建阶段和搜索阶段。可以看出,本发明全面好于单个的一棵树,尤其在树的构建阶段有两个数量级的性能优势。

表3树构建的比较

表4在树内搜索的比较

图6为本发明实施例提供的并行数据结构构建及其搜索的系统结构示意图,如图6所示,本实施例的系统可以包括:处理器21和存储器22。

存储器22,用于存储计算机程序(如实现上述并行数据结构构建及其搜索的方法的应用程序、功能模块等)、计算机指令等;

上述的计算机程序、计算机指令等可以分区存储在一个或多个存储器22中。并且上述的计算机程序、计算机指令、数据等可以被处理器21调用。

处理器21,用于执行存储器2存储的计算机程序,以实现上述实施例涉及的方法中的各个步骤。

具体可以参见前面方法实施例中的相关描述。

处理器21和存储器22可以是独立结构,也可以是集成在一起的集成结构。当处理器21和存储器22是独立结构时,存储器22、处理器21可以通过总线23耦合连接。

本实施例的服务器可以执行图1所示方法中的技术方案,其具体实现过程和技术原理参见图1所示方法中的相关描述,此处不再赘述。

此外,本申请实施例还提供一种计算机可读存储介质,计算机可读存储介质中存储有计算机执行指令,当用户设备的至少一个处理器执行该计算机执行指令时,用户设备执行上述各种可能的方法。

其中,计算机可读介质包括计算机存储介质和通信介质,其中通信介质包括便于从一个地方向另一个地方传送计算机程序的任何介质。存储介质可以是通用或专用计算机能够存取的任何可用介质。一种示例性的存储介质耦合至处理器,从而使处理器能够从该存储介质读取信息,且可向该存储介质写入信息。当然,存储介质也可以是处理器的组成部分。处理器和存储介质可以位于ASIC中。另外,该ASIC可以位于用户设备中。当然,处理器和存储介质也可以作为分立组件存在于通信设备中。

本领域普通技术人员可以理解:实现上述各方法实施例的全部或部分步骤可以通过程序指令相关的硬件来完成。前述的程序可以存储于一计算机可读取存储介质中。该程序在执行时,执行包括上述各方法实施例的步骤;而前述的存储介质包括:ROM、RAM、磁碟或者光盘等各种可以存储程序代码的介质。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 一种并行数据结构构建及其搜索的方法、系统

- 一种联盟链账本平台的数据结构构建方法及系统