高密度三维可编程存储器的制备方法

文献发布时间:2023-06-19 11:35:49

技术领域

本发明涉及存储器的制备技术。

背景技术

现有技术包括可擦除可编程只读存储器(EPROM),电可擦除可编程只读存储器(EEPROM),闪存,NAND-快闪存储器,硬磁盘、光盘(CD)、数字通用光盘(DVD),蓝光光盘协会注册的蓝光光盘等在内的各种数字存储技术,50余年来已经广泛用于数据存储。然而,存储介质的寿命通常小于5年到10年。针对大数据存储而开发的反熔丝存储技术,因其非常昂贵且存储密度低,不能满足海量数据存储的需求。

中国专利申请201811117240.4公开了一种三维可编程存储器的制备方法,其步骤包括:

1)形成基础结构体:以导电介质层和绝缘介质层交错重叠的方式,设置预定层数的导电介质层和绝缘介质层,形成基础结构体;

2)对基层结构体开槽:在基础结构体上至少开设3条自顶层到底层贯穿的并列的条形槽,各隔离槽相互独立,相邻两个条形槽的邻边为条形槽的长边;

3)在条形槽的内壁逐层设置预设的存储器结构所需的各存储介质层;

4)在条形槽的空腔中填充核心介质,形成核心介质层;

5)在条形槽的端部区域设置自顶层到底层贯穿的隔离槽,从形状上由隔离槽将各条形槽首尾连接为一条曲线,隔离槽侵入条形槽以使条形槽长边方向两侧的导电介质形成绝缘隔离;并在条形槽上开设自顶层到底层贯穿的切割槽孔,切割槽孔侵入其所在条形槽长边邻近的基础结构体,切割槽孔将条形槽分割为至少3个独立的存储体;

6)在隔离槽和切割槽孔中填充绝缘介质。

该方法中,首先在步骤2)开设数条独立的条形槽,槽内壁沉积存储介质并填充核心介质后,再以隔离槽将独立的条形槽连接为一条曲线。这样的方式存在不足:基础结构体是由导电介质层和绝缘介质层交替重叠构成,在某些工艺环境下,用于刻蚀导电介质层的材料和用于刻蚀绝缘介质层的材料有可能是不同的,需要反复更换不同的刻蚀材料,亦即,刻蚀层叠结构的成本比较高。该技术在步骤2)实现了层叠结构的刻蚀,在步骤5)中又一次刻蚀层叠结构,从成本上是不经济的。过于繁琐的工艺不但降低了生产效率,还可能导致良率降低。

类似的,中国专利申请201910136928.1公开了一种非易失性存储装置及其制造方法,同样存在工艺繁琐、良率不足的问题。

发明内容

本发明所要解决的技术问题是,提供一种高密度三维可编程存储器的制备方法,具有低成本、高成品率的特点。

本发明解决所述技术问题采用的技术方案是,高密度高密度三维可编程存储器的制备方法,其特征在于,包括下述步骤:

1)形成基础结构体:以导电介质层和绝缘介质层交错重叠的方式,设置预定层数的导电介质层和绝缘介质层,形成基础结构体;

2)对基础结构体开槽:在基础结构体上开设一道自顶层到底层贯穿的曲线状分割槽,由此分割槽将基础结构体分割为两个交错且相互分离的指叉结构;

3)在分割槽的内壁逐层设置预设的存储器结构所需的各存储介质层;

4)在分割槽中填充核心介质,形成核心介质层;

5)采用掩膜下刻蚀工艺,沿填充有核心介质的分割槽刻蚀出深孔,由深孔截断分割槽中填充的核心介质,形成沿分割槽的走向分布且彼此独立的预定数量的核心介质块;每一核心介质块仍然与两个指叉结构连接;所述预定数量的核心介质块至少为4个,具体数值由需求而定。

6)在步骤5)刻蚀出的深孔中填充绝缘介质。

进一步,所述步骤3)中,预设存储器结构为下述结构之一:

PN结型半导体存储器结构、肖特基半导体存储器结构、阻变存储器结构、磁变存储器结构、相变存储器结构、铁电存储器结构。

进一步的,预设存储器结构为PN结型半导体存储器结构,其包括P型导电区、N型导电区和设置于二者之间的绝缘介质区;

导电介质层为P型半导体,核心介质为N型半导体;

或者,导电介质层为N型半导体,核心介质层为P型半导体;

所述步骤3)包括:3.1在分割槽内设置绝缘层。

进一步的,预设存储器结构为肖特基型二极管存储器结构,其包括半导体导电区、金属导电区和设置于二者之间的绝缘介质区;

导电介质层为形成肖特基二极管结构所需的半导体,核心介质为形成肖特基二极管结构所需的金属;

或者,导电介质层为形成肖特基二极管结构所需的金属,核心介质层为形成肖特基二极管结构所需的半导体;

所述步骤3)包括:3.1在分割槽内设置绝缘层。

预设存储器结构为记忆介质存储器结构,所述记忆介质存储器为阻变存储器结构、磁变存储器结构、相变存储器结构或铁电存储器结构;

所述导电介质层和核心介质层的材质皆为金属或多晶硅;

所述步骤3)包括:3.1在分割槽内设置记忆介质层。

预设存储器结构为PN结型半导体存储器结构,其包括P型导电区、N型导电区和设置于二者之间的绝缘介质区;

导电介质层为P+型半导体,核心介质为N+型半导体或导体;

所述步骤3)包括:

3.1在分割槽内设置绝缘层,

3.2在绝缘层内壁设置低掺杂N型半导体层;

3.3在设置有绝缘层和低掺杂N型半导体层的条形槽的空腔内填充核心介质。

或者,预设存储器结构为PN结型半导体存储器结构,其包括P型导电区、N型导电区和设置于二者之间的绝缘介质区;

所述导电介质层为N+型半导体或导体,核心介质为P+型半导体;

所述步骤3)包括:

3.1在分割槽内设置低掺杂N型半导体层;

3.2在低掺杂N型半导体层内壁设置绝缘层;

3.3在设置有低掺杂N型半导体层和绝缘层的分割槽的空腔内填充核心介质。

或者,预设存储器结构为肖特基型半导体存储器结构,其包括金属导电区、半导体导电区和设置于二者之间的绝缘介质区;

所述步骤3)包括:

3.1在分割槽内设置绝缘层;

3.2在绝缘层内壁设置半导体层;

3.3在设置有绝缘层和导体层的分割槽的空腔内填充核心介质;

所述导电介质层为满足肖特基二极管所需的金属,所述半导体层为满足肖特基二极管所需的半导体,核心介质为导体。

所述步骤5)为:

5)采用掩膜下刻蚀工艺,沿填充有核心介质的分割槽刻蚀深孔,由深孔截断分割槽中的核心介质,形成由各个沿分割槽的走向分布且彼此独立的多个核心介质块;每一核心介质块仍然通过存储介质层与两个指叉结构连接。

本发明还包括一个穿透分割槽底部区域存储介质层的穿透步骤,所述穿透步骤为:在步骤3)完成后,刻蚀分割槽底部区域的各存储介质层直至穿透基础结构体;

或者,所述穿透步骤为:在步骤6)完成后,通过对填充的介质和底层电路加电,击穿分割槽底部区域的各存储介质层。

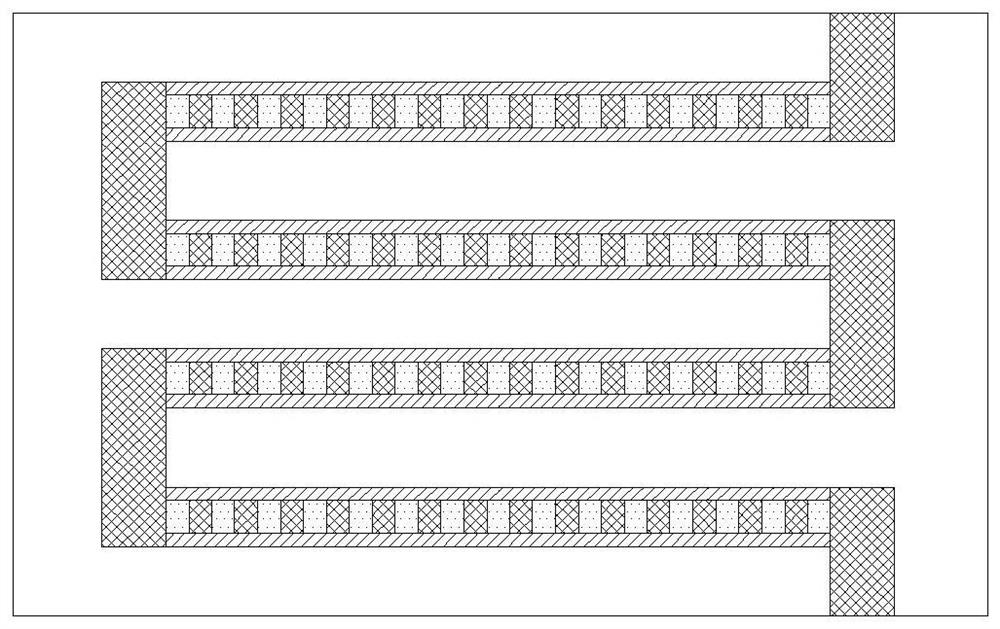

所述分割槽为包括横向矩形槽组和纵向矩形槽组,横向矩形槽组中的各横向矩形槽彼此平行,纵向形槽组中的各纵向矩形槽彼此平行,横向矩形槽垂直于纵向矩形槽,各矩形槽连接形成一道完整的曲线分割槽。

本发明的有益效果是,制备得到的半导体存储器存储密度高,并且工艺成本低,成品率高。本发明在一次多层刻蚀工艺步骤中完成了所有需要的多层刻蚀,极大的简化了工艺流程,降低了成本,提高了良品率。

本发明具有下述特点:

1、多层2bits OTP存储单元从深槽通过深井介质隔离而形成。

2、只需要两次深井刻蚀及填充,单元隔离和左右指叉隔离一步完成。

3、单元隔离自对准矩形深孔单元口径可以做到最新尺寸,以取得最高的存储密度。

4、工艺比较容易控制。

附图说明

图1为设置于衬底和底层电路的基础结构体的立体示意图。

图2为基础结构体的立体示意图。

图3为本发明的原型结构体的俯视示意图。

图4为本发明的原型结构体的正视方向示意图。

图5为本发明步骤2)处理后的原型结构体俯视方向示意图。

图6为步骤2)处理后的原型结构体A--A'方向剖视示意图。

图7为本发明步骤3处理后的原型结构体俯视方向示意图。

图8为步骤3)处理后的原型结构体A--A'方向剖视示意图。

图9为刻蚀穿透方式处理后的原型结构体A--A'方向剖视示意图。

图10为步骤4)处理后的原型结构体俯视方向示意图。

图11为步骤4)处理后的原型结构体A--A'方向剖视示意图。

图12为步骤5)处理后的原型结构体俯视方向示意图。

图13为步骤6)处理后的原型结构体俯视方向示意图。

图14为第一种实施方式的存储器结构示意图。

图15为第二种实施方式的存储器结构示意图。

图16为中国专利201910136928.1公开文件的图11。

具体实施方式

高密度三维可编程存储器的制备方法,包括下述步骤:

1)形成基础结构体:参见图1~图4,以导电介质层和绝缘介质层交错重叠的方式,设置预定层数的导电介质层和绝缘介质层,形成基础结构体。实际工艺中,基础结构体是设置在衬底和底层电路上,如图1和图4所示。图4中,41为导电介质层,42为绝缘介质层;或者42为绝缘介质层,41为导电介质层,43为底层电路,44为衬底。

2)对基础结构体开槽:参见图5、图6,在基础结构体上开设一道自顶层到底层贯穿的曲线状分割槽,由此分割槽将基础结构体分割为两个交错且相互分离的指叉结构;图6为图5的A--A'向剖视示意图。

3)参见图7~图8,在分割槽的内壁逐层设置预设的存储器结构所需的各存储介质层。此步骤可采用沉积工艺,沉积后会在分割槽的底部区域形成底部存储介质区,该底部存储介质层会将后续步骤的核心介质绝缘于底部电路,因此需要有一个“穿透”的步骤,使核心介质层和底部电路形成导电连接。

作为第一种穿透方式,穿透步骤可以是在步骤3)完成后、步骤4)以前将底部区域的存储介质区刻蚀出通孔(参见图9),如此步骤4)填充的核心介质即可与底部电路直接接触;也可以在步骤6)以后在核心介质和底部电路加电,击穿底部存储介质区,形成导电连接,即第二种穿透方式。

4)参见图10、图11,在分割槽中填充核心介质,形成核心介质层;

5)参见图12,采用掩膜下刻蚀工艺,沿填充有核心介质的分割槽刻蚀出深孔,由深孔截断分割槽中的核心介质以及存储介质,形成多个沿分割槽的走向分布且彼此独立的核心介质块;每一核心介质块仍然通过存储介质层与两个指叉结构连接。

6)在步骤5)刻蚀出的深孔中填充绝缘介质,如图13。

所述步骤3)中,预设的存储器结构为下述结构之一:

PN结型半导体存储器结构、肖特基半导体存储器结构、阻变存储器结构、磁变存储器结构、相变存储器结构、铁电存储器结构。

以图15所示的PN结型半导体存储器结构为例,其包括P型导电区、N型导电区和设置于二者之间的绝缘介质区,本发明通过将各存储介质层按照“P型导电区——绝缘介质区——N型导电区”的顺序逐层生长。当基础结构体的导电介质层本身即采用P型导电材料时,可无需再次设置P型半导体,其核心介质为N型半导体,此实施例的制备工艺中,步骤3)的存储介质层即为绝缘介质层,参见图15。

设置于分割槽内的各存储介质层可以是构成存储器的部分结构层,也可以是构成存储器的全部结构层,由基础结构体中导电介质层的材料和核心介质层的材料类型决定。例如,若基础结构体的导电介质层即为P型材料,则分割槽内壁可仅设置绝缘介质层和N型材料;若导电介质层的材料和核心介质层的材料皆为导体,则存储器的全部结构层皆需要在槽壁上逐层沉积,导电介质层和核心介质层仅仅作为引出导线。

第一种实施方式:分割槽内3层介质

本实施方式包括下述步骤:

1、在衬底和底层电路上形成基础结构体:以导电介质层(材质为低阻半导体或导体)和绝缘介质层交错重叠的方式(例如采用沉积工艺),设置预定层数的导电介质层和绝缘介质层,形成基础结构体;

2、对基层结构体开槽:采用掩膜定义,深井刻蚀工艺,在基础结构体上刻蚀出分割槽,将基础结构体分割为两个交错且相互分离的指叉结构;

3、采用ALD工艺,在分割槽的内壁沉积第一介质层101;然后再采用ALD工艺,在第一介质层101的表面沉积第二介质层102;

4、在设置有第一介质层和第二介质层的分割槽的空腔中填充核心介质形成核心介质层;

5、采用掩膜下刻蚀工艺,沿填充有核心介质的分割槽刻蚀出深孔,由深孔截断分割槽中的核心介质以及存储介质,形成沿分割槽的走向分布且彼此独立的多个核心介质块,称为核心介质块序列;每一核心介质块仍然通过存储介质层与两个指叉结构连接。

6)在深孔中填充绝缘介质材料。

本实施方式中,存储介质层包括第一介质层和第二介质层,涉及到的各介质的部分可用组合方式如下表。每一组合方式即为一个实施例。本实施方式的结构示意图参见图14。

表1

上表中的绝缘介质的厚度优选0.5~5nm,第一介质层和第二介质层皆为存储介质层。

本发明的特点是,形成包含指条和公共连接条的指叉结构,两个指叉结构相互交叉,指条之间为多个由绝缘体隔离的独立的存储体,所述绝缘体即为填充于切割槽孔内的绝缘介质。在基础结构体的每一层中,每个存储体都包含了两个存储单元,如图14,所述存储单元由第一介质——第二介质——核心介质构成,各层材料满足PN结或者肖特基结构所需。

第二种实施方式:分割槽内两层介质

本实施方式和第一种实施方式的区别是,本实施方式在分割槽中只设置两层介质,即第一介质和核心介质。

采用本实施方式的工艺所制备的存储器示意图如图10。图11是单个存储体的放大示意图。

涉及到的各介质的部分可用组合方式如下表,表中的第一介质层即为存储介质层。每一组合方式即为一个实施例。结构如图15。

表2

所述记忆介质为阻变存储器、磁变存储器、相变存储器或铁电存储器。

在本发明中,将基础结构体分割槽内除核心介质层以外的各介质层统称为“存储介质层”,例如:表1中的第一介质层(绝缘层)、表1中的第二介质层(缓冲层)以及表2中的第一介质层,本发明中,以上各层皆称为存储介质层。

本发明的工艺步骤非常简洁,可以概括为:

(1)对基础结构体开槽形成指叉结构;

(2)槽内壁设置存储介质层;

(3)填充核心介质;

(4)分割核心介质;

(5)填充绝缘介质;

本发明的图16为中国专利申请201910136928.1的图11,由其结构可知,其至少需要下述步骤:

(1)对基础结构体开槽形成指叉结构;

(2)槽内填充绝缘介质;

(3)对填充的绝缘介质第二次开槽;

(4)在步骤3开设的槽内壁设置数据存储层150;

(5)再次填充绝缘介质;

(6)深孔刻蚀;

(7)深孔内设置电极162、165。

显然的,本发明在工艺上极为简化。

- 高密度三维可编程存储器的制备方法

- 三维可编程存储器制备方法